Escolar Documentos

Profissional Documentos

Cultura Documentos

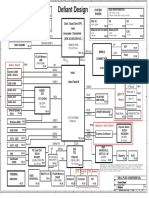

PWA FP381 schematic overview

Enviado por

Michael DavenportDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

PWA FP381 schematic overview

Enviado por

Michael DavenportDireitos autorais:

Formatos disponíveis

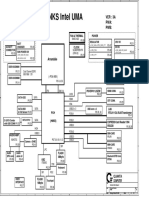

1 2 3 4 5 6 7 8

PWA FP381, PWB DY483,

JM7-INTEGRATED SCHEM UW474.

A

JM7 M/B PCB

VER : 1A A

POWER SYSTEM POWER

PG 44 Merom CLOCK

RESET CIRCUIT CK410M+LP

(478 Micro-FCPGA) REGULATOR PG 48

BATT +1.5V_RUN/+1.05V_VCCP CPU VR PG 51

PG 45 PG 3,4

SELECTOR

REGULATOR PG 49 PG 17

BATT (Symbol Rev.09) +1.8V_SUS/+1.25V_RUN DC/DC PG 52

PG 46 /+0.9V_DDR_VTT

AC/BATT CHARGER +3.3V_ALW/+5V_ALW/+15V_ALW

CONNECTOR

RUN POWER SW PG 53

PG 54 +3.3V_SUS/+5V_SUS

667/800 MHz FSB

+5V/+3.3V/+1.8V

LVDS

Panel Connector PG 24

Crestline SDVO SI1362

DDR2-SODIMM1 533/667 MHZ DDR II

B

1299 uFCBGA PG 18 B

PG 15,16 TVOUT

PG 5,6,7,8,9,10

VGA CRT CONN.

533/667 MHZ DDR II

DDR2-SODIMM2 PG 25

(Symbol Rev.09)

PG 15,16

USB2.0 (P0,P1) (EXT SIDE)

POWER USB & USB

USB2.0 (P2,P3) (EXT BACK)

IDE PG 33

Internal Media Bay DMI interface USB2.0 (P8)

33MHz PCI

CD-ROM PG 26 Q-SWITCH

USB1.0 SATA - HDD SATA PCIEx1 CARDBUS/1394 PG 42 DOCKING

PG 26 ICH8-M USB2.0 (P6)

SMART CARD OZ711EZ1TN CONNECTOR

USB2.0 (P4) PCIEx2

OZ77CR6LN 676 BGA PG 27

USB2.0 (P9)

PG 28 PG 43

IHDA PG 11,12,13,14 USB2.0 (P7) EXPRESS-CARD

C R5538 C

MINI-CARD PG 28

AUDIO/AMP MDC

(Symbol Rev.09) WLAN

PG 38,39 PG 30 PG 29

USB2.0 (P5) Biometric MINI-CARD

PG 35 WWAN

LPC PCIEx1

SPI PG 29

Bluetooth

S/PDIF Audio RJ11 Tip

for Dock Jacks for Dock Ring PG 35

PG 43 PG 39 PG 43 PG 30 SIO SIO

MEC5025 ECE5018 BCM5755M E-Switch RJ45/Magnetics

PI3L500

128KB Flash BC Expander /BCM5752 +3.3V_LAN

Keyboard ECE1077 BC TMKBC USB 2.0 Hub(4) PG 41

Controllor PG 40 PG 41

PG 34 128 Pins VTQFP 128 Pins VTQFP

DOCK LPC

PG 31 PG 32

D D

SPI PS/2

USER Keyboard Touchpad/ Serial Port IrDA FAN & THERMAL QUANTA

FLASH

INTERFACE Stick point EMC4001

Title

COMPUTER

PG 36 PG 36 PG 34 PG 35 PG 33 PG 35 PG 37 Schematic Block Diagram1

Size Document Number Rev

JM7 1A

Date: Monday, June 26, 2006 Sheet 1 of 57

1 2 3 4 5 6 7 8

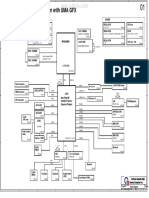

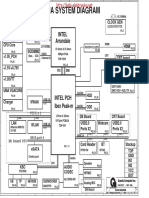

1 2 3 4 5 6 7 8

INDEX Power States

Control S3/ S4/ S5/

Pg# Description Power Rail S0/M0 S3/M1 S3/M1 S4/M1

Signal M-off M-off M-off

1 Schematic Block Diagram

2 Front Page +3.3V_ALW

3-4 Merom

+5V_ALW

5-10 Crestline

A 11-14 ICH8M +3.3V_LAN A

15-16 DDRII SO-DIMM(200P)

17 Clock Generator

18-23 VGA

24 LCD Conn. & SSP

+1.8V_SUS

25 CRT Conn

26 SATA & IDE Conn +0.9V_DDR_VTT

27 PCCARD/Conn & 1394

+5V_SUS

28 Express Card & Smart Card

29 Mini Card +3.3V_SUS

30 MDC Conn.

+5V_RUN

31 SIO (MEC5025)

32 SIO (MEC5018) +3.3V_RUN

33 SERIAL PORT & USB

+1.8V_RUN

34 Flash ROM, RTC & ECE1077

B 35 TP,BT & FIR +1.25V_RUN B

36 Switch,Keyboard & LED

+1.5V_RUN

37 FAN & Thermal

38-39 Audio CODEC(STAC9205)/Phone Jack +1.05V_VCCP

40-41 LOM (Nineveh)/Switch

VCC_VCRE

42-43 Docking Conn/Q-Switch

44 System Reset Circuit +LCDVCC

45-46 Battery Selector & Charger

+5V_MOD

47 DDR2_1.8VSUS, 0.9V

48 1.5VSUS,1.05V(VTT)

49 VGA DC/DC,1.25V,1.05V

50 CPU_MAX8786(3phase)

51 D/D Power

52 RUN Power Switch

53 DCIN,Batt

C C

54 PAD& SCREW

55 EMI CAP

56 SMBUS BLOCK

D D

QUANTA

Title

COMPUTER

Index & Power Status

Size Document Number Rev

JM7 1A

Date: Monday, June 26, 2006 Sheet 2 of 57

1 2 3 4 5 6 7 8

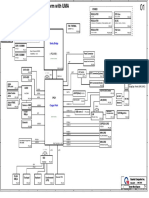

1 2 3 4 5 6 7 8

H_A#[3..16] U6A H_D#[0..63] U6B H_D#[0..63]

5 H_A#[3..16] 5 H_D#[0..63] H_D#[0..63] 5

H_A#3 J4 H1 H_D#0 E22 Y22 H_D#32

A[3]# ADS# H_ADS# 5 D[0]# D[32]#

H_A#4 L5 E2 H_D#1 F24 AB24 H_D#33

A[4]# BNR# H_BNR# 5 D[1]# D[33]#

H_A#5 L4 G5 H_D#2 E26 V24 H_D#34

A[5]# BPRI# H_BPRI# 5 D[2]# D[34]#

H_A#6 K5 H_D#3 G22 V26 H_D#35

H_A#7 A[6]# H_D#4 D[3]# D[35]# H_D#36

M3 A[7]# DEFER# H5 H_DEFER# 5 F23 D[4]# D[36]# V23

H_A#8 N2 F21 H_D#5 G25 T22 H_D#37

A[8]# DRDY# H_DRDY# 5 D[5]# D[37]#

H_A#9 J1 E1 H_D#6 E25 U25 H_D#38

A[9]# DBSY# H_DBSY# 5 D[6]# D[38]#

H_A#10 N3 +1.05V_VCCP H_D#7 E23 U23 H_D#39

A[10]# H_BR0# 5 D[7]# D[39]#

ADDR GROUP 0

DATA GRP 0

DATA GRP 2

H_A#11 P5 F1 Layout Note: H_D#8 K24 Y25 H_D#40

H_A#12 A[11]# BR0# R352 56 H_D#9 D[8]# D[40]# H_D#41

P2 A[12]# Place R646 G24 D[9]# D[41]# W22

1

H_A#13 L2 D20 H_IERR# 1 2 H_D#10 J24 Y23 H_D#42

CONTROL

A A[13]# IERR# +1.05V_VCCP close to D[10]# D[42]# A

H_A#14 P4 B3 R356 H_D#11 J23 W24 H_D#43

A[14]# INIT# H_INIT# 11 D[11]# D[43]#

H_A#15 P1 A[15]#

51/F_NC CPU. H_D#12 H22 D[12]# D[44]# W25 H_D#44

H_A#16 R1 H4 H_D#13 F26 AA23 H_D#45

A[16]# LOCK# H_LOCK# 5 D[13]# D[45]#

M1 H_D#14 K22 AA24 H_D#46

5 H_ADSTB#0

2

H_REQ#[0..4] ADSTB[0]# H_RESET# H_D#15 D[14]# D[46]# H_D#47

5 H_REQ#[0..4] RESET# C1 H_RESET# 5 H23 D[15]# D[47]# AB25

H_REQ#0 K3 F3 J26 Y26

REQ[0]# RS[0]# H_RS#0 5 5 H_DSTBN#0 DSTBN[0]# DSTBN[2]# H_DSTBN#2 5

H_REQ#1 H2 F4 H26 AA26

REQ[1]# RS[1]# H_RS#1 5 5 H_DSTBP#0 DSTBP[0]# DSTBP[2]# H_DSTBP#2 5

H_REQ#2 K2 G3 H25 U22

REQ[2]# RS[2]# H_RS#2 5 5 H_DINV#0 DINV[0]# DINV[2]# H_DINV#2 5

H_REQ#3 J3 G2

REQ[3]# TRDY# H_TRDY# 5 H_D#[0..63] H_D#[0..63]

H_REQ#4 L1

H_A#[17..35] REQ[4]# 5 H_D#[0..63] H_D#[0..63] 5

G6 H_D#16 N22 AE24 H_D#48

5 H_A#[17..35] HIT# H_HIT# 5 D[16]# D[48]#

H_A#17 Y2 E4 H_D#17 K25 AD24 H_D#49

A[17]# HITM# H_HITM# 5 D[17]# D[49]#

H_A#18 U5 H_D#18 P26 AA21 H_D#50

H_A#19 A[18]# ITP_BPM#0 H_D#19 D[18]# D[50]# H_D#51

R3 A[19]# BPM[0]# AD4 R23 D[19]# D[51]# AB22

H_A#20 W6 AD3 ITP_BPM#1 Layout Note: H_D#20 L23 AB21 H_D#52

A[20]# BPM[1]# D[20]# D[52]#

ADDR GROUP 1

H_A#21 U4 AD1 ITP_BPM#2 H_D#21 M24 AC26 H_D#53

XDP/ITP SIGNALS

H_A#22 A[21]# BPM[2]# ITP_BPM#3

Place voltage H_D#22 D[21]# D[53]# H_D#54

Y5 A[22]# BPM[3]# AC4 L22 D[22]# D[54]# AD20

divider within

DATA GRP 1

DATA GRP 3

H_A#23 U1 AC2 ITP_BPM#4 H_D#23 M23 AE22 H_D#55

H_A#24 A[23]# PRDY# ITP_BPM#5 0.5" of GTLREF H_D#24 D[23]# D[55]# H_D#56

R4 A[24]# PREQ# AC1 P25 D[24]# D[56]# AF23

H_A#25 T5 AC5 ITP_TCK pin H_D#25 P23 AC25 H_D#57

H_A#26 A[25]# TCK ITP_TDI H_D#26 D[25]# D[57]# H_D#58

T3 A[26]# TDI AA6 P22 D[26]# D[58]# AE21

H_A#27 W2 AB3 ITP_TDO H_D#27 T24 AD21 H_D#59

H_A#28 A[27]# TDO ITP_TMS +1.05V_VCCP H_D#28 D[27]# D[59]# H_D#60

W5 A[28]# TMS AB5 R24 D[28]# D[60]# AC22

H_A#29 Y4 AB6 ITP_TRST# H_D#29 L25 AD23 H_D#61

H_A#30 A[29]# TRST# ITP_DBRESET# H_D#30 D[29]# D[61]# H_D#62

U2 A[30]# DBR# C20 ITP_DBRESET# 13,31 T25 D[30]# D[62]# AF22

2

H_A#31 V4 H_D#31 N25 AC23 H_D#63

H_A#32 A[31]# R353 56 R339 D[31]# D[63]#

W3 A[32]# 5 H_DSTBN#1 L26 DSTBN[1]# DSTBN[3]# AE25 H_DSTBN#3 5

H_A#33 AA4 THERMAL 2 1 +1.05V_VCCP 1K/F M26 AF24

A[33]# 5 H_DSTBP#1 DSTBP[1]# DSTBP[3]# H_DSTBP#3 5

H_A#34 AB2 N24 AC20

A[34]# 5 H_DINV#1 DINV[1]# DINV[3]# H_DINV#3 5

B H_A#35 AA3 D21 H_PROCHOT# B

PAD T44

1

A[35]# PROCHOT# H_THERMDA V_CPU_GTLREF AD26 COMP0

5 H_ADSTB#1 V1 ADSTB[1]# THERMDA A24 H_THERMDA 37 GTLREF COMP[0] R26 Note:

B25 H_THERMDC CPU_TEST1 C23 MISC COMP[1] U26 COMP1 H_DPRTSTP need to daisy chain

THERMDC H_THERMDC 37 TEST1

2

A6 CPU_TEST2 D25 AA1 COMP2

11 H_A20M# A20M# TEST2 COMP[2] from ICH8 to IMVP6 to CPU.

A5 C7 H_THERMTRIP# CPU_TEST3 C24 Y1 COMP3

11 H_FERR# FERR# THERMTRIP# H_THERMTRIP# 37 TEST3 COMP[3]

ICH

C4 R360 56 R338 CPU_TEST4 AF26

11 H_IGNNE# IGNNE# TEST4

1 2 +1.05V_VCCP 2K/F CPU_TEST5 AF1 E5

TEST5 DPRSTP# H_DPRSTP# 6,11,51

D5 H CLK CPU_TEST6 A26 B5

11 H_STPCLK# H_DPSLP# 11

1

STPCLK# TEST6 DPSLP#

11 H_INTR C6 LINT0 DPWR# D24 H_DPWR# 5

11 H_NMI B4 LINT1 BCLK[0] A22 CLK_CPU_BCLK 17 6,17 CPU_MCH_BSEL0 B22 BSEL[0] PWRGOOD D6 H_PWRGOOD 11

11 H_SMI# A3 SMI# BCLK[1] A21 CLK_CPU_BCLK# 17 6,17 CPU_MCH_BSEL1 B23 BSEL[1] SLP# D7 H_CPUSLP# 5

6,17 CPU_MCH_BSEL2 C21 BSEL[2] PSI# AE6 H_PSI# 51

M4 RSVD[01]

N5 Merom Ball-out Rev 1a

RSVD[02] C101

T2 RSVD[03] Voltage Level shift

V3 H_THERMDA 1 2 H_THERMDC

RSVD[04]

RESERVED

B2 +1.05V_VCCP +3.3V_ALW

RSVD[05] 2200P/50V_NC CPU_TEST3

C3 RSVD[06] PAD T7

D2 PAD T42 CPU_TEST5

RSVD[07]

2

D22 R358 1K/F_NC

RSVD[08] CPU_TEST1

D3 RSVD[09] 1 2 For the purpose of testability, route these signals

F6 R351 R355 1K/F_NC through a ground referenced Z0 = 55ohm trace that

RSVD[10] 2.2K_NC CPU_TEST2

1 2

ends in a via that is near a GND via and is

2

Q57 C401 0.1U/10V_NC

1

2 1 CPU_TEST4 accessible through an oscilloscope connection.

Merom Ball-out Rev 1a H_PROCHOT# 1 3 R357 0_NC

CPU_PROCHOT# 31

1 2 CPU_TEST6

2N7002W-7-F_NC

C

Place C close to the FSB BCLK BSEL2 BSEL1 BSEL0 C

CPU_TEST4 pin. Make sure

CPU_TEST4 routing is 533 133 0 0 1

Populate ITP700Flex for bringup reference to GND and away 667 166 0 1 1

from other noisy signal.

+1.05V_VCCP 800 200 0 1 0

Layout Note:

Place couple 0.1uF Decoupling COMP0

caps with in 0.1" ITP connector.

1

COMP1

R9 R7 R3 R2 COMP2

51/F 51 39/F 150 +1.05V_VCCP +3.3V_ALW COMP3

ITP700 layout guidelines

JITP1 C3 0.1U/10V

2

2

2 1 Signal Resistor Value Connect To Resistor Placement

ITP_TDI 1 27 R344 R343 R347 R350

ITP_TMS TDI VTT0 C2 0.1U/10V 54.9/F 27.4/F 54.9/F 27.4/F

2 TMS VTT1 28 TDI 150 ohm ± 5% VCCP Place the pull-up near CPU

ITP_TCK 5 26 2 1

ITP_TDO R6 1 TCK VTAP

2 0 7 TMS 39 ohm ± 1% VCCP Within 200ps of ITP connector

1

ITP_TRST# TDO

3 TRST#

500 to 680

R8 22.6/F R10 150 TRST# ohm ± 5% GND Place the pull-down near CPU Comp0,2 connect with Zo=27.4ohm,Comp1,3

H_RESET# 1 2 12 25 ITP_DBRESET# 2 1 connect with Zo=55ohm, make those traces

RESET# DBR#

Layout Note: DBA# 24 Connect to TCK pin of CPU and then length shorter than 0.5".Trace should be

ITP_TCK

Place R8 close ITP. connect it to FBO pin of ITP connector at least 25 mils away from any other

11 FBO

TCK 27 ohm ± 1% GND in daisy chain. Place the pull-down toggling signal.

17 CLK_CPU_ITP# 8 BCLKN

near TCK0 pin of ITP connector

D 9 23 ITP_BPM#0 D

17 CLK_CPU_ITP BCLKP BPM0#

21 ITP_BPM#1 TDO 51 ohm ± 5% VCCP Place the pull-up near ITP

BPM1# ITP_BPM#2

BPM2# 19

10 17 ITP_BPM#3 Connect to CPURST# pin of GMCH through

R5 27/F

14

16

GND0

GND1

BPM3#

BPM4# 15

13

ITP_BPM#4

ITP_BPM#5

22.6 ohm ± 1%

series resistor

the series resistor placed within QUANTA

ITP_TCK GND2 BPM5# 200ps of ITP connector. Place the

2

R4

1

649/F

18

20

22

GND3

GND4

NC0

NC1

4

6

29

RESET# and pullup 51

ohm ± 1%.

VCCP

pull-up after the series resistor from

Title

COMPUTER

GND5 GND_0 ITP connector.

2 1 ITP_TRST# 30 Merom Processor (HOST BUS)

GND_1

ITP700Flex_NC Size Document Number Rev

JM7 1A

Date: Wednesday, June 28, 2006 Sheet 3 of 57

1 2 3 4 5 6 7 8

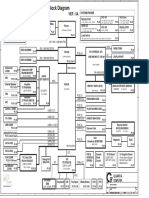

1 2 3 4 5 6 7 8

+VCC_CORE +VCC_CORE U6D

U6C A4 P6

VSS[001] VSS[082]

A7 VCC[001] VCC[068] AB20 A8 VSS[002] VSS[083] P21

A9 VCC[002] VCC[069] AB7 A11 VSS[003] VSS[084] P24

+VCC_CORE All use 10U 4V(+-20%,X6S,0805)Pb-Free. A10 AC7 A14 R2

VCC[003] VCC[070] VSS[004] VSS[085]

A12 VCC[004] VCC[071] AC9 A16 VSS[005] VSS[086] R5

A13 VCC[005] VCC[072] AC12 A19 VSS[006] VSS[087] R22

A15 VCC[006] VCC[073] AC13 A23 VSS[007] VSS[088] R25

1

A17 VCC[007] VCC[074] AC15 AF2 VSS[008] VSS[089] T1

C415 C73 C72 C71 C70 A18 AC17 B6 T4

10U/4V 10U/4V 10U/4V 10U/4V 10U/4V VCC[008] VCC[075] VSS[009] VSS[090]

A20 AC18 B8 T23

2

2

A VCC[009] VCC[076] VSS[010] VSS[091] A

B7 VCC[010] VCC[077] AD7 B11 VSS[011] VSS[092] T26

B9 VCC[011] VCC[078] AD9 B13 VSS[012] VSS[093] U3

B10 VCC[012] VCC[079] AD10 B16 VSS[013] VSS[094] U6

B12 VCC[013] VCC[080] AD12 B19 VSS[014] VSS[095] U21

+VCC_CORE B14 AD14 B21 U24

VCC[014] VCC[081] VSS[015] VSS[096]

B15 VCC[015] VCC[082] AD15 B24 VSS[016] VSS[097] V2

B17 VCC[016] VCC[083] AD17 C5 VSS[017] VSS[098] V5

B18 VCC[017] VCC[084] AD18 C8 VSS[018] VSS[099] V22

1

1

B20 VCC[018] VCC[085] AE9 C11 VSS[019] VSS[100] V25

C405 C406 C69 C68 C425 C9 AE10 C14 W1

10U/4V 10U/4V 10U/4V 10U/4V 10U/4V VCC[019] VCC[086] VSS[020] VSS[101]

C10 AE12 C16 W4

2

2

VCC[020] VCC[087] VSS[021] VSS[102]

C12 VCC[021] VCC[088] AE13 C19 VSS[022] VSS[103] W23

C13 VCC[022] VCC[089] AE15 C2 VSS[023] VSS[104] W26

C15 VCC[023] VCC[090] AE17 C22 VSS[024] VSS[105] Y3

8 inside cavity, north side, secondary layer. C17 VCC[024] VCC[091] AE18 C25 VSS[025] VSS[106] Y6

C18 VCC[025] VCC[092] AE20 D1 VSS[026] VSS[107] Y21

D9 VCC[026] VCC[093] AF9 D4 VSS[027] VSS[108] Y24

+VCC_CORE D10 AF10 D8 AA2

VCC[027] VCC[094] VSS[028] VSS[109]

D12 VCC[028] VCC[095] AF12 D11 VSS[029] VSS[110] AA5

D14 VCC[029] VCC[096] AF14 D13 VSS[030] VSS[111] AA8

D15 VCC[030] VCC[097] AF15 D16 VSS[031] VSS[112] AA11

1

1

D17 VCC[031] VCC[098] AF17 D19 VSS[032] VSS[113] AA14

C410 C411 C407 C408 C409 D18 AF18 D23 AA16

10U/4V 10U/4V 10U/4V 10U/4V 10U/4V VCC[032] VCC[099] +1.05V_VCCP VSS[033] VSS[114]

E7 AF20 D26 AA19

2

2

VCC[033] VCC[100] VSS[034] VSS[115]

E9 VCC[034] E3 VSS[035] VSS[116] AA22

E10 VCC[035] VCCP[01] G21 E6 VSS[036] VSS[117] AA25

E12 VCC[036] VCCP[02] V6 E8 VSS[037] VSS[118] AB1

1

E13 VCC[037] VCCP[03] J6 E11 VSS[038] VSS[119] AB4

+VCC_CORE E15 K6 + C430 E14 AB8

VCC[038] VCCP[04] 220U/4V VSS[039] VSS[120]

B E17 VCC[039] VCCP[05] M6 E16 VSS[040] VSS[121] AB11 B

E18 J21 E19 AB13

2

VCC[040] VCCP[06] VSS[041] VSS[122]

E20 VCC[041] VCCP[07] K21 E21 VSS[042] VSS[123] AB16

1

1

F7 VCC[042] VCCP[08] M21 E24 VSS[043] VSS[124] AB19

C434 C435 C412 C432 C433 F9 N21 F5 AB23

10U/4V 10U/4V 10U/4V 10U/4V 10U/4V VCC[043] VCCP[09] VSS[044] VSS[125]

F10 N6 F8 AB26

2

2

VCC[044] VCCP[10] VSS[045] VSS[126]

F12 VCC[045] VCCP[11] R21 F11 VSS[046] VSS[127] AC3

F14 R6 +1.5V_RUN F13 AC6

VCC[046] VCCP[12] VSS[047] VSS[128]

F15 VCC[047] VCCP[13] T21 F16 VSS[048] VSS[129] AC8

8 inside cavity, south side, secondary layer. F17 VCC[048] VCCP[14] T6 F19 VSS[049] VSS[130] AC11

F18 VCC[049] VCCP[15] V21 F2 VSS[050] VSS[131] AC14

F20 VCC[050] VCCP[16] W21 F22 VSS[051] VSS[132] AC16

AA7 VCC[051] F25 VSS[052] VSS[133] AC19

+VCC_CORE AA9 B26 G4 AC21

VCC[052] VCCA[01] VSS[053] VSS[134]

AA10 VCC[053] VCCA[02] C26 G1 VSS[054] VSS[135] AC24

AA12 VCC[054] G23 VSS[055] VSS[136] AD2

1

AA13 AD6 C443 C446 G26 AD5

VCC[055] VID[0] VID0 51 VSS[056] VSS[137]

1

AA15 AF5 0.01U/25V 10U/4V H3 AD8

VCC[056] VID[1] VID1 51 VSS[057] VSS[138]

C419 C429 C439 C438 C437 C436 AA17 AE5 H6 AD11

VID2 51

2

10U/4V 10U/4V 10U/4V 10U/4V 10U/4V 10U/4V VCC[057] VID[2] VSS[058] VSS[139]

AA18 AF4 VID3 51 H21 AD13

2

VCC[058] VID[3] VSS[059] VSS[140]

AA20 VCC[059] VID[4] AE3 VID4 51 H24 VSS[060] VSS[141] AD16

AB9 VCC[060] VID[5] AF3 VID5 51 J2 VSS[061] VSS[142] AD19

AC10 VCC[061] VID[6] AE2 VID6 51 J5 VSS[062] VSS[143] AD22

6 inside cavity, north side, primary layer. AB10 VCC[062] J22 VSS[063] VSS[144] AD25

AB12 VCC[063] Layout Note: J25 VSS[064] VSS[145] AE1

AB14 AF7 VCCSENSE Place C105 near PIN K1 AE4

VCC[064] VCCSENSE VCCSENSE 51 VSS[065] VSS[146]

+VCC_CORE AB15 K4 AE8

VCC[065] B26. VSS[066] VSS[147]

AB17 VCC[066] K23 VSS[067] VSS[148] AE11

AB18 AE7 VSSSENSE K26 AE14

VCC[067] VSSSENSE VSSSENSE 51 VSS[068] VSS[149]

L3 VSS[069] VSS[150] AE16

1

C C

Merom Ball-out Rev 1a L6 AE19

C89 C88 C87 C86 C85 C84 VSS[070] VSS[151]

. L21 VSS[071] VSS[152] AE23

10U/4V 10U/4V 10U/4V 10U/4V 10U/4V 10U/4V L24 AE26

2

+VCC_CORE VSS[072] VSS[153]

M2 VSS[073] VSS[154] A2

M5 VSS[074] VSS[155] AF6

1

M22 VSS[075] VSS[156] AF8

6 inside cavity, south side, primary layer. R336 M25 AF11

100/F VSS[076] VSS[157]

N1 VSS[077] VSS[158] AF13

N4 VSS[078] VSS[159] AF16

N23 AF19

2

VSS[079] VSS[160]

N26 VSS[080] VSS[161] AF21

VCCSENSE P3 A25

VSSSENSE VSS[081] VSS[162]

VSS[163] AF25

+PWR_SRC

1

+1.05V_VCCP Merom Ball-out Rev 1a

R334 .

1

1

100/F

+ C59 + C78 + C99 + C113

1

100U/25V 100U/25V 100U/25V 100U/25V_NC

2

C416 C426 C417 C427 C418 C428

2

0.1U/10V 0.1U/10V 0.1U/10V 0.1U/10V 0.1U/10V 0.1U/10V

2

Route VCCSENSE and VSSSENSE

Layout Note: traces at 27.4ohms and

Layout out: Need to add 100uF cap on PWR_SRC for cap singing. length matched to within 25

Place these inside socket cavity on North side secondary. Place on PWR_SRC near +VCC_CORE. mil. Place PU and PD within

2 inch of CPU.

D D

QUANTA

Title

COMPUTER

Merom Processor (POWER)

Size Document Number Rev

JM7 1A

Date: Wednesday, June 28, 2006 Sheet 4 of 57

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8

U9A H_A#[3..35]

H_D#[0..63] H_A#[3..35] 3

J13 H_A#3

3 H_D#[0..63] H_A#_3

H_D#0 E2 B11 H_A#4

H_D#1 H_D#_0 H_A#_4 H_A#5

A

G2 H_D#_1 H_A#_5 C11 A

H_D#2 G7 M11 H_A#6

H_D#3 H_D#_2 H_A#_6 H_A#7

M6 H_D#_3 H_A#_7 C15

H_D#4 H7 F16 H_A#8

H_D#5 H_D#_4 H_A#_8 H_A#9

H3 H_D#_5 H_A#_9 L13

H_D#6 G4 G17 H_A#10

H_D#7 H_D#_6 H_A#_10 H_A#11

F3 H_D#_7 H_A#_11 C14

H_D#8 N8 K16 H_A#12

H_D#9 H_D#_8 H_A#_12 H_A#13

H2 H_D#_9 H_A#_13 B13

H_D#10 M10 L16 H_A#14

H_D#11 H_D#_10 H_A#_14 H_A#15

N12 H_D#_11 H_A#_15 J17

H_D#12 N9 B14 H_A#16

+1.05V_VCCP H_D#13 H_D#_12 H_A#_16 H_A#17

H5 H_D#_13 H_A#_17 K19

H_D#14 P13 P15 H_A#18

H_D#15 H_D#_14 H_A#_18 H_A#19

K9 H_D#_15 H_A#_19 R17

H_D#16 M2 B16 H_A#20

H_D#_16 H_A#_20

1

H_D#17 W10 H20 H_A#21

R374 H_D#18 H_D#_17 H_A#_21 H_A#22

Y8 H_D#_18 H_A#_22 L19

221/F H_D#19 V4 D17 H_A#23

H_D#20 H_D#_19 H_A#_23 H_A#24

M3 H_D#_20 H_A#_24 M17

H_D#21 J1 N16 H_A#25

2

H_SWING H_D#22 H_D#_21 H_A#_25 H_A#26

N5 H_D#_22 H_A#_26 J19

H_D#23 N3 B18 H_A#27

H_D#_23 H_A#_27

1

H_D#24 W6 E19 H_A#28

H_D#_24 H_A#_28

2

R373 H_D#25 W9 B17 H_A#29

100/F C454 H_D#26 H_D#_25 H_A#_29 H_A#30

N2 H_D#_26 H_A#_30 B15

0.1U/10V H_D#27 Y7 E17 H_A#31

1

H_D#28 H_D#_27 H_A#_31 H_A#32

Y9 C18

2

H_D#29 H_D#_28 H_A#_32 H_A#33

P4 H_D#_29 H_A#_33 A19

H_D#30 W3 B19 H_A#34

H_D#31 H_D#_30 H_A#_34 H_A#35

B N1 H_D#_31 H_A#_35 N19 B

H_D#32 AD12

H_D#33 H_D#_32

AE3 H_D#_33 H_ADS# G12 H_ADS# 3

H_D#34 AD9 H17

H_D#_34 H_ADSTB#_0 H_ADSTB#0 3

H_D#35 AC9 G20

H_D#_35 H_ADSTB#_1 H_ADSTB#1 3

HOST

H_D#36 AC7 C8

H_D#_36 H_BNR# H_BNR# 3

+1.05V_VCCP H_D#37 AC14 E8

H_D#_37 H_BPRI# H_BPRI# 3

H_D#38 AD11 F12

H_D#_38 H_BREQ# H_BR0# 3

H_D#39 AC11 D6

H_D#_39 H_DEFER# H_DEFER# 3

H_D#40 AB2 C10

H_D#_40 H_DBSY# H_DBSY# 3

H_D#41 AD7 AM5

H_D#_41 HPLL_CLK CLK_MCH_BCLK 17

1

H_D#42 AB1 AM7

H_D#_42 HPLL_CLK# CLK_MCH_BCLK# 17

R413 R410 H_D#43 Y3 H8

H_D#_43 H_DPWR# H_DPWR# 3

54.9/F 54.9/F H_D#44 AC6 K7

H_D#_44 H_DRDY# H_DRDY# 3

H_D#45 AE2 E4

H_D#_45 H_HIT# H_HIT# 3

H_D#46 AC5 C6 H_HITM# 3

2

H_SCOMP H_D#47 H_D#_46 H_HITM#

AG3 H_D#_47 H_LOCK# G10 H_LOCK# 3

H_SCOMP# H_D#48 AJ9 B7

H_D#_48 H_TRDY# H_TRDY# 3

H_D#49 AH8

H_RCOMP H_D#50 H_D#_49

AJ14 H_D#_50

H_D#51 AE9 H_D#_51

1

H_D#52 AE11

R372 H_D#53 H_D#_52

AH12 H_D#_53 H_DINV#_0 K5 H_DINV#0 3

24.9/F H_D#54 AJ5 L2

H_D#_54 H_DINV#_1 H_DINV#1 3

H_D#55 AH5 AD13

H_D#_55 H_DINV#_2 H_DINV#2 3

Layout Note: H_D#56 AJ6 AE13 H_DINV#3 3

2

H_D#57 H_D#_56 H_DINV#_3

H_RCOMP trace should be AE7 H_D#_57

H_D#58 AJ7 M7

10-mil wide with 20-mil H_D#_58 H_DSTBN#_0 H_DSTBN#0 3

H_D#59 AJ2 K3

H_D#_59 H_DSTBN#_1 H_DSTBN#1 3

C

spacing. H_D#60 AE5 H_D#_60 H_DSTBN#_2 AD2 H_DSTBN#2 3 C

H_D#61 AJ3 AH11

H_D#_61 H_DSTBN#_3 H_DSTBN#3 3

H_D#62 AH2

H_D#63 H_D#_62

AH13 H_D#_63 H_DSTBP#_0 L7 H_DSTBP#0 3

H_DSTBP#_1 K2 H_DSTBP#1 3

H_DSTBP#_2 AC2 H_DSTBP#2 3

H_SWING B3 AJ10

+1.05V_VCCP H_SWING H_DSTBP#_3 H_DSTBP#3 3

H_RCOMP C2 H_RCOMP

H_REQ#_0 M14 H_REQ#0 3

H_SCOMP W1 E13

H_SCOMP H_REQ#_1 H_REQ#1 3

2

H_SCOMP# W2 A11

H_SCOMP# H_REQ#_2 H_REQ#2 3

R376 H13

H_REQ#_3 H_REQ#3 3

1K/F B6 B12

3 H_RESET# H_CPURST# H_REQ#_4 H_REQ#4 3

3 H_CPUSLP# E5 H_CPUSLP#

E12 H_RS#0 3

1

H_RS#_0

H_RS#_1 D7 H_RS#1 3

H_RS#_2 D8 H_RS#2 3

H_REF B9 H_AVREF

A9 H_DVREF

1

CRESTLINE_1p0

1

R375 C457

2K/F 0.1U/10V

2

2

Layout Note:

Place the 0.1 uF

D decoupling capacitor D

within 100 mils from

GMCH pins.

QUANTA

Title

COMPUTER

Crestline (HOST)

Size Document Number Rev

JM7 1A

Date: Wednesday, June 28, 2006 Sheet 5 of 57

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8

U9B U9C +VCC_PEG

+1.8V_SUS P36 J40 R397 24.9/F

RSVD1 24 BIA_PWM L_BKLT_CTRL

P37 RSVD2 SM_CK_0 AV29 M_CLK_DDR0 15 32 PANEL_BKEN H39 L_BKLT_EN PEG_COMPI N43 VCC3G_PCIE_R 1 2

1

R35 BB23 LCTLA_CLK E39 M43

RSVD3 SM_CK_1 M_CLK_DDR1 15 L_CTRL_CLK PEG_COMPO

N35 BA25 LCTLB_DATA E40

RSVD4 SM_CK_3 M_CLK_DDR3 15 L_CTRL_DATA

R446 AR12 AV23 L_IBG LCD_DDCCLK C37

RSVD5 SM_CK_4 M_CLK_DDR4 15 24 LCD_DDCCLK L_DDC_CLK

1K/F AR13 LCD_DDCDAT D35 J51

RSVD6 24 LCD_DDCDAT L_DDC_DATA PEG_RX#_0

2

AM12 AW30 M_CLK_DDR#0 15 24 ENVDD K40 L51 SDVOB_INT- 18

2

SM_RCOMP_VOH RSVD7 SM_CK#_0 R401 L_VDD_EN PEG_RX#_1

AN13 RSVD8 SM_CK#_1 BA23 M_CLK_DDR#1 15 PEG_RX#_2 N47

J12 AW25 2.4K L_IBG L41 T45

RSVD9 SM_CK#_3 M_CLK_DDR#3 15 LVDS_IBG PEG_RX#_3

1

1

C539 C538 AR37 AW23 PAD T53 L43 T50

RSVD10 SM_CK#_4 M_CLK_DDR#4 15 LVDS_VBG PEG_RX#_4

0.01U/25V 2.2U/6.3V AM36 N41 U40

1

A

R447 RSVD11 LVDS_VREFH PEG_RX#_5 A

AL36 BE29 DDR_CKE0_DIMMA 15,16 N40 Y44

2

3.01K/F RSVD12 SM_CKE_0 LVDS_VREFL PEG_RX#_6

AM37 RSVD13 SM_CKE_1 AY32 DDR_CKE1_DIMMA 15,16 24 LCD_ACLK- D46 LVDSA_CLK# PEG_RX#_7 Y40

2 D20 BD39 DDR_CKE3_DIMMB 15,16 UMA 24 LCD_ACLK+ C45 AB51

MUXING

RSVD14 SM_CKE_3 LVDSA_CLK PEG_RX#_8

SM_CKE_4 BG37 DDR_CKE4_DIMMB 15,16 24 LCD_BCLK- D44 LVDSB_CLK# PEG_RX#_9 W49

SM_RCOMP_VOL E42 AD44

24 LCD_BCLK+ LVDSB_CLK PEG_RX#_10

LVDS

SM_CS#_0 BG20 DDR_CS0_DIMMA# 15,16 PEG_RX#_11 AD40

1

C542 C546 BK16 G51 AG46

SM_CS#_1 DDR_CS1_DIMMA# 15,16 24 LCD_A0- LVDSA_DATA#_0 PEG_RX#_12

0.01U/25V 2.2U/6.3V BG16 +1.8V_SUS E51 AH49

SM_CS#_2 DDR_CS2_DIMMB# 15,16 24 LCD_A1- LVDSA_DATA#_1 PEG_RX#_13

R444 H10 BE13 F49 AG45

DDR_CS3_DIMMB# 15,16 24 LCD_A2-

2

1K/F RSVD20 SM_CS#_3 LVDSA_DATA#_2 PEG_RX#_14

B51 RSVD21 PEG_RX#_15 AG41

1

BJ20 BH18 M_ODT0 15,16

2

RSVD22 SM_ODT_0

RSVD

GRAPHICS

BK22 RSVD23 SM_ODT_1 BJ15 M_ODT1 15,16 24 LCD_A0+ G50 LVDSA_DATA_0 PEG_RX_0 J50

BF19 BJ14 R437 E50 L50

RSVD24 SM_ODT_2 M_ODT2 15,16 24 LCD_A1+ LVDSA_DATA_1 PEG_RX_1 SDVOB_INT+ 18

DDR

BH20 BE16 20/F F48 M47

RSVD25 SM_ODT_3 M_ODT3 15,16 24 LCD_A2+ LVDSA_DATA_2 PEG_RX_2

Santa Rosa Platform MOW WW15 BK18 U44

2

RSVD26 SMRCOMPP SMRCOMPP PEG_RX_3

For 4Gb DRAM support, BJ18 RSVD27 SM_RCOMP BL15 PEG_RX_4 T49

BF23 BK14 SMRCOMPN SMRCOMPN G44 T41

change Pin-BJ29 to DDR_A_MA14, RSVD28 SM_RCOMP# 24 LCD_B0- LVDSB_DATA#_0 PEG_RX_5

BG23 RSVD29 24 LCD_B1- B47 LVDSB_DATA#_1 PEG_RX_6 W45

1

change Pin-BE24 to DDR_B_MA14. BC23 RSVD30 SM_RCOMP_VOH BK31 SM_RCOMP_VOH

24 LCD_B2- B45 LVDSB_DATA#_2 PEG_RX_7 W41

BD24 BL31 SM_RCOMP_VOL AB50

RSVD31 SM_RCOMP_VOL R443 PEG_RX_8

15,16 DDR_A_MA14 BJ29 RSVD32 PEG_RX_9 Y48

BE24 AR49 V_DDR_MCH_REF 20/F E44 AC45

15,16 DDR_B_MA14 RSVD33 SM_VREF_0 24 LCD_B0+ LVDSB_DATA_0 PEG_RX_10

BH39 AW4 24 LCD_B1+ A47 AC41

2

RSVD34 SM_VREF_1 LVDSB_DATA_1 PEG_RX_11

AW20 RSVD35 24 LCD_B2+ A45 LVDSB_DATA_2 PEG_RX_12 AH47

+3.3V_RUN BK20 AG49

RSVD36 PEG_RX_13

C48 AH45

PCI-EXPRESS

R402 1 PM_EXTTS#0 RSVD37 PEG_RX_14

2 10K D47 RSVD38 DPLL_REF_CLK B42 MCH_DREFCLK 17 PEG_RX_15 AG42

R395 1 2 10K PM_EXTTS#1 B44 C42

RSVD39 DPLL_REF_CLK# MCH_DREFCLK# 17 DVO_RED#_C

C44 RSVD40 DPLL_REF_SSCLK H48 DREF_SSCLK 17 43 TV_CVBS E27 TVA_DAC PEG_TX#_0 N45

B A35 H47 G27 U39 DVO_GREEN#_C B

CLK

RSVD41 DPLL_REF_SSCLK# DREF_SSCLK# 17 43 TV_Y TVB_DAC PEG_TX#_1

B37 K27 U47 DVO_BLUE#_C

+1.05V_VCCP RSVD42 43 TV_C TVC_DAC PEG_TX#_2

B36 K44 N51 DVO_CLK#_C

RSVD43 PEG_CLK CLK_MCH_3GPLL 17 PEG_TX#_3

TV

R406 56_NC B34 K45 F27 R50

RSVD44 PEG_CLK# CLK_MCH_3GPLL# 17 TVA_RTN PEG_TX#_4

2

1 2 THERMTRIP_MCH# C34 RSVD45 J27 TVB_RTN PEG_TX#_5 T42

R387 R381 R398 L27 Y43

150/F 150/F 150/F TVC_RTN PEG_TX#_6

PEG_TX#_7 W46

Layout Note: DMI_RXN_0 AN47 DMI_MRX_ITX_N0 12 M35 TV_DCONSEL_0 PEG_TX#_8 W38

Location of all MCH_CFG strap AJ38 DMI_MRX_ITX_N1 12 P33 AD39

1

DMI_RXN_1 TV_DCONSEL_1 PEG_TX#_9

DMI_RXN_2 AN42 DMI_MRX_ITX_N2 12 PEG_TX#_10 AC46

resistors needs to be close to AN46 AC49

DMI_RXN_3 DMI_MRX_ITX_N3 12 PEG_TX#_11

minmize stub. PEG_TX#_12 AC42

DMI_RXP_0 AM47 DMI_MRX_ITX_P0 12 PEG_TX#_13 AH39

3,17 CPU_MCH_BSEL0 P27 CFG_0 DMI_RXP_1 AJ39 DMI_MRX_ITX_P1 12 PEG_TX#_14 AE49

3,17 CPU_MCH_BSEL1 N27 CFG_1 DMI_RXP_2 AN41 DMI_MRX_ITX_P2 12 PEG_TX#_15 AH44

3,17 CPU_MCH_BSEL2 N24 CFG_2 DMI_RXP_3 AN45 DMI_MRX_ITX_P3 12

PAD T45 CFG3 C21 VGA_BLU H32 M45 DVO_RED_C

CFG_3 25,43 VGA_BLU CRT_BLUE PEG_TX_0

CFG4 C23 AJ46 G32 T38 DVO_GREEN_C

DMI

PAD T12 CFG_4 DMI_TXN_0 DMI_MTX_IRX_N0 12 CRT_BLUE# PEG_TX_1

R391 2 1 4.02K/F_NC CFG5 F23 AJ41 VGA_GRN K29 T46 DVO_BLUE_C

CFG_5 DMI_TXN_1 DMI_MTX_IRX_N1 12 25,43 VGA_GRN CRT_GREEN PEG_TX_2

PAD T56 CFG6 N23 AM40 J29 N50 DVO_CLK_C

CFG_6 DMI_TXN_2 DMI_MTX_IRX_N2 12 CRT_GREEN# PEG_TX_3

PAD T49 CFG7 G23 AM44 VGA_RED F29 R51

CFG_7 DMI_TXN_3 DMI_MTX_IRX_N3 12 25,43 VGA_RED CRT_RED PEG_TX_4

VGA

PAD T46 CFG8 J20 E29 U43

CFG_8 CRT_RED# PEG_TX_5

CFG

R382 2 1 4.02K/F_NC CFG9 C20 CFG_9 DMI_TXP_0 AJ47 DMI_MTX_IRX_P0 12 PEG_TX_6 W42

PAD T58 CFG10 R24 AJ42 Y47

CFG_10 DMI_TXP_1 DMI_MTX_IRX_P1 12 PEG_TX_7

PAD T48 CFG11 L23 AM39 K33 Y39

CFG_11 DMI_TXP_2 DMI_MTX_IRX_P2 12 25 G_CLK_DDC2 CRT_DDC_CLK PEG_TX_8

PAD T52 CFG12 J23 AM43 G35 AC38

CFG_12 DMI_TXP_3 DMI_MTX_IRX_P3 12 25 G_DAT_DDC2 CRT_DDC_DATA PEG_TX_9

PAD T50 CFG13 E23 R390 1 2 30/F F33 AD47

CFG_13 25 VGAHSYNC CRT_HSYNC PEG_TX_10

PAD T47 CFG14 E20 R379 1 2 1.3K/F C32 AC50

CFG15 CFG_14 +1.25V_RUN R384 1 CRT_TVO_IREF PEG_TX_11

PAD T54 K23 CFG_15 25 VGAVSYNC 2 30/F E33 CRT_VSYNC PEG_TX_12 AD43

C

R405 2 1 4.02K/F_NC CFG16 M20 CFG_16 PEG_TX_13 AG39 C

+3.3V_RUN

GRAPHICS VID

CFG17

PAD T57

T55 CFG18

M24

L32

CFG_17 Non-iAMT 1

PEG_TX_14 AE50

AH43

PAD CFG_18 PEG_TX_15

R403 2 1 4.02K/F_NC CFG19 N33 CFG_19

R416

R394 2 1 4.02K/F_NC CFG20 L35 1K/F

CFG_20 CRESTLINE_1p0

VGA_BLU

2

E35 T51 PAD MCH_CLVREF VGA_GRN UMA

GFX_VID_0 +3.3V_RUN VGA_RED

13 PM_BMBUSY# G41 PM_BM_BUSY# GFX_VID_1 A39 T11 PAD UMA

1

3,11,51 H_DPRSTP# L39 PM_DPRSTP# GFX_VID_2 C38 T10 PAD

2

2

PM_EXTTS#0 L36 B39 T8 PAD C508 R418 R365 1 2 10K LCTLA_CLK

15 PM_EXTTS#0 PM_EXT_TS#_0 GFX_VID_3

PM

PM_EXTTS#1 J36 E36 T9 PAD 0.1U/10V 392/F R366 1 2 10K LCTLB_DATA R396 R400 R393 Layout Note:

15 PM_EXTTS#1 PM_EXT_TS#_1 GFX_VR_EN R364 2.2K LCD_DDCCLK 150/F 150/F 150/F

AW49 2 1 Place 150 ohm

1

13,44 ICH_PWRGD PLTRST#_R PWROK R363 2.2K LCD_DDCDAT

AV20 2 1

2

THERMTRIP_MCH# N20 RSTIN# termination resistors

37 THERMTRIP_MCH#

1

THERMTRIP# close to GMCH.

13,51 DPRSLPVR 1 2 G36 DPRSLPVR

R389 0 AM49

CL_CLK CL_CLK0 13

CL_DATA AK50 CL_DATA0 13

BJ51 AT43 Low=DMIx2 DVO_RED#_C C475 1 2 0.1U/10V

ICH_CL_PWROK 13,31 SDVOB_RED- 18

ME

NC_1 CL_PWROK DVO_GREEN#_C C489 0.1U/10V

BK51 NC_2 CL_RST# AN49 ICH_CL_RST0# 13 CFG5 DMI X2 Select High=DMIx4(Default) 1 2 SDVOB_GREEN- 18

BK50 AM50 DVO_BLUE#_C C483 1 2 0.1U/10V

NC_3 CL_VREF SDVOB_BLUE- 18

BL50 MCH_CLVREF PCI Express Low= Reveise Lane DVO_CLK#_C C471 1 2 0.1U/10V

NC_4 SDVOB_CLK- 18

BL49 NC_5 CFG9 Graphic Lane High=Normal operation

BL3 DVO_RED_C C473 1 2 0.1U/10V

NC_6 SDVOB_RED+ 18

BL2 FSB Dynamic Low=Dynamic ODT Disable DVO_GREEN_C C486 1 2 0.1U/10V

NC_7 SDVOB_GREEN+ 18

NC

BK1 CFG16 ODT High=Dynamic ODT Enable(default). DVO_BLUE_C C480 1 2 0.1U/10V

NC_8 SDVOB_BLUE+ 18

BJ1 H35 DVO_CLK_C C469 1 2 0.1U/10V

NC_9 SDVO_CTRL_CLK SDVO_CTRLCLK 18 SDVOB_CLK+ 18

E1 NC_10 K36 SDVO_CTRLDATA 18 DMI Lane Low=Normal(default).

MISC

SDVO_CTRL_DATA

A5 NC_11 CLK_REQ# G39 CLK_3GPLLREQ# 17 CFG19 Reversal High=Lane Reversed DC Blocked Cap.

D C51 NC_12 ICH_SYNC# G40 MCH_ICH_SYNC# 13 D

B50 NC_13

Low=Only SDVO or PCIEx1 is

A50 NC_14

SDVO/PCIE operational (defaults)

A49 A37 CFG20

BK2

NC_15

NC_16

TEST_1

TEST_2 R32

Concurrent

Operation

High=SDVO and PCIEx1 are operating

simultaneously via PEG port

QUANTA

2

CRESTLINE_1p0

R419

1

0_NC

2

R407

20K

R378

0

Low=No SDVO Device Present

Title

COMPUTER

12 SB_NB_PCIE_RST# (default) Crestline (VGA,DMI)

SDVO_CRTL_DATA SDVO Present. High=SDVO Device Present

R422 0 R421 100

1

1 2 2 1 PLTRST#_R Size Document Number Rev

12,18,28,29,31,32,40 PLTRST# JM7 1A

Date: Wednesday, June 28, 2006 Sheet 6 of 57

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8

15 DDR_A_D[0..63] 15 DDR_B_D[0..63]

U9D U9E

DDR_A_D0 AR43 BB19 DDR_A_BS0 DDR_B_D0 AP49 AY17 DDR_B_BS0

SA_DQ_0 SA_BS_0 DDR_A_BS0 15,16 SB_DQ_0 SB_BS_0 DDR_B_BS0 15,16

DDR_A_D1 AW44 BK19 DDR_A_BS1 DDR_B_D1 AR51 BG18 DDR_B_BS1

A SA_DQ_1 SA_BS_1 DDR_A_BS1 15,16 SB_DQ_1 SB_BS_1 DDR_B_BS1 15,16 A

DDR_A_D2 BA45 BF29 DDR_A_BS2 DDR_B_D2 AW50 BG36 DDR_B_BS2

SA_DQ_2 SA_BS_2 DDR_A_BS2 15,16 SB_DQ_2 SB_BS_2 DDR_B_BS2 15,16

DDR_A_D3 AY46 DDR_B_D3 AW51

DDR_A_D4 SA_DQ_3 DDR_A_CAS# DDR_B_D4 SB_DQ_3 DDR_B_CAS#

AR41 SA_DQ_4 SA_CAS# BL17 DDR_A_CAS# 15,16 AN51 SB_DQ_4 SB_CAS# BE17 DDR_B_CAS# 15,16

DDR_A_D5 AR45 DDR_B_D5 AN50

SA_DQ_5 DDR_A_DM[0..7] 15 SB_DQ_5 DDR_B_DM[0..7] 15

DDR_A_D6 AT42 AT45 DDR_A_DM0 DDR_B_D6 AV50 AR50 DDR_B_DM0

DDR_A_D7 SA_DQ_6 SA_DM_0 DDR_A_DM1 DDR_B_D7 SB_DQ_6 SB_DM_0 DDR_B_DM1

AW47 SA_DQ_7 SA_DM_1 BD44 AV49 SB_DQ_7 SB_DM_1 BD49

DDR_A_D8 BB45 BD42 DDR_A_DM2 DDR_B_D8 BA50 BK45 DDR_B_DM2

DDR_A_D9 SA_DQ_8 SA_DM_2 DDR_A_DM3 DDR_B_D9 SB_DQ_8 SB_DM_2 DDR_B_DM3

BF48 SA_DQ_9 SA_DM_3 AW38 BB50 SB_DQ_9 SB_DM_3 BL39

DDR_A_D10 BG47 AW13 DDR_A_DM4 DDR_B_D10 BA49 BH12 DDR_B_DM4

DDR_A_D11 SA_DQ_10 SA_DM_4 DDR_A_DM5 DDR_B_D11 SB_DQ_10 SB_DM_4 DDR_B_DM5

BJ45 SA_DQ_11 SA_DM_5 BG8 BE50 SB_DQ_11 SB_DM_5 BJ7

DDR_A_D12 BB47 AY5 DDR_A_DM6 DDR_B_D12 BA51 BF3 DDR_B_DM6

DDR_A_D13 SA_DQ_12 SA_DM_6 DDR_A_DM7 DDR_B_D13 SB_DQ_12 SB_DM_6 DDR_B_DM7

BG50 SA_DQ_13 SA_DM_7 AN6 AY49 SB_DQ_13 SB_DM_7 AW2

DDR_A_D14 BH49 DDR_B_D14 BF50

SA_DQ_14 DDR_A_DQS[0..7] 15 SB_DQ_14 DDR_B_DQS[0..7] 15

DDR_A_D15 BE45 AT46 DDR_A_DQS0 DDR_B_D15 BF49 AT50 DDR_B_DQS0

SA_DQ_15 SA_DQS_0 SB_DQ_15 SB_DQS_0

A

DDR_A_D16 AW43 BE48 DDR_A_DQS1 DDR_B_D16 BJ50 BD50 DDR_B_DQS1

SA_DQ_16 SA_DQS_1 SB_DQ_16 SB_DQS_1

B

DDR_A_D17 BE44 BB43 DDR_A_DQS2 DDR_B_D17 BJ44 BK46 DDR_B_DQS2

DDR_A_D18 SA_DQ_17 SA_DQS_2 DDR_A_DQS3 DDR_B_D18 SB_DQ_17 SB_DQS_2 DDR_B_DQS3

BG42 SA_DQ_18 SA_DQS_3 BC37 BJ43 SB_DQ_18 SB_DQS_3 BK39

DDR_A_D19 BE40 BB16 DDR_A_DQS4 DDR_B_D19 BL43 BJ12 DDR_B_DQS4

DDR_A_D20 SA_DQ_19 SA_DQS_4 DDR_A_DQS5 DDR_B_D20 SB_DQ_19 SB_DQS_4 DDR_B_DQS5

BF44 BH6 BK47 BL7

MEMORY

DDR_A_D21 SA_DQ_20 SA_DQS_5 DDR_A_DQS6 DDR_B_D21 SB_DQ_20 SB_DQS_5 DDR_B_DQS6

BH45 BB2 BK49 BE2

MEMORY

DDR_A_D22 SA_DQ_21 SA_DQS_6 DDR_A_DQS7 DDR_B_D22 SB_DQ_21 SB_DQS_6 DDR_B_DQS7

BG40 SA_DQ_22 SA_DQS_7 AP3 DDR_A_DQS#[0..7] 15 BK43 SB_DQ_22 SB_DQS_7 AV2 DDR_B_DQS#[0..7] 15

DDR_A_D23 BF40 AT47 DDR_A_DQS#0 DDR_B_D23 BK42 AU50 DDR_B_DQS#0

DDR_A_D24 SA_DQ_23 SA_DQS#_0 DDR_A_DQS#1 DDR_B_D24 SB_DQ_23 SB_DQS#_0 DDR_B_DQS#1

AR40 SA_DQ_24 SA_DQS#_1 BD47 BJ41 SB_DQ_24 SB_DQS#_1 BC50

DDR_A_D25 AW40 BC41 DDR_A_DQS#2 DDR_B_D25 BL41 BL45 DDR_B_DQS#2

DDR_A_D26 SA_DQ_25 SA_DQS#_2 DDR_A_DQS#3 DDR_B_D26 SB_DQ_25 SB_DQS#_2 DDR_B_DQS#3

AT39 SA_DQ_26 SA_DQS#_3 BA37 BJ37 SB_DQ_26 SB_DQS#_3 BK38

DDR_A_D27 AW36 BA16 DDR_A_DQS#4 DDR_B_D27 BJ36 BK12 DDR_B_DQS#4

DDR_A_D28 SA_DQ_27 SA_DQS#_4 DDR_A_DQS#5 DDR_B_D28 SB_DQ_27 SB_DQS#_4 DDR_B_DQS#5

AW41 SA_DQ_28 SA_DQS#_5 BH7 BK41 SB_DQ_28 SB_DQS#_5 BK7

DDR_A_D29 AY41 BC1 DDR_A_DQS#6 DDR_B_D29 BJ40 BF2 DDR_B_DQS#6

DDR_A_D30 SA_DQ_29 SA_DQS#_6 DDR_A_DQS#7 DDR_B_D30 SB_DQ_29 SB_DQS#_6 DDR_B_DQS#7

AV38 SA_DQ_30 SA_DQS#_7 AP2 BL35 SB_DQ_30 SB_DQS#_7 AV3

B DDR_A_D31 AT38 DDR_B_D31 BK37 B

SA_DQ_31 DDR_A_MA[0..13] 15,16 SB_DQ_31 DDR_B_MA[0..13] 15,16

DDR_A_D32 AV13 BJ19 DDR_A_MA0 DDR_B_D32 BK13 BC18 DDR_B_MA0

DDR_A_D33 SA_DQ_32 SA_MA_0 DDR_A_MA1 DDR_B_D33 SB_DQ_32 SB_MA_0 DDR_B_MA1

AT13 BD20 BE11 BG28

SYSTEM

DDR_A_D34 SA_DQ_33 SA_MA_1 DDR_A_MA2 DDR_B_D34 SB_DQ_33 SB_MA_1 DDR_B_MA2

AW11 BK27 BK11 BG25

SYSTEM

DDR_A_D35 SA_DQ_34 SA_MA_2 DDR_A_MA3 DDR_B_D35 SB_DQ_34 SB_MA_2 DDR_B_MA3

AV11 SA_DQ_35 SA_MA_3 BH28 BC11 SB_DQ_35 SB_MA_3 AW17

DDR_A_D36 AU15 BL24 DDR_A_MA4 DDR_B_D36 BC13 BF25 DDR_B_MA4

DDR_A_D37 SA_DQ_36 SA_MA_4 DDR_A_MA5 DDR_B_D37 SB_DQ_36 SB_MA_4 DDR_B_MA5

AT11 SA_DQ_37 SA_MA_5 BK28 BE12 SB_DQ_37 SB_MA_5 BE25

DDR_A_D38 BA13 BJ27 DDR_A_MA6 DDR_B_D38 BC12 BA29 DDR_B_MA6

DDR_A_D39 SA_DQ_38 SA_MA_6 DDR_A_MA7 DDR_B_D39 SB_DQ_38 SB_MA_6 DDR_B_MA7

BA11 SA_DQ_39 SA_MA_7 BJ25 BG12 SB_DQ_39 SB_MA_7 BC28

DDR_A_D40 BE10 BL28 DDR_A_MA8 DDR_B_D40 BJ10 AY28 DDR_B_MA8

DDR_A_D41 SA_DQ_40 SA_MA_8 DDR_A_MA9 DDR_B_D41 SB_DQ_40 SB_MA_8 DDR_B_MA9

BD10 SA_DQ_41 SA_MA_9 BA28 BL9 SB_DQ_41 SB_MA_9 BD37

DDR_A_D42 BD8 BC19 DDR_A_MA10 DDR_B_D42 BK5 BG17 DDR_B_MA10

DDR_A_D43 SA_DQ_42 SA_MA_10 DDR_A_MA11 DDR_B_D43 SB_DQ_42 SB_MA_10 DDR_B_MA11

AY9 SA_DQ_43 SA_MA_11 BE28 BL5 SB_DQ_43 SB_MA_11 BE37

DDR_A_D44 BG10 BG30 DDR_A_MA12 DDR_B_D44 BK9 BA39 DDR_B_MA12

DDR_A_D45 SA_DQ_44 SA_MA_12 DDR_A_MA13 DDR_B_D45 SB_DQ_44 SB_MA_12 DDR_B_MA13

AW9 SA_DQ_45 SA_MA_13 BJ16 BK10 SB_DQ_45 SB_MA_13 BG13

DDR_A_D46 BD7 DDR_B_D46 BJ8

DDR

DDR_A_D47 SA_DQ_46 DDR_B_D47 SB_DQ_46 DDR_B_RAS#

BB9 BJ6 AV16

DDR

SA_DQ_47 SB_DQ_47 SB_RAS# DDR_B_RAS# 15,16

DDR_A_D48 BB5 BE18 DDR_A_RAS# DDR_B_D48 BF4 AY18 T60 PAD

SA_DQ_48 SA_RAS# DDR_A_RAS# 15,16 SB_DQ_48 SB_RCVEN#

DDR_A_D49 AY7 AY20 T59 PAD DDR_B_D49 BH5

DDR_A_D50 SA_DQ_49 SA_RCVEN# DDR_B_D50 SB_DQ_49 DDR_B_WE#

AT5 SA_DQ_50 BG1 SB_DQ_50 SB_WE# BC17 DDR_B_WE# 15,16

DDR_A_D51 AT7 BA19 DDR_A_WE# DDR_B_D51 BC2

SA_DQ_51 SA_WE# DDR_A_WE# 15,16 SB_DQ_51

DDR_A_D52 AY6 DDR_B_D52 BK3

DDR_A_D53 SA_DQ_52 DDR_B_D53 SB_DQ_52

BB7 SA_DQ_53 BE4 SB_DQ_53

DDR_A_D54 AR5 DDR_B_D54 BD3

DDR_A_D55 SA_DQ_54 DDR_B_D55 SB_DQ_54

AR8 SA_DQ_55 BJ2 SB_DQ_55

DDR_A_D56 AR9 DDR_B_D56 BA3

DDR_A_D57 SA_DQ_56 DDR_B_D57 SB_DQ_56

AN3 SA_DQ_57 BB3 SB_DQ_57

DDR_A_D58 AM8 DDR_B_D58 AR1

DDR_A_D59 SA_DQ_58 DDR_B_D59 SB_DQ_58

AN10 SA_DQ_59 AT3 SB_DQ_59

DDR_A_D60 AT9 DDR_B_D60 AY2

C

DDR_A_D61 SA_DQ_60 DDR_B_D61 SB_DQ_60 C

AN9 SA_DQ_61 AY3 SB_DQ_61

DDR_A_D62 AM9 DDR_B_D62 AU2

DDR_A_D63 SA_DQ_62 DDR_B_D63 SB_DQ_62

AN11 SA_DQ_63 AT2 SB_DQ_63

CRESTLINE_1p0 CRESTLINE_1p0

D D

QUANTA

Title

COMPUTER

Crestline (DDR2)

Size Document Number Rev

JM7 1A

Date: Wednesday, June 28, 2006 Sheet 7 of 57

1 2 3 4 5 6 7 8

5 4 3 2 1

+3.3V_RUN

+1.05V_VCCP U9G U9F

R368 10 D28

AT35 1 2 +VCC_GMCH_L 1 2 AB33

VCC_1 VCC_NCTF_1

AT34 VCC_2 VCC_AXG_NCTF_1 T17 AB36 VCC_NCTF_2

AH28 T18 CH751H-40HPT AB37

VCC_3 VCC_AXG_NCTF_2 VCC_NCTF_3

AC32 VCC_5 VCC_AXG_NCTF_3 T19 AC33 VCC_NCTF_4 VSS_NCTF_1 T27

AC31 VCC_4 VCC_AXG_NCTF_4 T21 AC35 VCC_NCTF_5 VSS_NCTF_2 T37

AK32 T22 AC36 U24

VCC CORE

VCC_6 VCC_AXG_NCTF_5 VCC_NCTF_6 VSS_NCTF_3

AJ31 VCC_7 VCC_AXG_NCTF_6 T23 AD35 VCC_NCTF_7 VSS_NCTF_4 U28

AJ28 T25 +1.05V_VCCP AD36 V31

VCC_8 VCC_AXG_NCTF_7 VCC_NCTF_8 VSS_NCTF_5

AH32 VCC_9 VCC_AXG_NCTF_8 U15 AF33 VCC_NCTF_9 VSS_NCTF_6 V35

D

AH31 VCC_10 VCC_AXG_NCTF_9 U16 AF36 VCC_NCTF_10 VSS_NCTF_7 AA19 D

AH29 VCC_11 VCC_AXG_NCTF_10 U17 AH33 VCC_NCTF_11 VSS_NCTF_8 AB17

AF32 VCC_12 VCC_AXG_NCTF_11 U19 AH35 VCC_NCTF_12 VSS_NCTF_9 AB35

VSS NCTF

VCC_AXG_NCTF_12 U20 AH36 VCC_NCTF_13 VSS_NCTF_10 AD19

1

U21 + AH37 AD37

VCC_AXG_NCTF_13 C447 C441 C490 C487 C497 VCC_NCTF_14 VSS_NCTF_11

VCC_AXG_NCTF_14 U23 AJ33 VCC_NCTF_15 VSS_NCTF_12 AF17

R30 U26 Layout Note: 220U/2.5V 22U/10V 0.22U/10V 0.22U/10V 0.1U/10V AJ35 AF35

2

VCC_13 VCC_AXG_NCTF_15 VCC_NCTF_16 VSS_NCTF_13

VCC_AXG_NCTF_16 V16 370 mils from edge. AK33 VCC_NCTF_17 VSS_NCTF_14 AK17

VCC_AXG_NCTF_17 V17 AK35 VCC_NCTF_18 VSS_NCTF_15 AM17

VCC_AXG_NCTF_18 V19 Layout Note: AK36 VCC_NCTF_19 VSS_NCTF_16 AM24

VCC_AXG_NCTF_19 V20 Inside GMCH cavity. AK37 VCC_NCTF_20 VSS_NCTF_17 AP26

VCC_AXG_NCTF_20 V21 AD33 VCC_NCTF_21 VSS_NCTF_18 AP28

VCC_AXG_NCTF_21 V23 AJ36 VCC_NCTF_22 VSS_NCTF_19 AR15

VCC_AXG_NCTF_22 V24 AM35 VCC_NCTF_23 VSS_NCTF_20 AR19

VCC NCTF

Y15 Layout Note: AL33 AR28

+1.8V_SUS

POWER VCC_AXG_NCTF_23

VCC_AXG_NCTF_24

VCC_AXG_NCTF_25

Y16

Y17

370 mils from edge.

+1.05V_VCCP AL35

AA33

VCC_NCTF_24

VCC_NCTF_25

VCC_NCTF_26

VSS_NCTF_21

AU32 VCC_SM_1 VCC_AXG_NCTF_26 Y19 AA35 VCC_NCTF_27

AU33 VCC_SM_2 VCC_AXG_NCTF_27 Y20 AA36 VCC_NCTF_28

AU35 VCC_SM_3 VCC_AXG_NCTF_28 Y21 AP35 VCC_NCTF_29

1

AV33 VCC_SM_4 VCC_AXG_NCTF_29 Y23 AP36 VCC_NCTF_30

AW33 Y24 + C118 + C126 + C133 + C144 AR35

VCC_SM_5 VCC_AXG_NCTF_30 220U/2.5V 220U/2.5V 220U/2.5V_NC 220U/2.5V_NC VCC_NCTF_31

AW35 VCC_SM_6 VCC_AXG_NCTF_31 Y26 AR36 VCC_NCTF_32

AY35 Y28 Y32

2

VCC_SM_7 VCC_AXG_NCTF_32 VCC_NCTF_33

BA32 Y29 Y33

BA33

BA35

VCC_SM_8

VCC_SM_9

VCC_SM_10

VCC_AXG_NCTF_33

VCC_AXG_NCTF_34

VCC_AXG_NCTF_35

AA16

AA17

Y35

Y36

VCC_NCTF_34

VCC_NCTF_35

VCC_NCTF_36

POWER

BB33 VCC_SM_11 VCC_AXG_NCTF_36 AB16 Y37 VCC_NCTF_37 VSS_SCB1 A3

BC32 AB19 T30 B2

VSS SCB

VCC_SM_12 VCC_AXG_NCTF_37 VCC_NCTF_38 VSS_SCB2

BC33 VCC_SM_13 VCC_AXG_NCTF_38 AC16 T34 VCC_NCTF_39 VSS_SCB3 C1

C BC35 VCC_SM_14 VCC_AXG_NCTF_39 AC17 T35 VCC_NCTF_40 VSS_SCB4 BL1 C

BD32 VCC_SM_15 VCC_AXG_NCTF_40 AC19 Layout Note: U29 VCC_NCTF_41 VSS_SCB5 BL51

BD35 AD15 +1.05V_VCCP U31 A51

VCC_SM_16 VCC_AXG_NCTF_41 Inside GMCH cavity for VCC_AXG. VCC_NCTF_42 VSS_SCB6

BE32 VCC_SM_17 VCC_AXG_NCTF_42 AD16 U32 VCC_NCTF_43

BE33 VCC_SM_18 VCC_AXG_NCTF_43 AD17 U33 VCC_NCTF_44

BE35 VCC_SM_19 VCC_AXG_NCTF_44 AF16 U35 VCC_NCTF_45

VCC GFX NCTF

BF33 AF19 U36

VCC SM

VCC_SM_20 VCC_AXG_NCTF_45 VCC_NCTF_46

1

BF34 VCC_SM_21 VCC_AXG_NCTF_46 AH15 V32 VCC_NCTF_47

BG32 AH16 C482 C488 C466 C494 C470 C492 V33

VCC_SM_22 VCC_AXG_NCTF_47 0.1U/10V 0.1U/10V 0.47U/10V 1U/10V 10U/6.3V 22U/4V VCC_NCTF_48

BG33 AH17 2 V36

2

VCC_SM_23 VCC_AXG_NCTF_48 VCC_NCTF_49 +1.05V_VCCP

BG35 VCC_SM_24 VCC_AXG_NCTF_49 AH19 V37 VCC_NCTF_50

BH32 VCC_SM_25 VCC_AXG_NCTF_50 AJ16

BH34 VCC_SM_26 VCC_AXG_NCTF_51 AJ17 VCC_AXM_1 AT33

BH35 AJ19 AT31

VCC AXM

VCC_SM_27 VCC_AXG_NCTF_52 VCC_AXM_2

BJ32 VCC_SM_28 VCC_AXG_NCTF_53 AK16 VCC_AXM_3 AK29

BJ33 VCC_SM_29 VCC_AXG_NCTF_54 AK19 VCC_AXM_4 AK24

BJ34 VCC_SM_30 VCC_AXG_NCTF_55 AL16 Layout Note: VCC_AXM_5 AK23

BK32 AL17 +1.05V_VCCP AL24 AJ26

VCC_SM_31 VCC_AXG_NCTF_56 Inside GMCH cavity. VCC_AXM_NCTF_1 VCC_AXM_6

BK33 VCC_SM_32 VCC_AXG_NCTF_57 AL19 AL26 VCC_AXM_NCTF_2 VCC_AXM_7 AJ23

BK34 VCC_SM_33 VCC_AXG_NCTF_58 AL20 AL28 VCC_AXM_NCTF_3

BK35 VCC_SM_34 VCC_AXG_NCTF_59 AL21 AM26 VCC_AXM_NCTF_4

BL33 VCC_SM_35 VCC_AXG_NCTF_60 AL23 AM28 VCC_AXM_NCTF_5

VCC AXM NCTF

AU30 VCC_SM_36 VCC_AXG_NCTF_61 AM15 AM29 VCC_AXM_NCTF_6

AM16 C499 C503 C506 AM31

VCC_AXG_NCTF_62 0.1U/10V 0.1U/10V 0.1U/10V VCC_AXM_NCTF_7

AM19 AM32

2

+1.05V_VCCP VCC_AXG_NCTF_63 VCC_AXM_NCTF_8

VCC_AXG_NCTF_64 AM20 AM33 VCC_AXM_NCTF_9

R20

VCC_AXG_NCTF_65 AM21

AM23

Non-iAMT AP29

AP31

VCC_AXM_NCTF_10

VCC_AXG_1 VCC_AXG_NCTF_66 VCC_AXM_NCTF_11

T14 VCC_AXG_2 VCC_AXG_NCTF_67 AP15 AP32 VCC_AXM_NCTF_12

B

W13 VCC_AXG_3 VCC_AXG_NCTF_68 AP16 AP33 VCC_AXM_NCTF_13 B

W14 VCC_AXG_4 VCC_AXG_NCTF_69 AP17 AL29 VCC_AXM_NCTF_14

Y12 VCC_AXG_5 VCC_AXG_NCTF_70 AP19 AL31 VCC_AXM_NCTF_15

1

AA20 VCC_AXG_6 VCC_AXG_NCTF_71 AP20 AL32 VCC_AXM_NCTF_16

AA23 AP21 C182 C511 C510 AR31

VCC_AXG_7 VCC_AXG_NCTF_72 22U/4V 0.22U/10V 0.22U/10V VCC_AXM_NCTF_17

AA26 AP23 AR32

2

VCC_AXG_8 VCC_AXG_NCTF_73 VCC_AXM_NCTF_18

AA28 VCC_AXG_9 VCC_AXG_NCTF_74 AP24 AR33 VCC_AXM_NCTF_19

AB21 VCC_AXG_10 VCC_AXG_NCTF_75 AR20

AB24 VCC_AXG_11 VCC_AXG_NCTF_76 AR21

AB29 VCC_AXG_12 VCC_AXG_NCTF_77 AR23 Layout Note:

AC20 VCC_AXG_13 VCC_AXG_NCTF_78 AR24 Place close to GMCH edge.

AC21 AR26 CRESTLINE_1p0

VCC_AXG_14 VCC_AXG_NCTF_79

VCC GFX

AC23 VCC_AXG_15 VCC_AXG_NCTF_80 V26

AC24 VCC_AXG_16 VCC_AXG_NCTF_81 V28

AC26 VCC_AXG_17 VCC_AXG_NCTF_82 V29

AC28 Y31 +1.8V_SUS

AC29

VCC_AXG_18 VCC_AXG_NCTF_83 VCC_SM

VCC_AXG_19

AD20 VCC_AXG_20

AD23 VCC_AXG_21

1

AD24 AW45 VCCSM_LF1

VCC SM LF

VCC_AXG_22 VCC_SM_LF1

1

AD28 BC39 VCCSM_LF2 +

VCC_AXG_23 VCC_SM_LF2 VCCSM_LF3 C230 C202 C544 C545

AF21 VCC_AXG_24 VCC_SM_LF3 BE39

AF26 BD17 VCCSM_LF4 0.1U/10V 330U/6.3V 22U/4V 22U/4V

2

VCC_AXG_25 VCC_SM_LF4 VCCSM_LF5

AA31 VCC_AXG_26 VCC_SM_LF5 BD4

AH20 AW8 VCCSM_LF6

VCC_AXG_27 VCC_SM_LF6 VCCSM_LF7

AH21 VCC_AXG_28 VCC_SM_LF7 AT6 Layout Note:

AH23 VCC_AXG_29 Place C901 where LVDS

1

AH24 VCC_AXG_30 and DDR2 taps. Layout Note:

AH26 C512 C509 C530 C532 C529 C528 C519 Place on the edge.

VCC_AXG_31 0.1U/10V 0.1U/10V 0.22U/10V 0.22U/10V 0.47U/10V 1U/10V 1U/10V

AD31

2

VCC_AXG_32

A AJ20 VCC_AXG_33

A

AN14 VCC_AXG_34

QUANTA

CRESTLINE_1p0 Title

COMPUTER

Crestline (VCC,NCTF)

Size Document Number Rev

JM7 1A

Date: Wednesday, June 28, 2006 Sheet 8 of 57

5 4 3 2 1

5 4 3 2 1

+3.3V_RUN

U9H

+1.05V_VCCP +1.05V_VCCP

FB_180ohm+-25%_100mHz_1500mA_0.09ohm DC VCC_HV

J32 VCCSYNC VTT_1 U13

2

L29 R87 0 U12

+VCCA_CRTDAC +VCCA_CRTDAC_R +VCCA_CRTDAC_R VTT_2

+3.3V_RUN 1 2 1 2 A33 VCCA_CRT_DAC_1 VTT_3 U11

1

BLM18PG181SN1 B33 U9 D27

VCCA_CRT_DAC_2 VTT_4

1

3 1 U8 C477 C474 CH751H-40HPT_NC

CRT

VTT_5

1

C690 U7 2.2U/6.3V 4.7U/6.3V

1

C107 C112 0.1U/10V +VCC_TVBG_R VTT_6 +VCC_HV_L

A30 U5

2

0.1U/10V 22nF/3P_NC VCCA_DAC_BG VTT_7

U3

2

VTT_8

1

B32 VSSA_DAC_BG VTT_9 U2

U1 +1.05V_VCCP

D VTT_10 R367 D

VTT_11 T13 Place on the edge.

+VCCA_DPLLA B49 T11 10_NC

VCCA_DPLLA VTT_12

VTT

T10

2

+VCCA_DPLLB VTT_13

H49 VCCA_DPLLB VTT_14 T9

Non-iAMT 45mA MAx. 40mA MAx. T7

PLL

VTT_15

1

+VCCA_HPLL

FB_120ohm+-25%_100mHz +1.25V_RUN

10uH+-20%_100mA

AL2 VCCA_HPLL VTT_16 T6

T5 C476 C479 + C154 Non-

+1.25V_RUN VTT_17

_200mA_0.2ohm DC

L48 +VCCA_MPLL AM2 T3 0.47U/6.3V 4.7U/6.3V 220U/4V iAMT +3.3V_RUN

2

+VCCA_DPLLA C115 VCCA_MPLL VTT_18

2 1 T2

2

L50 10uH/100MA 1000P/50V VTT_19

R3

A LVDS

VTT_20

1

2 1 +VCCA_HPLL 2 1 +VCC_TX_LVDS A41 R2 +1.25V_RUN

VCCA_LVDS VTT_21

1

BLM11A121S + C464 C459 R1 +1.25V_RUN

470U/4V 0.1U/10V VTT_22

B41 VSSA_LVDS

Place on the edge. PJP31

1

+3.3V_RUN

2

C161 C498 AT23 +VCC_AXD_L 1 2+VCC_AXD_R 2 1

22U/10V 0.1U/10V VCC_AXD_1 L54 0

AU28

2

VCC_AXD_2

K50 VCCA_PEG_BG VCC_AXD_3 AU24 Reserved L81 pad for

1

L30 AT29

A PEG

VCC_AXD_4 inductor.

AXD

L51 2 1 +VCCA_DPLLB K49 AT25 C517 C198

BLM11A121S 10uH/100MA VSSA_PEG_BG VCC_AXD_5 1U/10V 22U/10V

AT30

2

VCC_AXD_6

1

2 1 +VCCA_MPLL C468 Place caps close

1

R420 0.1Caps should be + C128 C130 0.1U/10V +VCCA_PEG_PLL U51 AR29 to VCC_AXD.

VCCA_PEG_PLL VCC_AXD_NCTF

1

0.5/F/0603 placed 200 mils 470U/4V 0.1U/10V

2

1 2 C451 C453

2

with in its pins.

1

AW18 B23 +1.25V_RUN 1U/10V 10U/6.3V

2

+VCCA_MPLL_L C507 VCCA_SM_1 VCC_AXF_1

AV19 B21

AXF

VCCA_SM_2

POWER VCC_AXF_2

1

0.1U/10V AU19 A21

2

C167 VCCA_SM_3 VCC_AXF_3

AU18 VCCA_SM_4

22U/10V AU17 AJ50 +1.25V_RUN

PJP29

2

VCCA_SM_5 VCC_DMI

C Place caps close C

A SM

1

+1.25V_RUN 1 2 +VCCA_SM AT22 to VCC_AXF

VCCA_SM_7 +VCC_SM_CK C502

AT21 BK24

SM CK

VCCA_SM_8 VCC_SM_CK_1

1

AT19 BK23 0.1U/10V

2

VCCA_SM_9 VCC_SM_CK_2

2

1

+ C175 C505 C518 C526 C504 AT18 BJ24 Place PJP62 for

100U/6.3V 4.7U/6.3V 22U/4V 22U/4V 1U/10V VCCA_SM_10 VCC_SM_CK_3

AT17 VCCA_SM_11 VCC_SM_CK_4 BJ23 +1.8V_SUS +1.8V_SUS

Non-iAMT AR17

2

2

VCCA_SM_NCTF_1

AR16 VCCA_SM_NCTF_2 R102 0/1206 PJP8

A43 +VCC_TX_LVDS 1 2 +VCC_TX_LVDS_R 2 1

A CK

PJP30 VCC_TX_LVDS

BC29 VCCA_SM_CK_1

1

1 2 +VCCA_SM_CK BB29 +3.3V_RUN For EMI +1.8V_RUN

+1.25V_RUN VCCA_SM_CK_2

1

C40 + fine tune. PJP10

+VCC_TVDACA_R VCC_HV_1 C116 C121

C25 B40 2 1

HV

VCCA_TVA_DAC_1 VCC_HV_2

1

C533 C520 C523 1 C535 B25 1000P/50V 220U/4V

2

VCCA_TVA_DAC_2

1

22U/4V 1U/10V 1U/10V 0.1U/10V +VCC_TVDACB_R C27 VCCA_TVB_DAC_1 C460

B27 AD51

TV

2

+1.25V_RUN +VCC_TVDACC_R VCCA_TVB_DAC_2 VCC_PEG_1 0.1U/10V +VCC_PEG +1.05V_VCCP

B28 W50

2

L49 VCCA_TVC_DAC_1 VCC_PEG_2

A28 VCCA_TVC_DAC_2 VCC_PEG_3 W51

PEG

1 2 +VCCA_PEG_PLL V49 R127 0/1206

D TV/CRT

BLM21PG221SN1D VCC_PEG_4

VCC_PEG_5 V50 1 2

1

+VCCD_TVDAC_R M32 VCCD_CRT

1

L29 VCCD_TVDAC For EMI

1

FB_220ohm+-25%_100MHz R417 +VCC_RXR_DMI

Non-iAMT AH50 + fine tune.

DMI

1/F/0603 +1.25V_RUN +VCCQ_TVDAC_R VCC_RXR_DMI_1 C146 C147

_2A_0.1ohm DC Place PJP54 for N28 VCCD_QDAC VCC_RXR_DMI_2 AH51

1

+1.8V_SUS 220U/4V 10U/6.3V

1 2

2

C485 AN2

0.1U/10V VCCD_HPLL +VTTLF1 +1.05V_VCCP

A7

VTTLF

2

C496 +VCCA_PEG_PLL VTTLF1 +VTTLF2

U48 VCCD_PEG_PLL VTTLF2 F2

10U/6.3V PJP9 AH1 +VTTLF3 R134 0/1206

LVDS

2

VTTLF3

1

B B

+1.8V_SUS 1 2 +VCCD_LVDS J41 1 2

C180 C484 VCCD_LVDS_1

H42 VCCD_LVDS_2

1

0.1U/10V 0.1U/10V PJP11 For EMI

2

1

+1.8V_RUN 1 2 + fine tune.

1

C166 C156

C137 C138 CRESTLINE_1p0 220U/4V 10U/6.3V

2

FB_180ohm+-25%_100mHz_1500mA_0.09ohm DC 1U/10V 10U/6.3V_NC

2

L28 R83 0

+3.3V_RUN 1 2 +VCC_TVDACA 1 2 +VCC_TVDACA_R +VTTLF1

BLM18PG181SN1 +VTTLF2

1 3 +VTTLF3

1

22nF & 0.1uF for

1

1

C102 C103 C108 +1.8V_SUS

VCC_TVDACA:C_R should

2

10U/6.3V 0.1U/10V 22nF/3P_NC C495 C456 C455 R449 0/1206

2

be placed with in 250 0.47U/10V 0.47U/10V 0.47U/10V +VCC_SM_CK 1 2

2

2

mils from Crestline.

1

For EMI

R86 0 R79 0.03/F R84 0 R436

fine tune.

1

+VCC_TVBG_R 2 1 +VCC_TVBG 2 1 +VCC_TVDACB 1 2 +VCC_TVDACB_R 1/F/0603

C199 C534

1 2

3 1 1 3 +1.5V_RUN 22U/10V 0.1U/10V +VCC_SM_CK_L

2

1

R354 0

C111 C106 C104 C109 1 2 +VCCD_TVDAC_R C540

2

22nF/3P_NC 0.1U/10V 0.1U/10V 22nF/3P_NC 10U/6.3V

2

2

1

1 3

C444 +VCCQ_TVDAC_R

0.1U/10V C442

2

A 22nF/3P_NC A

R85 0

+3.3V_RUN +VCC_TVDACC 1 2 +VCC_TVDACC_R L47 R359 0

+1.5V_RUN 1 2 +VCCQ_TVDAC 1 2

D8 R78 10_NC 1 3 BLM18PG181SN1 QUANTA

1

2 1 +VCC_TVDAC_L 1 2 1 3

C105 C110 C448

FB_180ohm+-25%_

COMPUTER

2

CH751H-40HPT_NC 0.1U/10V 22nF/3P_NC 0.1U/10V C449

100mHz_1500mA_

2

TV DAC Voltage Follower Circuit -700 mV. 22nF/3P_NC Title

0.09ohm DC Crestline (POWER)

Size Document Number Rev

JM7 1A

Date: Wednesday, June 28, 2006 Sheet 9 of 57

5 4 3 2 1

5 4 3 2 1

U9I U9J

C46 VSS_199 VSS_287 W11

A13 VSS_1 VSS_100 AW24 C50 VSS_200 VSS_288 W39

A15 VSS_2 VSS_101 AW29 C7 VSS_201 VSS_289 W43

A17 VSS_3 VSS_102 AW32 D13 VSS_202 VSS_290 W47

A24 VSS_4 VSS_103 AW5 D24 VSS_203 VSS_291 W5

AA21 VSS_5 VSS_104 AW7 D3 VSS_204 VSS_292 W7

AA24 VSS_6 VSS_105 AY10 D32 VSS_205 VSS_293 Y13

AA29 VSS_7 VSS_106 AY24 D39 VSS_206 VSS_294 Y2

D

AB20 VSS_8 VSS_107 AY37 D45 VSS_207 VSS_295 Y41 D

AB23 VSS_9 VSS_108 AY42 D49 VSS_208 VSS_296 Y45

AB26 VSS_10 VSS_109 AY43 E10 VSS_209 VSS_297 Y49

AB28 VSS_11 VSS_110 AY45 E16 VSS_210 VSS_298 Y5

AB31 VSS_12 VSS_111 AY47 E24 VSS_211 VSS_299 Y50

AC10 VSS_13 VSS_112 AY50 E28 VSS_212 VSS_300 Y11

AC13 VSS_14 VSS_113 B10 E32 VSS_213 VSS_301 P29

AC3 VSS_15 VSS_114 B20 E47 VSS_214 VSS_302 T29

AC39 VSS_16 VSS_115 B24 F19 VSS_215 VSS_303 T31

AC43 VSS_17 VSS_116 B29 F36 VSS_216 VSS_304 T33

AC47 VSS_18 VSS_117 B30 F4 VSS_217 VSS_305 R28

AD1 VSS_19 VSS_118 B35 F40 VSS_218

AD21 VSS_20 VSS_119 B38 F50 VSS_219

AD26 VSS_21 VSS_120 B43 G1 VSS_220

AD29 VSS_22 VSS_121 B46 G13 VSS_221 VSS_306 AA32

AD3 VSS_23 VSS_122 B5 G16 VSS_222 VSS_307 AB32

AD41 VSS_24 VSS_123 B8 G19 VSS_223 VSS_308 AD32

AD45 VSS_25 VSS_124 BA1 G24 VSS_224 VSS_309 AF28

AD49 VSS_26 VSS_125 BA17 G28 VSS_225 VSS_310 AF29

AD5 VSS_27 VSS_126 BA18 G29 VSS_226 VSS_311 AT27

AD50 VSS_28 VSS_127 BA2 G33 VSS_227 VSS_312 AV25

AD8 VSS_29 VSS_128 BA24 G42 VSS_228 VSS_313 H50

AE10 VSS_30 VSS_129 BB12 G45 VSS_229

AE14 VSS_31 VSS_130 BB25 G48 VSS_230

AE6 VSS_32 VSS_131 BB40 G8 VSS_231

AF20 BB44 H24

AF23

AF24

VSS_33

VSS_34

VSS_35

VSS VSS_132

VSS_133

VSS_134

BB49

BB8

H28

H4

VSS_232

VSS_233

VSS_234

AF31 VSS_36 VSS_135 BC16 H45 VSS_235

AG2 VSS_37 VSS_136 BC24 J11 VSS_236

C AG38 VSS_38 VSS_137 BC25 J16 VSS_237

C

AG43 VSS_39 VSS_138 BC36 J2 VSS_238

AG47 VSS_40 VSS_139 BC40 J24 VSS_239

AG50 VSS_41 VSS_140 BC51 J28 VSS_240

AH3 BD13 J33

AH40

AH41

VSS_42

VSS_43

VSS_44

VSS_141

VSS_142

VSS_143

BD2

BD28

J35

J39

VSS_241

VSS_242

VSS_243

VSS

AH7 VSS_45 VSS_144 BD45

AH9 VSS_46 VSS_145 BD48 K12 VSS_245

AJ11 VSS_47 VSS_146 BD5 K47 VSS_246

AJ13 VSS_48 VSS_147 BE1 K8 VSS_247

AJ21 VSS_49 VSS_148 BE19 L1 VSS_248

AJ24 VSS_50 VSS_149 BE23 L17 VSS_249

AJ29 VSS_51 VSS_150 BE30 L20 VSS_250

AJ32 VSS_52 VSS_151 BE42 L24 VSS_251

AJ43 VSS_53 VSS_152 BE51 L28 VSS_252

AJ45 VSS_54 VSS_153 BE8 L3 VSS_253

AJ49 VSS_55 VSS_154 BF12 L33 VSS_254

AK20 VSS_56 VSS_155 BF16 L49 VSS_255

AK21 VSS_57 VSS_156 BF36 M28 VSS_256

AK26 VSS_58 VSS_157 BG19 M42 VSS_257

AK28 VSS_59 VSS_158 BG2 M46 VSS_258

AK31 VSS_60 VSS_159 BG24 M49 VSS_259

AK51 VSS_61 VSS_160 BG29 M5 VSS_260

AL1 VSS_62 VSS_161 BG39 M50 VSS_261

AM11 VSS_63 VSS_162 BG48 M9 VSS_262

AM13 VSS_64 VSS_163 BG5 N11 VSS_263

AM3 VSS_65 VSS_164 BG51 N14 VSS_264

AM4 VSS_66 VSS_165 BH17 N17 VSS_265

B

AM41 VSS_67 VSS_166 BH30 N29 VSS_266 B

AM45 VSS_68 VSS_167 BH44 N32 VSS_267

AN1 VSS_69 VSS_168 BH46 N36 VSS_268

AN38 VSS_70 VSS_169 BH8 N39 VSS_269

AN39 VSS_71 VSS_170 BJ11 N44 VSS_270

AN43 VSS_72 VSS_171 BJ13 N49 VSS_271

AN5 VSS_73 VSS_172 BJ38 N7 VSS_272

AN7 VSS_74 VSS_173 BJ4 P19 VSS_273

AP4 VSS_75 VSS_174 BJ42 P2 VSS_274

AP48 VSS_76 VSS_175 BJ46 P23 VSS_275

AP50 VSS_77 VSS_176 BK15 P3 VSS_276

AR11 VSS_78 VSS_177 BK17 P50 VSS_277

AR2 VSS_79 VSS_178 BK25 R49 VSS_278

AR39 VSS_80 VSS_179 BK29 T39 VSS_279

AR44 VSS_81 VSS_180 BK36 T43 VSS_280

AR47 VSS_82 VSS_181 BK40 T47 VSS_281

AR7 VSS_83 VSS_182 BK44 U41 VSS_282

AT10 VSS_84 VSS_183 BK6 U45 VSS_283

AT14 VSS_85 VSS_184 BK8 U50 VSS_284

AT41 VSS_86 VSS_185 BL11 V2 VSS_285

AT49 VSS_87 VSS_186 BL13 V3 VSS_286

AU1 VSS_88 VSS_187 BL19

AU23 VSS_89 VSS_188 BL22

AU29 BL37 CRESTLINE_1p0

VSS_90 VSS_189

AU3 VSS_91 VSS_190 BL47

AU36 VSS_92 VSS_191 C12

AU49 VSS_93 VSS_192 C16

AU51 VSS_94 VSS_193 C19

AV39 VSS_95 VSS_194 C28

AV48 VSS_96 VSS_195 C29

A AW1 VSS_97 VSS_196 C33 A

AW12 VSS_98 VSS_197 C36

AW16 VSS_99 VSS_198 C41

CRESTLINE_1p0

QUANTA

Title

COMPUTER

Crestline (VSS)

Size Document Number Rev

JM7 1A

Date: Wednesday, June 28, 2006 Sheet 10 of 57

5 4 3 2 1

1 2 3 4 5 6 7 8

32.768KHZ R515 10M +RTC_CELL +RTC_CELL

2 1

1

W2

R514 0 R520 R550

ICH_RTCX1 1 4 1 2 ICH_RTCX2 332K/F 332K/F

2

2 3 ICH_INTVRMEN ICH_LAN100_SLP

1

C618 32.768KHZ C625

A A

15P/50V 15P/50V

2

R522 R539

0_NC 0_NC

2

+RTC_CELL ICH8M Internal VR Enable Strap ICH8M LAN100 SLP Strap

(Internal VR for VccSus1.05, VccSus1.5, VccCL1.5) (Internal VR for VccLAN1.05 and VccCL1.05)

Low = Internal VR Disabled Low = Internal VR Disabled

2

ICH_INTVRMEN High = Internal VR Enabled(Default) ICH_LAN100_SLP High = Internal VR Enabled(Default)

R534 R527 +1.05V_VCCP

1M 20K

U18A

2

1

ICH_RTCRST# ICH_RTCX1 AG25 E5

RTCX1 FWH0/LAD0 LPC_LAD0 31,32,40

2

ICH_INTRUDER# ICH_RTCX2 AF24 F5

RTCX2 FWH1/LAD1 LPC_LAD1 31,32,40

G8 R519 R518 R528

FWH2/LAD2 LPC_LAD2 31,32,40

1

ICH_RTCRST# AF23 F6 56_NC 56_NC 56

RTCRST# FWH3/LAD3 LPC_LAD3 31,32,40

C638

LPC

RTC

1U/10V ICH_INTRUDER# AD22 C4 LPC_LFRAME# 31,32,40

2

1

INTRUDER# FWH4/LFRAME# H_DPRSTP#

ICH_INTVRMEN AF25 G9 H_DPSLP#

INTVRMEN LDRQ0# LPC_LDRQ0# 32

ICH_LAN100_SLP AD21 E6 H_FERR#

LAN100_SLP LDRQ1#/GPIO23 LPC_LDRQ1# 32

T25 PAD GLAN_CLK B24 AF13 SIO_A20GATE

GLAN_CLK A20GATE SIO_A20GATE 31

A20M# AG26 H_A20M# 3

D22 LAN_RSTSYNC

Reserved for AF26 H_DPRSTP# +3.3V_RUN

DPRSTP# H_DPRSTP# 3,6,51

B

Intel Nineveh T30 PAD LAN_RXD0 C21 AE26 H_DPSLP# B

LAN / GLAN

LAN_RXD0 DPSLP# H_DPSLP# 3

T28 PAD LAN_RXD1 B21

design. LAN_RXD2 LAN_RXD1 H_FERR#

T89 PAD C22 LAN_RXD2 FERR# AD24 H_FERR# 3

2

T90 PAD LAN_TXD0

T92 PAD LAN_TXD1 D21 AG29 R566 R558

LAN_TXD2 LAN_TXD0 CPUPWRGD/GPIO49 H_PWRGOOD 3 10K 10K

T98 PAD E20 LAN_TXD1

C20 LAN_TXD2 IGNNE# AF27 H_IGNNE# 3

CPU

1

T29 PAD AH21 AE24 SIO_A20GATE

GLAN_DOCK#/GPIO13 INIT# H_INIT# 3

R551 1 2 33 ACZ_BIT_CLK AC20 SIO_RCIN#

30 ICH_AZ_MDC_BITCLK INTR H_INTR 3

R552 1 2 33 R521 24.9/F D25 AH14 SIO_RCIN#

38 ICH_AZ_CODEC_BITCLK GLAN_COMPI RCIN# SIO_RCIN# 31

+1.5V_PCIE_ICH 1 2 GLAN_COMP C25 GLAN_COMPO

NMI AD23 H_NMI 3

2

ACZ_BIT_CLK AJ16 AG28

HDA_BIT_CLK SMI# H_SMI# 3 +1.05V_VCCP

C649 C646 ACZ_SYNC AJ15

27P/50V_NC 27P/50V_NC HDA_SYNC

AA24 H_STPCLK# 3

1

ACZ_RST# STPCLK#

AE14 HDA_RST#

2

AE27 THERMTRIP#_ICH

THRMTRIP# R517

38 ICH_AZ_CODEC_SDIN0 AJ17 HDA_SDIN0 PAD T88

R547 1 2 33 ACZ_SYNC AH17 AA23 56

30 ICH_AZ_MDC_SYNC 30 ICH_AZ_MDC_SDIN1

IHDA

R546 33 HDA_SDIN1 TP8 IDE_DD[0..15]

38 ICH_AZ_CODEC_SYNC 1 2 T31 PAD AH15 HDA_SDIN2 IDE_DD[0..15] 26

R556 1 2 33 ACZ_RST# T111PAD AD13 V1 IDE_DD0

30 ICH_AZ_MDC_RST#

1

R555 33 HDA_SDIN3 DD0 IDE_DD1 THERMTRIP#_ICH

38 ICH_AZ_CODEC_RST# 1 2 DD1 U2

R562 1 2 33 ACZ_SDOUT ACZ_SDOUT AE13 V3 IDE_DD2

30 ICH_AZ_MDC_SDOUT HDA_SDOUT DD2

R557 1 2 33 T1 IDE_DD3

38 ICH_AZ_CODEC_SDOUT DD3

AE10 V4 IDE_DD4

HDA_DOCK_EN#/GPIO33 DD4 IDE_DD5

AG14 HDA_DOCK_RST#/GPIO34 DD5 T5

Place all series terms close to ICH8 except for SDIN input AB2 IDE_DD6

SATA_ACT#_R DD6 IDE_DD7

lines,which should be close to source.Placement of R292, R286, AF10 SATALED# DD7 T6

T3 IDE_DD8

C R283 & R289 should equal distance to the T split trace point as DD8 IDE_DD9 C

26 SATA_RX0- AF6 SATA0RXN DD9 R2

R291, R285, R284 & R290 respective. Basically,keep the same 26 SATA_RX0+ AF5 SATA0RXP DD10 T4 IDE_DD10

distance from T for all series termination resistors. SATA_TX0-_C AH5 V6 IDE_DD11

SATA_TX0+_C SATA0TXN DD11 IDE_DD12

AH6 SATA0TXP DD12 V5

U1 IDE_DD13

IDE

DD13 IDE_DD14

AG3 SATA1RXN DD14 V2

AG4 U6 IDE_DD15

C668 SATA_TX0-_C SATA1RXP DD15

26 SATA_TX0- 2 1 3900P/25V AJ4 SATA1TXN

C667 2 1 3900P/25V SATA_TX0+_C AJ3 AA4 IDE_DA0

SATA

26 SATA_TX0+ SATA1TXP DA0 IDE_DA0 26

AA1 IDE_DA1

DA1 IDE_DA1 26

AF2 AB3 IDE_DA2

SATA2RXN DA2 IDE_DA2 26

Distance between the ICH-8 M and cap on the "P" AF1 SATA2RXP

signal should be identical distance between the AE4 Y6 IDE_DCS1#

SATA2TXN DCS1# IDE_DCS1# 26

AE3 Y5 IDE_DCS3#

ICH-6 M and cap on the "N" signal for same pair. SATA2TXP DCS3# IDE_DCS3# 26

17 CLK_PCIE_SATA# AB7 SATA_CLKN DIOR# W4 IDE_DIOR# 26

17 CLK_PCIE_SATA AC6 SATA_CLKP DIOW# W3 IDE_DIOW# 26

DDACK# Y2 IDE_DDACK# 26

This circuit is Place within 500mils R585 24.9/F AG1 Y3

SATARBIAS# IDEIRQ IDE_IRQ 26

of ICH8 ball 2 1 SATABIAS AG2 Y1

only needed if the +3.3V_RUN SATARBIAS IORDY

W5

IDE_DIORDY 26

DDREQ IDE_DDREQ 26

platform has the

SNIFFER. ICH8M REV 1.0

1

R571

10K +3.3V_RUN

32,35 LED_MASK#

2

D 3 1 SATA_ACT#_R XOR Chain Entrance Strap R563 D

36 SATA_ACT#

1K_NC

ICH RSVD HDA SDOUT Description

Q68

QUANTA

1

2N7002W-7-F 0 0 RSVD ACZ_SDOUT

ICH_RSVD 13

R575 0_NC 0 1 Enter XOR Chain

COMPUTER

2

1 2

1 0 Normal Operation (Default) R542 Title

1K_NC ICH8-M (CPU,IDE,SATA,LPC,AC97,LAN)

1 1 Set PCIE port config bit 1

Size Document Number Rev

1

JM7 1A

Date: Wednesday, June 28, 2006 Sheet 11 of 57

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8

U18D

29 PCIE_RX1- P27 PERN1 DMI0RXN V27 DMI_MTX_IRX_N0 6

Place TX DC blocking caps close ICH8. P26 V26

Direct Media Interface

29 PCIE_RX1+ PERP1 DMI0RXP DMI_MTX_IRX_P0 6

PCIE_TXN1_C N29 U29

PETN1 DMI0TXN DMI_MRX_ITX_N0 6

C621 1 2 0.1U/10V PCIE_TXN1_C MiniWWAN PCIE_TXP1_C N28 U28

29 PCIE_TX1- PETP1 DMI0TXP DMI_MRX_ITX_P0 6

C622 1 2 0.1U/10V PCIE_TXP1_C

29 PCIE_TX1+

29 PCIE_RX2- M27 PERN2 DMI1RXN Y27 DMI_MTX_IRX_N1 6

29 PCIE_RX2+ M26 PERP2 DMI1RXP Y26 DMI_MTX_IRX_P1 6

C620 1 2 0.1U/10V PCIE_TXN2_C PCIE_TXN2_C L29 W29

29 PCIE_TX2- PETN2 DMI1TXN DMI_MRX_ITX_N1 6

C619 1 2 0.1U/10V PCIE_TXP2_C MiniWLAN PCIE_TXP2_C L28 W28

29 PCIE_TX2+ PETP2 DMI1TXP DMI_MRX_ITX_P1 6

K27 AB26

PCI-Express

PERN3 DMI2RXN DMI_MTX_IRX_N2 6

C623 1 2 0.1U/10V PCIE_TXN4_C K26 AB25

A 28 PCIE_TX4- PERP3 DMI2RXP DMI_MTX_IRX_P2 6 A

C624 1 2 0.1U/10V PCIE_TXP4_C J29 AA29

28 PCIE_TX4+ PETN3 DMI2TXN DMI_MRX_ITX_N2 6

J28 PETP3 DMI2TXP AA28 DMI_MRX_ITX_P2 6

C626 1 2 0.1U/10V GLAN_TXN_C H27 AD27

40 PCIE_TX6-/GLAN_TX- 28 PCIE_RX4- PERN4 DMI3RXN DMI_MTX_IRX_N3 6

C627 1 2 0.1U/10V GLAN_TXP_C H26 AD26

40 PCIE_TX6+/GLAN_TX+ 28 PCIE_RX4+ PERP4 DMI3RXP DMI_MTX_IRX_P3 6

PCIE_TXN4_C G29 AC29

PETN4 DMI3TXN DMI_MRX_ITX_N3 6

Express Card PCIE_TXP4_C G28 AC28

PETP4 DMI3TXP DMI_MRX_ITX_P3 6

F27 PERN5 DMI_CLKN T26 CLK_PCIE_ICH# 17

F26 PERP5 DMI_CLKP T25 CLK_PCIE_ICH 17

E29 PETN5

E28 Y23 R537 24.9/F

PETP5 DMI_ZCOMP DMI_COMP

DMI_IRCOMP Y24 2 1 +1.5V_PCIE_ICH Place within 500mils of ICH8

40 PCIE_RX6-/GLAN_RX- D27 PERN6/GLAN_RXN

40 PCIE_RX6+/GLAN_RX+ D26 PERP6/GLAN_RXP USBP0N G3 ICH_USBP0- 33 Ext Side Top

GLAN_TXN_C C29 G2 ICH_USBP0+ 33

GLAN_TXP_C PETN6/GLAN_TXN USBP0P

Giga Bit LOM C28 PETP6/GLAN_TXP USBP1N H5 ICH_USBP1- 33 Ext Side Bottom

USBP1P H4 ICH_USBP1+ 33

R530 1 2 15 ICH_EC_SPI_CLK_R C23 H2 ICH_USBP2- 33 Ext Back Bottom

31 ICH_EC_SPI_CLK SPI_CLK USBP2N

Layout Note: ICH_SPI_CS# B23 H1 ICH_USBP2+ 33

ICH_SPI_CS1#_R SPI_CS0# USBP2P

Place R288,R324 and R282 E22 J3 ICH_USBP3- 33 Power USB

SPI

SPI_CS1# USBP3N

USBP3P J2 ICH_USBP3+ 33

within 500 mils from ICH. R531 1 2 15 ICH_EC_SPI_DO_R D23 K5 ICH_USBP4- 28 Smart Card

31 ICH_EC_SPI_DO SPI_MOSI USBP4N

31 ICH_EC_SPI_DIN F21 SPI_MISO USBP4P K4 ICH_USBP4+ 28

K2 ICH_USBP5- 35 Biometric PCI Pullups +3.3V_RUN

USB_OC0_1# USBP5N RP43

33 USB_OC0_1# AJ19 OC0# USBP5P K1 ICH_USBP5+ 35

+3.3V_ALW

AG16 OC1#/GPIO40 USBP6N L3 ICH_USBP6- 28 Express Card 6 5

USB_OC2_3#

33 USB_OC2_3# AG15

AE15

OC2#/GPIO41 USB USBP6P L2

M5

ICH_USBP6+

ICH_USBP7-

28

35 Blue Tooth

7

8

4

3 PCI_STOP#

R526 OC4# OC3#/GPIO42 USBP7N PCI_FRAME#

B AF15 OC4#/GPIO43 USBP7P M4 ICH_USBP7+ 35 9 2 B

5

U17 15 OC5# AG17 M2 ICH_USBP8- 43 Dock 10 1 PCI_REQ1#

R523 15_NC ICH_SPI_CS# OC6# OC5#/GPIO29 USBP8N +3.3V_RUN

2 1 2 AD12 OC6#/GPIO30 USBP8P M1 ICH_USBP8+ 43

1 2 4 OC7# AJ18 N3 ICH_USBP9- 29 WWAN

34 SPI_CS0# OC7#/GPIO31 USBP9N 10P8R-8.2K

1 OC8# AD14 N2 ICH_USBP9+ 29 +3.3V_RUN

SIO_SPI_CS# 31 OC8# USBP9P RP45

R262 0 OC9# AH18

7SH08_NC OC9# PCI_DEVSEL#

1 2 USBRBIAS# F2 6 5

F3 USBRBIAS ICH_GPIO4_PIRQG# 7 4 PCI_SERR#

USBRBIAS ICH_GPIO3_PIRQF#

8 3

ICH8M REV 1.0 PCI_PIRQD# 9 2 ICH_GPIO2_PIRQE#

10 1 PCI_TRDY#

+3.3V_RUN

2

Non-iAMT Short F2 and F3 at the package

+3.3V_SUS R581

RP48 and keep length to less than 22.6/F

10P8R-8.2K

+3.3V_RUN

OC6# 6 5

500mils. Trace Impedance RP46

OC4# 7 4 OC8# should be 60ohms +/- 15%. ICH_GPIO5_PIRQH# 6 5

1

OC5# 8 3 USB_OC2_3# PCI_REQ0# 7 4 PCI_PIRQC#

OC7# 9 2 USB_OC0_1# PCI_PLOCK# 8 3 PCI_PIRQB#

10 1 OC9# PCI_PERR# 9 2 PCI_PIRQA#

+3.3V_SUS PCI_IRDY#

+3.3V_RUN 10 1

ICH_SPI_CS1#_R Boot BIOS Strap

10P8R-10K

PCI_GNT0#

10P8R-8.2K

GNT0# SPI_CS1#

2

LPC 11 No stuff No stuff

R578 R529 SB_WWAN_PCIE_RST# R543 2 1 20K

27,42 PCI_AD[0..31] U18B 1K 1K_NC PCI 10 No stuff Stuff SB_WLAN_PCIE_RST# R554 2 1 20K

PCI_AD0 D20 A4 PCI_REQ0# SB_LOM_PCIE_RST# R565 2 1 20K

PCI_REQ0# 43

1

PCI_AD1 AD0 REQ0# PCI_GNT0#

E19 AD1 PCI GNT0# D7 PCI_GNT0# 42 SPI 01 Stuff No stuff

PCI_AD2 D19 E18 PCI_REQ1#

C AD2 REQ1#/GPIO50 PCI_REQ1# 27 C

PCI_AD3 A20 C18 PCI_GNT1# BIOS should not enable the

AD3 GNT1#/GPIO51 PCI_GNT1# 27

PCI_AD4 D17 B19 SB_WWAN_PCIE_RST# internal GPIO pull up resistor.

AD4 REQ2#/GPIO52 SB_WWAN_PCIE_RST# 29

PCI_AD5 A21 F18 SB_WLAN_PCIE_RST#

AD5 GNT2#/GPIO53 SB_WLAN_PCIE_RST# 29

PCI_AD6 A19 A11 SB_LOM_PCIE_RST#

AD6 REQ3#/GPIO54 SB_LOM_PCIE_RST# 40

PCI_AD7 C19 C10 SB_NB_PCIE_RST#

AD7 GNT3#/GPIO55 SB_NB_PCIE_RST# 6

PCI_AD8 SB_NB_PCIE_RST#

PCI_AD9

A18

B16

AD8

C17

Non-iAMT +3.3V_SUS Add Buffers as needed for

AD9 C/BE0# PCI_C_BE0# 27,42

2

PCI_AD10 A12 E15 C691 Loading and fanout concerns.

AD10 C/BE1# PCI_C_BE1# 27,42

PCI_AD11 E16 F16 1 2

AD11 C/BE2# PCI_C_BE2# 27,42

PCI_AD12 A14 E17 R559

AD12 C/BE3# PCI_C_BE3# 27,42

PCI_AD13 G16 1K_NC 0.047U/10V

AD13

5

PCI_AD14 A15 C8 PCI_IRDY# U42

PCI_IRDY# 27,42

1

PCI_AD15 AD14 IRDY#

B6 AD15 PAR D9 PCI_PAR 27,42 2

PCI_AD16 C11 G6 PCI_RST#_G 4

AD16 PCIRST# PCI_RST# 27,28,42

PCI_AD17 A9 D16 PCI_DEVSEL# PCI_RST#_G 1

AD17 DEVSEL# PCI_DEVSEL# 27,42

PCI_AD18 D11 A7 PCI_PERR# A16 away override strap.

AD18 PERR# PCI_PERR# 27,42

PCI_AD19 B12 B7 PCI_PLOCK# 7SH32

AD19 PLOCK# PCI_PLOCK# 42

PCI_AD20 C12 F10 PCI_SERR# Low = A16 swap override enabled.

AD20 SERR# PCI_SERR# 27,42

PCI_AD21 D10 C16 PCI_STOP# SB_NB_PCIE_RST# High = Default. +3.3V_SUS

AD21 STOP# PCI_STOP# 27,42

PCI_AD22 C7 C9 PCI_TRDY# C614

AD22 TRDY# PCI_TRDY# 27,42

PCI_AD23 F13 A17 PCI_FRAME# 1 2

AD23 FRAME# PCI_FRAME# 27,42

PCI_AD24 E11

PCI_AD25 AD24

E13 AD25 PLTRST# AG24 PCI_PLTRST# CLK_PCI_ICH 0.047U/10V

5

PCI_AD26 E12 B10 CLK_PCI_ICH U39

AD26 PCICLK CLK_PCI_ICH 17

2

PCI_AD27 D8 G7 2

AD27 PME# ICH_PME# 32

PCI_AD28 A6 4

AD28 PLTRST# 6,18,28,29,31,32,40

PCI_AD29 E8 R564 PCI_PLTRST# 1

PCI_AD30 AD29 10_NC

D6 AD30

PCI_AD31 A3 7SH32

2 1

AD31

D DOCK REQ0 GNT0 PIRQA D

PCI_PIRQA# F9

Interrupt I/F F8 ICH_GPIO2_PIRQE# Cardbus or C655

42 PCI_PIRQA# PIRQA# PIRQE#/GPIO2

PCI_PIRQB# B5 G11 ICH_GPIO3_PIRQF# REQ1 GNT1 PIRQD 8.2P/16V_NC

T107 PAD Cardbus/1394

QUANTA

1

PCI_PIRQC# PIRQB# PIRQF#/GPIO3 ICH_GPIO4_PIRQG#

T109 PAD C5 PIRQC# PIRQG#/GPIO4 F12

PCI_PIRQD# A10 B3 ICH_GPIO5_PIRQH# PIRQC

27 PCI_PIRQD# PIRQD# PIRQH#/GPIO5

ICH8M REV 1.0

1394/MediaCard REQ2 GNT2 PIRQD Reserved for EMI.

Place resister and cap Title

COMPUTER

close to ICH. ICH8-M (USB,DMI,PCIE,PCI)

Size Document Number Rev

JM7 1A

Date: Wednesday, June 28, 2006 Sheet 12 of 57

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8

Place these close to ICH7.

CLK_ICH_48M

+3.3V_SUS Non-iAMT

1

A A

R541 2 1 10K RSV_ICH_CL_RST1# +3.3V_RUN R582

R545 2 1 10K ICH_RI# 10_NC

R532 2 1 10K SIO_EXT_SCI#

R548 2 1 1K ICH_PCIE_WAKE#

1 2

2

+3.3V_SUS

Non-iAMT

RP44 R568 C666

1 2 ICH_SMBDATA 8.2K 4.7P/50V_NC

2

3 4 ICH_SMBCLK

1

U18C

4P2R-2.2K ICH_SMBCLK AJ26 AJ12

28,29,40 ICH_SMBCLK ICH_SMBDATA SMBCLK SATA0GP/GPIO21

28,29,40 ICH_SMBDATA AD19 SMBDATA SATA1GP/GPIO19 AJ10

Clocks SATA

GPIO

RSV_ICH_CL_RST1# AG21 AF11 CLK_ICH_14M

SMB

T94 PAD LINKALERT# SATA2GP/GPIO36

T105 PAD AC17 SMLINK0 SATA3GP/GPIO37 AG11

1

T96 PAD AE19 SMLINK1

AG9 CLK_ICH_14M

+3.3V_RUN CLK14 CLK_ICH_14M 17

ICH_RI# AF17 G5 CLK_ICH_48M R574

RI# CLK48 CLK_ICH_48M 17

10_NC

T112 PAD RSV_LPCPD# F4 D3 ICH_SUSCLK

PAD T113

1 2

SUS_STAT#/LPCPD# SUSCLK

2

3,31 ITP_DBRESET# AD15 SYS_RESET#

SLP_S3# AG23 SIO_SLP_S3# 31

R570 AG12 AF21 C664

6 PM_BMBUSY# BMBUSY#/GPIO0 SLP_S4# PAD T84

8.2K AD18 4.7P/50V_NC

SIO_SLP_S5# 31

2

SIO_EXT_SCI# SLP_S5#

31 SIO_EXT_SCI# AG22

1

CLKRUN# SMBALERT#/GPIO11 RSV_SIO_S4_STATE#

S4_STATE#/GPIO26 AH27 PAD T24

17 H_STP_PCI# AE20

GPIO

STP_PCI#/GPIO15

1

AG18 AE23 ICH_PWRGD

SYS

17 H_STP_CPU# STP_CPU#/GPIO25 PWROK ICH_PWRGD 6,44

DPRSLPVR

DPRSLPVR 6,51

B R569 CLKRUN# AH11 AJ14 B

Power MGT

10_NC 27,31,32 CLKRUN# CLKRUN#/GPIO32 DPRSLPVR/GPIO16 R538 8.2K

ICH_PCIE_WAKE# AE17 AE21 ICH_BATLOW# 2 1 +3.3V_SUS

32 ICH_PCIE_WAKE#

2

IRQ_SERIRQ WAKE# BATLOW#

27,31,32,40 IRQ_SERIRQ AF12 SERIRQ

T106 PAD RSV_THRM# AC13 C2

THRM# PWRBTN# SIO_PWRBTN# 31

Option to " Disable " ICH_PWRGD R535 2 1 10K

clkrun. Pulling it down IMVP_PWRGD AJ20 AH20 RSV_ICH_LAN_RST#

31,44,51 IMVP_PWRGD VRMPWRGD LAN_RST# PAD T100

DPRSLPVR R560 1 2 100K

will keep the clks AJ22 AG27 ICH_RSMRST#

T26 PAD TP7 RSMRST# ICH_RSMRST# 31

running. ICH_RSMRST# R516 2 1 10K_NC

26 USB_IDE# AJ8 TACH1/GPIO1 CK_PWRGD E1 CLK_PWRGD 17

T33 PAD RSVD_GPIO6 AJ9 RSV_ICH_LAN_RST# R549 2 1 1M

SIO_EXT_WAKE# TACH2/GPIO6 ICH_CL_PWROK

32 SIO_EXT_WAKE# AH9 TACH3/GPIO7 CLPWROK E3 ICH_CL_PWROK 6,31

ICH_CL_PWROK R579 2 1 1M

31 SIO_EXT_SMI# AE16

AC19

GPIO8

AJ25 RSV_SIO_SLP_M# Non-iAMT

T91 PAD GPIO12 SLP_M# PAD T85

PCIE_MCARD1_DET# AG8

29 PCIE_MCARD1_DET# TACH0/GPIO17

USB_MCARD1_DET# AH12 F23

Controller Link

29 USB_MCARD1_DET# GPIO18 CL_CLK0 CL_CLK0 6

PCIE_MCARD2_DET# AE11 AE18 RSV_ICH_CL_CLK1

GPIO

29 PCIE_MCARD2_DET# GPIO20 CL_CLK1 PAD T104

USB_MCARD2_DET# AG10

29 USB_MCARD2_DET# SCLOCK/GPIO22

T83 PAD AH25 QRT_STATE0/GPIO27 CL_DATA0 F22 CL_DATA0 6

AD16 AF19 RSV_ICH_CL_DATA1

26 IDE_RST_MOD QRT_STATE1/GPIO28 CL_DATA1 PAD T97

17 SATA_CLKREQ# AG13 SATACLKREQ#/GPIO35

T114 PAD RSVD_GPIO38 AF9 D24 CL_VREF0

RSVD_GPIO39 SLOAD/GPIO38 CL_VREF0 CL_VREF1

T32 PAD AJ11 SDATAOUT0/GPIO39 CL_VREF1 AH23 PAD T87

T102 PAD RSVD_GPIO48 AD10 SDATAOUT1/GPIO48

CL_RST# AJ23 ICH_CL_RST0# 6

SPKR AD9

38 SPKR SPKR

AJ27

MISC

MEM_LED/GPIO24 PAD T22

R263 2 1 0 MCH_ICH_SYNC#_R AJ13 AJ24

6 MCH_ICH_SYNC# MCH_SYNC# ME_EC_ALERT/GPIO10 PAD T23

AF22 GPIO14

C EC_ME_ALERT/GPIO14 PAD T93 C

AJ21 AG19 RSV_WOL_EN

11 ICH_RSVD TP3 WOL_EN/GPIO9 PAD T95

ICH8M REV 1.0 R544 10K

+3.3V_RUN 2 1 +3.3V_SUS

UMA Package:RC0402-C +3.3V_RUN +3.3V_ALW

R261 2 1 2.2K_NC IMVP_PWRGD

Non-iAMT

Discrete Package: RC0402

2

+3.3V_RUN +3.3V_RUN R524 R536

Non-iAMT 3.24K/F 3.24K/F_NC

SMbus address D2

2

+3.3V_RUN

1

2

4

R561 2 1 10K RSV_THRM# R577 These are for CL_VREF0 CL_VREF1

R567 2 1 10K_NC MCH_ICH_SYNC#_R 1K_NC backdrive issue. RP42

R193 2 1 10K IRQ_SERIRQ 4P2R-2.2K

1

1

R267 2 1 10K RSVD_GPIO6 SPKR

2

1

R573 2 1 10K RSVD_GPIO38 C635 R525 C644 R533

1

3

R265 2 1 10K RSVD_GPIO39 Q41 0.1U/10V 453/F 0.1U/10V_NC 453/F_NC

R572 2 1 10K RSVD_GPIO48 No Reboot strap. 3 1

28,29,40 ICH_SMBDATA MEM_SDATA 15

2

R269 1 2 100K PCIE_MCARD1_DET#

2

R268 1 2 100K USB_MCARD1_DET# Low = Default.

R576 1 2 100K PCIE_MCARD2_DET# SPKR High = No Reboot. 2N7002W-7-F

R266 2 1 100K USB_MCARD2_DET#

+3.3V_RUN

2

D Q42 D

28,29,40 ICH_SMBCLK 3 1 MEM_SCLK 15

+3.3V_ALW

2N7002W-7-F QUANTA

R458 2 1 10K SIO_EXT_SMI#

Title

COMPUTER

ICH8-M (PM,GPIO,SMB,CL)

Size Document Number Rev

JM7 1A

Date: Wednesday, June 28, 2006 Sheet 13 of 57

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8

+RTC_CELL U18E

+1.05V_VCCP

A23 VSS[001] VSS[099] K7

2

A5 VSS[002] VSS[100] L1

2

C611 C633 C612 AA2 L13

1U/10V 0.1U/10V 0.1U/10V C648 C659 VSS[003] VSS[101]

AA7 L15

1

R264 100 U18F 0.1U/10V 0.1U/10V +1.05V_VCCP +1.5V_RUN VSS[004] VSS[102]

A25 L26

1

D33 VSS[005] VSS[103]

+5V_RUN 1 2 AD25 VCCRTC VCC1_05[01] A13 AB1 VSS[006] VSS[104] L27

VCC1_05[02] B13 1 R540 AB24 VSS[007] VSS[105] L4

D18 A16 C13 AC11 L5

+ICH_V5REF_RUN V5REF[1] VCC1_05[03] VSS[008] VSS[106]

+3.3V_RUN 2 1 T7 V5REF[2] VCC1_05[04] C14 3 1 2 AC14 VSS[009] VSS[107] M12

VCC1_05[05] D14 AC25 VSS[010] VSS[108] M13

2

CH751H-40HPT G4 E14 2 10/0805 AC26 M14

C303 V5REF_SUS VCC1_05[06] VSS[011] VSS[109]

A VCC1_05[07] F14 AC27 VSS[012] VSS[110] M15 A

0.1U/10V AA25 G14 BAT54C AD17 M16

1

VCC1_5_B[01] VCC1_05[08] VSS[013] VSS[111]

Non-iAMT R276 10

AA26

AA27

VCC1_5_B[02] VCC1_05[09] L11

L12

AD20

AD28

VSS[014] VSS[112] M17

M23

VCC1_5_B[03] VCC1_05[10] VSS[015] VSS[113]

+5V_SUS 1 2 AB27 VCC1_5_B[04] VCC1_05[11] L14 AD29 VSS[016] VSS[114] M28

AB28 VCC1_5_B[05] VCC1_05[12] L16 AD3 VSS[017] VSS[115] M29

D19 AB29 L17 AD4 M3

+ICH_V5REF_SUS VCC1_5_B[06] VCC1_05[13] VSS[018] VSS[116]

+3.3V_SUS 2 1 D28 VCC1_5_B[07] VCC1_05[14] L18 AD6 VSS[019] VSS[117] N1

D29 VCC1_5_B[08] VCC1_05[15] M11 AE1 VSS[020] VSS[118] N11

2

CORE

CH751H-40HPT E25 M18 AE12 N12

C312 VCC1_5_B[09] VCC1_05[16] VSS[021] VSS[119]

E26 VCC1_5_B[10] VCC1_05[17] P11 1uH+-20%_800mA AE2 VSS[022] VSS[120] N13

0.1U/10V E27 P18 AE22 N14

1

VCC1_5_B[11] VCC1_05[18] L59 +1.5V_RUN VSS[023] VSS[121]

F24 VCC1_5_B[12] VCC1_05[19] T11 AD1 VSS[024] VSS[122] N15

F25 T18 1uH_800MA R512 1 AE25 N16

VCC1_5_B[13] VCC1_05[20] +1.5V_DMIPLL VSS[025] VSS[123]

G24 VCC1_5_B[14] VCC1_05[21] U11 2 1+1.5V_DMIPLL_R 2 1 AE5 VSS[026] VSS[124] N17

H23 VCC1_5_B[15] VCC1_05[22] U18 AE6 VSS[027] VSS[125] N18

H24 VCC1_5_B[16] VCC1_05[23] V11 AE9 VSS[028] VSS[126] N26

2

J23 VCC1_5_B[17] VCC1_05[24] V12 AF14 VSS[029] VSS[127] N27

J24 V14 C630 C615 AF16 N4

VCC1_5_B[18] VCC1_05[25] 0.01U/25V 10U/6.3V VSS[030] VSS[128]

K24 V16 AF18 N5

1

VCC1_5_B[19] VCC1_05[26] VSS[031] VSS[129]

K25 VCC1_5_B[20] VCC1_05[27] V17 AF3 VSS[032] VSS[130] N6

+1.5V_RUN L23 V18 AF4 P12

VCC1_5_B[21] VCC1_05[28] VSS[033] VSS[131]

L24 VCC1_5_B[22] AG5 VSS[034] VSS[132] P13

VCCA3GP