Escolar Documentos

Profissional Documentos

Cultura Documentos

Map3511 828

Enviado por

riyad abdulhafeedTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Map3511 828

Enviado por

riyad abdulhafeedDireitos autorais:

Formatos disponíveis

rammer

Confidential

Datasheet Version 1.0

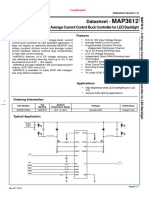

MAP3511 – Average Current Control Buck Controller for LED Backlight

Datasheet - MAP3511

Average Current Control Buck Controller for LED Backlight

General Description Features

MAP3511 is an average-mode current control buck 8.5V to 18V Input Voltage Range

controller for LED backlight application. It does not Average-Mode Current Control

require an additional dimming MOSFET and utilizes Programmable Constant off-time

constant off-time control and average current control Up to 3V Analog Dimming Input

feedback without external loop compensation or high- 1% CS Voltage Accuracy

side current sensing. Direct PWM Dimming Input

MAP3511 features ±1% CS voltage accuracy and Fault Output(MOSFET Drain-Source Short)

has dedicated analog dimming input up to 3V. It can Short Circuit Protection

be powered from 8.5V ~ 18V supply. UVLO

MAP3511 provides MOSFET DS short detection(FLT 8 Leads SOIC Package with Halogen-free

output), SCP and UVLO.

MAP3511 is available 8 leads SOIC with Halogen- Applications

free (fully RoHS compliant). High Brightness white LED backlighting for LCD

TVs

General LED lighting applications

Ordering Information

Top Ambient

Part Number Package RoHS Status

Marking Temperature Range

MAP3511SIRH MAP3511 -40℃ to +85℃ 8Leads SOIC Halogen Free

1 Typical Application

VIN

CIN

MAP3511

VCC 2 D COUT LEDs

VCC

7 FLT

CVCC FLT

L

PWM RPWM 6

PWM

ADIM RADIM RG Q

8 4

ADIM GATE

CADIM RF

1

CS

CF RCS

5

TOFF GND 3

RTOFF

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

Pin Configuration

1 CS M ADIM 8

A

2 VCC P FLT 7

3

3 GND 5 PWM 6

1

4 GATE 1 TOFF 5

SOIC-8L

Pin Description

8leads

Name Description

SOIC

1 CS External current sense (Note 1)

2 VCC Power supply input. Need external bypass capacitor

3 GND Ground

4 GATE GATE driver output to drive external NMOSFET

5 TOFF Setting for GATE off-time(Note 2)

6 PWM PWM signal input for dimming

7 FLT Fault Output

8 ADIM Setting for LED current thru external DC voltage

2

Note 1: Connect external resistor to GND to sense the external power MOSFET source current as shown in typical application

Note 2: Connect external resistor to GND to set GATE off-time as shown in typical application

Functional Block Diagram

Internal

VCC LDO

supply GND

+

POR

-

UVLO

Current Off-

TOFF Mirror Timer

↓

S Q

GATE

R

ADIM AV PWM

Average-

Mode

Control

Logic

L/E

CS Blanking

SCP

MOSFET

DS Short

FLT

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

Absolute Maximum Ratings(Note 1)

Symbol Parameter Min Max Unit

VVCC, VGATE, VPWM VCC, GATE, PWM pins Voltage -0.3 20 V

VCS, VTOFF, VADIM, VFLT CS, TOFF, ADIM, FLT pins Voltage -0.3 5 V

TPAD Soldering Lead/ Pad Temperature 10sec 300 °C

TJ Junction Temperature -40 +150 °C

TS Storage Temperature -65 +150 °C

HBM on All Pins (Note 2) -2000 +2000

ESD V

MM on All Pins (Note 3) -200 +200

Note 1: Stresses beyond the above listed maximum ratings may damage the device permanently. Operating above the recommended

conditions for extended time may stress the device and affect device reliability. Also the device may not operate normally above the

recommended operating conditions. These are stress ratings only.

Note 2: ESD tested per JESD22A-114.

Note 3: ESD tested per JESD22A-115.

Recommended Operating Conditions (Note 1)

Parameter Min Max Unit

VVcc Supply Input Voltage 8.5 18.0 V

VADIM ADIM Input Range 0.5 3.0 V

TA Ambient Temperature (Note 2) -40 +85 °C

Note 1: Normal operation of the device is not guaranteed if operating the device over outside range of recommended conditions.

Note 2: The ambient temperature may have to be derated if used in high power dissipation and poor thermal resistance conditions.

Package Thermal Resistance (Note 1)

3

Parameter θJA Unit

MAP3511SIRH 8 Leads SOIC 94.6 ℃/W

Note 1: Multi-layer PCB based on JEDEC standard (JESD51-7)

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

Electrical Characteristics

Unless noted, VVCC = 12V, CVCC = 1.0F, and typical values are tested at TA = 25C.

Parameter Test Condition Min Typ Max Unit

Supply

VVCC Input Voltage Range 8.5 18 V

IQ Quiescent Current VPWM = 5V, VCS = 0V 1.6 mA

Under Voltage Lockout Release threshold(rising VVCC) 7.5 8.0 8.5

VUVLO V

Threshold Voltage on VCC pin Lockout hysteresis(falling VVCC) 0.5 1.0 1.5

OFF Timer

RTOFF=52kΩ 4.5 5.0 5.5

tOFF GATE Off-time us

RTOFF=104kΩ 9 10 11

tON_MIN Min. On-Time 300 ns

tON_MAX Max. On-Time VADIM = 3V 33 us

tOFF_MIN Min. Off-Time 1.0 1.1 us

DMAX Max. Duty Cycle VADIM = 3V, tOFF=1us 97 %

GATE Driver

ISOURCE GATE Source Current VGATE = 0V 400 mA

ISINK GATE Sink Current VGATE = VVCC=12V 800 mA

tRISE GATE Output Rising Time CGATE=1nF, VVCC = 12V 50 85 ns

tFALL GATE Output Falling Time CGATE=1nF, VVCC = 12V 25 45 ns

Current Sense & Dimming

VADIM ADIM Input Voltage Range 0.5 3.0 V

AV VADIM to CS Voltage Ratio 0.5075 V/V

VADIM = 0.5V 0.2512 0.2563

VCS CS Voltage V

VADIM = 3.0V 1.5073 1.5377

tLEB Leading Edge Blanking Time 300 ns

PWM Interface

4 Logic Input Level on VPWM_L : Logic Low 0.8

VPWM V

PWM pin VPWM_H : Logic High 2.0

RPWM Pull-down Resistor on PWM pin VPWM = 4V 50 100 150 kΩ

Protection

AVSCP VADIM to SCP Voltage Ratio 1.45 V/V

VADIM = 0.5V 0.6888 0.7250 0.7613

SCP Detection Threshold Voltage

VSCP VADIM = 1.0V 1.3775 1.4500 1.5225 V

on CS pins

VADIM = 2.5V 3.4438 3.6250 3.8063

tDELAY SCP Delay Time 300 ns

tRESTART Restart Time 1 ms

MOSFET DS Short Detection VADIM = 0.5V (Note 1, 2) 0.25

VSCPDS V

Threshold Voltage on CS pin VADIM = 2.5V (Note 1, 2) 1.25

VFLT FLT pin High Voltage 4.5 5 V

Note 1: These parameters, although guaranteed by design, are not tested in mass production.

Note 2: At start-up(VVCC >= VUVLO release threshold) or VPWM = Logic ‘High’ at running

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

Typical Operating Characteristics

Unless otherwise noted, VVCC = 12V and TA = 25C.

Set ILED=425mA Set ILED=425mA

Set ILED=425mA

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

Typical Operating Characteristics

Unless otherwise noted, VVCC = 12V and TA = 25C.

VUVLO(RELEASE) vs. Temp VUVLO(HYS) vs. Temp.

AV(VADIM=0.5V) vs. Temp AV(VADIM=3.0V) vs. Temp

tOFF(RTOFF=52kΩ) vs. Temp VSCP(VADIM=1V) vs. Temp

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

Typical Operating Characteristics

Unless otherwise noted, VVCC = 12V and TA = 25C.

Constant Current Control Min. Dimming(COUT=330nF)

GATE 20V/div PWM 5V/div

GATE 20V/div

VLED 20V/div

IL 0.1A/div IL 0.1A/div

ILED 0.1A/div

ILED 0.1A/div

20us/div

Soft-start(COUT=330nF) VADIM Off

GATE 20V/div ADIM 0.2V/div

GATE 20V/div

IL 0.1A/div

VCS 0.2V/div

ILED 20us/div IL 0.2A/div

0.1A/div

UVLO Release UVLO Lockout

VCC 2V/div VCC 2V/div

GATE 10V/div

GATE 10V/div

IL 0.2A/div IL 0.2A/div

SCP(LED All Short) SCP(Inductor Short)

GATE 20V/div GATE 20V/div

VLED 20V/div VLED 20V/div

1ms/div 1ms/div

VCS 1V/div VCS 2V/div

IL 0.5A/div IL 2A/div

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

Typical Operating Characteristics

Unless otherwise noted, VVCC = 12V and TA = 25C.

SCP(Catch Diode Short) FLT Output(@ PWM Off @ Running)

GATE 20V/div

PWM 5V/div

VLED 20V/div

VCS 1V/div

1ms/div

VCS 2V/div

IL 2A/div FLT 5V/div

FLT Output(@ PWM On @ Running) FLT Output(@ PWM On or Off @ Start-up)

PWM 5V/div

VCC 5V/div

VCS 1V/div

VCS 1V/div

FLT 5V/div

FLT 5V/div

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

Functional Description

GENERAL DESCRIPTION UVLO

The MAP3511 is a low-side single switch control, The MAP3511 has an Internal LDO regulator to supply

constant off-time buck controller optimized to LED internal circuit and GATE driver. This LDO is powered

backlight applications. The IC employs unique average- up when the VCC voltage rises to UVLO release

mode current control architecture which provides threshold.

precise LED current accuracy. It does not require any If the voltage on the VCC pin falls below UVLO

external loop compensation or high side current lockout threshold, the device turns-off the GATE output

sensing. and be reset. This ensures fail-safe operation for VCC

The IC operates at continuous conduction mode to input voltage falling.

reduce output ripple, thus small output capacitor is

available. The off time is user adjustable through the SCP

selection of an external resistor, this allows the design

to be optimized for a given switching frequency range If the CS voltage rises VSCP during normal operation,

and supports wide range of input voltages. the MAP3511 turns-off the GATE output after tDELAY(typ.

300ns) time. The auto-restart time is typ. 1ms(tRESTART).

RCS SETTING This protects for hard instantaneous short such as

catch diode, inductor or LED bar short.

The current sense resistor value is calculated by

following equation. tDELAY tDELAY

0 . 5075 V GATE

R CS [ ]

ADIM

I LED

VSCP

ROFF SETTING CS

9

The off-time of the GATE driver is programmed by an

tRESTART

external resistor connected between the TOFF pin and

ground. Do not leave this pin open. The off-time is

calculated by following equation.

0 . 4 t OFF [ us ] 1000

R TOFF [k ]

38 . 4

PWM DIMMING

The brightness control of the LEDs is performed by a

pulse-width modulation. The GATE output is valid only

at PWM on period. this means that the GATE maintains

off-state as long as PWM signal is logic low.

Care should be taken to test at low PWM duty-cycle

because the output capacitor can affect rising and

falling time of LED current due to its charging and

discharging time.

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

MOSFET D-S Short Detection & FLT Output

In case the following drain-source short events of external MOSFET occur, the FLT pin goes to logic HIGH state

immediately. This shuts off the whole system power supply. The protection status is latched and can be cleared by

applying a complete power-on-reset(POR).

CASE(1) : At start-up - Regardless of PWM logic state, if VCS is equal or over than 0.5*VADIM and last over 4us.

FLT pin voltage goes HIGH level before the first GATE output if PWM is logic HIGH state.

CASE(2) : At dimming(PWM=logic HIGH) - At first, SCP will be occured. Even though the GATE is off-state by SCP,

if the CS voltage is equal or over than 0.5*VADIM and last over 30us.

CASE(3) : At other condition(PWM=logic LOW) - If the CS voltage is equal or over than 3.6V and lasts over 4us.

VCC

UVLO_H

UVLO_L

PWM

GATE

4us

30us 3.6V

4us 1.7 X VADIM

VCS

0.5 X VADIM

10

FLT CASE(1) CASE(2) CASE(3)

The FLT pin is at logic low state when no error is detected.

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

External Components Selection

Inductor MOSFET

In order to achieve accurate constant current output, The power MOSFET is chosen based on maximum

the MAP3511 is required to operate in Continuous stress voltage, maximum peak MOSFET current, total

Conduction Mode (CCM) under all operating conditions. power losses, maximum allowed operating temperature

In general, the magnitude of the inductor ripple current and the driver capability of the MAP3511.

should be kept as small as possible. If the PCB size is

not limited, higher inductance values result in better Maximum stress voltage on the power MOSFET

accuracy of the output current. However, in order to (drain-source voltage) for this buck converter is equal

minimize the physical size of the circuit, an inductor to the input voltage. The power MOSFET must be

with minimum physical outline should be selected such selected with some voltage margin. For example, if the

that the converter always operates in CCM and the input voltage is maximally 400 V, then maximum drain-

peak inductor current does not exceed the saturation source voltage should be 450 V or higher.

current limit of the inductor.

The Min. inductance(boundary inductance) which Maximum peak MOSFET current was selected in

guarantees CCM operation can be calculated as; order to calculate the inductor size. Also in this case,

the power MOSFET must be chosen with some current

I LB 2 I OUT

margin.

The power losses in the MOSFET can be separated

V OUT V OUT (1 D ) into conduction losses and switching losses. The

L MIN t OFF

I LB 2 I OUT f SW conduction loss, PCOND, is the I2R loss across the

MOSFET. The conduction loss is given by;

The ripple current through chosen inductor is as

2

following equation; PCOND R DS ( ON ) I RMS k

(V IN V OUT ) D Where, k is the temperature coefficient of the MOSFET.

I L

11 L f SW The switching loss is related to QGD and QGS1 which

determine the commutation time. QGS1 is the charge

between the threshold voltage and the plateau voltage

For example, in case VIN=175V, VOUT=135V,

IOUT(ILED)=425mA, fSW =50kHz and target ripple when a driver charges the gate, which can be read in

current=300mA; the chart of VGS vs. QG of the MOSFET datasheet. QGD

is the charge during the plateau voltage. These two

parameters are needed to estimate the turn on and turn

V OUT 135

D 0 . 77 off loss.

V IN 175

Q GS 1 R G

P SW V DS I IN f SW

V OUT (1 D ) 135 (1 0 . 77 ) V DR V TH

L MIN 0 . 73 [ mH ]

2 I OUT f SW 2 0 . 425 50 10

3

Q GD R G

V DS I IN f SW

V DR V PLT

The ripple current at LMIN is 2*IOUT=850[mA] and this is

too large to use.

where VTH is the threshold voltage, VPLT is the plateau

For target ripple current(ΔIL=300mA); voltage, RG is the gate resistance, VDS is the drain-

source voltage, VDR is the drive voltage

(V IN V OUT ) D (175 135 ) 0 . 77 The total gate charge, QG, is used to calculate the

L 2 . 05 [ mH ]

I L f SW 0 . 3 50 10

3

gate drive loss. The expression is

In this case, the chosen conventional inductor is P DR Q G V DR f SW

2mH/1A.

Fast switching MOSFETs can cause noise spikes

which may affect performance. To reduce these spikes

a drive resistor can be placed between GATE pin and

the MOSFET gate.

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

Catch Diode PCB LAYOUT GUIDE

The catch diode is chosen based on its maximum A gate drive signal output from GATE pin becomes

stress voltage, its maximum peak current and total noise source, which may cause malfunction of IC due

power losses. The power losses are lower for a larger to cross talk if placed by the side of an analog line. It is

duty cycle and vice-versa, because the diode is opened recommended to avoid placing the output line

(connected) during off-time. especially by the side of CS, ADIM and TOFF pins as

far as possible.

Maximum voltage stress across the diode is equal to Following figure shows an example of demo board.

the input voltage VIN, and therefore the power diode

must be selected with some voltage margin. For

example, if the input voltage is maximally 400 V, then

maximum repetitive peak reverse voltage (VRRM) should

be 450 V or higher.

Maximum peak diode current is selected in order to

calculate the inductor size. Also in this case, the catch

diode must be selected with some current margin.

The voltage drop across the diode in a conducting

state is primarily responsible for the losses in the diode.

The power dissipated by the diode can be calculated

as the product of the forward voltage and the output

load current for the time that the diode is conducting.

The switching losses which occur at the transitions

from conducting to non-conducting states are very

small compared to conduction losses and are usually

ignored. The power dissipated by the catch diode is

given by:

12

PD V D I O (1 D )

Where, VD is the forward voltage drop of the catch

diode.

Input Capacitor

Select the input capacitor to ensure that the input

voltage ripple is within a desired range (1% to 5% of

the input bus voltage). The input capacitor is usually

electrolytic and its ESR dominates its impedance.

A 4.7μF to 22μF electrolytic capacitor will usually

suffice.

Output Capacitor

Selecting a suitable capacitor can reduce LED current

ripple and increase LED life-time. Note that having too

large of a capacitance will cause the LED current to

respond slowly. The typical value of the capacitor is

0.33μF.

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

Physical Dimensions

13

8 Leads SOIC

MagnaChip Semiconductor Ltd. doesn’t not recommend the use of its products in hostile environments, including, without limitation,

aircraft, nuclear power generation, medical appliances, and devices or systems in which malfunction of any product can reasonably

be expected to result in a personal injury. Seller’s customers using or selling Seller’s products for use in such applications do so at

their own risk and agree to fully defend and indemnify Seller.

MagnaChip reserves the right to change the specifications and circuitry without notice at any time. MagnaChip does not consider

responsibility for use of any circuitry other than circuitry entirely included in a MagnaChip product.

is a registered trademark of MagnaChip Semiconductor Ltd.

MagnaChip Semiconductor Ltd.

891, Daechi-Dong, Kangnam-Gu, Seoul, 135-738 Korea

Tel : 82-2-6903-3451 / Fax : 82-2-6903-3668 ~9

www.magnachip.com

Dec 12th 2014

rammer

Confidential

Datasheet Version 1.0

MAP3511 – Average Current Control Buck Controller for LED Backlight

Datasheet Revision History

Date Version Changes

2014-12-12 Version 1.0 Initial release

14

Dec 12th 2014

Você também pode gostar

- MAP3511Documento14 páginasMAP3511Дмитрий КопышевAinda não há avaliações

- Datasheet - : 2-CH Average Current Control Buck Controller For LED BacklightDocumento14 páginasDatasheet - : 2-CH Average Current Control Buck Controller For LED BacklightBiju PrestcomAinda não há avaliações

- QQ MAP361Documento11 páginasQQ MAP361Mamur bogonAinda não há avaliações

- Transition-Mode PFC Controller With Fault Condition ProtectionDocumento20 páginasTransition-Mode PFC Controller With Fault Condition ProtectionMega BoxAinda não há avaliações

- Transition-Mode PFC Controller With Fault Condition ProtectionDocumento16 páginasTransition-Mode PFC Controller With Fault Condition ProtectionAdailton SantosAinda não há avaliações

- DS8816ADocumento21 páginasDS8816AAgustin AyalaAinda não há avaliações

- Rt8816a-06 Gtx1070 Gigabyte MemoriasDocumento21 páginasRt8816a-06 Gtx1070 Gigabyte Memoriastechgamebr85Ainda não há avaliações

- Dual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesDocumento21 páginasDual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesДмитрий НичипоровичAinda não há avaliações

- MAP8802 MagnaChipDocumento16 páginasMAP8802 MagnaChipnadie696Ainda não há avaliações

- A82C250Documento20 páginasA82C250AdamAinda não há avaliações

- Infineon ILD2111 DS v01 - 00 ENDocumento66 páginasInfineon ILD2111 DS v01 - 00 ENИван КумбровAinda não há avaliações

- Green-Mode PWM Controller: General Description FeaturesDocumento10 páginasGreen-Mode PWM Controller: General Description FeaturesValdir DerlannAinda não há avaliações

- PCA82C251: 1. General DescriptionDocumento16 páginasPCA82C251: 1. General Descriptionsam etcAinda não há avaliações

- Ds8204a 05Documento19 páginasDs8204a 05marcelo Chiu LeonAinda não há avaliações

- MT7860 MaxicTechnologyDocumento7 páginasMT7860 MaxicTechnologySatishAinda não há avaliações

- AOZ1948AIDocumento13 páginasAOZ1948AIfox7878Ainda não há avaliações

- Datasheet PDFDocumento11 páginasDatasheet PDFlucio20000Ainda não há avaliações

- RT8057Documento11 páginasRT8057antonio carlos clementino cruzAinda não há avaliações

- Multi-Phase PWM Controller With PWM-VID Reference: General Description FeaturesDocumento24 páginasMulti-Phase PWM Controller With PWM-VID Reference: General Description FeaturesSurendra SharmaAinda não há avaliações

- R1283K001CDocumento26 páginasR1283K001CdinhdtdAinda não há avaliações

- MP3391 r1.12Documento18 páginasMP3391 r1.12Elsa Nababan EchaAinda não há avaliações

- MP3391Documento18 páginasMP3391Raul AlfaroAinda não há avaliações

- Multi-Phase DC/DC Controller For CPU Core Power Supply: General Description FeaturesDocumento14 páginasMulti-Phase DC/DC Controller For CPU Core Power Supply: General Description FeaturesTeles SilvaAinda não há avaliações

- Peak 3A Bus Termination RegulatorDocumento12 páginasPeak 3A Bus Termination RegulatormkubawatAinda não há avaliações

- Data Sheet: Beyond Innovation Technology Co., LTDDocumento6 páginasData Sheet: Beyond Innovation Technology Co., LTDOlivier OuinaAinda não há avaliações

- Chapter 3 ELECTRONICS: Edition: 156Documento47 páginasChapter 3 ELECTRONICS: Edition: 156Bagas dwi PrasetyoAinda não há avaliações

- 3A, 1Mhz, Synchronous Step-Down Converter: General Description FeaturesDocumento12 páginas3A, 1Mhz, Synchronous Step-Down Converter: General Description FeatureskiryanoffAinda não há avaliações

- LD7522PS Psu IcDocumento17 páginasLD7522PS Psu IcJerryMungoAinda não há avaliações

- RT8800APQV Datasheet (PDF) Download - Richtek Technology CorporationDocumento21 páginasRT8800APQV Datasheet (PDF) Download - Richtek Technology Corporationlucas sousaAinda não há avaliações

- R1283x SERIES: 2ch DC/DC For CCD & OLEDDocumento26 páginasR1283x SERIES: 2ch DC/DC For CCD & OLEDarnaud.herbertAinda não há avaliações

- FAN7529 (IC601) - Datasheet IIDocumento20 páginasFAN7529 (IC601) - Datasheet IIJose BenavidesAinda não há avaliações

- PCA82C251: 1. General DescriptionDocumento17 páginasPCA82C251: 1. General DescriptionAndres Emilio Veloso RamirezAinda não há avaliações

- DS8884B 01Documento46 páginasDS8884B 01semar bypasAinda não há avaliações

- Green-Mode PWM Controller GuideDocumento16 páginasGreen-Mode PWM Controller Guidegulhshan khanAinda não há avaliações

- Rt8813a r05 RichtekDocumento24 páginasRt8813a r05 RichtekjokophpAinda não há avaliações

- RT3661AB-RichTek Sau AS3661AB PDFDocumento36 páginasRT3661AB-RichTek Sau AS3661AB PDFeduardskAinda não há avaliações

- LD7578J LeadtrendDocumento19 páginasLD7578J Leadtrendnagahara.eduardoAinda não há avaliações

- CIR9803 DatasheetDocumento2 páginasCIR9803 DatasheetLong Trần NhậtAinda não há avaliações

- CS9803GPDocumento2 páginasCS9803GPmostafa ashrafAinda não há avaliações

- CS9803GPDocumento2 páginasCS9803GPng_viet_cuong_groupAinda não há avaliações

- RT8812C-02 GTX1070Documento20 páginasRT8812C-02 GTX1070techgamebr85Ainda não há avaliações

- AP384XG Data SheetDocumento13 páginasAP384XG Data Sheetjoseluise68Ainda não há avaliações

- RT8204-DS8204-06 Single Synchronous Buck With LDO ControllerDocumento19 páginasRT8204-DS8204-06 Single Synchronous Buck With LDO ControllerMaks ProstAinda não há avaliações

- DC To DC Converter rt8272Documento14 páginasDC To DC Converter rt8272hadAinda não há avaliações

- Datasheet 28Documento35 páginasDatasheet 28Eric ArcherAinda não há avaliações

- V02 0409en - DS - HCPL 7860 - 2015 03 061 908727Documento18 páginasV02 0409en - DS - HCPL 7860 - 2015 03 061 908727Shirley CastañedaAinda não há avaliações

- Ap 3843 CPDocumento13 páginasAp 3843 CPJesus ChaileAinda não há avaliações

- PCA_82C250Documento19 páginasPCA_82C250RuslanAinda não há avaliações

- PCA82C250: 1. General DescriptionDocumento17 páginasPCA82C250: 1. General Descriptionsabir siddiquiAinda não há avaliações

- 2A, 18V, 800Khz Synchronous Step-Down Converter: General Description FeaturesDocumento15 páginas2A, 18V, 800Khz Synchronous Step-Down Converter: General Description FeaturesJose Carlos SoaresAinda não há avaliações

- 500ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatorDocumento13 páginas500ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatoreugeneAinda não há avaliações

- LD7576PS Green-Mode PWM Controller With High-Voltage Start-Up Circuit and Adjustable OLP Delay TimeDocumento22 páginasLD7576PS Green-Mode PWM Controller With High-Voltage Start-Up Circuit and Adjustable OLP Delay TimeAnonymous PJrRBT7bO2Ainda não há avaliações

- DatasheetDocumento12 páginasDatasheetWAN MOZESAinda não há avaliações

- LD7522Documento18 páginasLD7522uyfcastellAinda não há avaliações

- RT8577ADocumento18 páginasRT8577ASamuel SamTechAinda não há avaliações

- Aoz1212ai PDFDocumento18 páginasAoz1212ai PDF060279Ainda não há avaliações

- BO039M1920M DatasheetDocumento21 páginasBO039M1920M DatasheetJohn LyalAinda não há avaliações

- Green-Mode PWM Controller Technical DocumentDocumento19 páginasGreen-Mode PWM Controller Technical DocumentЕвгений ПAinda não há avaliações

- Datasheet 1000A 50mvDocumento1 páginaDatasheet 1000A 50mvriyad abdulhafeedAinda não há avaliações

- Ve Shunt 500ADocumento1 páginaVe Shunt 500Ariyad abdulhafeedAinda não há avaliações

- Ve Shunt 500ADocumento1 páginaVe Shunt 500Ariyad abdulhafeedAinda não há avaliações

- CM508Documento1 páginaCM508riyad abdulhafeedAinda não há avaliações

- Samsung Ue32h6200aw Ue40h6200aw Ue48h6200aw Ue50h6200aw Ue55h6200aw Ue60h6200aw Chassis U8dcDocumento71 páginasSamsung Ue32h6200aw Ue40h6200aw Ue48h6200aw Ue50h6200aw Ue55h6200aw Ue60h6200aw Chassis U8dcstefanoAinda não há avaliações

- Vortix Roof Type Fan TRM10Documento1 páginaVortix Roof Type Fan TRM10riyad abdulhafeedAinda não há avaliações

- Diodes Group Body Marking - VishayDocumento25 páginasDiodes Group Body Marking - VishayPelotaDeTrapoAinda não há avaliações

- CM508Documento1 páginaCM508riyad abdulhafeedAinda não há avaliações

- CM508Documento1 páginaCM508riyad abdulhafeedAinda não há avaliações

- 17IPS20Documento2 páginas17IPS20Antonio Verdu AlfonsoAinda não há avaliações

- EZ-THUMP™ Series: Portable Fault Location SystemsDocumento2 páginasEZ-THUMP™ Series: Portable Fault Location Systemsriyad abdulhafeedAinda não há avaliações

- Multicluster-Box 12: Operating ManualDocumento54 páginasMulticluster-Box 12: Operating Manualriyad abdulhafeedAinda não há avaliações

- Cof PDFDocumento4 páginasCof PDFSetiadi DennyAinda não há avaliações

- Fault Location and Cable Repair Manual IMDocumento16 páginasFault Location and Cable Repair Manual IMriyad abdulhafeedAinda não há avaliações

- LGE6841Documento1 páginaLGE6841Windy AmestyAinda não há avaliações

- Data Book 2017Documento280 páginasData Book 2017riyad abdulhafeedAinda não há avaliações

- TSUMV59XU Datasheet PDFDocumento33 páginasTSUMV59XU Datasheet PDFHamza Abbasi AbbasiAinda não há avaliações

- All India CW Pricelist Wef 01.05.2021Documento6 páginasAll India CW Pricelist Wef 01.05.2021Sameer PadhyAinda não há avaliações

- The Minecraft Survival Quest ChallengeDocumento4 páginasThe Minecraft Survival Quest Challengeapi-269630780100% (1)

- Breadth First Search (BFS) Depth First Search (DFS) A-Star Search (A ) Minimax Algorithm Alpha-Beta PruningDocumento31 páginasBreadth First Search (BFS) Depth First Search (DFS) A-Star Search (A ) Minimax Algorithm Alpha-Beta Pruninglevecem778Ainda não há avaliações

- Keyence cv700 - Man2Documento232 páginasKeyence cv700 - Man2kamaleon85Ainda não há avaliações

- History of Architecture in Relation To Interior Period Styles and Furniture DesignDocumento138 páginasHistory of Architecture in Relation To Interior Period Styles and Furniture DesignHan WuAinda não há avaliações

- 1 Osteology (MCQ)Documento12 páginas1 Osteology (MCQ)Utkarsh MishraAinda não há avaliações

- Eslit-Vinea-LA 03 Task #1-4Documento11 páginasEslit-Vinea-LA 03 Task #1-4darkAinda não há avaliações

- Ahmed (2018)Documento9 páginasAhmed (2018)zrancourttremblayAinda não há avaliações

- Predict CambodianDocumento11 páginasPredict CambodianMd Ibrahim KhalilAinda não há avaliações

- Knife Gate ValveDocumento67 páginasKnife Gate Valvekrishna100% (1)

- Noor Hafifi Bin Jalal: Operating Code 1: Demand ForecastDocumento47 páginasNoor Hafifi Bin Jalal: Operating Code 1: Demand ForecastGopalakrishnan SekharanAinda não há avaliações

- 7-Seater MPV: Kia SingaporeDocumento16 páginas7-Seater MPV: Kia SingaporeadiAinda não há avaliações

- Examen 03 Aula - F PostgradoDocumento5 páginasExamen 03 Aula - F PostgradodiegoAinda não há avaliações

- Bla Irv RanchDocumento84 páginasBla Irv RanchArturo Palma RamírezAinda não há avaliações

- RA ELECTRONICSENGR DAVAO Apr2019 PDFDocumento6 páginasRA ELECTRONICSENGR DAVAO Apr2019 PDFPhilBoardResultsAinda não há avaliações

- C15 DiagranmaDocumento2 páginasC15 Diagranmajose manuel100% (1)

- Daraz PKDocumento4 páginasDaraz PKshavais100% (1)

- Assessment Nursing Diagnosis Scientific Rationale Planning Intervention Rationale EvaluationDocumento9 páginasAssessment Nursing Diagnosis Scientific Rationale Planning Intervention Rationale Evaluationclydell joyce masiarAinda não há avaliações

- STTH2002C: High Efficiency Ultrafast DiodeDocumento16 páginasSTTH2002C: High Efficiency Ultrafast DiodeAseng saputraAinda não há avaliações

- Behavioural Theory of The Firm: Presented By: Shubham Gupta Sumit MalikDocumento26 páginasBehavioural Theory of The Firm: Presented By: Shubham Gupta Sumit MalikvarunymrAinda não há avaliações

- Aegon Life Insurance Marketing Strategy AnalysisDocumento22 páginasAegon Life Insurance Marketing Strategy AnalysissalmanAinda não há avaliações

- Saturn Engine Compression Test GuideDocumento7 páginasSaturn Engine Compression Test GuideManuel IzquierdoAinda não há avaliações

- The 4Ms of Operations: Prepared By: Karla Jane F. BangaysisoDocumento18 páginasThe 4Ms of Operations: Prepared By: Karla Jane F. BangaysisoKarla BangFerAinda não há avaliações

- Dialysis PowerpointDocumento10 páginasDialysis Powerpointapi-266328774Ainda não há avaliações

- Transforming City Governments For Successful Smart CitiesDocumento194 páginasTransforming City Governments For Successful Smart CitiesTri Ramdani100% (2)

- Patanjali PDFDocumento11 páginasPatanjali PDFSiddharth GuptaAinda não há avaliações

- Chapter 3 Theoretical ConsiderationsDocumento8 páginasChapter 3 Theoretical Considerationsapi-3696675Ainda não há avaliações

- 1404 Pratul Singhal Ideal Gas Equation Density StoichiometryDocumento22 páginas1404 Pratul Singhal Ideal Gas Equation Density StoichiometryYang ChoudhuryAinda não há avaliações

- Soft Matter Physics Seminar on Non-Equilibrium SystemsDocumento98 páginasSoft Matter Physics Seminar on Non-Equilibrium Systemsdafer_daniAinda não há avaliações

- Essential Components of an Effective Road Drainage SystemDocumento11 páginasEssential Components of an Effective Road Drainage SystemRaisanAlcebarAinda não há avaliações