Escolar Documentos

Profissional Documentos

Cultura Documentos

Features: Dual, Low Power CMOS Operational Amplifiers

Enviado por

Dibya DeyTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Features: Dual, Low Power CMOS Operational Amplifiers

Enviado por

Dibya DeyDireitos autorais:

Formatos disponíveis

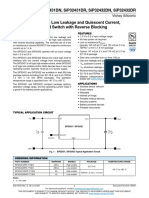

DATASHEET

ICL7621 FN3403

Dual, Low Power CMOS Operational Amplifiers Rev.5.00

Mar 4, 2010

The ICL761X/762X series is a family of monolithic CMOS Features

operational amplifiers. These devices provide the designer

with high performance operation at low supply voltages and • Wide Operating Voltage Range . . . . . . . . . . . 1V to 8V

selectable quiescent currents. They are an ideal design tool • High Input Impedance . . . . . . . . . . . . . . . . . . . . . . . 1012

when ultra low input current and low power dissipation are • Input Current Lower Than BIFETs . . . . . . . . . . . 1pA (Typ)

desired.

• Output Voltage Swing . . . . . . . . . . . . . . . . . . . . V+ and V-

The basic amplifier will operate at supply voltages ranging • Available as Duals (Refer to ICL7611 for Singles)

from 1V to 8V, and may be operated from a single Lithium

• Low Power Replacement for Many Standard Op Amps

cell. The output swing ranges to within a few millivolts of the

supply voltages. Applications

The quiescent supply current of these amplifiers is set to • Portable Instruments

100µA at the factory. This results in power consumption as • Telephone Headsets

low as 200µW per amplifier.

• Hearing Aid/Microphone Amplifiers

Of particular significance is the extremely low (1pA) input • Meter Amplifiers

current, input noise current of 0.01pA/Hz, and 1012 input

• Medical Instruments

impedance. These features optimize performance in very

high source impedance applications. • High Impedance Buffers

The inputs are internally protected. Outputs are fully Pinouts ICL7621

protected against short circuits to ground or to either supply. (8 LD PDIP, SOIC)

TOP VIEW

Because of the low power dissipation, junction temperature

rise and drift are quite low. Applications utilizing these

OUTA 1 8 V+

features may include stable instruments, extended life

designs, or high density packages. -INA 2 - 7 OUTB

+

+INA 3 6 -INB

Ordering Information -

+

V- 4 5 +INB

TEMP.

PART PART RANGE PKG.

NUMBER MARKING (°C) PACKAGE DWG. #

ICL7621DCPA 7621 DCPA 0 to +70 8 Ld PDIP - E8.3

D Grade - IQ = 100µA

ICL7621DCPAZ* 7621 DCPAZ 0 to +70 8 Ld PDIP - E8.3

(Note 2) D Grade - IQ = 100µA

ICL7621DCBA 7621 DCBA 0 to +70 8 Ld SOIC - M8.15

(Note 1) D Grade - IQ = 100µA

ICL7621DCBAZ 7621 DCBAZ 0 to +70 8 Ld SOIC - M8.15

(Notes 1, 2) D Grade - IQ = 100µA

*Pb-free PDIPs can be used for through hole wave solder processing only.

They are not intended for use in Reflow solder processing applications.

NOTES:

1. Add “-T” suffix for tape and reel. Please refer to TB347 for details on reel

specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-

free material sets, molding compounds/die attach materials, and 100%

matte tin plate plus anneal (e3 termination finish, which is RoHS

compliant and compatible with both SnPb and Pb-free soldering

operations). Intersil Pb-free products are MSL classified at Pb-free

peak reflow temperatures that meet or exceed the Pb-free

requirements of IPC/JEDEC J STD-020.

FN3403 Rev.5.00 Page 1 of 9

Mar 4, 2010

ICL7621

Absolute Maximum Ratings Thermal Information

Supply Voltage V+ to V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18V Thermal Resistance (Typical, Note 5) JA (°C/W) JC (°C/W)

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . V- -0.3 to V+ +0.3V PDIP Package . . . . . . . . . . . . . . . . . . . 120 N/A

Differential Input Voltage (Note 3) . . . . . . . . . [(V+ +0.3) - (V- -0.3)]V SOIC Package . . . . . . . . . . . . . . . . . . . 160 N/A

Duration of Output Short Circuit (Note 4). . . . . . . . . . . . . . Unlimited Maximum Junction Temperature (Plastic Package) . . . . . . . +150°C

Maximum Storage Temperature Range . . . . . . . . . . -65°C to +150°C

Operating Conditions Pb-Free Reflow Profile. . . . . . . . . . . . . . . . . . . . . . . . .see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

*Pb-free PDIPs can be used for through hole wave solder

processing only. They are not intended for use in Reflow solder

processing applications.

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and

result in failures not covered by warranty.

NOTES:

3. Long term offset voltage stability will be degraded if large input differential voltages are applied for long periods of time.

4. The outputs may be shorted to ground or to either supply, for VSUPPLY 10V. Care must be taken to insure that the dissipation rating is not

exceeded.

5. JA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications VSUPPLY = 5V, Unless Otherwise Specified.

TEMP. MIN MAX

PARAMETER SYMBOL TEST CONDITIONS (°C) (Note 6) TYP (Note 6) UNITS

Input Offset Voltage VOS RS 100k +25 - - 15 mV

Full - - 20 mV

Temperature Coefficient of VOS VOS/T RS 100k - - 25 - µV/oC

Input Offset Current IOS +25 - 0.5 30 pA

0 to +70 - - 300 pA

-55 to +125 - 800 pA

Input Bias Current IBIAS +25 - 1.0 50 pA

0 to +70 - - 400 pA

-55 to +125 - - 4000 pA

Common Mode Voltage Range VCMR IQ = 100µA +25 4.2 - - V

Output Voltage Swing VOUT IQ = 100µA, RL = 100k +25 4.9 - - V

0 to +70 4.8 - - V

-55 to +125 4.5 - - V

Large Signal Voltage Gain AVOL VO = 4.0V, RL = 100k, IQ = 100µA +25 80 102 - dB

0 to +70 75 - - dB

-55 to +125 68 - - dB

Unity Gain Bandwidth GBW IQ = 100µA +25 - 0.48 - MHz

Input Resistance RIN +25 - 1012 -

Common Mode Rejection Ratio CMRR RS 100k IQ = 100µA +25 70 91 - dB

Power Supply Rejection Ratio PSRR RS 100k IQ = 100µA +25 80 86 - dB

(VSUPPLY = 8V to 2V)

Input Referred Noise Voltage eN RS = 100, f = 1kHz +25 - 100 - nV/Hz

Input Referred Noise Current iN RS = 100, f = 1kHz +25 - 0.01 - pA/Hz

Supply Current (Per Amplifier) ISUPPLY No Signal, No Load, IQ = 100µA +25 - 0.1 0.25 mA

Channel Separation VO1/VO2 AV = 100 +25 - 120 - dB

FN3403 Rev.5.00 Page 2 of 9

Mar 4, 2010

ICL7621

Electrical Specifications VSUPPLY = 5V, Unless Otherwise Specified. (Continued)

TEMP. MIN MAX

PARAMETER SYMBOL TEST CONDITIONS (°C) (Note 6) TYP (Note 6) UNITS

Slew Rate SR AV = 1, CL = 100pF, VIN = 8VP-P, +25 - 0.16 - V/µs

IQ = 100µA, RL = 100k

Rise Time tR VIN = 50mV, CL = 100pF, +25 - 2 - µs

IQ = 100µA, RL = 100k

Overshoot Factor OS VIN = 50mV, CL = 100pF, +25 - 10 - %

IQ = 100µA, RL = 100k

NOTE:

6. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by

characterization and are not production tested.

Schematic Diagram

IQ

INPUT STAGE SETTING STAGE OUTPUT STAGE

V+

A

900k

3k 3k C

QP5 6.3V

V- QP7

100k QP8

QP1 QP2 QP6

QP3 QP4

V+

QP9

+INPUT QN1 QN2

CFF = 9pF

OUTPUT

V- CC = 33pF

V+

-INPUT

QN7 QN9

QN4 QN6 QN10 QN11

V-

QN5

6.3V

V+

QN3

TABLE OF JUMPERS IQ E

QN8

ICL7621 C, E 100µA G

V-

FN3403 Rev.5.00 Page 3 of 9

Mar 4, 2010

ICL7621

Application Information

Static Protection Output Stage and Load Driving Considerations

All devices are static protected by the use of input diodes. Each amplifiers’ quiescent current flows primarily in the output

However, strong static fields should be avoided, as it is stage. This is approximately 70% of the IQ settings. This allows

possible for the strong fields to cause degraded diode junction output swings to almost the supply rails for output loads of

characteristics, which may result in increased input leakage 1M, 100k, and 10k, using the output stage in a highly

currents. linear class A mode. In this mode, crossover distortion is

avoided and the voltage gain is maximized. However, the

Latchup Avoidance

output stage can also be operated in Class AB for higher

Junction-isolated CMOS circuits employ configurations which output currents (see graphs in “Typical Performance Curves”

produce a parasitic 4-layer (PNPN) structure. The 4-layer beginning on page 6). During the transition from Class A to

structure has characteristics similar to an SCR, and under Class B operation, the output transfer characteristic is

certain circumstances may be triggered into a low impedance nonlinear and the voltage gain decreases.

state resulting in excessive supply current. To avoid this

condition, no voltage greater than 0.3V beyond the supply rails Frequency Compensation

may be applied to any pin. In general, the op amp supplies The ICL76XX are internally compensated, and are stable for

must be established simultaneously with, or before any input closed loop gains as low as unity with capacitive loads up to

signals are applied. If this is not possible, the drive circuits 100pF.

must limit input current flow to 2mA to prevent latchup.

Typical Applications

Choosing the Proper IQ

The user is cautioned that, due to extremely high input

Each device in the ICL76XX family has a similar IQ setup scheme,

impedances, care must be exercised in layout, construction,

which allows the amplifier to be set to nominal quiescent currents

board cleanliness, and supply filtering to avoid hum and noise

of 10µA, 100µA or 1mA. These current settings change only very

pickup.

slightly over the entire supply voltage range. The ICL7611/12

have an external IQ control terminal, permitting user selection of

each amplifiers’ quiescent current. The ICL7621 has a fixed IQ

setting of 100µA.

+5 +5

VIN ICL76XX

+

VOUT VIN - ICL76XX

- VOUT

RL 10k 100k + TO CMOS OR

LPTTL LOGIC

1M

FIGURE 1. SIMPLE FOLLOWER FIGURE 2. LEVEL DETECTOR

-

1/2 1M

ICL7621 -

1/2

1µF + ICL7621

+

1M +

- 1M

ICL76XX VOUT V- V+

+ DUTY CYCLE

680k

WAVEFORM GENERATOR

NOTE: Since the output range swings exactly from rail to rail,

NOTE: Low leakage currents allow integration times up to frequency and duty cycle are virtually independent of power supply

several hours. variations.

FIGURE 3. PHOTOCURRENT INTEGRATOR FIGURE 4. TRIANGLE/SQUARE WAVE GENERATOR

FN3403 Rev.5.00 Page 4 of 9

Mar 4, 2010

ICL7621

1M

VOH +8V

0.5µF 2.2M 20k

TO

VIN 10k SUCCEEDING + TA = +125°C

+ V+

10µF INPUT

1/2 20k

STAGE

ICL7621 OUT

1.8k = 5%

- SCALE

ADJUST VOL - V-

- V+

1/2

COMMON ICL7621

-8V

+

FIGURE 5. AVERAGING AC TO DC CONVERTER FOR A/D FIGURE 6. BURN-IN AND LIFE TEST CIRCUIT

CONVERTERS SUCH AS ICL7106, ICL7107,

ICL7109, ICL7116, ICL7117

0.2µF

0.2µF

0.2µF

30k 160k

+ 680k 100k 51k

1/2 +

ICL7621

1/2

- ICL7621

-

360k

INPUT 1M

0.1µF 0.2µF 0.1µF

OUTPUT

360k NOTE 7 1M

NOTE 7

NOTES:

7. Small capacitors (25pF to 50pF) may be needed for stability in some cases.

8. The low bias currents permit high resistance and low capacitance values to be used to achieve low frequency cutoff. fC = 10Hz, AVCL = 4,

Passband ripple = 0.1dB.

FIGURE 7. FIFTH ORDER CHEBYCHEV MULTIPLE FEEDBACK LOW PASS FILTER

FN3403 Rev.5.00 Page 5 of 9

Mar 4, 2010

ICL7621

Typical Performance Curves

10k 104

TA = +25°C V+ - V- = 10V

NO LOAD NO LOAD

NO SIGNAL NO SIGNAL

SUPPLY CURRENT (µA)

SUPPLY CURRENT (µA)

1k 103

IQ = 100µA

100 102 IQ = 100µA

10 10

1 1

0 2 4 6 8 10 12 14 16 -50 -25 0 25 50 75 100 125

SUPPLY VOLTAGE (V) FREE-AIR TEMPERATURE (°C)

FIGURE 8. SUPPLY CURRENT PER AMPLIFIER vs SUPPLY FIGURE 9. SUPPLY CURRENT PER AMPLIFIER vs FREE-AIR

VOLTAGE TEMPERATURE

1000 1000

VSUPPLY = 10V

VS = 5V

DIFFERENTIAL VOLTAGE GAIN (kV/V)

VOUT = 8V

INPUT BIAS CURRENT (pA)

100

100

RL = 100k

IQ = 100µA

10

10

1.0

0.1 1

-50 -25 0 25 50 75 100 125 -75 -50 -25 0 25 50 75 100 125

FREE-AIR TEMPERATURE (°C) FREE-AIR TEMPERATURE (°C)

FIGURE 10. INPUT BIAS CURRENT vs TEMPERATURE FIGURE 11. LARGE SIGNAL DIFFERENTIAL VOLTAGE GAIN

vs FREE-AIR TEMPERATURE

107 105

COMMON MODE REJECTION RATIO (dB)

TA = +25°C VSUPPLY = 10V

DIFFERENTIAL VOLTAGE GAIN (V/V)

106 VSUPPLY = 15V 100

105 95

IQ = 100µA

IQ = 100µA 90

104

85

103

80

102

10 75

1 70

0.1 1.0 10 100 1k 10k 100k 1M -75 -50 -25 0 25 50 75 100 125

FREQUENCY (Hz) FREE-AIR TEMPERATURE (°C)

FIGURE 12. LARGE SIGNAL FREQUENCY RESPONSE FIGURE 13. COMMON MODE REJECTION RATIO vs FREE-AIR

TEMPERATURE

FN3403 Rev.5.00 Page 6 of 9

Mar 4, 2010

ICL7621

Typical Performance Curves (Continued)

EQUIVALENT INPUT NOISE VOLTAGE (nV/Hz)

100 600

SUPPLY VOLTAGE REJECTION RATIO (dB)

VSUPPLY = 10V TA = +25°C

95 3V VSUPPLY 16V

500

90 IQ = 100µA

400

85

300

80

200

75

70 100

65 0

-75 -50 -25 0 25 50 75 100 125 10 100 1k 10k 100k

FREE-AIR TEMPERATURE (°C) FREQUENCY (Hz)

FIGURE 14. POWER SUPPLY REJECTION RATIO vs FREE-AIR FIGURE 15. EQUIVALENT INPUT NOISE VOLTAGE vs

TEMPERATURE FREQUENCY

16 0.01

MAXIMUM OUTPUT SINK CURRENT (mA)

VSUPPLY TA = +25°C

14 =8V

IQ = 100µA

MAXIMUM PEAK-TO-PEAK

OUTPUT VOLTAGE (VP-P)

12

0.1

10

VSUPPLY

=5V

8

IQ = 100µA

6

1.0

4

VSUPPLY

2 =2V

0 10

100 1k 10k 100k 1M 10M 0 2 4 6 8 10 12 14 16

FREQUENCY (Hz)

SUPPLY VOLTAGE (V)

FIGURE 16. OUTPUT VOLTAGE vs FREQUENCY FIGURE 17. OUTPUT SINK CURRENT vs SUPPLY VOLTAGE

8

TA = +25°C, VSUPPLY = 10V

INPUT AND OUTPUT VOLTAGE (V)

6 RL = 100k, CL = 100pF

2

OUTPUT

0

-2

INPUT

-4

-6

0 20 40 60 80 100 120

TIME (µs)

FIGURE 18. VOLTAGE FOLLOWER LARGE SIGNAL PULSE RESPONSE (IQ = 100µA)

FN3403 Rev.5.00 Page 7 of 9

Mar 4, 2010

ICL7621

Dual-In-Line Plastic Packages (PDIP)

N

E8.3 (JEDEC MS-001-BA ISSUE D)

8 LEAD DUAL-IN-LINE PLASTIC PACKAGE

E1

INDEX INCHES MILLIMETERS

AREA 1 2 3 N/2

SYMBOL MIN MAX MIN MAX NOTES

-B-

A - 0.210 - 5.33 4

-A-

D E A1 0.015 - 0.39 - 4

BASE A2 0.115 0.195 2.93 4.95 -

PLANE A2

-C- A

SEATING

B 0.014 0.022 0.356 0.558 -

PLANE L C B1 0.045 0.070 1.15 1.77 8, 10

L

D1 A1 eA C 0.008 0.014 0.204 0.355 -

D1

B1 e D 0.355 0.400 9.01 10.16 5

eC C

B

eB D1 0.005 - 0.13 - 5

0.010 (0.25) M C A B S

E 0.300 0.325 7.62 8.25 6

NOTES: E1 0.240 0.280 6.10 7.11 5

1. Controlling Dimensions: INCH. In case of conflict between

e 0.100 BSC 2.54 BSC -

English and Metric dimensions, the inch dimensions control.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982. eA 0.300 BSC 7.62 BSC 6

3. Symbols are defined in the “MO Series Symbol List” in Section eB - 0.430 - 10.92 7

2.2 of Publication No. 95. L 0.115 0.150 2.93 3.81 4

4. Dimensions A, A1 and L are measured with the package seated

N 8 8 9

in JEDEC seating plane gauge GS-3.

5. D, D1, and E1 dimensions do not include mold flash or protru- Rev. 0 12/93

sions. Mold flash or protrusions shall not exceed 0.010 inch

(0.25mm).

6. E and eA are measured with the leads constrained to be per-

pendicular to datum -C- .

7. eB and eC are measured at the lead tips with the leads uncon-

strained. eC must be zero or greater.

8. B1 maximum dimensions do not include dambar protrusions.

Dambar protrusions shall not exceed 0.010 inch (0.25mm).

9. N is the maximum number of terminal positions.

10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3,

E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch

(0.76 - 1.14mm).

FN3403 Rev.5.00 Page 8 of 9

Mar 4, 2010

ICL7621

Small Outline Plastic Packages (SOIC)

N

M8.15 (JEDEC MS-012-AA ISSUE C)

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

INDEX

AREA H 0.25(0.010) M B M

INCHES MILLIMETERS

E

SYMBOL MIN MAX MIN MAX NOTES

-B-

A 0.0532 0.0688 1.35 1.75 -

1 2 3 A1 0.0040 0.0098 0.10 0.25 -

L

B 0.013 0.020 0.33 0.51 9

SEATING PLANE C 0.0075 0.0098 0.19 0.25 -

-A-

A h x 45°

D 0.1890 0.1968 4.80 5.00 3

D

E 0.1497 0.1574 3.80 4.00 4

-C- e 0.050 BSC 1.27 BSC -

H 0.2284 0.2440 5.80 6.20 -

e A1

C h 0.0099 0.0196 0.25 0.50 5

B 0.10(0.004)

L 0.016 0.050 0.40 1.27 6

0.25(0.010) M C A M B S

N 8 8 7

NOTES: 0° 8° 0° 8° -

1. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of Rev. 1 6/05

Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006

inch) per side.

4. Dimension “E” does not include interlead flash or protrusions. Inter-

lead flash and protrusions shall not exceed 0.25mm (0.010 inch) per

side.

5. The chamfer on the body is optional. If it is not present, a visual index

feature must be located within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The lead width “B”, as measured 0.36mm (0.014 inch) or greater

above the seating plane, shall not exceed a maximum value of

0.61mm (0.024 inch).

10. Controlling dimension: MILLIMETER. Converted inch dimensions

are not necessarily exact.

© Copyright Intersil Americas LLC 2001-2010. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted

in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such

modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are

current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its

subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN3403 Rev.5.00 Page 9 of 9

Mar 4, 2010

Você também pode gostar

- Banachek UnlimitedDocumento34 páginasBanachek UnlimitedserenaAinda não há avaliações

- The Unofficial Aterlife GuideDocumento33 páginasThe Unofficial Aterlife GuideIsrael Teixeira de AndradeAinda não há avaliações

- 10th Aug. 2011 Structural Calculation (For Sub.) - 03Documento29 páginas10th Aug. 2011 Structural Calculation (For Sub.) - 03Nguyễn Tiến Việt100% (1)

- Report - IvatanDocumento28 páginasReport - IvatanJohara Winel PerezAinda não há avaliações

- Moses ManualDocumento455 páginasMoses ManualDadypeesAinda não há avaliações

- Overall Method StatementDocumento33 páginasOverall Method Statementsaranga100% (1)

- Intumescent Paint For Steel NZ - Coating - Co.nzDocumento8 páginasIntumescent Paint For Steel NZ - Coating - Co.nzPeter ThomsonAinda não há avaliações

- Prawn ProcessingDocumento21 páginasPrawn ProcessingKrishnaAinda não há avaliações

- Leica CM1850 IFU 2v6C en PDFDocumento54 páginasLeica CM1850 IFU 2v6C en PDFPaulo GoesAinda não há avaliações

- IPHS Guidelines For District Hospitals (101 To 500 Bedded) PDFDocumento124 páginasIPHS Guidelines For District Hospitals (101 To 500 Bedded) PDFSatish Vaidya67% (3)

- Siemens Servo-I Ventilator - Service Manual PDFDocumento70 páginasSiemens Servo-I Ventilator - Service Manual PDFРинат Жахин100% (1)

- Pharmd CurriculumDocumento18 páginasPharmd Curriculum5377773Ainda não há avaliações

- Ci 7621Documento9 páginasCi 7621Ezsilvasilva SilvaAinda não há avaliações

- ICL7611-1.4MHz, Low Power CMOS Operational AmplifiersDocumento13 páginasICL7611-1.4MHz, Low Power CMOS Operational Amplifiersy0956880Ainda não há avaliações

- 100V/2A Peak, Low Cost, High Frequency Half Bridge Driver FeaturesDocumento13 páginas100V/2A Peak, Low Cost, High Frequency Half Bridge Driver FeaturescarcavaAinda não há avaliações

- Features: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierDocumento5 páginasFeatures: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierAlexandre Correa100% (1)

- Icl7650s Cba-1zDocumento13 páginasIcl7650s Cba-1zmarcodlcruz94Ainda não há avaliações

- Features: 110Mhz, High Slew Rate, High Output Current BufferDocumento12 páginasFeatures: 110Mhz, High Slew Rate, High Output Current BufferPepe ChorizoAinda não há avaliações

- Ca 3260Documento4 páginasCa 3260Carlos TibussiAinda não há avaliações

- Features: High Supply Voltage 220Mhz Unity-Gain Stable Operational AmplifierDocumento13 páginasFeatures: High Supply Voltage 220Mhz Unity-Gain Stable Operational AmplifiersdasfaAinda não há avaliações

- Icl 7667Documento11 páginasIcl 7667De JeanAinda não há avaliações

- NE/SA/SE5532/5532A: Internally-Compensated Dual Low Noise Operational AmplifierDocumento13 páginasNE/SA/SE5532/5532A: Internally-Compensated Dual Low Noise Operational AmplifierOmar QuintanillaAinda não há avaliações

- NE/SA/SE5532/5532A: Internally-Compensated Dual Low Noise Operational AmplifierDocumento12 páginasNE/SA/SE5532/5532A: Internally-Compensated Dual Low Noise Operational Amplifiersaul camposAinda não há avaliações

- HCPL 7601 AvagoDocumento13 páginasHCPL 7601 AvagoSyed Khawar MukhtarAinda não há avaliações

- Jameco Part Number 1762453: Distributed byDocumento7 páginasJameco Part Number 1762453: Distributed byIkram BalochAinda não há avaliações

- CA5260, CA5260A: FeaturesDocumento7 páginasCA5260, CA5260A: FeaturesCharbel TadrosAinda não há avaliações

- DatasheetDocumento12 páginasDatasheetAsad AhmedAinda não há avaliações

- Features: Automatic Battery Back-Up SwitchDocumento8 páginasFeatures: Automatic Battery Back-Up SwitchdeepakgkdAinda não há avaliações

- Sip32431 RC VishayDocumento14 páginasSip32431 RC VishayYargen GonzalezAinda não há avaliações

- Single-Channel: 6N138, 6N139 Dual-Channel: HCPL-2730, HCPL-2731 Low Input Current High Gain Split Darlington OptocouplersDocumento15 páginasSingle-Channel: 6N138, 6N139 Dual-Channel: HCPL-2730, HCPL-2731 Low Input Current High Gain Split Darlington Optocouplersdevrim.kosalAinda não há avaliações

- Safa Micro hw-1Documento30 páginasSafa Micro hw-1suhailhajajjiAinda não há avaliações

- Ina 129Documento29 páginasIna 129Victor Hugo OrtizAinda não há avaliações

- 4.5-V To 65-V Input, Compact Bias Supply With Power Stage Reference Design For Igbt/Sic Gate DriversDocumento44 páginas4.5-V To 65-V Input, Compact Bias Supply With Power Stage Reference Design For Igbt/Sic Gate DriversDebasish MishraAinda não há avaliações

- Icl7667 1528911Documento12 páginasIcl7667 1528911Trung Nguyên VõAinda não há avaliações

- REN Isl84714 DST 20010407Documento10 páginasREN Isl84714 DST 20010407siltnafxxxgmail.com wongAinda não há avaliações

- str-l472 Ds enDocumento2 páginasstr-l472 Ds enJuan Diego Chavarría RojasAinda não há avaliações

- TPS7A7001 Very Low Input, Very Low Dropout, 2-Amp Regulator With EnableDocumento23 páginasTPS7A7001 Very Low Input, Very Low Dropout, 2-Amp Regulator With EnableXiong ChwAinda não há avaliações

- Iqan-Xs: Electronic Remote ControlsDocumento2 páginasIqan-Xs: Electronic Remote ControlsVăn ĐạtAinda não há avaliações

- ISO5500 2.5-A Isolated IGBT, MOSFET Gate Driver: 1 Features 3 DescriptionDocumento45 páginasISO5500 2.5-A Isolated IGBT, MOSFET Gate Driver: 1 Features 3 DescriptionBubai BhattacharyyaAinda não há avaliações

- INA12x Precision, Low-Power Instrumentation Amplifiers: 1 Features 3 DescriptionDocumento29 páginasINA12x Precision, Low-Power Instrumentation Amplifiers: 1 Features 3 DescriptionLuis Zavala100% (1)

- Tsop 752 WDocumento13 páginasTsop 752 WMatias RendonAinda não há avaliações

- ISL6455 RenesasDocumento13 páginasISL6455 RenesasArief MandolloAinda não há avaliações

- Features: EL5202, EL5203Documento14 páginasFeatures: EL5202, EL5203Евгений ИвановAinda não há avaliações

- Sip 32431Documento15 páginasSip 32431Remy MendozaAinda não há avaliações

- TSOP752.., TSOP754..: Vishay SemiconductorsDocumento13 páginasTSOP752.., TSOP754..: Vishay SemiconductorsMaktum KamatAinda não há avaliações

- EPS 901-123 - Rev R - IOPDocumento2 páginasEPS 901-123 - Rev R - IOPFarhan YassarAinda não há avaliações

- Super Voltage Converter Features: ICL7660SDocumento12 páginasSuper Voltage Converter Features: ICL7660SyoAinda não há avaliações

- DB en Ib Il 24 Do 16 5559 en 04Documento9 páginasDB en Ib Il 24 Do 16 5559 en 04Gergő FaragóAinda não há avaliações

- TL - 080 PDFDocumento12 páginasTL - 080 PDFmichael luqueAinda não há avaliações

- Cio 116 Data Sheet 4921240524 UkDocumento10 páginasCio 116 Data Sheet 4921240524 UkSergio Andres MurilloAinda não há avaliações

- Texas-Instruments-TPS61021ADSGR C193037Documento34 páginasTexas-Instruments-TPS61021ADSGR C193037Bryan LopezAinda não há avaliações

- Tps 63010Documento27 páginasTps 63010Farouk AnçaAinda não há avaliações

- Ina 168Documento27 páginasIna 168Merlin SithAinda não há avaliações

- Features: CMOS Voltage ConvertersDocumento12 páginasFeatures: CMOS Voltage ConvertersAlexAinda não há avaliações

- Datasheet - HK hcpl-2731 92412Documento13 páginasDatasheet - HK hcpl-2731 92412Anonymous aP1FSUPoAinda não há avaliações

- DatasheetDocumento26 páginasDatasheetmas-nhAinda não há avaliações

- Max11359A 16-Bit Data-Acquisition System With Adc, Dac, Upios, RTC, Voltage Monitors, and Temp SensorDocumento67 páginasMax11359A 16-Bit Data-Acquisition System With Adc, Dac, Upios, RTC, Voltage Monitors, and Temp SensorM. Ahmad RazaAinda não há avaliações

- EPS 9492-PS-PLUS Rev 2Documento2 páginasEPS 9492-PS-PLUS Rev 2Procurement PardisanAinda não há avaliações

- AD706JNDocumento12 páginasAD706JNapi-3825669Ainda não há avaliações

- PAM8006A: A Product Line of Diodes IncorporatedDocumento13 páginasPAM8006A: A Product Line of Diodes IncorporatedSimilinga MnyongeAinda não há avaliações

- High Speed, Dual, 4 A MOSFET Driver: Data SheetDocumento13 páginasHigh Speed, Dual, 4 A MOSFET Driver: Data Sheet나야나Ainda não há avaliações

- TS922, TS922A: Rail-To-Rail, High Output Current Dual Operational AmplifierDocumento24 páginasTS922, TS922A: Rail-To-Rail, High Output Current Dual Operational AmplifiercurzAinda não há avaliações

- TPS6106x Constant Current LED Driver With Digital and PWM Brightness ControlDocumento29 páginasTPS6106x Constant Current LED Driver With Digital and PWM Brightness ControlShames ElhoryaAinda não há avaliações

- 2.5A, 18V, 500Khz Acot Synchronous Step-Down Converter: General Description FeaturesDocumento14 páginas2.5A, 18V, 500Khz Acot Synchronous Step-Down Converter: General Description FeaturesMaxAinda não há avaliações

- Ina190 PDFDocumento45 páginasIna190 PDFVlad MoiseAinda não há avaliações

- Dual Power MOSFET Driver Features: File Number Data Sheet April 1999Documento8 páginasDual Power MOSFET Driver Features: File Number Data Sheet April 1999tommyhghAinda não há avaliações

- 103 - Tidu449bDocumento92 páginas103 - Tidu449bMahdi TavassoliAinda não há avaliações

- 6N137, HCNW137, HCNW2601, HCNW2611, HCPL-0600, HCPL-0601, HCPL-0611, HCPL-0630, HCPL-0631, HCPL-0661, HCPL-2601, HCPL-2611, HCPL-2630, HCPL-2631, HCPL-4661Documento30 páginas6N137, HCNW137, HCNW2601, HCNW2611, HCPL-0600, HCPL-0601, HCPL-0611, HCPL-0630, HCPL-0631, HCPL-0661, HCPL-2601, HCPL-2611, HCPL-2630, HCPL-2631, HCPL-4661haAinda não há avaliações

- HCPL 7710 300 AvagoDocumento19 páginasHCPL 7710 300 Avagohanif khanAinda não há avaliações

- HCPL 7710 300 AvagoDocumento19 páginasHCPL 7710 300 Avagohanif khanAinda não há avaliações

- ABB Semiconductors. Power Semiconductors Product Brochure 2016 PDFDocumento40 páginasABB Semiconductors. Power Semiconductors Product Brochure 2016 PDFnavaron64Ainda não há avaliações

- Phototherapymachin MonitorDocumento7 páginasPhototherapymachin MonitorDibya DeyAinda não há avaliações

- Acrylic Wall Putty PDFDocumento2 páginasAcrylic Wall Putty PDFD_Vijay_Krishn_975Ainda não há avaliações

- Standard Pitch Diameter ChartDocumento5 páginasStandard Pitch Diameter ChartDibya DeyAinda não há avaliações

- Our Commitment Makes The Difference!: Company Presentation Our Mission Activities & Services Quality ManagementDocumento12 páginasOur Commitment Makes The Difference!: Company Presentation Our Mission Activities & Services Quality ManagementDibya DeyAinda não há avaliações

- The Innovative Versatile Transport Incubator Works With Any Environment EfficientlyDocumento4 páginasThe Innovative Versatile Transport Incubator Works With Any Environment EfficientlyDibya DeyAinda não há avaliações

- LG Refrigerator Compressor CatalogueDocumento11 páginasLG Refrigerator Compressor CatalogueMilos Lazovic73% (11)

- RTD Temperature vs. Resistance TableDocumento4 páginasRTD Temperature vs. Resistance TableNAYEEMAinda não há avaliações

- IntroductiontoFluoroscopySafety8 20 13Documento39 páginasIntroductiontoFluoroscopySafety8 20 13vasty.overbeek100% (1)

- Installation and User Manual: All Rights ReservedDocumento28 páginasInstallation and User Manual: All Rights ReservedDibya DeyAinda não há avaliações

- lp339 The CDocumento13 páginaslp339 The CDibya DeyAinda não há avaliações

- Refrigerator Make RemiDocumento4 páginasRefrigerator Make RemiDibya DeyAinda não há avaliações

- LV Injector Manufacturer SpecificationsDocumento1 páginaLV Injector Manufacturer SpecificationsDibya DeyAinda não há avaliações

- l6566b Ic DatasheetDocumento51 páginasl6566b Ic DatasheetDibya DeyAinda não há avaliações

- Electrical Safety - 0 PDFDocumento3 páginasElectrical Safety - 0 PDFSATISH MALVIYAAinda não há avaliações

- CI ULN2003A - Depe Placa de Cda A Senzorului RX PDFDocumento9 páginasCI ULN2003A - Depe Placa de Cda A Senzorului RX PDFRata IonAinda não há avaliações

- Sa1 PDFDocumento1 páginaSa1 PDFDibya DeyAinda não há avaliações

- Qfix Payment Consolidated Fee Receipt PDFDocumento1 páginaQfix Payment Consolidated Fee Receipt PDFDibya Dey100% (1)

- 1986 EMT Disruption of Microbial Cells For Intracellular ProductsDocumento11 páginas1986 EMT Disruption of Microbial Cells For Intracellular ProductsLezid CortesAinda não há avaliações

- Navy Supplement To The DOD Dictionary of Military and Associated Terms, 2011Documento405 páginasNavy Supplement To The DOD Dictionary of Military and Associated Terms, 2011bateljupko100% (1)

- Single Door Feeder Pillar 200A MCCBDocumento1 páginaSingle Door Feeder Pillar 200A MCCBMiqdad AliAinda não há avaliações

- Sudip Praposal - 1Documento20 páginasSudip Praposal - 1Usha BbattaAinda não há avaliações

- SAT Biochar Ethylene Poster 10 - 10b PDFDocumento1 páginaSAT Biochar Ethylene Poster 10 - 10b PDFsherifalharamAinda não há avaliações

- The Ieee Test System Methods: Reliability ofDocumento11 páginasThe Ieee Test System Methods: Reliability ofFsdaSdsAinda não há avaliações

- RhythmDocumento10 páginasRhythmSalcedo NoelAinda não há avaliações

- Full Download Short Term Financial Management 3rd Edition Maness Test BankDocumento35 páginasFull Download Short Term Financial Management 3rd Edition Maness Test Bankcimanfavoriw100% (31)

- Mathematical Modeling of Mechanical Systems and Electrical SystemsDocumento49 páginasMathematical Modeling of Mechanical Systems and Electrical SystemsMary DunhamAinda não há avaliações

- ReviewerDocumento3 páginasReviewerKristine SantominAinda não há avaliações

- Chennai To Vishakhapatnam El6Vvd: Indigo 6E-6835Documento3 páginasChennai To Vishakhapatnam El6Vvd: Indigo 6E-6835VENKATESH POONDRUAinda não há avaliações

- A Textual Introduction To Acarya Vasuvan PDFDocumento3 páginasA Textual Introduction To Acarya Vasuvan PDFJim LeeAinda não há avaliações

- Electrical Power System Device Function NumberDocumento2 páginasElectrical Power System Device Function Numberdan_teegardenAinda não há avaliações

- Class 12 - Maths - MatricesDocumento87 páginasClass 12 - Maths - MatricesAishwarya MishraAinda não há avaliações

- S590 Machine SpecsDocumento6 páginasS590 Machine SpecsdilanAinda não há avaliações

- Egt Margen From The Best ArticalDocumento6 páginasEgt Margen From The Best ArticalakeelAinda não há avaliações

- Easergy PS100 48VDC Power SupplyDocumento2 páginasEasergy PS100 48VDC Power SupplyRichard SyAinda não há avaliações

- Germania Agenturinfo enDocumento4 páginasGermania Agenturinfo enДушан СтепановићAinda não há avaliações

- Updated SAP Cards Requirement JalchdDocumento51 páginasUpdated SAP Cards Requirement Jalchdapi-3804296Ainda não há avaliações

- Physics 101Documento21 páginasPhysics 101Kuna KunavathiAinda não há avaliações

- Tabel Gsi, RMR, RmiDocumento4 páginasTabel Gsi, RMR, RmiPup BooAinda não há avaliações