Escolar Documentos

Profissional Documentos

Cultura Documentos

DD Handout

Enviado por

AsdgjkTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

DD Handout

Enviado por

AsdgjkDireitos autorais:

Formatos disponíveis

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, Pilani

Pilani Campus

Instruction Division

Date: 02/08/2017

FIRST SEMESTER 2017-2018

In addition to Part-I (General Handout for all courses appended to the timetable) this portion

gives further specific details regarding the course.

Course Handout

Course No : CS F 215/ EEE F215 / INSTR F215

Course Title : Digital Design

Instructor-in-charge : Dr. Pawan K. Ajmera (pawan.ajmera@pilani.bits-pilani.ac.in)

Instructors for Lecture : Dr. Nitin Chaturvedi, Dr. Pawan K. Ajmera.

Tutorial Instructors : Prof. S. Mohan, Pawan K. Ajmera,

Dr. Asutosh Kar, Mr. Harshvardhan

Practical Instructors : Tulsi Ram Sharma, Abheek Gupta, Ravinder Kumar, Dhananjay,

Prateek Bindra, Punit Khatri

Scope and Objective: The objective of the course is to impart knowledge of the basic

tools for the design of digital circuits and to provide methods and procedures suitable

for a variety of digital design applications.

Text Books :

T1: M. Moris Mano and Michael D. Ciletti “Digital Design”, PHI, 5th Edition, 2013.

T2: G. Raghurama, S. Gurunarayanan, S. Mohan, Karthik, “Laboratory Manual”, EDD

notes 2007.

Reference Books:

R1: Ronald J. Tocci and Neal S. Widmer, “Digital Systems-Principles and Application”,

Pearson, 10th Edition, 2007.

R2: Thomas l. Floyd, “Digital Fundamentals,” Pearson, 9th Edition, 20

R2: Donald D. Givonne, “Digital Principles and Design” TMH, 2003

Please Do Not Print Unless Necessary

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, Pilani

Pilani Campus

Instruction Division

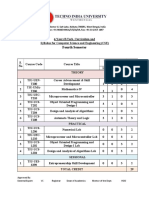

Course Plan

Lecture

Main Topic Contents Reference

No.

01 Introduction Introduction to Digital systems and characteristics

Number systems Digital, Binary, Octal and Hexadecimal, Number-Base T1:1.1-1.9

02

and codes Conversions, Complements, Signed Binary Numbers.

Logic Gates and Digital Logic Gates, Truth Table, Boolean Algebra, Theorems T1:2.1-2.8

03

Boolean Algebra and Properties, Boolean Functions, Canonical and Std. forms.

Minimization Gate-Level Minimization, The Karnaugh Map Method, T1:3.1-3.8

04-05

Techniques Quine-McCluskey Method

Simulation and Hardware Description Language (Verilog HDL) T1:3.11

07

synthesis

Introduction, Analysis and Design Procedure, Binary Adder- T1:4.1-4.7

Combinational

08-11 Subtractor, Decimal Adder, Binary Multiplier, HDL Models of T1:4.12

Logic Circuits

Combinational Circuits.

Sequential Logic Introduction, Storage Elements: Latches and Flip-Flops. T1:5.1-5.4

12-13

Circuits

Magnitude Comparator, Decoders, Encoders, Multiplexers, T1:4.8-

14-18 MSI Logic Circuits

HDL Models of Combinational Circuits. 4.12

Analysis of Clocked Sequential Circuits, State Reduction and T1:5.5-5.8

Synchronous

19-23 Assignment, Design Procedure, HDL Models of Sequential

Sequential circuits

Circuits

Registers and Registers, Shift Registers, Ripple Counters, Synchronous T1:6.1-6.5

24-28

Counters Counters, HDL for Registers and Counters

Introduction, Random-Access Memory, Memory Decoding, T1:7.1-7.8

Memory and

29-32 Error Detection and Correction, Read-Only Memory,

PLD’s

Programmable Logic Array, Programmable Array Logic

Design of Digital Register Transfer Level (RTL) Notation, Algorithmic State T1:8.1-8.8

33-37

Systems Machines (ASMs), HDL description.

Digital Integrated TTL, MOS Logic families and characteristics. T1:10.1-

38-40

Circuits 10.9

Evaluation Scheme:

EC No. Evaluation Component Duration Marks Date and Time Nature of Component

1 Weekly Quiz 10 Min 45 Continuous Close Book

Laboratory

2 180 Min 12 + 33 Continuous Close Book

(Attendance + Lab exam)

10/10 2:00 -

3 Mid-Semester Exam 90 Min 90 Close Book

3:30 PM

_

Please Do Not Print Unless Necessary

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, Pilani

Pilani Campus

Instruction Division

4 Comprehensive Exam 180 Min 120 5/12 FN Open/Close Book

Total 300

Practicals

S.No. Name of experiment

1. BOOLEAN FUNCTIONS IMPLEMENTATION

2. DESIGN OF ARITHMATIC CIRCUITS

3. IMPLEMENTATION OF BCD ADDER

4. DECODERS, MULTIPLEXERS AND DEMULTIPLEXERS

5. LATCHES & FLIP-FLOPS

6. OPERATION OF A 4-BIT COUNTER

7. COMPARATORS & ARITHMETIC LOGIC UNIT

8. COUNTER DESIGN

9. SHIFT REGISTERS

10. DESIGN OF SEQUENCE DETECTOR

11. MEMORIES AND FPGAS

Assignments: There will be simulation based assignments, which will be as take home assignments.

Chamber Consultation Hours: To be announced in the class.

Notices: Notices regarding the course will be displayed only on the EEE (FD II) notice

board/NALANDA.

Makeup Policy: Makeup will be granted to extremely genuine cases only, provided the IC has been

informed.

Instructor - in - charge

CS F215/ EEE F215 / INSTR F215

Please Do Not Print Unless Necessary

Você também pode gostar

- Birla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionDocumento4 páginasBirla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionTrideeb BhattacharyaAinda não há avaliações

- Digital Signal Processing: A Practical Guide for Engineers and ScientistsNo EverandDigital Signal Processing: A Practical Guide for Engineers and ScientistsNota: 4.5 de 5 estrelas4.5/5 (7)

- DDDocumento3 páginasDDJAY JANAK MANEKAinda não há avaliações

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Documento3 páginasCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Deepti MishraAinda não há avaliações

- Bits PilaniDocumento3 páginasBits PilaniasdmddamcAinda não há avaliações

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Documento4 páginasCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24f20220264Ainda não há avaliações

- Ece F215 Digital Design - HandoutDocumento3 páginasEce F215 Digital Design - HandoutRishiAinda não há avaliações

- Page 1 of 2: W.E.F. AY 2018-19Documento2 páginasPage 1 of 2: W.E.F. AY 2018-19Jenny BhadouriyaAinda não há avaliações

- Digital Electronics Course OutlineDocumento15 páginasDigital Electronics Course OutlineYash KuncolienkerAinda não há avaliações

- BITS Pilani Signals & Systems Course DetailsDocumento3 páginasBITS Pilani Signals & Systems Course Detailssaurjyesh nayakAinda não há avaliações

- Digital Design Course HandoutDocumento4 páginasDigital Design Course HandoutShubham RohilaAinda não há avaliações

- Uttarakhand Technical University Dehradun: Study and Evaluation Scheme (B.Tech. Iii Year)Documento7 páginasUttarakhand Technical University Dehradun: Study and Evaluation Scheme (B.Tech. Iii Year)Ankit SharmaAinda não há avaliações

- 15ec751 DSP AlogorithmsDocumento40 páginas15ec751 DSP AlogorithmsSudheer BabuAinda não há avaliações

- Department Electronics Communication Course PlanDocumento4 páginasDepartment Electronics Communication Course PlansarvanmeAinda não há avaliações

- Digital Electronics and Computer OrganizationDocumento3 páginasDigital Electronics and Computer OrganizationSai Prajwal SavanamAinda não há avaliações

- Handout DSP Ece Eee f434Documento2 páginasHandout DSP Ece Eee f434Nitesh JainAinda não há avaliações

- CHHATTISGARH SWAMI VIVEKANAND TECHNICAL UNIVERSITY, BHILAI DIPLOMA PROGRAMME IN INFORMATION TECHNOLOGYDocumento20 páginasCHHATTISGARH SWAMI VIVEKANAND TECHNICAL UNIVERSITY, BHILAI DIPLOMA PROGRAMME IN INFORMATION TECHNOLOGYshriram1082883Ainda não há avaliações

- IT3L3 Digital System Design Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 Marks ObjectivesDocumento2 páginasIT3L3 Digital System Design Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 Marks ObjectivesVyshnavi ThottempudiAinda não há avaliações

- Digital Design: Cs/Eee/Ece /instr F215Documento34 páginasDigital Design: Cs/Eee/Ece /instr F215SIDDHANT RAVINDRA KULKARNIAinda não há avaliações

- M.Tech ECE SyllabusDocumento4 páginasM.Tech ECE Syllabuspaku deyAinda não há avaliações

- Academic Course DescriptionDocumento8 páginasAcademic Course DescriptionRajalearn2 Ramlearn2Ainda não há avaliações

- Number System and CodesDocumento300 páginasNumber System and Codes011S6Amit PandeyAinda não há avaliações

- Course Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentDocumento6 páginasCourse Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentAbdullah SohailAinda não há avaliações

- SY Btech E&TC Syllabus - 2!03!2021Documento40 páginasSY Btech E&TC Syllabus - 2!03!2021legad40026Ainda não há avaliações

- Course Description Form (CDF) Digital Signal Processing EEE324 - Updated 4Documento10 páginasCourse Description Form (CDF) Digital Signal Processing EEE324 - Updated 4Huzaifa YasirAinda não há avaliações

- Fourth Semester: S. No Course Code Course Title Contact Hrs. / Week Credit L T PDocumento10 páginasFourth Semester: S. No Course Code Course Title Contact Hrs. / Week Credit L T Pjiman84235Ainda não há avaliações

- Updated Course Outline EE 221 - Digital - Logic - Design - Spring - 2023Documento9 páginasUpdated Course Outline EE 221 - Digital - Logic - Design - Spring - 2023Laiqa AliAinda não há avaliações

- Aei-5th & 6TH Sem23062008Documento44 páginasAei-5th & 6TH Sem23062008War MachineAinda não há avaliações

- Attachment Circular 2023081115025923 Ic 001Documento9 páginasAttachment Circular 2023081115025923 Ic 001shivam.cs667Ainda não há avaliações

- Birla Institute of Technology & Science, Pilani Hyderabad Campus Second Semester 2018-2019 Course Handout (Part-II) 07-01-2019Documento3 páginasBirla Institute of Technology & Science, Pilani Hyderabad Campus Second Semester 2018-2019 Course Handout (Part-II) 07-01-2019PriAinda não há avaliações

- GTU Digital Electronics Course OverviewDocumento3 páginasGTU Digital Electronics Course OverviewBhargavsinh ParmarAinda não há avaliações

- BITS Course Handout: Introduction to MEMSDocumento5 páginasBITS Course Handout: Introduction to MEMSParth SoodanAinda não há avaliações

- DDE 1313 Digital Electronics 1 LODocumento6 páginasDDE 1313 Digital Electronics 1 LOAhmad FadzlyAinda não há avaliações

- 05 Unit V DTEDocumento217 páginas05 Unit V DTEKrunal WaniAinda não há avaliações

- 311001-Fundamentals of Ict SyllabusDocumento10 páginas311001-Fundamentals of Ict SyllabusSuriRawatAinda não há avaliações

- Chhattisgarh Swami Vivekanand Technical University, BhilaiDocumento22 páginasChhattisgarh Swami Vivekanand Technical University, Bhilaibheshram janghelAinda não há avaliações

- dtev-180916171027Documento217 páginasdtev-180916171027vaishnavi biradarAinda não há avaliações

- Birla Institute of Technology & Science, Pilani Instruction Division FIRST SEMESTER 2017 - 2018 Course Handout (Part Ii)Documento2 páginasBirla Institute of Technology & Science, Pilani Instruction Division FIRST SEMESTER 2017 - 2018 Course Handout (Part Ii)prabhatAinda não há avaliações

- ECE-VII-DSP ALGORITHMS & ARCHITECTURE Part ADocumento111 páginasECE-VII-DSP ALGORITHMS & ARCHITECTURE Part AmanjumathgowdaAinda não há avaliações

- Deca ChoDocumento9 páginasDeca ChoTARANGITAinda não há avaliações

- Semester VI course detailsDocumento7 páginasSemester VI course detailsHarsh KumarAinda não há avaliações

- EE-355 Digital Communication Systems OverviewDocumento4 páginasEE-355 Digital Communication Systems OverviewMarina KhanAinda não há avaliações

- EE407 Digital Signal ProcessingDocumento2 páginasEE407 Digital Signal ProcessingbibuthomasAinda não há avaliações

- Ece VII DSP Algorithms Architecture 10ec751 Notes PDFDocumento181 páginasEce VII DSP Algorithms Architecture 10ec751 Notes PDFManojAinda não há avaliações

- ME F320 Engineering OptimizationDocumento5 páginasME F320 Engineering OptimizationARYAAN PARIDAAinda não há avaliações

- RTS SyllabusDocumento3 páginasRTS SyllabusthejasAinda não há avaliações

- Syallbus B. Tech CSE First YearDocumento12 páginasSyallbus B. Tech CSE First YearRishav RajAinda não há avaliações

- Digital ElectronicsDocumento2 páginasDigital ElectronicsretheeshvkmAinda não há avaliações

- CS C363Documento3 páginasCS C363Aravind KondamudiAinda não há avaliações

- CP16036Documento6 páginasCP16036Sankar TerliAinda não há avaliações

- B Tech CIVIL Engineering CurriculumDocumento36 páginasB Tech CIVIL Engineering CurriculumG Ravi Kiran HSCAinda não há avaliações

- Digital Design EEE F215 HandoutDocumento3 páginasDigital Design EEE F215 HandoutHarshilGargAinda não há avaliações

- Bits g553 Real Time SystemsDocumento2 páginasBits g553 Real Time SystemsUriti Venkata Naga KishoreAinda não há avaliações

- Don Bosco Institute of Technology: Course Syllabi With CO'sDocumento2 páginasDon Bosco Institute of Technology: Course Syllabi With CO'sprashantgeminiAinda não há avaliações

- CP Je Tele PH1Documento2 páginasCP Je Tele PH1Sagnik ChakrabortyAinda não há avaliações

- UT Dallas Syllabus For Ee4361.501.08f Taught by Issa Panahi (Imp015000)Documento2 páginasUT Dallas Syllabus For Ee4361.501.08f Taught by Issa Panahi (Imp015000)UT Dallas Provost's Technology GroupAinda não há avaliações

- DPSD CS8351 U1 PDFDocumento182 páginasDPSD CS8351 U1 PDFPragna SidhireddyAinda não há avaliações

- BITS Pilani Goa Campus Course on VLSI DesignDocumento3 páginasBITS Pilani Goa Campus Course on VLSI DesignNitu SharmaAinda não há avaliações

- Sas Handour EEE f243Documento3 páginasSas Handour EEE f243johnmechanjiAinda não há avaliações

- Birla Institute of Technology and Science, Pilani Set-ADocumento2 páginasBirla Institute of Technology and Science, Pilani Set-AAsdgjkAinda não há avaliações

- Eg With Auto CadDocumento23 páginasEg With Auto CadDeepak DahiyaAinda não há avaliações

- MMVY Guidelines for Fee ReimbursementDocumento4 páginasMMVY Guidelines for Fee ReimbursementrocinguyAinda não há avaliações

- SeatingArrangementStudent PDFDocumento1 páginaSeatingArrangementStudent PDFAsdgjkAinda não há avaliações

- Linha HP COMPAQ PRO 6300 SMALL FORM FACTOR-14269 - Div PDFDocumento65 páginasLinha HP COMPAQ PRO 6300 SMALL FORM FACTOR-14269 - Div PDFredepiresAinda não há avaliações

- Screw Jack ReportDocumento9 páginasScrew Jack ReportAmar100% (3)

- Award Bios 4.51PG Postcodes PDFDocumento3 páginasAward Bios 4.51PG Postcodes PDFandresviglinoAinda não há avaliações

- VM665 - Student Exercises - P PDFDocumento218 páginasVM665 - Student Exercises - P PDFNacho Ponisio100% (1)

- FileDocumento114 páginasFilevaibhav shuklaAinda não há avaliações

- IT EssentialsDocumento56 páginasIT EssentialsDaniel ErgichoAinda não há avaliações

- 6 Cylinder Head - ValveDocumento14 páginas6 Cylinder Head - ValveSaraAinda não há avaliações

- 2 RRU DBS and BTS Introduction and Hardware Installation PDFDocumento74 páginas2 RRU DBS and BTS Introduction and Hardware Installation PDFikhlas boutayebAinda não há avaliações

- Presentation On Transmission Line TowersDocumento72 páginasPresentation On Transmission Line TowersAhmed MostafaAinda não há avaliações

- EFINITIONDocumento7 páginasEFINITIONSanduni kaushalyaAinda não há avaliações

- 735-061221-00x GForceType12 Graphical InstallationDocumento8 páginas735-061221-00x GForceType12 Graphical InstallationFranco AlmonacidAinda não há avaliações

- Krohne IFC 010 ManualDocumento67 páginasKrohne IFC 010 ManualDnyaneshwar PatilAinda não há avaliações

- Digital TD Controller: For NEXO PS Series Cabinets and LS SubsDocumento2 páginasDigital TD Controller: For NEXO PS Series Cabinets and LS SubsrummanhzAinda não há avaliações

- HP Integrity Virtual Machines 4.3: Release Notes: HP Part Number: 5900-1828 Published: August 2011, Edition 15.0Documento50 páginasHP Integrity Virtual Machines 4.3: Release Notes: HP Part Number: 5900-1828 Published: August 2011, Edition 15.0Satish MadhanaAinda não há avaliações

- Create An Ebook Table of Contents in Microsoft WordDocumento9 páginasCreate An Ebook Table of Contents in Microsoft WordDion ShawAinda não há avaliações

- St. Joseph’s senior secondary school Navi Mumbai C++ Tic-Tac-Toe gameDocumento20 páginasSt. Joseph’s senior secondary school Navi Mumbai C++ Tic-Tac-Toe gameMurtuza KhambatiAinda não há avaliações

- Adva Micromux™: Support For Lower-Speed Clients Today With No Impact On Future ScalabilityDocumento2 páginasAdva Micromux™: Support For Lower-Speed Clients Today With No Impact On Future ScalabilityCyprienLaleau100% (1)

- K7VM2-R30 UmDocumento29 páginasK7VM2-R30 UmSyed Irfan BashaAinda não há avaliações

- 015-Using Tables in ANSYSDocumento4 páginas015-Using Tables in ANSYSmerlin1112255Ainda não há avaliações

- Altivar 61/71: Devicenet™ Card User'S ManualDocumento72 páginasAltivar 61/71: Devicenet™ Card User'S ManualMarcelo Alexis Pacheco CastroAinda não há avaliações

- User Guide: Lenovo E40-30, Lenovo E40-70, Lenovo E40-80, Zhao Yang E40-30, Zhao Yang E40-70 and Zhao Yang E40-80Documento74 páginasUser Guide: Lenovo E40-30, Lenovo E40-70, Lenovo E40-80, Zhao Yang E40-30, Zhao Yang E40-70 and Zhao Yang E40-80wilAinda não há avaliações

- PolyMat MainDocumento74 páginasPolyMat Mainריאל אמנם נכוןAinda não há avaliações

- Address Decoding TechniqueDocumento8 páginasAddress Decoding TechniqueYash SarohaAinda não há avaliações

- NetBackup CommandsDocumento723 páginasNetBackup Commandsruterjunior0% (1)

- LP Series Limpsfield Combustion Operating and Maintenance Manual Iss3Documento63 páginasLP Series Limpsfield Combustion Operating and Maintenance Manual Iss3hoangtien1991Ainda não há avaliações

- Locking Devices, Keys, Springs, Rivets and WeldingDocumento13 páginasLocking Devices, Keys, Springs, Rivets and WeldingSrinath SaiAinda não há avaliações

- Ferrit p3019 PDFDocumento1 páginaFerrit p3019 PDFPeggyAinda não há avaliações

- Chapter 2 DatabaseDocumento18 páginasChapter 2 DatabaseNicho GuimbaolibotAinda não há avaliações

- NotePerformer - Users GuideDocumento56 páginasNotePerformer - Users GuideDan Sannich100% (1)

- Cutting Plotter FC8600-60/75/100/130/160: Service ManualDocumento152 páginasCutting Plotter FC8600-60/75/100/130/160: Service ManualOtavio MirandaAinda não há avaliações