Escolar Documentos

Profissional Documentos

Cultura Documentos

Co Important Bits

Enviado por

Rajani Reddy0 notas0% acharam este documento útil (0 voto)

100 visualizações4 páginasTítulo original

co important bits

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

DOCX, PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato DOCX, PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

100 visualizações4 páginasCo Important Bits

Enviado por

Rajani ReddyDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato DOCX, PDF, TXT ou leia online no Scribd

Você está na página 1de 4

1 The small extremely fast, RAM’s are called as _______ [ A ]

a) Cache b) Heaps c) Accumulators d) Stacks

2 The control unit controls other units by generating ___________ [ B ]

a) Control signals b) Timing signals c) Transfer signals d) Command Signals

3 The Input devices can send information to the processor. [ A ]

a) When the SIN status flag is set b) When the data arrives regardless of the SIN

flag c) Neither of the cases d) Either of the cases

4 ______ bus structure is usually used to connect I/O devices. [ A ]

a) Single bus b) Multiple bus c) Star bus d) Rambus

5 The I/O interface required to connect the I/O device to the bus consists of ______ [C]

a) Address decoder and registers b) Control circuits

c) Address decoder, registers and Control circuits d) Only Control circuits

6 To reduce the memory access time we generally make use of ______ [ D ]

a) Heaps b) Higher capacity RAM’s c) SDRAM’s d) Cache’s

7 The standard SRAM chips are costly as _________ [ B ]

a) They use highly advanced micro-electronic devices b) They house 6 transistor

per chip c) They require specially designed PCB’s d) None

8 The drawback of building a large memory with DRAM is ______________ [ C ]

a) The large cost factor b) The inefficient memory organisation

c) The Slow speed of operation d) All of the mentioned

9 The fastest data access is provided using _______ [D ]

a) Caches b) DRAM’s c) SRAM’s d) Registers

10 5. The memory which is used to store the copy of data or instructions stored in larger [ A ]

memories, inside the CPU is called _______

a) Level 1 cache b) Level 2 cache c) Registers d) TLB

11 The larger memory placed between the primary cache and the memory is called [ B ]

______

a) Level 1 cache b) Level 2 cache c) EEPROM d) TLB

12 The next level of memory hierarchy after the L2 cache is _______ [ D ]

a) Secondary storage b) TLB c) Main memory d) Register

13 The last on the hierarchy scale of memory devices is ______ [ B ]

a) Main memory b) Secondary memory c) TLB d) Flash drives

14 The general purpose registers are combined into a block called as ______ [ C ]

a) Register bank b) Register Case c) Register file d) None of the mentioned

15 In ______ technology, the implementation of the register file is by using an array of [ A ]

memory locations.

a) VLSI b) ANSI c) ISA d) ASCI

16 In a three BUS architecture, how many input and output ports are there? [ C ]

a) 2 output and 2 input b) 1 output and 2 input c) 2 output and 1 input

d) 1 output and 1 input

17 The main advantage of multiple bus organisation over a single bus is __________ [A ]

a) Reduction in the number of cycles for execution b) Increase in size of the

registers c) Better Connectivity d) None of the mentioned

18 CISC stands for _________ [ C ]

a) Complete Instruction Sequential Compilation b) Computer Integrated Sequential

Compiler c) Complex Instruction Set Computer d) Complex Instruction

Sequential Compilation

19 If the instruction Add R1, R2, R3 is executed in a system which is pipelined, then the [ C ]

value of S is (Where S is term of the Basic performance equation).

a) 3 b) ~2 c) ~1 d) 6

20 ______ have been developed specifically for pipelined systems. [ C ]

a) Utility software b) Speed up utilities c) Optimizing compilers

d) None of the mentioned

21 The pipelining process is also called as ______ [ B ]

a) Superscalar operation b) Assembly line operation

c) Von Neumann cycle d) None of the mentioned

22 The fetch and execution cycles are interleaved with the help of ________ [ B ]

a) Modification in processor architecture b) Clock c) Special unit d) Control unit

23 Each stage in pipelining should be completed within ___________ cycle. [ A ]

a) 1 b) 2 c) 3 d) 4

24 If a unit completes its task before the allotted time period, then _______ [B ]

a) It’ll perform some other task in the remaining time b) Its time gets

reallocated to a different task c) It’ll remain idle for the remaining time

d) None of the mentioned

25 If a unit completes its task before the allotted time period, then _______ [ C ]

a) It’ll perform some other task in the remaining time b) Its time gets reallocated to

a different task c) It’ll remain idle for the remaining time D) None

26 If a unit completes its task before the allotted time period, then _______ [ C ]

a) It’ll perform some other task in the remaining time b) Its time gets reallocated to

a different task c) It’ll remain idle for the remaining time d) None

27 To increase the speed of memory access in pipelining, we make use of _______ [ C ]

a) Special memory locations b) Special purpose registers c) Cache d) Buffers

28 The periods of time when the unit is idle is called as _____ [ D ]

a) Stalls b) Bubbles c) Hazards d) Both Stalls and Bubbles

29 The contention for the usage of a hardware device is called ______ [ A ]

a) Structural hazard b) Stalk c) Deadlock d) None

30 The situation wherein the data of operands are not available is called ______ [ A ]

a) Data hazard b) Stock c) Deadlock d) Structural hazard

31 Any condition that causes a processor to stall is called as _________ [ A ]

a) Hazard b) Page fault c) System error d) None

32 2. The periods of time when the unit is idle is called as ________ [ D ]

a) Stalls b) Bubbles c) Hazards d) Both Stalls and Bubbles

33 The contention for the usage of a hardware device is called ______ [ A ]

a) Structural hazard b) Stalk c) Deadlock d) None

34 The stalling of the processor due to the unavailability of the instructions is called as [ a ]

___________

a) Control hazard b) structural hazard c) Input hazard d) None

35 The time lost due to the branch instruction is often referred to as ____________ [ c ]

a) Latency b) Delay c) Branch penalty d) None

36 ____________ method is used in centralized systems to perform out of order [ B ]

execution.

a) Scorecard b) Score boarding c) Optimizing d) Redundancy

37 The algorithm followed in most of the systems to perform out of order execution is [A ]

__________

a) Tomasulo algorithm b) Score carding c) Reader-writer algorithm d) None

38 The problem where process concurrency becomes an issue is called as ___________ [ D]

a) Philosophers problem b) Bakery problem c) Bankers problem

d) Reader-writer problem

39 We make use of ______ circuits to implement multiplication. [ C]

a) Flip flops b) Combinatorial c) Fast adders d) None

40 . The multiplier is stored in ______ [ B ]

a) PC Register b) Shift register c) Cache d) None

41 The ______ is used to coordinate the operation of the multiplier. [ C ]

a) Controller b) Coordinator c) Control sequencer d) None

42 The method used to reduce the maximum number of summands by half is _______ [B]

a) Fast multiplication b) Bit-pair recording c) Quick multiplication d) None

43 In the Three-Segment Instruction pipeline the sequence of segments are ________ [ A ]

__________

a) Instruction Fetch, ALU operation, Execute Instruction b) ALU Operation,

Execute Instruction, Instruction Fetch c) Instruction Fetch, Execute Instruction,

ALU Operation d) Execute Instruction, ALU Operation, Instruction Fetch

44 A semaphore can be initialized by means _________ instruction in conjunction with a [ B]

hardware lock mechanism

a) Lock and set b) Test and Set c) Set and Test d) Test and Lock

45 The processor with 24 address lines will the ________ Bytes of memory capacity. [D ]

a)24 MB b)28 MB c)24 KB d)16 MB

46 Expand MISD [ C ]

a) Multi Instrument Single Device b) Multiple Instruction Single

Device

c) Multiple Instruction Single Data d)Multilayer Instruction Single Data

47 Expand MIMD [ C]

a) Multi Instrument Multi Device b) Multiple Instruction Multi Device

c) Multiple Instruction Multiple Data d)Multilayer Instruction Multiple Data

48 Expand SISD [ C]

a) Single Instrument Single Device b) Single Instruction Single Device

c) Single Instruction Single Data d) Single Instruction Single Data

49 Expand SIMD [ C]

a) Single Instrument Multi Device b) Single Instruction Multi Device

c) Single Instruction Multiple Data d) Single Instruction Multiple Data

50 Expand UART [A]

a) Universal Asynchronous Receiver Transmitter b) Unidirectional Asynchronous

Receiver Transmitter c) Unilateral Asynchronous Receiver Transmitter d)none

51 Expand DMA [ C]

a)Direct Mode Access b) Data Mode Array c)Direct Memory Access d) Data

Memory Array

52 Computer system that supervises the flow of information between auxiliary memory [ C ]

and main memory is called the ________________

a) Maintenance system b) Control system c)Memory management system d)None

53 On receiving an interrupt from an I/O device, the CPU [ B ]

a) Halts for predetermined time b) branches off to the ISR after completion of the

current instruction c) branches off to the ISR immediately d) Hands over control of

address bus and data bus to the interrupting device.

54 Which of the following is not an input device? [ D ]

a) Mouse b) Keyboard c) Light Pen d) VDU

55 Which of the following is an example of Input device? [ A ]

a)Scanner b) Speaker c) CD d) Printer

56 Which of the following is not an input device? [ D ]

a) web cam b) scanner c)light pen d) None

57 System containing only one processor is called [ b ]

a) multiprocessor b) single processor c) dual processor d) specific processor

58 The code that changes the value of the semaphore is ____________ [ C]

a) remainder section code b) non – critical section code c) critical section code

d) none of the mentioned

59 Semaphore is a/an _______ to solve the critical section problem. [ C]

a) hardware for a system b) special program for a system

c) integer variable d) none of the mentioned

60 Alternative way of a snooping-based coherence protocol, is called a [ B]

A) Memory protocol B)Directory protocol C)Register protocol D)None

Você também pode gostar

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemNo EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemAinda não há avaliações

- 300+ TOP Computer Organization and Architecture MCQ PDFDocumento37 páginas300+ TOP Computer Organization and Architecture MCQ PDFSaikumar NemalikantiAinda não há avaliações

- Operating System MCQDocumento25 páginasOperating System MCQlakshmi.sAinda não há avaliações

- Delta Pulse Metal Detector Practical GuideDocumento0 páginaDelta Pulse Metal Detector Practical Guidecrazymax9083% (6)

- Tma Cit309Documento4 páginasTma Cit309Vivienne OkaforAinda não há avaliações

- Biju Patnik University of Technology: Computer Science & Engineering (Cse) & Information Technology (IT)Documento72 páginasBiju Patnik University of Technology: Computer Science & Engineering (Cse) & Information Technology (IT)Kumar AnupamAinda não há avaliações

- Data Sheet FLC 100Documento2 páginasData Sheet FLC 100Ömer Vehbe100% (1)

- HiSIM-HV - A Compact Model For Simulation of High-Voltage MOSFET CircuitsDocumento8 páginasHiSIM-HV - A Compact Model For Simulation of High-Voltage MOSFET CircuitsMa SeenivasanAinda não há avaliações

- B17 Basic Computer Bangla PDFDocumento11 páginasB17 Basic Computer Bangla PDFKalam Khan100% (1)

- B.sc. Information TechnologyDocumento67 páginasB.sc. Information TechnologyArchana PatilAinda não há avaliações

- Cse Test 1Documento8 páginasCse Test 1Er Chandan SoniAinda não há avaliações

- Cs8491 Computer Architecture Unit - 3Documento9 páginasCs8491 Computer Architecture Unit - 3ASIF MAinda não há avaliações

- Computer Organization Questions and Answers - Set-2Documento6 páginasComputer Organization Questions and Answers - Set-2Mouli Mandal100% (2)

- UntitledDocumento29 páginasUntitledMaji091Ainda não há avaliações

- Mcq-Microprocessors 3BSC FinalDocumento7 páginasMcq-Microprocessors 3BSC FinalSathishAinda não há avaliações

- TYBSC Computer Science SEM VI UG CS 321 Operating SystemDocumento47 páginasTYBSC Computer Science SEM VI UG CS 321 Operating SystemPriyanka MahajanAinda não há avaliações

- Aca Mid-1 Obj With AnsDocumento9 páginasAca Mid-1 Obj With AnsHanisha BavanaAinda não há avaliações

- Wa0001.Documento6 páginasWa0001.Sam HackAinda não há avaliações

- MC0070-Operating Systems With Unix Model Question PaperDocumento23 páginasMC0070-Operating Systems With Unix Model Question Paperprac87Ainda não há avaliações

- PipeliningDocumento3 páginasPipeliningahmed_kazimAinda não há avaliações

- Computer Architecture Unit 1 MCQDocumento6 páginasComputer Architecture Unit 1 MCQRaagavi VAinda não há avaliações

- CO MID-1 BitsDocumento6 páginasCO MID-1 BitsMᴀɴɪ TᴇᴊᴀAinda não há avaliações

- Mces MCQDocumento50 páginasMces MCQshrimanAinda não há avaliações

- Maths Punjab Board McqsDocumento10 páginasMaths Punjab Board McqsSafe DepositAinda não há avaliações

- SPPU All Course MCQ: All MCQ PDF Format Mba / Be /ba /engieenaring / BSC /MSC /bca/ BcomDocumento8 páginasSPPU All Course MCQ: All MCQ PDF Format Mba / Be /ba /engieenaring / BSC /MSC /bca/ BcomQueency FernandesAinda não há avaliações

- The - Format Is Usually Used To Store Data.: A) BCD B) Decimal C) Hexadecimal D) OctalDocumento27 páginasThe - Format Is Usually Used To Store Data.: A) BCD B) Decimal C) Hexadecimal D) OctalSuchit KumarAinda não há avaliações

- Cs8491 Computer Architecture Unit - 1Documento12 páginasCs8491 Computer Architecture Unit - 1ASIF MAinda não há avaliações

- MCQ CoaDocumento7 páginasMCQ Coa30. Suraj IngaleAinda não há avaliações

- UNIT1 Short and Long QuestionsDocumento16 páginasUNIT1 Short and Long QuestionsSoumen MitraAinda não há avaliações

- Interview Questions: 300+ Top Computer Organization & Architecture Mcqs and AnswersDocumento55 páginasInterview Questions: 300+ Top Computer Organization & Architecture Mcqs and AnswersmohammedAinda não há avaliações

- Operating System MCQ's Set1: Ans: DDocumento8 páginasOperating System MCQ's Set1: Ans: DYash KuncolienkerAinda não há avaliações

- Computer Fundamental & OSDocumento9 páginasComputer Fundamental & OSgopalmondal110Ainda não há avaliações

- Allahabad Bank Clerk Exam, 2008: Computer General Knowledge (Solved)Documento7 páginasAllahabad Bank Clerk Exam, 2008: Computer General Knowledge (Solved)bankbankbankAinda não há avaliações

- Objective QA - EC 6009Documento13 páginasObjective QA - EC 6009Santhanamari GAinda não há avaliações

- COA MergeDocumento426 páginasCOA MergeParth chaudhariAinda não há avaliações

- Computer Fundamentals Questions and AnswersDocumento276 páginasComputer Fundamentals Questions and AnswersMersal Ahmed AnamAinda não há avaliações

- Co Gate ExamDocumento4 páginasCo Gate ExamjyothibellaryvAinda não há avaliações

- BDA IV B.Tech I Sem MR18-Mid-2 Objective QuestionsDocumento11 páginasBDA IV B.Tech I Sem MR18-Mid-2 Objective QuestionsSai PhaniAinda não há avaliações

- CS 101 Quiz#1 Solution 1Documento17 páginasCS 101 Quiz#1 Solution 1Unknown PersonAinda não há avaliações

- Os - 2Documento1 páginaOs - 2Kannan ThenmozhiAinda não há avaliações

- ES MCQ CDACDocumento54 páginasES MCQ CDACVijayanand SAinda não há avaliações

- Os ConceptsDocumento4 páginasOs ConceptsBhaskar SinAinda não há avaliações

- Computer OrganizationDocumento8 páginasComputer OrganizationVeerabhadra Durgam100% (1)

- Advance Computer ArchitectureDocumento13 páginasAdvance Computer Architectureदिब्यम प्रभात्Ainda não há avaliações

- Computer Architecture McqsDocumento10 páginasComputer Architecture McqsSatsshhAinda não há avaliações

- MCQ OsDocumento5 páginasMCQ Oskushagra sharmaAinda não há avaliações

- Multiple Choice Questions - Coa: Ans: ADocumento8 páginasMultiple Choice Questions - Coa: Ans: ADeepa GoudAinda não há avaliações

- Ii B.Tech (Cse) - Co-Unit-I-Mcqs: Multiple Choice QuestionsDocumento13 páginasIi B.Tech (Cse) - Co-Unit-I-Mcqs: Multiple Choice QuestionsDanielHaileAinda não há avaliações

- Are Numbers and Encoded Characters Generally Used As OperandsDocumento9 páginasAre Numbers and Encoded Characters Generally Used As OperandsAnurag ChitrakarAinda não há avaliações

- Computer Organization - Functional Units of A ComputerDocumento31 páginasComputer Organization - Functional Units of A ComputerKiruthiga PrabakaranAinda não há avaliações

- Computer OrganizationDocumento31 páginasComputer OrganizationKiruthiga PrabakaranAinda não há avaliações

- Recent Electronic Components - STUDENTSDocumento20 páginasRecent Electronic Components - STUDENTSaryan KadamAinda não há avaliações

- 117BZ - Computer Organization PDFDocumento8 páginas117BZ - Computer Organization PDFvenkiscribd444Ainda não há avaliações

- Arm MCQDocumento12 páginasArm MCQAshok Kumar60% (5)

- Unit 3 Memory Management Amultiple Choice Questions:: 18Csc205J Operating Systems Unit 3Documento17 páginasUnit 3 Memory Management Amultiple Choice Questions:: 18Csc205J Operating Systems Unit 3AKASH V (RA2111003040108)Ainda não há avaliações

- Assignment 1 MCQDocumento4 páginasAssignment 1 MCQamit dava0% (1)

- ES MCQ CDACDocumento53 páginasES MCQ CDACAshish Ghodke100% (2)

- Es MCQDocumento31 páginasEs MCQAshish GhodkeAinda não há avaliações

- Cao MCQDocumento13 páginasCao MCQsaiananyaAinda não há avaliações

- C++ MCQDocumento17 páginasC++ MCQAbdelazeem ElkadeemAinda não há avaliações

- ÔN TẬP CUỐI MÔN OSDocumento16 páginasÔN TẬP CUỐI MÔN OSNguyễn Bảo HưngAinda não há avaliações

- 2 - Fybca 203 Os1 Mcqbank - 2020 2021Documento3 páginas2 - Fybca 203 Os1 Mcqbank - 2020 2021rupeshpawar0086Ainda não há avaliações

- Technical QuestionsDocumento15 páginasTechnical Questionscse_soloAinda não há avaliações

- MLX90316SDC MelexisDocumento10 páginasMLX90316SDC MelexisWalter Taipe QuispeAinda não há avaliações

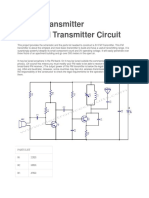

- 3V FM Transmitter 3V FM Transmitter CircuitDocumento4 páginas3V FM Transmitter 3V FM Transmitter Circuitpeter.gomes20087216Ainda não há avaliações

- Usb ItnDocumento6 páginasUsb ItnEU VaAinda não há avaliações

- Advance Communication Lab-15ECL76Documento39 páginasAdvance Communication Lab-15ECL76Pradeep kumarAinda não há avaliações

- AdcDocumento3 páginasAdcGopi ChannagiriAinda não há avaliações

- MMF60R580Q Datasheet v1.2 20210610Documento10 páginasMMF60R580Q Datasheet v1.2 20210610Ferney Martinez Romero Martinez RomeroAinda não há avaliações

- Faculty Routine Updated Spring-14Documento25 páginasFaculty Routine Updated Spring-14sabitavabiAinda não há avaliações

- CAO - Two Marks Question BankDocumento17 páginasCAO - Two Marks Question BankRamkumar SivakaminathanAinda não há avaliações

- Exercise 1.: Single Phase Load&compensationDocumento3 páginasExercise 1.: Single Phase Load&compensationhuynhvanan24930% (1)

- Wein Bridge Oscillator CircuitDocumento3 páginasWein Bridge Oscillator CircuitIndhu k100% (1)

- CT 3477saDocumento2 páginasCT 3477sasudipta_kolAinda não há avaliações

- Detectomat Katalog 2011Documento226 páginasDetectomat Katalog 2011Milica LolićAinda não há avaliações

- Cabo IHM SchneiderDocumento2 páginasCabo IHM Schneiderlorentz franklinAinda não há avaliações

- Chapter7 Input Output Organization PDFDocumento19 páginasChapter7 Input Output Organization PDFjijin kAinda não há avaliações

- Funai 29a-250-450 Service ManualDocumento70 páginasFunai 29a-250-450 Service Manualgnaks58Ainda não há avaliações

- I. Multiple Choice (30 PTS.)Documento3 páginasI. Multiple Choice (30 PTS.)Hanz AngeloAinda não há avaliações

- Automatic Distance Relay PDFDocumento4 páginasAutomatic Distance Relay PDFOmar Chayña VelásquezAinda não há avaliações

- Build A Double Bazooka Antenna (K3DAV Version)Documento11 páginasBuild A Double Bazooka Antenna (K3DAV Version)Steven BaynesAinda não há avaliações

- Data Sheet - C 272 Stereo Power AmplifierDocumento2 páginasData Sheet - C 272 Stereo Power Amplifieringmel79Ainda não há avaliações

- Voltage RegulatorsDocumento12 páginasVoltage RegulatorsAsghar AliAinda não há avaliações

- Zener ZpyDocumento6 páginasZener ZpysabbelsabbelAinda não há avaliações

- EPEVER Datasheet IPower 220v 1Documento2 páginasEPEVER Datasheet IPower 220v 1David QuintanaAinda não há avaliações

- MALVINO 69pagesDocumento69 páginasMALVINO 69pagesLaurena SilvestreAinda não há avaliações

- BEP R2 0 Blueprint 02 Link Planning and Design v08Documento36 páginasBEP R2 0 Blueprint 02 Link Planning and Design v08Vlad LazărAinda não há avaliações

- Alternating Current CircuitsDocumento18 páginasAlternating Current CircuitsSimpson BrotherAinda não há avaliações