Escolar Documentos

Profissional Documentos

Cultura Documentos

Class 5

Enviado por

Anil Guguloth0 notas0% acharam este documento útil (0 voto)

19 visualizações22 páginasj

Título original

class5

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoj

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

19 visualizações22 páginasClass 5

Enviado por

Anil Gugulothj

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

Você está na página 1de 22

Class 5

Low Power Modes Block

Low Power Mode Control 0 Register

(LPMCR0)

Automatic Wakeup in Low-power

Modes

• Wakeup from HALT: Set WDHALTI bit in CLKCTL

register to 1. When the device wakes up from

HALT, it will be through a CPU-watchdog reset.

The WDFLAG bit in the WDCR register can be

used to differentiate between a CPU-watchdog-

reset and a device reset.

• Wakeup from STANDBY: Set WDINTE bit in

LPMCR0 register to 1. When the device wakes up

from STANDBY, it will be through the WAKEINT

interrupt (Interrupt 1.8 in the PIE).

CPU Watchdog Block

Watchdog

• The WDCNTR is reset when the proper

sequence is written to the WDKEY register

before the 8-bit watchdog counter (WDCNTR)

overflows.

WDKEY sequences

Watchdog Reset or Watchdog

Interrupt Mode

• The watchdog can be configured in the SCSR register to either reset

the device (WDRST) or assert an interrupt (WDINT)

• Reset mode:

If the watchdog is configured to reset the device, then the WDRST

signal will pull the device reset (XRS) pin low for 512 OSCCLK cycles

when the watchdog counter reaches its maximum value.)

• Interrupt mode:

• If the watchdog is configured to assert an interrupt, then the

WDINT signal will be driven low for 512 OSCCLK cycles, causing the

WAKEINT interrupt in the PIE to be taken if it is enabled in the PIE

module. The watchdog interrupt is edge triggered on the falling

edge of WDINT. Thus, if the WAKEINT interrupt is re-enabled before

WDINT goes inactive, you will not immediately get another

interrupt. The next WAKEINT interrupt will occur at the next

watchdog timeout.

Watchdog Operation in Low Power

Modes

• In STANDBY mode, all of the clocks to the peripherals are turned off

on the device. The only peripheral that remains functional is the

watchdog since the watchdog module runs off the oscillator clock

(OSCCLK). The WDINT signal is fed to the Low Power Modes (LPM)

block so that it can be used to wake the device from STANDBY low

power mode (if enabled). See the Low Power Modes Block section

of the device data manual for details.

• In IDLE mode, the watchdog interrupt (WDINT) signal can generate

an interrupt to the CPU to take the CPU out of IDLE mode. The

watchdog is connected to the WAKEINT interrupt in the PIE.

• In HALT mode, this feature cannot be used because the oscillator

(and PLL) are turned off and, therefore, so is the watchdog.

Emulation Considerations

• CPU Suspended: When the CPU is suspended, the

watchdog clock (WDCLK) is suspended

• Run-Free Mode: When the CPU is placed in run-free

mode, then the watchdog module resumes operation

as normal.

• Real-Time Single-Step Mode: When the CPU is in real-

time single-step mode, the watchdog clock(WDCLK) is

suspended. The watchdog remains suspended even

within real time interrupts.

• Real-Time Run-Free Mode: When the CPU is in real-

time run-free mode, the watchdog operates as normal.

System Control and Status Register

(SCSR)

Watchdog Counter Register

(WDCNTR)

Watchdog Reset Key Register

(WDKEY)

Watchdog Control Register (WDCR)

32-Bit CPU Timers 0/1/2

• The CPU Timer-0 and CPU-Timer 1 can be

used in user applications.

• Timer 2 is reserved for DSP/BIOS. If the

application is not using DSP/BIOS, then Timer

2 can be used in the application.

32-Bit CPU Timers 0/1/2

CPU-Timer Interrupts Signals and

Output Signal

CPU-Timer Interrupts Signals and

Output Signal

• The 32-bit counter register TIMH:TIM is

loaded with the value in the period register

PRDH:PRD.

• The counter decrements once every

(TPR[TDDRH:TDDR]+1) SYSCLKOUT cycles,

where TDDRH:TDDR is the timer divider. When

the counter reaches 0, a timer interrupt

output signal generates an interrupt pulse.

CPU-Timers 0, 1, 2 Configuration and

Control Registers

TIMERxTIM Register (x = 0, 1, 2)

TIMERxTIMH Register

TIMERxPRD Register (x = 0, 1, 2)

Você também pode gostar

- UGSemsterSyllabus Chemistry 6Sem614Chemistry English InorganicOrganicPhysicalChemistryDocumento168 páginasUGSemsterSyllabus Chemistry 6Sem614Chemistry English InorganicOrganicPhysicalChemistryAnil GugulothAinda não há avaliações

- UGSemsterSyllabus Chemistry 5Sem514Chemistry EnglishDocumento234 páginasUGSemsterSyllabus Chemistry 5Sem514Chemistry EnglishAnil GugulothAinda não há avaliações

- UGSemsterSyllabus Chemistry 5Sem6AChemistry EnglishDocumento169 páginasUGSemsterSyllabus Chemistry 5Sem6AChemistry EnglishAnil GugulothAinda não há avaliações

- LL JL: Experiment-I Mosfet Device CharacteristicsDocumento5 páginasLL JL: Experiment-I Mosfet Device CharacteristicsAnil GugulothAinda não há avaliações

- Laboratory Manual and Record: ChemistryDocumento67 páginasLaboratory Manual and Record: ChemistryAnil GugulothAinda não há avaliações

- Writing The Effective Resume: The First Step Toward Landing Your Next JobDocumento25 páginasWriting The Effective Resume: The First Step Toward Landing Your Next JobAnil GugulothAinda não há avaliações

- EE700 Assignment 2 QuestionsDocumento2 páginasEE700 Assignment 2 QuestionsAnil GugulothAinda não há avaliações

- HVDC Transmission LinesDocumento19 páginasHVDC Transmission LinesAnil GugulothAinda não há avaliações

- Please Confirm The Same by Acknowledging This Email With Your Reply As Soon As PossibleDocumento1 páginaPlease Confirm The Same by Acknowledging This Email With Your Reply As Soon As PossibleAnil GugulothAinda não há avaliações

- Artificial Neural Networks For Transformer Protection: Project GuideDocumento7 páginasArtificial Neural Networks For Transformer Protection: Project GuideAnil GugulothAinda não há avaliações

- Agricultural RevolutionDocumento35 páginasAgricultural RevolutionAnil GugulothAinda não há avaliações

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- Conduit Box BWP-40BDocumento2 páginasConduit Box BWP-40Bvalimorsk ltd.Ainda não há avaliações

- 315MN GARAGE Door Opener Abridor de Puerta de Cochera: Owner's Manual/Manual Del PropietarioDocumento76 páginas315MN GARAGE Door Opener Abridor de Puerta de Cochera: Owner's Manual/Manual Del PropietarioLuis Alfonso BernalAinda não há avaliações

- UTP Cable Datasheet Nexans N100-605-O5Documento3 páginasUTP Cable Datasheet Nexans N100-605-O5Ruddy Alfredo Cabrejos RamosAinda não há avaliações

- Test Bank For Operating Systems Internals and Design Principles 8 e 8th Edition 0133805913Documento5 páginasTest Bank For Operating Systems Internals and Design Principles 8 e 8th Edition 0133805913beatrixnolanrmsAinda não há avaliações

- Agisoft Metashape & Agisoft Photoscan ComparisonDocumento5 páginasAgisoft Metashape & Agisoft Photoscan ComparisonBilly SilaenAinda não há avaliações

- UMG8900 Installation Manual-Software InstallationDocumento130 páginasUMG8900 Installation Manual-Software Installationfiras ibrahimAinda não há avaliações

- PX-PR PROFILE Printer: Part No. 557.202.864Documento4 páginasPX-PR PROFILE Printer: Part No. 557.202.864johnAinda não há avaliações

- Auto-Tune Evo 6.09 RTAS PC Notes: InstallationDocumento4 páginasAuto-Tune Evo 6.09 RTAS PC Notes: InstallationLite GangsterAinda não há avaliações

- Manual Da Placa Mae MSI MS-7267Documento93 páginasManual Da Placa Mae MSI MS-7267yuukalinin25% (4)

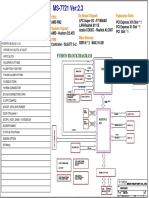

- Msi MS-7721 Rev 2.3 - Msi Fm2-A55m-E33Documento28 páginasMsi MS-7721 Rev 2.3 - Msi Fm2-A55m-E33Alejandro FernandezAinda não há avaliações

- Ficha Técnica Bisagras Certf. UlDocumento3 páginasFicha Técnica Bisagras Certf. UlQuiroa, Antonio JAinda não há avaliações

- So KZ Re MN SMP Series en GL 231130Documento36 páginasSo KZ Re MN SMP Series en GL 231130beriloAinda não há avaliações

- Console Repair Guy: How To Determine The Xbox 360 Secondary Error CodeDocumento4 páginasConsole Repair Guy: How To Determine The Xbox 360 Secondary Error CodedanielAinda não há avaliações

- NetServer UserManualDocumento104 páginasNetServer UserManualruben alarconAinda não há avaliações

- MoKo Case Fit Microsoft Surface Pro 7 Pro 6 Pro 5 Pro 2017 Pro 4 Pro LTE, All-In-One Protective Rugged CovDocumento1 páginaMoKo Case Fit Microsoft Surface Pro 7 Pro 6 Pro 5 Pro 2017 Pro 4 Pro LTE, All-In-One Protective Rugged CovAlpha TutorialAinda não há avaliações

- Research QuestionsDocumento6 páginasResearch QuestionsiAmAlfaAinda não há avaliações

- Programmers Manual FlexGripPlus SASSDocumento67 páginasProgrammers Manual FlexGripPlus SASSEsteban RodriguezAinda não há avaliações

- Coral Dev Board DatasheetDocumento28 páginasCoral Dev Board DatasheetNgo Tien TuAinda não há avaliações

- Snake Game: Presentation OnDocumento11 páginasSnake Game: Presentation Onkeshavs ingh0% (1)

- The ARM Instruction Set: Advanced RISC MachinesDocumento58 páginasThe ARM Instruction Set: Advanced RISC MachinesPoorva RathoreAinda não há avaliações

- 04 Storage Virtualization BasicsDocumento40 páginas04 Storage Virtualization BasicsElias KnebelAinda não há avaliações

- PT. Kalimantan MultimediaDocumento4 páginasPT. Kalimantan MultimediaRicky FadriannurAinda não há avaliações

- OS Part-1Documento12 páginasOS Part-1Govind GuptaAinda não há avaliações

- Asus FX505GT Rev 2.0 SchematicDocumento69 páginasAsus FX505GT Rev 2.0 SchematicNikolaj B0% (1)

- Lecture (Chapter 2)Documento24 páginasLecture (Chapter 2)ekiholoAinda não há avaliações

- D 1295042413Documento4 páginasD 1295042413Norbert DeakAinda não há avaliações

- Dell Technologies Edge Gateway 5200 Spec SheetDocumento2 páginasDell Technologies Edge Gateway 5200 Spec SheetdeepakAinda não há avaliações

- CC Practical 04Documento4 páginasCC Practical 04Arsalan DafedarAinda não há avaliações

- TBC Fender PDFDocumento3 páginasTBC Fender PDFmuhammad amanyAinda não há avaliações

- Intel Server Board SE7221BK1-E Intel Server Platform SR1425BK1-E, Intel Server Chassis SC5250-E Spares/Parts List and Configuration GuideDocumento9 páginasIntel Server Board SE7221BK1-E Intel Server Platform SR1425BK1-E, Intel Server Chassis SC5250-E Spares/Parts List and Configuration GuideYAinda não há avaliações