Escolar Documentos

Profissional Documentos

Cultura Documentos

AS1115 Datasheet v1 06 LED Driver

Enviado por

farianekDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

AS1115 Datasheet v1 06 LED Driver

Enviado por

farianekDireitos autorais:

Formatos disponíveis

Data sheet

AS1115

64 LEDs, I²C Interfaced LED Driver with Keyscan

1 General Description 2 Key Features

The AS1115 is a compact LED driver for 64 single LEDs ! 3.4MHz I²C-Compatible Interface

or 8 digits of 7-segments. The devices can be pro- ! Individual LED Segment Control

grammed via an I²C compatible 2-wire interface. ! Readback for 16 Keys plus Interrupt

Every segment can be individually addressed and ! Open and Shorted LED Error Detection

updated separately. Only one external resistor (RSET) is - Global or Individual Error Detection

required to set the current. LED brightness can be con- ! Hexadecimal- or BCD-Code for 7-Segment Displays

trolled by analog or digital means. ! 200nA Low-Power Shutdown Current (typ; data

retained)

The devices include an integrated BCD code-B/HEX

! Digital and Analog Brightness Control

decoder, multiplex scan circuitry, segment and display

! Display Blanked on Power-Up

drivers, and a 64-bit memory. Internal memory stores

the shift register settings, eliminating the need for contin- ! Drive Common-Cathode LED Displays

uous device reprogramming. ! Supply Voltage Range: 2.7 to 5.5V

! Software Reset

All outputs of the AS1115 can be configured for key

! Optional External Clock

readback. Key-switch status is obtained by polling for up

! Package:

to 64 keys while 16 keys can be used to trigger an inter-

rupt. - QSOP-24

- TQFN(4x4)-24

Additionally the AS1115 offers a diagnostic mode for

easy and fast production testing.

The AS1115 features a low shutdown current of typically

3 Applications

200nA, and an operational current of typically 350µA. The AS1115 is ideal for seven-segment or dot matrix

The number of digits can be programmed, the devices user interface displays of set-top boxes, VCRs, DVD-

can be reset by software, and an external clock is also players, washing machines, micro wave ovens, refriger-

supported. ators and other white good or personal electronic appli-

The device is available in a QSOP-24 and the cations.

TQFN(4x4)-24 package.

Figure 1. AS1115 - Typical Application Diagram

VDD DIG0 to

2.7 to 5.5V DIG7 8

9.53kΩ

ISET SEGA-DP

KEY0-7 8

SDA AS1115

SDA 8

SCL

SCL KEYA

IRQ

µP IRQ

KEYB

GND

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 1 - 24

AS1115

Datasheet - P i n o u t

4 Pinout

Pin Assignments

Figure 2. Pin Assignments (Top View)

SEGDP

SEGD

DIG1

DIG0

SDA

22 SEGDP

IRQ

21 SEG E

18 SEGG

23 SEGD

20 SEGC

17 SEGB

15 SEGA

16 SEGF

13 ISET

19 VDD

14 SCL

24 IRQ

24 23 22 21 20 19

DIG2 1 18 SEG E

DIG3 2 17 SEGC

AS1115 GND 3 16 VDD

AS1115

DIG4 4 15 SEGG

DIG5 5 Exposed

14 SEGB

DIG7 10

KEYB 12

KEYA 11

SDA 1

DIG0 2

DIG1 3

DIG2 4

DIG3 5

GND 6

DIG4 7

DIG5 8

DIG6 9

Pad

DIG6 6 13 SEGF

7 8 9 10 11 12

KEYB

SEGA

KEYA

DIG7

ISET

SCL

Pin Descriptions

Table 1. Pin Descriptions

Pin NameQSOP-24 TQFN(4x4)-24 Description

SDA 1 22 Serial-Data I/O. Open drain digital I/O I²C data pin.

Digit Drive Lines. Eight digit drive lines that sink current from the display

1, 2, 4, 5, 6, 7, common cathode. Keyscan detection optional, but must be polled by the

DIG0:DIG7 2-5, 7-10 23, 24

µProzessor.

GND 6 3 Ground.

Keyscan Input. Keyscan lines for key readback. Can be used for self-

KEYA 11 8

adressing.

KEYB 12 9 Keyscan Input. Keyscan lines for key readback.

Set Segment Current. Connect to VDD or a reference voltage through

ISET 13 10 RSET to set the peak segment current (see Selecting RSET Resistor

Value and Using External Drivers on page 19).

SCL 14 11 Serial-Clock Input. 3.4MHz maximum rate.

IRQ 24 21 Interupt Request Output. Open drain pin.

SEGA:SEGG 15-18, Seven Segment and Decimal Point Drive Lines. 8 seven-segment

12-15, 17-20

, SEGDP 20-23 drives and decimal point drive that source current to the display.

VDD 19 16 Positive Supply Voltage. Connect to +2.7 to +5.5V supply.

Exposed Pad. This pin also functions as a heat sink. Solder it to a large

- Exposed Pad

pad or to the circuit-board ground plane to maximize power dissipation.

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 2 - 24

AS1115

Datasheet - A b s o l u t e M a x i m u m R a t i n g s

5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only,

and functional operation of the device at these or any other conditions beyond those indicated in Section 6 Electrical

Characteristics on page 4 is not implied. Exposure to absolute maximum rating conditions for extended periods may

affect device reliability.

Table 2. Absolute Maximum Ratings

Parameter Min Max Units Notes

VDD to GND -0.3 7 V

Input Voltage Range 7 or

All other pins to GND -0.3 V

VDD + 0.3

DIG0:DIG7 Sink Current 500 mA

Current

SEGA:SEGG, SEGDP 100 mA

Humidity 5 85 % Non-condensing

Digital outputs 1000 V

Electrostatic Discharge Norm: MIL 833 E method 3015

All other pins 1000 V

Latch-Up Immunity ±100 mA EIA/JESD78

88 ºC/W on PCB, QSOP-24 package

Thermal Resistance ΘJA

30.5 ºC/W on PCB, TQFN(4x4)-24 package

Ambient Temperature -40 +85 ºC

Storage Temperature -55 150 ºC

The reflow peak soldering

temperature (body temperature)

specified is in accordance with IPC/

JEDEC J-STD-020D “Moisture/

Package Body Temperature +260 ºC Reflow Sensitivity Classification for

Non-Hermetic Solid State Surface

Mount Devices”.

The lead finish for Pb-free leaded

packages is matte tin (100% Sn).

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 3 - 24

AS1115

Datasheet - E l e c t r i c a l C h a r a c t e r i s t i c s

6 Electrical Characteristics

VDD = 2.7V to 5.5V, RSET = 9.53kΩ, TAMB = -40 to +85°C, typ. values @ TAMB = +25ºC, VDD = 5.0V (unless otherwise

specified).

Table 3. Electrical Characteristics

Symbol Parameter Conditions Min Typ Max Unit

VDD Operating Supply Voltage 2.7 5.5 V

All digital inputs at VDD or

0.2 2 µA

IDDSD Shutdown Supply Current GND, TAMB = +25ºC

single digit, TAMB = +85ºC 4 µA

RSET = open circuit. 0.35 0.6

IDD Operating Supply Current All segments and decimal mA

335

point on; ISEG = -40mA.

fOSC Display Scan Rate 8 digits scanned 0.48 0.96 kHz

IDIGIT Digit Drive Sink Current VOUT = 0.65V 320 mA

ISEG Segment Drive Source Current -35 -41 -47 mA

VDD = 5.0V, VOUT = (VDD -1V)

ΔISEG Segment Drive Current Matching 3 %

ISEG Segment Drive Source Current Average Current 47 mA

Table 4. Logic Inputs/Outputs Characteristics

Symbol Parameter Conditions Min Typ Max Unit

IIH, IIL Input Current SDA, SCL VIN = 0V or VDD -1 1 µA

VIH Logic High Input Voltage SDA, SCL 0.7xVDD V

VIL Logic Low Input Voltage SDA, SCL 0.3xVDD V

VOL(SDA) SDA Output Low Voltage ISINK = 3mA 0.4 V

VKEYopen Keyscan Open Input Voltage 0.8xVDD V

VKEYshort Keyscan Short Input Voltage 0.7x VDD V

VOL(IRQ) Interrupt Output Low Voltage ISINK = 3mA 0.4 V

ΔVI Hysteresis Voltage DIN, CLK, LD/CS 1 V

Capacitive Load for Each Bus Line 400 pF

Open Detection Level Threshold 0.7x 0.75x 0.8x V

VDD VDD VDD

0.05x 0.1x 0.15x

Short Detection Level Threshold V

VDD VDD VDD

Table 5. Timing Characteristics

Symbol Parameter Conditions Min Typ Max Unit

fSCL SCL Frequency 0.1 3.4 MHz

Bus Free Time Between STOP and

tBUF 1.3 µs

START Conditions

Hold Time for Repeated

tHOLDSTART 160 ns

START Condition

tLOW SCL Low Period 50 75 ns

tHIGH SCL High Period 50 75 ns

Setup Time for Repeated

tSETUPSTART 100 ns

START Condition

tSETUPDATA Data Setup Time 10 ns

tHOLDDATA Data Hold Time 70 ns

tRISE(SCL) SCL Rise Time 10 40 ns

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 4 - 24

AS1115

Datasheet - E l e c t r i c a l C h a r a c t e r i s t i c s

Table 5. Timing Characteristics

Symbol Parameter Conditions Min Typ Max Unit

SCL Rise Time after Repeated START

tRISE(SCL1) 10 80 ns

Condition and After an ACK Bit

tFALL(SCL) SCL Fall Time 10 40 ns

tRISE(SDA) SDA Rise Time 20 80 ns

tFALL(SDA) SDA Fall Time 20 80 ns

tSETUPSTOP STOP Condition Setup Time 160 ns

tSPIKESUP Pulse Width of Spike Suppressed 50 ns

Key Readback

Debounce Time 20 ms

Notes:

1. The Min / Max values of the Timing Characteristics are guaranteed by design.

2. All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC

(Statistical Quality Control) methods.

Figure 3. Timing Diagram

SDI

tBUF

tHOLDSTART

tHIGH tSPIKESUP

tHOLDSTART

tSETUPDATA

tR tSETUPSTOP

tF

tLOW tSETUPSTART

SCL

STOP START tHOLDDATA Repeated

START

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 5 - 24

AS1115

Datasheet - Ty p i c a l O p e r a t i n g C h a r a c t e r i s t i c s

7 Typical Operating Characteristics

RSET = 9.53kΩ, VRset = VDD;

Figure 4. Display Scan Rate vs. Supply Voltage; Figure 5. Display Scan Rate vs. Temperature;

780 800

Vdd=2.7V

Vdd=4V

780 Vdd=5V

760

Vdd=5.5V

760

fosc (Hz) .

fosc (Hz) .

740

740

720

720

700 Tamb=-40°C

Tamb=+25°C

700

Tamb=+85°C

680 680

2.7 3.1 3.5 3.9 4.3 4.7 5.1 5.5 -40 -15 10 35 60 85

Vdd (V) Tamb (°C)

Figure 6. Segment Current vs. Temperature; Figure 7. Segment Current vs. RSET;

60 50

Vseg = 4V; Vdd = 5V

Vseg = 3V; Vdd = 5V

50 Vseg = 2V; Vdd = 5V

40 Vseg = 1.7V; Vdd = 2.7V

40

Iseg (mA) .

Iseg (mA) .

30

30

20

20

Vseg = 1.7V; Vdd = 2.7V

Vseg = 1.7V; Vdd = 5V 10

10 Vseg = 3V; Vdd = 5V

Vseg = 4V; Vdd = 5V

0 0

-40 -15 10 35 60 85 0 10 20 30 40 50 60 70 80 90

Tamb (°C) Rset (kOhm)

Figure 8. Segment Current vs. Supply Voltage; Figure 9. Segment Current vs. VDD; VRset = 2.8V

60 50

Vseg = 1.7V

45 Vseg = 2V

50 Vseg = 2.3V

40

Vseg = 3.1V

35

40

Iseg (mA) .

Iseg (mA) .

30

30 25

20

20

Vseg = 1.7V

15

10

Vseg = 3V 10

Vseg = 4V

5

0 0

2.7 3.1 3.5 3.9 4.3 4.7 5.1 5.5 2.7 3 3.3 3.6 3.9 4.2

Vdd (V) Vdd (V)

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 6 - 24

AS1115

Datasheet - Ty p i c a l O p e r a t i n g C h a r a c t e r i s t i c s

Figure 10. VDIGIT vs. IDIGIT Figure 11. Input High Level vs. Supply Voltage

0.4 3.5

0.3

2.5

Vdig (V) .

Vih (V) .

2

0.2

1.5

Vdd = 2.7V

1

0.1

Vdd = 3.3V

Vdd = 4V

0.5

Vdd = 5V

Vdd = 5.5V

0 0

0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 2.7 3.1 3.5 3.9 4.3 4.7 5.1 5.5

Idig (A) Vdd (V)

Figure 12. ISEG vs. VSEG; VDD = 5V Figure 13. ISEG vs. VSEG; VDD = 4V

50 50

Rext = 10k Rext = 8k2

45 Rext = 13k 45 Rext = 10k

Rext = 18k Rext = 13k

40 Rext = 30k 40 Rext = 18k

Rext = 56k Rext = 30k

35 35

Iseg (mA) .

Iseg (mA) .

30 30

25 25

20 20

15 15

10 10

5 5

0 0

2 2.5 3 3.5 4 4.5 5 1 1.5 2 2.5 3 3.5 4

Vseg (V) Vseg (V)

Figure 14. ISEG vs. VSEG; VDD = 3.3V Figure 15. ISEG vs. VSEG; VDD = 2.7V

50 50

Rext = 6k8 Rext = 4k7

45 Rext = 8k2 45 Rext = 5k6

Rext = 10k Rext = 6k8

40 Rext = 13k 40 Rext = 10k

Rext = 18k Rext = 13k

35 35

Iseg (mA) .

Iseg (mA) .

30 30

25 25

20 20

15 15

10 10

5 5

0 0

1 1.2 1.4 1.6 1.8 2 2.2 2.4 2.6 2.8 3 3.2 1 1.2 1.4 1.6 1.8 2 2.2 2.4 2.6

Vseg (V) Vseg (V)

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 7 - 24

AS1115

Datasheet - D e t a i l e d D e s c r i p t i o n

8 Detailed Description

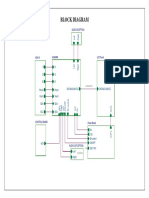

Block Diagram

Figure 16. AS1115 - Block Diagram (QSOP-24 Package)

Open/Short

Detection VDD

+

–

RSET

19

+

VDD

–

Oszillator 13

VDD ISET

24 8 15-18, 20-23

IRQ SEGA-G,

Digital Control SEGDP

Logic 8 2-5, 7-10

DIG0 to DIG7

VDD (PWM, Debounce,....)

2 11, 12

KEYA, KEYB

VDD

14

SCL I²C Registers 6

Interface

1

GND

SDA Data - Registers

Control - Registers

Scan - Registers AS1115

Figure 17. ESD Structure

VDD valid for the pins: VDD

- IRQ

- SCL

- SDA valid for the pins:

- ISET - DIG0 to DIG7

- SEGA-G, SEGDP

- KEYA, KEYB

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 8 - 24

AS1115

Datasheet - D e t a i l e d D e s c r i p t i o n

I²C Interface

The AS1115 supports the I²C serial bus and data transmission protocol in high-speed mode at 3.4MHz. The AS1115

operates as a slave on the I²C bus. The bus must be controlled by a master device that generates the serial clock

(SCL), controls the bus access, and generates the START and STOP conditions. Connections to the bus are made via

the open-drain I/O pins SCL and SDA.

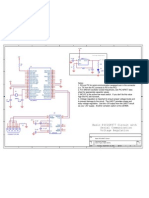

Figure 18. I²C Interface Initialisation

1 8 9 1 8 9

0 0 0 0 0 A1 A0 R/W D15 D14 D13 D12 D11 D10 D9 D8

Default values at power up: A1 = A0 = 0

Figure 19. Bus Protocol

SDI MSB

Slave Address ACK from

R/W Receiver

Direction Bit

ACK from

Receiver

SCL 1 2 6 7 8 9 1 2 3-8 8 9

ACK ACK

Repeat if More Bytes Transferred

START STOP or

Repeated

START

The bus protocol (as shown in Figure 19) is defined as:

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line

while the clock line is HIGH will be interpreted as control signals.

The bus conditions are defined as:

- Bus Not Busy. Data and clock lines remain HIGH.

- Start Data Transfer. A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a

START condition.

- Stop Data Transfer. A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH,

defines the STOP condition.

- Data Valid. The state of the data line represents valid data, when, after a START condition, the data line is stable

for the duration of the HIGH period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data

bytes transferred between START and STOP conditions is not limited and is determined by the master device.

The information is transferred byte-wise and each receiver acknowledges with a ninth-bit.

Within the I²C bus specifications a high-speed mode (3.4MHz clock rate) is defined.

- Acknowledge: Each receiving device, when addressed, is obliged to generate an acknowledge after the recep-

tion of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge

bit. A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way

that the SDA line is stable LOW during the HIGH period of the acknowledge clock pulse. Of course, setup and

hold times must be taken into account. A master must signal an end of data to the slave by not generating an

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 9 - 24

AS1115

Datasheet - D e t a i l e d D e s c r i p t i o n

acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the

data line HIGH to enable the master to generate the STOP condition.

- Figure 19 on page 9 details how data transfer is accomplished on the I²C bus. Depending upon the state of the R/

W bit, two types of data transfer are possible:

- Master Transmitter to Slave Receiver. The first byte transmitted by the master is the slave address, followed by

a number of data bytes. The slave returns an acknowledge bit after the slave address and each received byte.

- Slave Transmitter to Master Receiver. The first byte, the slave address, is transmitted by the master. The slave

then returns an acknowledge bit. Next, a number of data bytes are transmitted by the slave to the master. The

master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received

byte, a not-acknowledge is returned. The master device generates all of the serial clock pulses and the START

and STOP conditions. A transfer is ended with a STOP condition or a repeated START condition. Since a

repeated START condition is also the beginning of the next serial transfer, the bus will not be released.

The AS1115 can operate in the following slave modes:

- Slave Receiver Mode. Serial data and clock are received through SDA and SCL. After each byte is received, an

acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial

transfer. Address recognition is performed by hardware after reception of the slave address and direction bit.

- Slave Transmitter Mode. The first byte (the slave address) is received and handled as in the slave receiver

mode. However, in this mode the direction bit will indicate that the transfer direction is reversed. Serial data is

transmitted on SDA by the AS1115 while the serial clock is input on SCL. START and STOP conditions are recog-

nized as the beginning and end of a serial transfer.

I²C Device Self Addressing

If this feature is used, 2 of the 16 key readback nodes can be left open or shorted for self-addressing. This is done with

KEYA together with SEGG and SEGF. This two nodes cannot be used for key-readback in this case. After startup all

devices have the predefined adress 0000000. A single command for self-addressing will update all connected AS1115.

This command has to be done after startup or everytime the AS1115 gets disconnected from the supply. The I²C

address definition must be done with fixed connection, since I²C detection is excluded from debounce time of key reg-

isters.

I²C Device Address Byte

The address byte (see Figure 20) is the first byte received following the START condition from the master device.

Figure 20. I²C Device Address Byte

MSB 6 5 4 3 2 1 LSB

predefined address: 0 0 0 0 0 0 0 R/W

MSB 6 5 4 3 2 1 LSB

updated address: 0 0 0 0 0 A1 A0 R/W

- The default slave address is factory-set to 0000000.

- The two LSB bits of the address byte are the device select bits, A0 to A1, which can be set by the self-adress

command after startup. A maximum of four devices with the same pre-set code can therefore be connected on

the same bus at one time.

- The last bit of the address byte (R/W) define the operation to be performed. When set to a 1 a read operation is

selected; when set to a 0 a write operation is selected.

Following the START condition, the AS1115 monitors the I²C bus, checking the device type identifier being transmitted.

Upon receiving the address code, and the R/W bit, the slave device outputs an acknowledge signal on the SDA line.

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 10 - 24

AS1115

Datasheet - D e t a i l e d D e s c r i p t i o n

Command Byte

The AS1115 operation, (see Table 6) is determined by a command byte (see Figure 21 on page 11).

Figure 21. Command Byte

MSB 6 5 4 3 2 1 LSB

D15 D14 D13 D12 D11 D10 D09 D08

Figure 22. Command and Single Data Byte Received

From Master to Slave AS1115 Registers

From Slave to Master

0 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

S Slave Address R/W A Command Byte A Data Byte A P

1 Byte

Acknowledge Acknowledge Acknowledge

from AS1115 0 from AS1115 0 from AS1115 0

Autoincrement

Memory Word

Address

Figure 23. Setting the Pointer to a Address Register to select a Data Register for a Read Operation

From Master to Slave AS1115 Registers

From Slave to Master

0 D15 D14 D13 D12 D11 D10 D9 D8

S Slave Address R/W A Command Byte A P

Acknowledge Acknowledge

from AS1115 0 from AS1115 0

Figure 24. Reading nBytes from AS1115

Autoincrement

Memory Word

From Master to Slave Address Stop reading

From Slave to Master Acknowledge Acknowledge Not Acknowledge

from AS1115 0 from Master 0 from Master 1

n Bytes

S Slave Address R/W A First Data Byte A Second Data Byte /A P

1 D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

Autoincrement

AS1115 Registers to next address

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 11 - 24

AS1115

Datasheet - D e t a i l e d D e s c r i p t i o n

Initial Power-Up

On initial power-up, the AS1115 registers are reset to their default values, the display is blanked, and the device goes

into shutdown mode. At this time, all registers should be programmed for normal operation.

Note: The default settings enable only scanning of one digit; the internal decoder is disabled and the Intensity Control

Register (see page 17) is set to the minimum values.

Shutdown Mode

The AS1115 devices feature a shutdown mode, where they consume only 200nA (typ) current. Shutdown mode is

entered via a write to the Shutdown Register (see Table 7). During shutdown mode the Digit-Registers maintain their

data.

Shutdown mode can either be used as a means to reduce power consumption or for generating a flashing display

(repeatedly entering and leaving shutdown mode). For minimum supply current in shutdown mode, logic input should

be at GND or VDD (CMOS logic level).

When entering or leaving shutdown mode, the Feature Register is reset to its default values (all 0s) when Shutdown

Register bit D7 (page 13) = 0.

Note: When Shutdown Register bit D7 = 1, the Feature Register is left unchanged when entering or leaving shut-

down mode. If the AS1115 is used with an external clock, Shutdown Register bit D7 should be set to 1 when

writing to the Shutdown Register.

Digit- and Control-Registers

The AS1115 devices contain 8 Digit-Registers,11 control-registers and 10 diagnostic-registers, which are listed in Table

6. All registers are selected using a 8-bit address word, and communication is done via the I²C interface.

! Digit Registers – These registers are realized with an on-chip 64-bit memory. Each digit can be controlled directly

without rewriting the whole register contents.

! Control Registers – These registers consist of decode mode, display intensity, number of scanned digits, shut-

down, display test and features selection registers.

Table 6. Register Address Map

Address

Type

Register Page

D15:D13 D12 D11 D10 D9 D8 D7:D0

Digit 0 000 0 0 0 0 1 N/A

Digit 1 000 0 0 0 1 0 N/A

Digit Register

Digit 2 000 0 0 0 1 1 N/A

Digit 3 000 0 0 1 0 0 (see Table 9 on page 14, N/A

Table 10 on page 14 and

Digit 4 000 0 0 1 0 1 Table 11 on page 15) N/A

Digit 5 000 0 0 1 1 0 N/A

Digit 6 000 0 0 1 1 1 N/A

Digit 7 000 0 1 0 0 0 N/A

Decode-Mode 000 0 1 0 0 1 (see Table 8 on page 13) 13

Global Intensity 000 0 1 0 1 0 (see Table 17 on page 17) 17

Scan Limit 000 0 1 0 1 1 (see Table 19 on page 17) 17

Control Register

Shutdown 000 0 1 1 0 0 (see Table 7 on page 13) 12

Self-Adressing 001 0 1 1 0 1 N/A

Feature 000 0 1 1 1 0 (see Table 20 on page 18) 18

Display Test Mode 000 0 1 1 1 1 (see Table 14 on page 16) 13

DIG0:DIG1 Intensity 000 1 0 0 0 0 (see Table 18 on page 17)

DIG2:DIG3 Intensity 000 1 0 0 0 1 (see Table 18 on page 17)

DIG4:DIG5 Intensity 000 1 0 0 1 0 (see Table 18 on page 17)

DIG6:DIG7 Intensity 000 1 0 0 1 1 (see Table 18 on page 17)

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 12 - 24

AS1115

Datasheet - D e t a i l e d D e s c r i p t i o n

Table 6. Register Address Map

Address

Type

Register Page

D15:D13 D12 D11 D10 D9 D8 D7:D0

Diagnostic Digit 0 000 1 0 1 0 0 N/A

Keyscan/Diagnostic Register

Diagnostic Digit 1 000 1 0 1 0 1 N/A

Diagnostic Digit 2 000 1 0 1 1 0 N/A

Diagnostic Digit 3 000 1 0 1 1 1 N/A

Diagnostic Digit 4 000 1 1 0 0 0 N/A

Diagnostic Digit 5 000 1 1 0 0 1 N/A

Diagnostic Digit 6 000 1 1 0 1 0 N/A

Diagnostic Digit 7 000 1 1 0 1 1 N/A

KEYA 000 1 1 1 0 0

KEYB 000 1 1 1 0 1

The Shutdown Register controls AS1115 shutdown mode.

Table 7. Shutdown Register Format (Address (HEX) = 0x0C))

Register Data

Mode HEX Code

D7 D6 D5 D4 D3 D2 D1 D0

Shutdown Mode, 0x00 0 X X X X X X 0

Reset Feature Register to Default Settings

Shutdown Mode, Feature Register Unchanged 0x80 1 X X X X X X 0

Normal Operation, 0x01 0 X X X X X X 1

Reset Feature Register to Default Settings

Normal Operation, Feature Register Unchanged 0x81 1 X X X X X X 1

Decode Enable Register (0x09)

The Decode Enable Register sets the decode mode. BCD/HEX decoding (either BCD code – characters 0:9, E, H, L,

P, and -, or HEX code – characters 0:9 and A:F) is selected by bit D2 (page 18) of the Feature Register. The Decode

Enable Register is used to select the decode mode or no-decode for each digit. Each bit in the Decode Enable Regis-

ter corresponds to its respective display digit (i.e., bit D0 corresponds to digit 0, bit D1 corresponds to digit 1 and so

on). Table 9 lists some examples of the possible settings for the Decode Enable Register bits.

Note: A logic high enables decoding and a logic low bypasses the decoder altogether.

When decode mode is used, the decoder looks only at the lower-nibble (bits D3:D0) of the data in the Digit-Registers,

disregarding bits D6:D4. Bit D7 sets the decimal point (SEG DP) independent of the decoder and is positive logic (bit

D7 = 1 turns the decimal point on). Table 9 lists the code-B font; Table 10 lists the HEX font.

When no-decode mode is selected, data bits D7:D0 of the Digit-Registers correspond to the segment lines of the

AS1115. Table 11 shows the 1:1 pairing of each data bit to the appropriate segment line.

Table 8. Decode Enable Register Format Examples

Register Data

Decode Mode HEX Code

D7 D6 D5 D4 D3 D2 D1 D0

No decode for digits 7:0 0x00 0 0 0 0 0 0 0 0

Code-B/HEX decode for digit 0. No decode for digits 7:1 0x01 0 0 0 0 0 0 0 1

Code-B/HEX decode for digit 0:2. No decode for digits 7:3 0x07 0 0 0 0 0 1 1 1

Code-B/HEX decode for digits 0:5. No decode for digits 7:6 0x3F 0 0 1 1 1 1 1 1

Code-B/HEX decode for digits 0,2,5. 0x25 0 0 1 0 0 1 0 1

No decode for digits 1, 3, 4, 6, 7

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 13 - 24

AS1115

Datasheet - D e t a i l e d D e s c r i p t i o n

Figure 25. Standard 7-Segment LED Intensity Control and Inter-Digit Blanking

A

F B

G

E C

D

DP

Table 9. Code-B Font

Char- Register Data Char- Register Data Char- Register Data

acter D7 D6:D4 D3 D2 D1 D0 acter D7 D6: D4 D3 D2 D1 D0 acter D7 D6:D4 D3 D2 D1 D0

X 0 0 0 0 X 0 1 1 0 X 1 1 0 0

X 0 0 0 1 X 0 1 1 1 X 1 1 0 1

X 0 0 1 0 X 1 0 0 0 X 1 1 1 0

X 0 0 1 1 X 1 0 0 1 X 1 1 1 1

*

X 0 1 0 0 X 1 0 1 0 1 X X X X X

X 0 1 0 1 X 1 0 1 1

*

The decimal point can be enabled with every character by setting bit D7 = 1.

Table 10. HEX Font

Char- Register Data Char- Register Data Char- Register Data

acter D7 D6:D4 D3 D2 D1 D0 acter D7 D6: D4 D3 D2 D1 D0 acter D7 D6:D4 D3 D2 D1 D0

X 0 0 0 0 X 0 1 1 0 X 1 1 0 0

X 0 0 0 1 X 0 1 1 1 X 1 1 0 1

X 0 0 1 0 X 1 0 0 0 X 1 1 1 0

X 0 0 1 1 X 1 0 0 1 X 1 1 1 1

*

X 0 1 0 0 X 1 0 1 0 1 X X X X X

X 0 1 0 1 X 1 0 1 1

*

The decimal point can be enabled with every character by setting bit D7 = 1.

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 14 - 24

AS1115

Datasheet - D e t a i l e d D e s c r i p t i o n

Table 11. No-Decode Mode Data Bits and Corresponding Segment Lines

D7 D6 D5 D4 D3 D2 D1 D0

Corresponding Segment Line DP A B C D E F G

I²C Self Addressing

If this feature is used, 2 of the 16 key readback nodes can be left open or shorted for self-addressing. This is done with

KEYA together with SEGG (A0) and SEGF (A1). This two nodes cannot be used for key-readback in this case. After

startup all devices have the predefined adress 0000000. A single command for selfaddressing will update all con-

nected AS1115. This command has to be done after startup or everytime the AS1115 gets disconnected from the sup-

ply. The I²C address definition must be done with fixed connection, since I²C detection is excluded from debounce time

of key registers.

Note: A short writes a logical “0” whereas an open writes a logical “1” as address bit.

Table 12. Self Addressing Register (Address (HEX) = 0x2D))

D7 D6 D5 D4 D3 D2 D1 D0

Factory-set IC address X X X X X X X 0

User-set IC address X X X X X X X 1

Keyscan Register

These two registers contain the result of the keyscan input of the 16 keys. To ensure proper results the data in these

registers are updated only if the logic data scanned is stable for 20ms (debounce time). A change of the data stored

within these two registers is indicated by a logic low on the IRQ pin. The IRQ is high-impedance if a read operation on

the key scan registers is started.

Table 13. LED Diagnostic Register Address

Segment

Register HEX Address

Key D7 D6 D5 D4 D3 D2 D1 D0

0x1C KEYA

DP A B C D E F G

0x1D KEYB

Note: If I²C self addressing is used segment G&F of KEYA is used for the two LSB of the I²C address. In this case

these two nodes cannot be used as a key. Additionally the debounce time is disabled for these two bits.

The data within the keyscan register is updated continuously during every cycle (1/10 of refresh rate). There-

fore, to get a valid readback of keys it is recommended to read out the keyscan registers immediately after the

IRQ is triggered. A short writes a logical “0” whereas an open writes a logical “1” as keyscan register bit.

Note: If the blink_en bit (bit D4 in the Feature Register 0x0E) is set to ‘1’, the keyscan is not returning a valid value.

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 15 - 24

AS1115

Datasheet - D e t a i l e d D e s c r i p t i o n

Display-Test Mode

The AS1115 can detect open or shorted LEDs. Readout of either open LEDs or short LEDs is possible, as well as a OR

relation of open and short.

Note: All settings of the digit- and control-registers are maintained.

Table 14. Testmode Register Summary

D7 D6 D5 D4 D3 D2 D1 D0

X RSET_short RSET_open LED_global LED_test LED_open LED_short DISP_test

Table 15. Testmode Register Bit Description (Address (HEX) = 0x0F))

Addr: 0x0F Address

Bit Bit Name Default Access D7:D0

Optical display test. (Testmode for external visual test.)

D0 DISP_test 0 W 0: Normal operation; 1: Run display test (All digits are tested

independently from scan limit & shutdown register.)

Starts a test for shorted LEDs. (Can be set together with D2)

D1 LED_short 0 W

0: Normal operation; 1: Activate testmode

Starts a test for open LEDs. (Can be set together with D1)

D2 LED_open 0 W

0: Normal operation; 1: Activate testmode

Indicates an ongoing open/short LED test

D3 LED_test 0 R

0: No ongoing LED test; 1: LED test in progress

Indicates that the last open/short LED test has detected an error

D4 LED_global 0 R

0: No error detected; 1: Error detected

Checks if external resistor RSET is open

D5 RSET_open 0 R

0: RSET correct; 1: RSET is open

Checks if external resistor RSET is shorted

D6 RSET_short 0 R

0: RSET correct; 1: RSET is shorted

D7 0 - Not used

LED Diagnostic Registers

These eight registers contain the result of the LED open/short test for the individual LED of each digit.

Table 16. LED Diagnostic Register Address

Register Segment Register Segment

HEX HEX

Address Digit D7 D6 D5 D4 D3 D2 D1 D0 Address Digit D7 D6 D5 D4 D3 D2 D1 D0

0x14 DIG0 0x18 DIG4

0x15 DIG1 0x19 DIG5

DP A B C D E F G DP A B C D E F G

0x16 DIG2 0x1A DIG6

0x17 DIG3 0x1B DIG7

Note: If one or more short occures in the LED array, detection of individual LED fault could become ambiguous.

Intensity Control Register (0x0A)

The brightness of the display can be controlled by digital means using the Intensity Control Registers and by analog

means using RSET (see Selecting RSET Resistor Value and Using External Drivers on page 19). The intensity can be

controlled globally for all digits, or for each digit individually. The global intensity command will write intensity data to all

four individual brightness registers, while the individual intesity command will only write to the associated individual

intensity register.

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 16 - 24

AS1115

Datasheet - D e t a i l e d D e s c r i p t i o n

Display brightness is controlled by an integrated pulse-width modulator which is controlled by the lower-nibble of the

Intensity Control Register. The modulator scales the average segment-current in 16 steps from a maximum of 15/16

down to 1/16 of the peak current set by RSET.

Table 17. Intensity Register Format

Register Data Register Data

Duty Cycle HEX Code Duty Cycle HEX Code

MSB D2 D1 LSB MSB D2 D1 LSB

1/16 (min on) 0xX0 0 0 0 0 9/16 0xX8 1 0 0 0

2/16 0xX1 0 0 0 1 10/16 0xX9 1 0 0 1

3/16 0xX2 0 0 1 0 11/16 0xXA 1 0 1 0

4/16 0xX3 0 0 1 1 12/16 0xXB 1 0 1 1

5/16 0xX4 0 1 0 0 13/16 0xXC 1 1 0 0

6/16 0xX5 0 1 0 1 14/16 0xXD 1 1 0 1

7/16 0xX6 0 1 1 0 15/16 0xXE 1 1 1 0

8/16 0xX7 0 1 1 1 15/16 (max on) 0xXF 1 1 1 1

Table 18. Intensity Register Address

Register Data

Register HEX Address

Type D7:D4 D3:D0

0x0A Global X Global Intensity

0x10 Digit Digit 1 Intensity Digit 0 Intensity

0x11 Digit Digit 3 Intensity Digit 2 Intensity

0x12 Digit Digit 5 Intensity Digit 4 Intensity

0x13 Digit Digit 7 Intensity Digit 6 Intensity

Scan-Limit Register (0x0B)

The Scan-Limit Register controls which of the digits are to be displayed. When all 8 digits are to be displayed, the

update frequency is typically 700Hz. If the number of digits displayed is reduced, the update frequency is increased.

The frequency can be calculated using 10 x fOSC/(N+2), where N is the number of digits.

Note: To avoid differences in brightness this register should not be used to blank parts of the display (leading zeros).

Table 19. Scan-Limit Register Format (Address (HEX) = 0x0B))

HEX Register Data HEX Register Data

Scan Limit Scan Limit

Code D7:D3 D2 D1 D0 Code D7:D3 D2 D1 D0

Display digit 0 only 0xX0 X 0 0 0 Display digits 0:4 0xX4 X 1 0 0

Display digits 0:1 0xX1 X 0 0 1 Display digits 0:5 0xX5 X 1 0 1

Display digits 0:2 0xX2 X 0 1 0 Display digits 0:6 0xX6 X 1 1 0

Display digits 0:3 0xX3 X 0 1 1 Display digits 0:7 0xX7 X 1 1 1

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 17 - 24

AS1115

Datasheet - D e t a i l e d D e s c r i p t i o n

Feature Register (0x0E)

The Feature Register is used for enabling various features including switching the device into external clock mode,

applying an external reset, selecting code-B or HEX decoding, enabling or disabling blinking, setting the blinking rate,

and resetting the blink timing.

Note: At power-up the Feature Register is initialized to 0.

Table 20. Feature Register Summary

D7 D6 D5 D4 D3 D2 D1 D0

blink_ sync blink_ blink_en NU decode_sel reg_res clk_en

start freq_sel

Table 21. Feature Register Bit Descriptions (Address (HEX) = 0xXE)

Feature Register

Addr: 0xXE

Enables and disables various device features.

Bit Bit Name Default Access Bit Description

External clock active.

D0 clk_en 0 R/W 0 = Internal oscillator is used for system clock.

1 = Pin CLK of the serial interface operates as system clock input.

Resets all control registers except the Feature Register.

0 = Reset Disabled. Normal operation.

D1 reg_res 0 R/W 1 = All control registers are reset to default state (except the Feature

Register) identically after power-up.

Note: The Digit Registers maintain their data.

Selects display decoding for the selected digits (Table 8 on page 13).

D2 decode_sel 0 R/W 0 = Enable Code-B decoding (see Table 9 on page 14).

1 = Enable HEX decoding (see Table 10 on page 14).

D3 NU Not used

Enables blinking.

D4 blink_en 0 R/W

0 = Disable blinking. 1 = Enable blinking.

Sets blink with low frequency (with the internal oscillator enabled):

D5 blink_freq_sel 0 R/W 0 = Blink period typically is 1 second (0.5s on, 0.5s off).

1 = Blink period is 2 seconds (1s on, 1s off).

Synchronizes blinking on the rising edge of pin LD/CS. The multiplex

and blink timing counter is cleared on the rising edge of pin LD/CS. By

D6 sync 0 R/W

setting this bit in multiple devices, the blink timing can be synchronized

across all the devices.

Start Blinking with display enabled phase. When bit D4 (blink_en) is set,

bit D7 determines how blinking starts.

D7 blink_start 0 R/W

0 = Blinking starts with the display turned off.

1 = Blinking starts with the display turned on.

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 18 - 24

AS1115

Datasheet - Ty p i c a l A p p l i c a t i o n

9 Typical Application

Selecting RSET Resistor Value and Using External Drivers

Brightness of the display segments is controlled via RSET. The current that flows into ISET defines the current that flows

through the LEDs.

Segment current is about 200 times the current in ISET. Typical values for RSET for different segment currents, operat-

ing voltages, and LED voltage drop (VLED) are given in Table 22 & Table 23. The maximum current the AS1115 can

drive is 47mA. If higher currents are needed, external drivers must be used, in which case it is no longer necessary

that the devices drive high currents.

Note: The display brightness can also be logically controlled (see Intensity Control Register (0x0A) on page 16).

Table 22. RSET vs. Segment Current and LED Forward Voltage, VDD = 2.7V & 3.3V & 3.6V

VLED VLED VLED

ISEG (mA)

1.5V 2.0V 1.5V 2.0V 2.5V 1.5V 2.0V 2.5V 3.0V

40 5kΩ 4.4kΩ 6.7kΩ 6.4kΩ 5.7kΩ 7.5kΩ 7.2kΩ 6.6kΩ 5.5kΩ

VDD = 2.7V

VDD = 3.3V

VDD = 3.6V

30 6.9kΩ 5.9kΩ 9.1kΩ 8.8kΩ 8.1kΩ 10.18kΩ 9.8kΩ 9.2kΩ 7.5kΩ

20 10.7kΩ 9.6kΩ 13.9kΩ 13.3kΩ 12.6kΩ 15.6kΩ 15kΩ 14.3kΩ 13kΩ

10 22.2kΩ 20.7kΩ 28.8kΩ 27.7kΩ 26kΩ 31.9kΩ 31kΩ 29.5kΩ 27.3kΩ

Table 23. RSET vs. Segment Current and LED Forward Voltage, VDD = 4.0V & 5.0V

ISEG VLED VLED

(mA) 1.5V 2.0V 2.5V 3.0V 3.5V 1.5V 2.0V 2.5V 3.0V 3.5V 4.0V

40 8.6kΩ 8.3kΩ 7.9kΩ 7.6kΩ 5.2kΩ 11.35kΩ 11.12kΩ 10.84kΩ 10.49kΩ 10.2kΩ 9.9kΩ

VDD = 4.0V

VDD = 5.0V

30 11.6kΩ 11.2kΩ 10.8kΩ 9.9kΩ 7.8kΩ 15.4kΩ 15.1kΩ 14.7kΩ 14.4kΩ 13.6kΩ 13.1kΩ

20 17.7kΩ 17.3kΩ 16.6kΩ 15.6kΩ 13.6kΩ 23.6kΩ 23.1kΩ 22.6kΩ 22kΩ 21.1kΩ 20.2kΩ

10 36.89kΩ 35.7kΩ 34.5kΩ 32.5kΩ 29.1kΩ 48.9kΩ 47.8kΩ 46.9kΩ 45.4kΩ 43.8kΩ 42kΩ

Calculating Power Dissipation

The upper limit for power dissipation (PD) for the AS1115 is determined from the following equation:

PD = (VDD x 5mA) + (VDD - VLED)(DUTY x ISEG x N) (EQ 1)

Where:

VDD is the supply voltage.

DUTY is the duty cycle set by intensity register (page 17).

N is the number of segments driven (worst case is 8)

VLED is the LED forward voltage

ISEG = segment current set by RSET

Dissipation Example:

ISEG = 40mA, N = 8, DUTY = 15/16, VLED = 2.2V at 40mA, VDD = 5V (EQ 2)

PD = 5V(5mA) + (5V - 2.2V)(15/16 x 40mA x 8) = 0.865W (EQ 3)

Thus, for a TQFN(4x4)-24 package ΘJA = +30.5°C/W, the maximum allowed TAMB is given by:

TJ,MAX = TAMB + PD x ΘJA = 150°C = TAMB + 0.865W x 30.5°C/W (EQ 4)

In this example the maximum ambient temperature must stay below 123.61°C.

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 19 - 24

AS1115

Datasheet - Ty p i c a l A p p l i c a t i o n

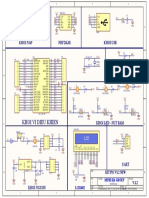

8x8 Dot Matrix Mode

The application example in Figure 26 shows the AS1115 in the 8x8 LED dot matrix mode.

The LED columns have common cathodes and are connected to the DIG0:7 outputs. The rows are connected to the

segment drivers. Each of the 64 LEDs can be addressed separately. The columns are selected via the digits as listed

in Table 6 on page 12.

The Decode Enable Register (see page 13) must be set to ‘00000000’ as described in Table 8 on page 13. Single

LEDs in a column can be addressed as described in Table 11 on page 15, where bit D0 corresponds to segment G and

bit D7 corresponds to segment DP.

Figure 26. Application Example as LED Dot Matrix Driver

VDD DIG0 to

2.7 to 5V

DIG7

9.53kΩ

ISET SEG A to G

SEP DP

SDA AS1115 Diode Arrangement

SDA

SCL

SCL

IRQ

µP IRQ

GND

Keyscan

The key readback of the AS1115 can be used either for push buttons as well as switches. If only a single key is

pressed (shorted) at a time no additional diodes are required. If a detection of multiple simultaneous keystrokes is

required diodes within the keypath, as shown in Figure 27, are required. Pressing multiple keys without the diodes

would result in ambiguous results. Since KEYA and KEYB have independent inputs only keys on the same path are

affected.

Figure 27. Keyscan Configuration

SEGA SEGB SEGC SEGD SEG E SEGF SEGG SEGDP

KEYA

KEYB

IRQ Diodes are optional and only required if multiple keystrokes must be

detected simultaneously.

If I²C Self-Adressing is used these two keys cannot be used for read-

back and must be either hard wired opened or shorted.

A short writes a logical “0” whereas an open writes a logical “1” as

address bit.

Note: If the blink_en bit (bit D4 in the Feature Register 0x0E) is set to ‘1’, the keyscan is not returning a valid value.

Supply Bypassing and Wiring

In order to achieve optimal performance the AS1115 should be placed very close to the LED display to minimize effects

of electromagnetic interference and wiring inductance.

Furthermore, it is recommended to connect a 10µF and a 0.1µF ceramic capacitor between pins VDD and GND to

avoid power supply ripple (see Figure 26).

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 20 - 24

AS1115

Datasheet - P a c k a g e D r a w i n g s a n d M a r k i n g s

10 Package Drawings and Markings

The AS1115 is available in the QSOP-24 package.

Figure 28. QSOP-24 Package

Symbol Min Max

A 1.35 1.75

A1 0.10 0.25

A2 1.37 1.57

b 0.20 0.30

C 0.19 0.25

D 8.55 8.74

E 5.79 6.20

E1 3.81 3.99

e 0.635 BSC

h 0.22 0.49

L 0.40 1.27

θ 0º 8º

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 21 - 24

AS1115

Datasheet - P a c k a g e D r a w i n g s a n d M a r k i n g s

Figure 29. TQFN(4x4)-24 Package

19 20 21 22 23 24

18 1

17 2

16 3

15 4

14 5

13 6

12 11 10 9 8 7

m

m

Symbol Min Typ Max Symbol Min Typ Max

A 0.50 0.55 0.60 e 0.50BSC

A1 0.00 0.05 L 0.30 0.35 0.40

A3 0.152REF L1 0.00 0.10

b 0.18 0.23 0.28 aaa 0.10

D 4.00BSC bbb 0.10

E 4.00BSC ccc 0.10

D2 2.70 2.80 2.90 ddd 0.05

E2 2.70 2.80 2.90 eee 0.08

Notes:Unilateral coplanarity zone applies to the exposed heat sink slug as well as the terminals.

1. All dimensions are in millimeters; angles in degrees.

2. Dimension b applies to metallized terminal and is measured between 0.25mm and 0.30mm from terminal tip.

Dimension L1 represents terminal full back from package edge up to 0.1mm is acceptable.

3. Coplanarity applies to the exposed heat slug as well as the terminal.

4. Radius on terminal is optional.

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 22 - 24

AS1115

Datasheet - O r d e r i n g I n f o m a t i o n

11 Ordering Infomation

The devices are available as the standard products shown in Table 24.

Table 24. Ordering Information

Ordering Code Marking Description Delivery Form Package

AS1115-BSST AS1115 64 LEDs, I²C Interfaced LED Driver Tape and Reel QSOP-24

AS1115-BQFT ASSD with Keyscan Tape and Reel TQFN(4x4)-24

Note: All products are RoHS compliant and Pb-free.

Buy our products or get free samples online at ICdirect: http://www.austriamicrosystems.com/ICdirect

For further information and requests, please contact us mailto:sales@austriamicrosystems.com

or find your local distributor at http://www.austriamicrosystems.com/distributor

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 23 - 24

AS1115

Datasheet

Copyrights

Copyright © 1997-2010, austriamicrosystems AG, Tobelbaderstrasse 30, 8141 Unterpremstaetten, Austria-Europe.

Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged,

translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

Disclaimer

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing

in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding

the information set forth herein or regarding the freedom of the described devices from patent infringement.

austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice.

Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for

current information. This product is intended for use in normal commercial applications. Applications requiring

extended temperature range, unusual environmental requirements, or high reliability applications, such as military,

medical life-support or life-sustaining equipment are specifically not recommended without additional processing by

austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show

deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However,

austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to

personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or

consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the tech-

nical data herein. No obligation or liability to recipient or any third party shall arise or flow out of

austriamicrosystems AG rendering of technical or other services.

Contact Information

Headquarters

austriamicrosystems AG

Tobelbaderstrasse 30

A-8141 Unterpremstaetten, Austria

Tel: +43 (0) 3136 500 0

Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.austriamicrosystems.com/contact

www.austriamicrosystems.com/LED-Driver-ICs/AS1115 Revision 1.06 24 - 24

Você também pode gostar

- 910990-Identify Mobile Phone Parts and Integrated Circuit ICs With Phone Parts Diagram 2019Documento11 páginas910990-Identify Mobile Phone Parts and Integrated Circuit ICs With Phone Parts Diagram 2019Asmie DamtieAinda não há avaliações

- RTN 950A V100R005C01 Product Description 01 PDFDocumento200 páginasRTN 950A V100R005C01 Product Description 01 PDFHamid RazaAinda não há avaliações

- Radio MobileDocumento39 páginasRadio MobilewladimirAinda não há avaliações

- Exploring PIC microcontrollers using MPLAB and ProteusDocumento13 páginasExploring PIC microcontrollers using MPLAB and ProteusErandi Brito100% (1)

- 433aschematic PDFDocumento1 página433aschematic PDFCarlos Vasquez100% (1)

- ProteusDocumento12 páginasProteusGuesh Gebrekidan100% (1)

- 1-Basics of MicroprocessorDocumento9 páginas1-Basics of Microprocessorafzal_a100% (1)

- PIC Real Time Clock DS1307: Analogue Keys Multiplexed 7seg Display IcspDocumento1 páginaPIC Real Time Clock DS1307: Analogue Keys Multiplexed 7seg Display Icspveeramaniks408100% (1)

- 256/128 Kbit Serial I C Bus EEPROM Without Chip Enable LinesDocumento16 páginas256/128 Kbit Serial I C Bus EEPROM Without Chip Enable LinesRoni Socompi100% (1)

- BLOCK DIAGRAM AUDIO VIDEO LCD CONTROLDocumento15 páginasBLOCK DIAGRAM AUDIO VIDEO LCD CONTROLMechDR100% (1)

- Practical PIC ProjectsDocumento14 páginasPractical PIC ProjectsArdhika Dhennis Putra Ananda100% (1)

- Esp32 Devkitc v4-SchDocumento1 páginaEsp32 Devkitc v4-SchCamilo Sànchez100% (1)

- Arduino Uno Schematic Annotated1Documento1 páginaArduino Uno Schematic Annotated1matthewwu2003100% (1)

- An 9723Documento2 páginasAn 9723Stacy Mcclain100% (1)

- Basic 16f877Documento1 páginaBasic 16f877api-27535945100% (1)

- By Marl Us: Lighting The Right To TheDocumento7 páginasBy Marl Us: Lighting The Right To TheGiancarloRichardRivadeneyraMiranda100% (1)

- Schematic PDFDocumento1 páginaSchematic PDFMajk Stone100% (1)

- 16FUSB Schematic-1.2 PDFDocumento1 página16FUSB Schematic-1.2 PDFgermanmkurylo100% (1)

- RemoteDocumento2 páginasRemotejithinraj33100% (1)

- How Do You Determine The Frequency of A Pulse Sequence and Speeds - ID - 27864874 - Industry Support Siemens PDFDocumento1 páginaHow Do You Determine The Frequency of A Pulse Sequence and Speeds - ID - 27864874 - Industry Support Siemens PDFBENICHOU Houari100% (1)

- Advanced Microcontrollers: Chapter - 26Documento36 páginasAdvanced Microcontrollers: Chapter - 26ramesh_br85100% (1)

- ECG PC CircuitDocumento1 páginaECG PC CircuitSanchitha Ashok100% (1)

- Home security system circuit diagramDocumento1 páginaHome security system circuit diagramVũ Thị Thu Hương100% (1)

- U2 chip circuit diagramDocumento1 páginaU2 chip circuit diagramTuan Anh100% (1)

- Osoyoo Balance Car Robot DigramDocumento1 páginaOsoyoo Balance Car Robot DigramSW100% (1)

- LilyGo SIM800C 20200630Documento4 páginasLilyGo SIM800C 20200630Bill Ordoñez Egoavil100% (1)

- Mach Nguyen LyDocumento1 páginaMach Nguyen Lytín nguyễn100% (1)

- Micro Smart ManualDocumento455 páginasMicro Smart ManualJuan Carlos100% (1)

- Circuit DiagramDocumento10 páginasCircuit DiagramM Rameez Ur Rehman100% (1)

- Circuit diagram titleDocumento5 páginasCircuit diagram titleAnonymous smdEgZN2Ie100% (1)

- Octal Configurable Low/High Side Driver: DescriptionDocumento18 páginasOctal Configurable Low/High Side Driver: DescriptionDan Esenther100% (1)

- 16Fxxx With ICSPDocumento3 páginas16Fxxx With ICSPAlonso Corado100% (2)

- 10.1 I2C Basics - EngscopeDocumento8 páginas10.1 I2C Basics - Engscopeshadow_smdk100% (1)

- LCD 8051 Ver1Documento6 páginasLCD 8051 Ver1Nur Razanah Mohd Yasin100% (1)

- Schematic - Kit EZPICDocumento1 páginaSchematic - Kit EZPICNguyen Huu Quang100% (2)

- 4 Pin LCDDocumento13 páginas4 Pin LCDVenkata Konda Reddy Mulle100% (1)

- Pic18 Interrupt 2Documento19 páginasPic18 Interrupt 2adamwaiz100% (3)

- Sheet 2Documento2 páginasSheet 2Jesus Crispin100% (1)

- 89c51 - Projectboard - Circuit DiagramDocumento2 páginas89c51 - Projectboard - Circuit DiagramNirmal Vinu100% (1)

- SCH Mainboard ESP32 S2 Drone V1 2Documento1 páginaSCH Mainboard ESP32 S2 Drone V1 2Brijesh Savliya100% (1)

- Lab2 MotorControl 08Documento18 páginasLab2 MotorControl 08ĐạiDương100% (1)

- A Usb Rev 1 - 00Documento1 páginaA Usb Rev 1 - 00jceletronic100% (2)

- Unit - Iii MPMC-1Documento79 páginasUnit - Iii MPMC-1gunda manasa100% (1)

- Analog Front-End Signal ConditioningDocumento4 páginasAnalog Front-End Signal ConditioningRene Gonzales Vasquez100% (2)

- Wireless device circuit diagramDocumento1 páginaWireless device circuit diagramnilton santos machado100% (1)

- Destm32 L1 11 - SCHDocumento1 páginaDestm32 L1 11 - SCHHolop100% (1)

- LPC P2148Documento19 páginasLPC P2148Sharath Babu100% (1)

- Choosing The Correct DigipotDocumento4 páginasChoosing The Correct Digipottubeman1814100% (1)

- SSC-32 Ver 2.0: Manual Written For Firmware Version SSC32-1.06XE Range Is 0.50mS To 2.50mSDocumento15 páginasSSC-32 Ver 2.0: Manual Written For Firmware Version SSC32-1.06XE Range Is 0.50mS To 2.50mSSergio Juan100% (1)

- Simple Icom CI-V InterfaceDocumento2 páginasSimple Icom CI-V InterfaceMike100% (1)

- Opamp TIDocumento5 páginasOpamp TIAmogh Gajaré100% (1)

- Reset VCC H1 H2 H3 H4 H5 H6 H7 H8Documento1 páginaReset VCC H1 H2 H3 H4 H5 H6 H7 H8Vt Tung100% (1)

- Parity Bit Generator Using 3 Input XOR GDocumento6 páginasParity Bit Generator Using 3 Input XOR Gvirat sharma100% (1)

- LCDCharacterDocumento1 páginaLCDCharacterJIGNESH100% (1)

- Picprog CircuitDocumento1 páginaPicprog Circuitmiguel709100% (1)

- PIC Programming Module USB and Traffic Light System ControllerDocumento26 páginasPIC Programming Module USB and Traffic Light System ControllerJosh, LRT100% (1)

- W6100-Evb SCH V110 PDFDocumento3 páginasW6100-Evb SCH V110 PDFYuriy100% (2)

- I2C Interface To Serial EEPROMDocumento8 páginasI2C Interface To Serial EEPROMShri Kulkarni100% (1)

- PHOENIX - RS232 - 485 To TCPDocumento14 páginasPHOENIX - RS232 - 485 To TCPJorge_Andril_5370100% (1)

- Assembly Language Programming Memory Segmentation and RegistersDocumento9 páginasAssembly Language Programming Memory Segmentation and RegistersJayvee Coliao100% (1)

- HdmiDocumento1 páginaHdmiAbhishek100% (2)

- Features: 8-Character, 16-Segment, Microprocessor Compatible, LED Display Decoder DriverDocumento13 páginasFeatures: 8-Character, 16-Segment, Microprocessor Compatible, LED Display Decoder DriverPedro Pablo Escobar MartinezAinda não há avaliações

- Deh 2390ubDocumento16 páginasDeh 2390ubapurva_bahadur100% (2)

- E - Commerce: Ever Changing Future of The Business WorldDocumento11 páginasE - Commerce: Ever Changing Future of The Business Worldemilio greg diegoAinda não há avaliações

- ATCommandSet StepIIIDocumento70 páginasATCommandSet StepIIIeduranddecassisAinda não há avaliações

- User Manual: Question? Contact PhilipsDocumento53 páginasUser Manual: Question? Contact PhilipsYvesAinda não há avaliações

- Characteristics of IoTDocumento4 páginasCharacteristics of IoTmikkumar5Ainda não há avaliações

- FIXML Technical BackgroundDocumento13 páginasFIXML Technical BackgroundЮра ПальчикAinda não há avaliações

- Toshiba - STI 1422 - ECS R42IIX - 37GR42000-C0 PDFDocumento39 páginasToshiba - STI 1422 - ECS R42IIX - 37GR42000-C0 PDFAnildo Eldivar De Oliveira Sarmento100% (1)

- PLDT Ar 2018 Fiber PowerDocumento149 páginasPLDT Ar 2018 Fiber PowerAnna Sophia YorkAinda não há avaliações

- New PVR Android - DWI859SDocumento18 páginasNew PVR Android - DWI859SS H ZaidiAinda não há avaliações

- Cisco Nexus 9000 Series NX-OS VXLAN Configuration Guide, Release 9.3 (X)Documento560 páginasCisco Nexus 9000 Series NX-OS VXLAN Configuration Guide, Release 9.3 (X)Hoang HanAinda não há avaliações

- Compressive Sensing – A 25 Minute TourDocumento49 páginasCompressive Sensing – A 25 Minute Tourandres alfonso varelo silgadoAinda não há avaliações

- C&C08 OVSV610R103 H302HCB Frame Deployment Guide (V1.00) - 20050110-BDocumento17 páginasC&C08 OVSV610R103 H302HCB Frame Deployment Guide (V1.00) - 20050110-BAbdullatif0% (1)

- Megmeet PartsDocumento2 páginasMegmeet Partsnugraha1805Ainda não há avaliações

- Fingerprint Time Attendance & Access Control Termin Al: FeaturesDocumento2 páginasFingerprint Time Attendance & Access Control Termin Al: FeaturesnammarisAinda não há avaliações

- SRX4100 and SRX4200 Services Gateways: Product DescriptionDocumento6 páginasSRX4100 and SRX4200 Services Gateways: Product DescriptionLiviu MeliothAinda não há avaliações

- Archive: DatasheetDocumento12 páginasArchive: DatasheetIan WallaceAinda não há avaliações

- Hfe JBL s4800Documento3 páginasHfe JBL s4800Steve WalschotAinda não há avaliações

- M.Tech Lab Manual-FInal-4.8.2021Documento28 páginasM.Tech Lab Manual-FInal-4.8.2021RAMYA VATHSALYA PAinda não há avaliações

- 3GPP TS 24.008Documento729 páginas3GPP TS 24.008holapaquitoAinda não há avaliações

- Mvh-A208vbt - Manual de ServicoDocumento74 páginasMvh-A208vbt - Manual de ServicoFernando Aparecido BaldáviaAinda não há avaliações

- Vfe Out-Band DCN MopDocumento34 páginasVfe Out-Band DCN Mopmohamed abdel karimAinda não há avaliações

- Argus Nnpx412m E1 PDFDocumento1 páginaArgus Nnpx412m E1 PDFSuwarno サスケAinda não há avaliações

- 5.7 GHZ SM: Specifications Sheet Motorola CanopyDocumento1 página5.7 GHZ SM: Specifications Sheet Motorola CanopyperuingenierosAinda não há avaliações

- IT4000 Service Manual OriginalDocumento177 páginasIT4000 Service Manual OriginalAlejandro Lay100% (2)

- 2022 Interactive Whiteboard Catalog Iproda 1Documento3 páginas2022 Interactive Whiteboard Catalog Iproda 1Realg4 LifeAinda não há avaliações

- Manual de Serviço - DEP250Documento237 páginasManual de Serviço - DEP250Anderson Gomes Resende (Gres)Ainda não há avaliações

- Call For Papers: ISSN: 0976 - 1764 (Online) 0976 - 2205 (Print)Documento3 páginasCall For Papers: ISSN: 0976 - 1764 (Online) 0976 - 2205 (Print)ijasucAinda não há avaliações