Escolar Documentos

Profissional Documentos

Cultura Documentos

SystemVerilog Verif

Enviado por

Sunil SharmaDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

SystemVerilog Verif

Enviado por

Sunil SharmaDireitos autorais:

Formatos disponíveis

SystemVerilog for Verification Professionals

3 Days

50% lecture, 50% lab

Advanced Level

Note: This course was developed and is taught by XtremeEDA, a company which specializes

in verification consulting and training.

Overview

In the semiconductor industry, faster time-to-market is the key to gaining a strong

competitive advantage in the marketplace. Having a leading edge verification methodology is

vital to achieving this. Our newest course offering SystemVerilog for Verification

Professionals provides everything that you, the verification professional, need to create

advanced constrained-random coverage-driven self-checking testbenches in the

SystemVerilog language. From data types to program blocks and interfaces, to interprocess

synchronization and communication, you will learn everything you need to create advanced

SystemVerilog verification environments. This course details the advanced verification

features of the language, focusing on constrained randomization, assertions, functional

coverage, and other tools that facilitate an effective reusable verification environment.

Throughout the course an example design is taken through the entire verification process,

implementing a state-of-the-art, coverage-driven, constrained-random, assertion-based

verification environment.

Intended Audience

This course is designed for Hardware Verification Professionals who are interested in

furthering their knowledge of verification.

Prerequisites

A good grasp of Verilog is required.

Course Outline:

Day 1 • The SystemVerilog solution

• Introduction to Coverage Driven

Verification Methodology Overview Verification (CDV) methodology

• Traditional verification approaches

• Issues with tradition verification SystemVerilog Syntax

approaches • Data types

TM Associates, Inc ● www.tm-associates.com ● 503-656-4457

• Arrays and queues • Modports

• Data declarations • Tasks/functions

• Operators and expressions • Parameterized

• New SystemVerilog statements • Virtual

• Tasks and functions

Day 3

Day 2

Intelligent Self Checking

Object Oriented Programming (OOP) • Checking Methodology

• OOP methodology overview • SystemVerilog Assertions (SVA)

• Classes • Immediate

• Properties and methods • Sequences

• Constructors • Properties

• Data hiding • Assertion coverage and control

• Encapsulation • Data Checking

• Polymorphism

• Inheritance Functional Coverage

• Coverage methodology

Constrained-Random Generation • Different forms of coverage

• Random variables • Defining coverage groups

• The randomize() function • Defining coverage bins

• Defining constraints • Transition coverage

• Random number generation • Cross coverage

• Random stability • Coverage options

• Random sequences • Architecting coverage

Driving and Receiving Data Miscellaneous Features

• Clocking blocks • File I/O

• Program blocks • New messaging tasks

• Concurrency and synchronization • Direct Programming Interface (DPI)

• Interfaces

Laboratory Exercises:

Laboratory exercises (10 in total) will be performed by the student throughout the duration of

the course.

For more information, contact:

Tom Wille • tw@tm-associates.com

TM Associates, Inc. • 503-656-4457

www.tm-associates.com

TM Associates, Inc ● www.tm-associates.com ● 503-656-4457

Você também pode gostar

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- FDMEE Admin Guide PDFDocumento554 páginasFDMEE Admin Guide PDFpraveenkumarvi53810% (1)

- Word-Order-In-English - Vi2 PDFDocumento6 páginasWord-Order-In-English - Vi2 PDFwahyu chandra wijayaAinda não há avaliações

- Explanation of Weld SymbolsDocumento2 páginasExplanation of Weld SymbolspmjoshirAinda não há avaliações

- Engaging The Moving Image Noel CarrolliDocumento449 páginasEngaging The Moving Image Noel CarrolliSonny PrentAinda não há avaliações

- The Platonic Reading of AugustineDocumento35 páginasThe Platonic Reading of AugustineAndrés Solís100% (1)

- World Languages Committee BookletDocumento75 páginasWorld Languages Committee BookletmarthaAinda não há avaliações

- Wonderware Alarm DB Logger Object For Wonderware Application Server User Guide Ver 1.x Rev 1.0 PR 00186Documento17 páginasWonderware Alarm DB Logger Object For Wonderware Application Server User Guide Ver 1.x Rev 1.0 PR 00186Dino PradanaAinda não há avaliações

- Intriduction - SAMDocumento33 páginasIntriduction - SAMmuraliAinda não há avaliações

- Fluid Statics PrintDocumento16 páginasFluid Statics PrintJoanne SoloriaAinda não há avaliações

- CMS Web App User Guide 3 2Documento42 páginasCMS Web App User Guide 3 2రవి కిరణ్ పూలAinda não há avaliações

- BC9180 Software Reference Guide (ENG)Documento56 páginasBC9180 Software Reference Guide (ENG)brasicanoAinda não há avaliações

- Worship: For The Leadership Podcast With Pastor Steve MurrellDocumento1 páginaWorship: For The Leadership Podcast With Pastor Steve MurrellRhegie SamonteAinda não há avaliações

- Relationship Between Henry Higgins and Eliza DoolittleDocumento5 páginasRelationship Between Henry Higgins and Eliza DoolittleUmal MalikAinda não há avaliações

- A Look at Architypal CriticismDocumento9 páginasA Look at Architypal Criticismseeker03Ainda não há avaliações

- Rizal's LifeDocumento32 páginasRizal's LifenngabacAinda não há avaliações

- Linear Search and Binary SearchDocumento24 páginasLinear Search and Binary SearchADityaAinda não há avaliações

- Chapter 3 - SelectionsDocumento52 páginasChapter 3 - Selectionsnaqibullah2022faryabAinda não há avaliações

- Imaginea Pascala La EvIOAN PAcifica 2012Documento16 páginasImaginea Pascala La EvIOAN PAcifica 2012CinevaAinda não há avaliações

- Program TemplateDocumento2 páginasProgram TemplateErwin MigalangAinda não há avaliações

- Design of Sensor Nodes in Underwater Sensor Networks: Yu Yang, Zhang Xiaomin, Peng BO, Fu YujingDocumento5 páginasDesign of Sensor Nodes in Underwater Sensor Networks: Yu Yang, Zhang Xiaomin, Peng BO, Fu Yujinghari9923Ainda não há avaliações

- Senior High School Student Permanent Record: Republic of The Philippines Department of EducationDocumento3 páginasSenior High School Student Permanent Record: Republic of The Philippines Department of EducationJennisRollenAranetaMaagadAinda não há avaliações

- Group 5 - Modal AdverbDocumento13 páginasGroup 5 - Modal AdverbLidya Margareta MahulaeAinda não há avaliações

- Careerit Devops Course ContentDocumento9 páginasCareerit Devops Course Contentdileep.sAinda não há avaliações

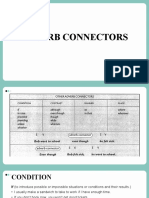

- Adverb ConnectorDocumento11 páginasAdverb ConnectorAges TiaraAinda não há avaliações

- Assignment 1: Instruction: Answer The Following Question IndependentlyDocumento4 páginasAssignment 1: Instruction: Answer The Following Question IndependentlyAntoine John GalichaAinda não há avaliações

- Framework Development of FTP Programs Mini Project - ReportDocumento13 páginasFramework Development of FTP Programs Mini Project - ReportBaburam KumaraswaranAinda não há avaliações

- Linq - Beyond Queries: LINQ For Better Business LogicDocumento15 páginasLinq - Beyond Queries: LINQ For Better Business LogicDanish QureshiAinda não há avaliações

- Rainbow Class 7Documento94 páginasRainbow Class 7Yassilya GhizlaneAinda não há avaliações

- Math-5-video-Lesson Script-2Documento8 páginasMath-5-video-Lesson Script-2charm sobremisanaAinda não há avaliações

- Set 2 Book 3: Pip and PogDocumento35 páginasSet 2 Book 3: Pip and PogSuganya PalanisamyAinda não há avaliações