Escolar Documentos

Profissional Documentos

Cultura Documentos

Lista Exercicios P2

Enviado por

braust torresDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Lista Exercicios P2

Enviado por

braust torresDireitos autorais:

Formatos disponíveis

EXERCÍCIOS – CIRCUITOS DIGITAIS

1) O circuito abaixo refere-se a um contador assíncrono disparado por borda positiva. Adotar que

inicialmente os flip-flops estejam resetados.

a) Montar a tabela verdade para 4 pulsos de clock e obter seu respectivo diagrama de

temporização.

b) De acordo com a resposta obtida no item anterior, qual a função deste circuito?

2) Considerando um contador de 3 flip-flops, qual a relação existente entre as freqüências

apresentadas em suas respectivas saídas?

3) O que é módulo de um contador?

4) Monte o circuito de um contador síncrono crescente de 2 bits e obtenha sua tabela de

sequência de estados para 4 pulsos de clock, adotando que inicialmente a saída do contador é 01.

5) No exercício anterior foi possível entender o princípio de funcionamento de um contador

síncrono crescente de 2 bits. Que alteração poderia ser feita no circuito do contador do exercício

anterior para que operasse como um contador decrescente síncrono de 2 bits? Monte o circuito.

6) Implementar um contador assíncrono de módulo seis disparado por borda positiva utilizando

FF’s JK. Desenhe o diagrama elétrico e o diagrama de transição das saídas.

7) Implentar um contador assíncrono de módulo 12. Esboce o diagrama de transição das saídas

8) Montar o diagrama elétrico de um contador síncrono crescente de módulo 8.

9) Refaça o exercício anterior adotando um módulo igual a 7.

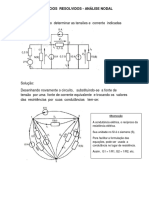

10) Para o circuito crescente/decrescente de 2 bits apresentado a seguir, inicialmente o flip-flop

FF0 está setado e o flip-flop FF1 está resetado. Obter o diagrama de transições e a tabela de

sequência de estados adotando que a entrada de controle é nível ALTO para os primeiros 2

pulsos de clock e nível BAIXO para os 4 pulsos de clock seguintes.

11) Para o circuito crescente/decrescente de 3 bits apresentado abaixo, os flip-flops encontram-se

inicialmente resetados. Obter o diagrama de transições e a tabela de sequência de estados

adotando que a entrada de controle é nível ALTO para os primeiros 8 pulsos de clock e nível

BAIXO para os 8 pulsos de clock seguintes.

12) Obtenha a tabela verdade, a expressão booleana e o diagrama lógico para um MUX de 8

canais de entrada.

13) Obter um MUX de 4 canais utilizando MUX de 2 canais. Qual a finalidade desta ampliação

da capacidade de canais?

14) Obter um MUX de 16 canais utilizando apenas MUX de 4 canais.

15) Realizar um DEMUX de 4 canais. Obter sua tabela e seu respectivo diagrama lógico.

16) Realizar um DEMUX de 16 canais. Obter sua tabela e seu respectivo diagrama lógico.

17) Obter um DEMUX de 4 canais utilizando DEMUX de 2 canais.

Você também pode gostar

- Elb BasicaDocumento2 páginasElb Basicabraust torresAinda não há avaliações

- LISTA Ce2 (3) - RESOLVIDA - EXERCICIOS DIVERSOSDocumento8 páginasLISTA Ce2 (3) - RESOLVIDA - EXERCICIOS DIVERSOSbraust torresAinda não há avaliações

- Exercícios resolvidos de circuitos RLCDocumento13 páginasExercícios resolvidos de circuitos RLCbraust torresAinda não há avaliações

- LISTA Ce24 - RESOLVIDA - EXERCICIOS DIVERSOSDocumento5 páginasLISTA Ce24 - RESOLVIDA - EXERCICIOS DIVERSOSbraust torresAinda não há avaliações

- EEIG Lista2 10EXDocumento7 páginasEEIG Lista2 10EXbraust torresAinda não há avaliações

- LISTA Ce2 (1) - RESOLVIDA - EXERCICIOS DIVERSOSDocumento8 páginasLISTA Ce2 (1) - RESOLVIDA - EXERCICIOS DIVERSOSbraust torresAinda não há avaliações

- EEIG Lista1 10EXDocumento3 páginasEEIG Lista1 10EXbraust torresAinda não há avaliações

- EEIG Lista1 10EXDocumento3 páginasEEIG Lista1 10EXbraust torresAinda não há avaliações

- EEIG Lista1 10EXDocumento3 páginasEEIG Lista1 10EXbraust torresAinda não há avaliações

- Wild 7 Alnico - Spirit PickupsDocumento1 páginaWild 7 Alnico - Spirit PickupsheraldoAinda não há avaliações

- Motores A Diesel Marítimos PDFDocumento21 páginasMotores A Diesel Marítimos PDFRogério JuniorAinda não há avaliações

- Curso Online Paralisia FacialDocumento84 páginasCurso Online Paralisia FacialAnne Kelly Sales100% (3)

- FARIA - Acordes Arpejos e EscalasDocumento82 páginasFARIA - Acordes Arpejos e EscalasFelipe Eugenio VinhalAinda não há avaliações

- CERRADO Matas de GaleriaDocumento178 páginasCERRADO Matas de GaleriaMurilo HenriqueAinda não há avaliações

- ESTRADA ILUMINADAE.I.Bichano e Zumbi 1ºanoDocumento81 páginasESTRADA ILUMINADAE.I.Bichano e Zumbi 1ºanoPriscila ParreiraAinda não há avaliações

- CadernoExercicios (CircuitosI)Documento59 páginasCadernoExercicios (CircuitosI)Rodrigo ArrudaAinda não há avaliações

- Técnico de DesportoDocumento14 páginasTécnico de DesportoDavid RodriguesAinda não há avaliações

- Estudo de Caso MAgazineDocumento2 páginasEstudo de Caso MAgazineAlisson SouzaAinda não há avaliações

- 20 Bienal de São Paulo - Vol. I 1989Documento248 páginas20 Bienal de São Paulo - Vol. I 1989AlineAugustaAinda não há avaliações

- Estratégias da Apple para dupla não tributaçãoDocumento16 páginasEstratégias da Apple para dupla não tributaçãoFernando MasagãoAinda não há avaliações

- Dramaturgia Das Histórias - KISHOTENKETSUDocumento27 páginasDramaturgia Das Histórias - KISHOTENKETSUronaldsverasAinda não há avaliações

- Bolo de Cenoura Yämmi - Receitas - ContinenteDocumento1 páginaBolo de Cenoura Yämmi - Receitas - ContinenteJorge SantosAinda não há avaliações

- Diagnóstico Sócio-Demográfico Vale AlcântaraDocumento73 páginasDiagnóstico Sócio-Demográfico Vale AlcântaraProjecto AlkantaraAinda não há avaliações

- ComparDocumento1 páginaComparelivelton souzaAinda não há avaliações

- artigo 3 gestantesDocumento14 páginasartigo 3 gestantesPaula OliveiraAinda não há avaliações

- Lista 1Documento6 páginasLista 1Igor Rocha AlvesAinda não há avaliações

- Organização da Rede Básica do SUSDocumento46 páginasOrganização da Rede Básica do SUSGleicy SantosAinda não há avaliações

- Bomba KSB - Ama Drainer N 302 SEDocumento24 páginasBomba KSB - Ama Drainer N 302 SEAlexAntonioPradoAinda não há avaliações

- A rede do conhecimento tradicional da linhagem taoísta Pai LinDocumento196 páginasA rede do conhecimento tradicional da linhagem taoísta Pai LinBeatriz OrsolonAinda não há avaliações

- Memoria Descritiva (Com Imagens)Documento31 páginasMemoria Descritiva (Com Imagens)Sergio RochaAinda não há avaliações

- A Importância Do Esporte para A Qualidade de Vida - KLEBERDocumento1 páginaA Importância Do Esporte para A Qualidade de Vida - KLEBERHadassa.c officeAinda não há avaliações

- ComoCriarRPGDocumento30 páginasComoCriarRPGRubens CostaAinda não há avaliações

- BrasíliaDocumento28 páginasBrasíliaIsaque Julião ChagasAinda não há avaliações

- COVID-19 tabela de ocupação máxima de áreas comerciais até 300m2Documento1 páginaCOVID-19 tabela de ocupação máxima de áreas comerciais até 300m2Cristiano SouzaAinda não há avaliações

- Formações de Kitesurf AKSDocumento11 páginasFormações de Kitesurf AKSCarlosAinda não há avaliações

- OverheadDocumento8 páginasOverheadadriano_pittel9936Ainda não há avaliações

- Manual Diagrama Da TartarugaDocumento4 páginasManual Diagrama Da TartarugaGabrielle MarquesAinda não há avaliações

- Resenha - o Silencio Dos Homens - Kalina LimaDocumento2 páginasResenha - o Silencio Dos Homens - Kalina LimaKalina Lima SantosAinda não há avaliações

- Tecnologias de manejo florestal sustentável na AmazôniaDocumento4 páginasTecnologias de manejo florestal sustentável na AmazôniaalissongsousaAinda não há avaliações