Escolar Documentos

Profissional Documentos

Cultura Documentos

Practicas

Enviado por

Liam JJTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Practicas

Enviado por

Liam JJDireitos autorais:

Formatos disponíveis

Curso 2004/2005 1

Práctica 0.- Introducción

Objetivos.

El objetivo de esta práctica consiste en la realización de un pequeño montaje, así como

su simulación, para que el alumno se familiarice con el laboratorio y su instrumental.

Problema.

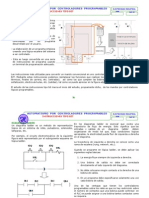

Se dispone del siguiente circuito, donde hemos utilizado puertas AND que realizan el

producto lógico u operación AND y puertas OR que realizan la suma lógica u operación OR:

Puerta AND

A

B

Puerta OR

F

C

Se pide realizar las siguientes tareas:

• Obtener de forma teórica el valor de la señal de salida (F) para todas las combinacio-

nes de las tres señales de entrada (A, B, C), así como pasarla a un cronograma.

• Obtener mediante simulación el cronograma de la señal F recorriendo todas las com-

binaciones posibles de las señales de entrada. Para ello, y de forma previa, se debe

obtener el retraso máximo del circuito.Pasar del cronograma obtenido a una tabla de

combinaciones (esperar a que el circuito haya finalizado la operación para incluirla en

la tabla).

• Montar el circuito y obtener el valor de la señal de salida para todas las combinacio-

nes de las señales de entrada. ¿Qué valores obtenemos si no conectamos la alimenta-

ción?, ¿y si no conectamos la tierra?, ¿y si no conectamos ni la alimentación ni la

tierra?

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 2

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 3

Solución de la Práctica 0

Estudio teórico.

El circuito de la figura está formado por una puerta AND, que realiza el producto lógico,

y una puerta OR, que realiza la suma lógica. El comportamiento de estas operaciones es el

mostrado en la siguiente tabla.

A B A·B A+B

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 1

Por lo tanto, el valor de la señal F será el mostrado en la siguiente tabla.

A B C A·B F

0 0 0 0 0

0 0 1 0 1

0 1 0 0 0

0 1 1 0 1

1 0 0 0 0

1 0 1 0 1

1 1 0 1 1

1 1 1 1 1

El cronograma se muestra a continuación (incluiremos un retraso hipotético para cada combi-

nación).

A·B

Deberá aparecer este pequeño

pulso, ya que la señal C baja

antes que suba el producto

A·B

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 4

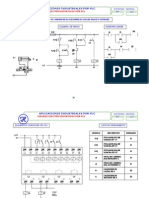

Simulación.

En primer lugar debemos conocer el retraso máximo del circuito. Este retraso será el

correspondiente a la suma de las puertas que estén conectadas en serie (una detrás de otra). En

el caso de que existan más de un grupo de puertas conectadas de esta forma, nos quedaremos

con la suma máxima.

En nuestro caso particular tenemos conectadas en serie una puerta AND y una puerta

OR. Luego el retraso máximo será la suma de los retrasos de la puerta AND y la puerta OR.

Los retrasos de las diferentes puertas son:

• (17.5 + 12)/2 = 14.75 ns para la puerta AND

• (10 + 14)/2 = 12 ns para la puerta OR

Luego el retraso máximo será igual a 26.75 ns.

La descripción del circuito será la siguiente:

-- Descripción del circuito

-- Declaración de la entidad

entity pract_0 is

port(A,B,C : in bit;

F : out bit);

end pract_0;

-- Declaración de la arquitectura

architecture primera of pract_0 is

signal S1 : bit;

begin

-- En el asignamiento se introduce el retraso

-- correspondiente a la puerta

S1 <= A and B after 14.75ns;

F <= C or S1 after 12ns;

end;

Para comprobar que el comportamiento es el correcto debemos realizar una simulación.

Para realizar la simulación debemos describir un nuevo sistema, que siempre vamos a denomi-

nar test. Este sistema no tendrá comunicación con el exterior, y contendrá el circuito que se

quiere simular y los estímulos (combinaciones) de las señales de entrada que se quieran consi-

derar. Un posible esquema de un sistema de test se muestra a continuación.

-- Declaración de un sistema de test

-- Declaración de la entidad

entity test is

end test;

-- Declaración de la arquitectura

architecture primera of test is

signal S1, S2, S3, S4: bit;

component pract_0

port( A,B,C : in bit;

F : out bit);

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 5

end component;

for all:pract_0 use entity work.pract_0;

begin

B1: pract_0 port map (S1, S2, S3, S4);

-- El tiempo de paso de cada combinación debe ser

-- mayor que el retraso máximo del circuito (27ns)

-- En este caso hemos elegido 50ns

S1 <= ‘0’, ‘1’ after 50ns, ‘0’ after 100ns,

‘1’ after 150ns, ‘0’ after 200ns,

‘0’ after 250ns, ‘1’ after 300ns,

‘0’ after 350ns, ‘1’ after 400ns;

S2 <= ‘0’, ‘1’ after 100ns, ‘0’ after 200ns,

‘1’ after 300ns, ‘0’ after 400ns;

S3 <= ‘0’, ‘1’ after 200ns, ‘0’ after 400ns;

end;

Se ha simulado el modelo y hemos obtenido las siguientes formas de onda.

Pulso detectado

en el estudio

teórico

A B C F

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 6

Montaje.

El montaje que se debe realizar puede ser el mostrado en la siguiente figura.

7408

A

B 7432

F

C

+5

7408 7432

A

B

masa

C

F

Una vez realizado el montaje, chequeamos en un LED el valor de la señal F, obteniendo el

siguiente comportamiento.

A B C F

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

A la vista de la tabla anterior podemos comprobar que el comportamiento es el mismo que el

obtenido en el estudio teórico y en la simulación.

En el supuesto de que no conectásemos la alimentación de los integrados, podemos com-

probar que la señal F siempre tiene un valor bajo, independientemente del valor de las señales

de entrada.

En el supuesto de que no conectásemos la tierra de los integrados, podemos comprobar

que la señal F siempre tiene un valor alto, independientemente del valor de las señales de

entrada.

En el supuesto de que no conectásemos ni la alimentación ni la tierra de los integrados,

podemos comprobar que la señal F siempre tiene el mismo valor, independientemente del valor

de las señales de entrada.

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 7

Práctica I.- Álgebra de Boole I

Objetivos.

El objetivo de esta práctica consiste en utilizar y verificar las leyes y teoremas del álgebra

de Boole, así como aplicar los criterios de minimalidad estudiados en las clases teóricas.

Problema.

Un estudio llevado a cabo sobre el crecimiento de dos clases diferentes de fresas, se han

obtenido los siguientes resultados:

• Clase A crece adecuadamente cuando:

• está iluminada y bien regada

• está iluminada y bien abonada

• Clase B crece adecuadamente cuando:

• no está iluminada y bien abonada

• no está regada y bien abonada

para el que se disponen de sensores de iluminación (I), abono (A) y riego (R).

Se nos ha indicado que cualquiera de las siguientes fórmulas lógicas implimenta el sis-

tema de detección anterior:

• FA(I, A, R) = I·A + I·R

FB(I, A, R) = I·A + R·A

• FA(I, A, R) = I·(R+A) + A

FB(I, A, R) = I·A·R + I·R·A + I·R·A

• FA(I, A, R) = I·(R+A)

FB(I, A, R) =A·(R+I)

• FA(I, A, R) = I·A + I·R·A

FB(I, A, R) = R·A + I·R·A

Según estas fórmulas se pide lo siguiente:

• Averiguar cuál de estas fórmulas son equivalentes mediante el Álgebra de Boole.

• Averiguar cuál de estas fórmulas son equivalentes mediante la tabla de combinacio-

nes, así como generar los cronogramas equivalentes.

• Aplicar los criterios de minimalidad a cada una de las fórmulas, cuantificando cada

uno de ellos. Indicar cuáles son las fórmulas mínimas de las diferentes funciones

implementadas.

• Indicar cuáles de las fórmulas implementan el sistema de crecimiento descrito.

• Realizar la simulación de todas las fórmulas, con el fin de verificar los puntos anterio-

res. Como resultado, se debe indicar el cronograma de salida, así como la tabla de

combinaciones equivalente.

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 8

• Realizar el montaje de las fórmulas que implementan el sistema de detección. (Para

ello construir el circuito lógico equivalente para cada caso. Si hay algún operador que

no tenga un equivalente directo en el laboratorio, por el número de entradas, aplicar

las leyes asociativas para obtenerlo).

I R A FA FB

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 9

Práctica II.- Puertas lógicas compuestas

Objetivos.

Introducir al alumno en la utilización y propiedades de puertas compuestas como puertas

NAND, NOR y XOR.

Problema 1.

Una empresa de componentes electrónicos tiene un exceso de puertas NOR. Luego se

nos ha encargado tratar de convencer a un comprador que puede implementar cualquier cir-

cuito utilizando únicamente este tipo de puertas.

Para ello, se pide lo siguiente:

• Obtener de forma teórica la transformación del conjunto completo formado por puer-

tas AND, OR e inversores.

• Obtener de forma teórica como se realizaría una puerta NOR de cuatro entradas utili-

zando únicamente puertas NOR de dos entradas.

• Transformar la fórmula F(x,y,z) = (x+y)·y·z, de tal forma que solamente se utilicen

puertas NOR, y comprobar que ambas fórmulas corresponden a la misma función de

conmutación.

• Realizar la transformación de los puntos anteriores mediante simulación. Pasar del

cronograma obtenido mediante simulación a la siguiente tabla de combinaciones.

U X Y Z X X+Y X·Y X+Y+Z+U FAND,OR,INV FNOR

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 10

• Comprobar la equivalencia de las fórmulas de F(x, y, z), utilizando puertas AND, OR

e inversores, y utilizando únicamente un integrado de puertas NOR, mediante mon-

taje. Para ello, rellenar la siguiente tabla para su posterior comparación.

X Y Z FAND,OR,INV FNOR

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Problema 2.

Seguidamente nos encontramos en una situación muy similar a la del problema anterior,

pero con las puertas XOR. En este caso se pide:

• Demostrar teóricamente que las puertas XOR cumplen la propiedad asociativa.

• En el caso de que las puertas XOR no formen un conjunto completo, encontrar un

conjunto de puertas completo en el que se encuentren las puertas XOR y solamente

otro tipo de puerta más, es decir, los conjuntos podrían ser los siguientes: {XOR,

AND}, {XOR, OR}, {XOR, INV} (Se tienen disponibles los dos niveles lógicos).

• Transformar la fórmula F(x,y,z) = (x+y)·y·z, de tal forma que solamente se utilicen

puertas del conjunto seleccionado, y comprobar que ambas fórmulas corresponden a

la misma función de conmutación.

• Realizar la transformación de los puntos anteriores mediante simulación. Para ello se

deberá pasar el cronograma a una tabla equivalente a la del problema anterior.

FAND,OR, F

U X Y Z X X+Y X·Y X⊕(Y⊕Ζ) (X⊕Y)⊕Ζ NOR

INV

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 11

• Comprobar la equivalencia de las fórmulas de F(x, y, z), utilizando puertas AND, OR

e inversores, y utilizando el conjunto seleccionado, mediante montaje. Para ello, relle-

nar la siguiente tabla para su posterior comparación.

X Y Z FAND,OR,INV FNOR

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 12

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 13

Práctica III.- Análisis de Circuitos

combinacionales (I)

Objetivos.

Esta práctica tiene como principal objetivo introducir al alumno en la problématica del

análisis transitorio de los circuitos combinacionales.

Problema 1.

Se pide estudiar los azares de los siguientes circuitos.

X

Y

X F

x5

x5

Este estudio deberá incluir los siguientes pasos:

• Realizar un estudio teórico del estado transitorio de los circuitos anteriores. Para ello

considerar los hipotéticos retrasos de cada puerta que exista en el circuito, y determi-

nar la relación que debe existir entre los diferentes retrasos para que los posibles aza-

res se muestren en la señal de salida, tras rellenar el siguiente cronograma.

• Realizar las simulaciones de los circuitos con los retrasos obtenidos de las hojas de

especificaciones de las puertas involucradas (para ello utilizar el siguiente ). Compro-

bar que las relaciones temporales obtenidas en el punto anterior se verifican en la

simulación.

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 14

• Montar los circuitos y comprobar en el osciloscopio la presencia o ausencia de azares.

Para ello conectar la entrada X a la señal de reloj suministrada por el entrenador a una

frecuencia de 100 kHz, mientras que las señales Y y Z irán a conmutadores para com-

probar que los azares sólo se ven para las condiciones obtenidas en el primer punto,

rellenando los siguientes cronogramas

¿Para qué transiciones se producen los azares de cada circuito? ¿por qué?

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 15

• Obtener en el laboratorio los retrasos de varias puertas de una misma función lógica,

de varios circuitos integrados diferentes:. En el caso de puertas de dos entradas,

conectar una de ellas a la señal de reloj anterior y la restante al valor lógico que se

comporta como elemento neutro.

Función lógica 1º CI 2º CI 3º CI 4º CI

Puerta AND (2 entradas)

Puerta NAND (2 entradas)

Puerta OR (2 entradas)

Puerta NOR (2 entradas)

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 16

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 17

Práctica IV: Análisis de Circuitos

Combinacionales (II)

Objetivos.

Esta práctica tiene como principal objetivo introducir al alumno en la problématica del

análisis de los circuitos combinacionales.

Problema 1.

Una empresa de telecomunicaciones dispone del siguiente circuito lógico:

b0

b1

b2

F1

F2

donde b2, b1 y b0 son los bits correspondientes a una palabra de código y las salidas F1 y F2

detectan cuáles de las combinaciones binarias pertenecen realmente al código de la empresa

(siempre y cuando alguna de las salidas se active).

Se pide lo siguiente:

• Determinar cuáles son las palabras de código con las que trabaja la empresa.

• Realizar un análisis transitorio para deducir la posibilidad de problemas debido al

estado transitorio del circuito. También, según los retrasos indicados en las hojas de

especificaciones, cuantificar el retraso del camino crítico.

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 18

• Realizar la simulación del circuito para comprobar el análisis estacionario. En el cro-

nograma deberá aparecer la salida de la puerta OR de dos entradas, además de las

señales de entrada y salida. También se deberá obtener la tabla de combinaciones a

partir del cronograma.

• Comprobar mediante emulación el análisis estacionario del circuito.

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 19

Práctica V: Diseño de Circuitos

Combinacionales

Objetivos.

Esta práctica tiene como principal objetivo introducir al alumno en la problématica del

diseño de los circuitos combinacionales.

Problema.

Una empresa de telecomunicaciones dispone de un cricuito del que sólo se conoce su

comportamiento. Este comportamiento es el mostrado por el siguiente cronograma.

F1

F2

F3

Dicha empresa desea obtener un circuito equivalente, que muestre el comportamiento anterior.

El diseño debe tener los siguientes pasos:

• Pasar el cronograma anterior a una tabla de combinaciones.

X Y Z F1 F2 F3

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

• Realizar el diseño de forma teórica, considerando que las dos salidas son indepen-

dientes.

• Realizar el diseño de forma teórica, considerando que las dos salidas pertencen a una

misma función multisalida.

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 20

• Obtener las tablas de combinaciones de los circuitos obtenidos en los dos apartados

anteriores.

Salidas independientes Multisalida

X Y Z F1 F2 F3 F1 F2 F3

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

• Aplicar los cirterios de minimalidad a ambas soluciones, e indicar cuál es la fórmula

mínima.

• Verificar ambas soluciones mediante simulación, comprobando que son representa-

ciones de la misma función. Para ello, pasar de los cronogramas a una tabla de combi-

naciones.

Salidas independientes Multisalida

X Y Z F1 F2 F3 F1 F2 F3

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

• Comprobar mediante emulación el diseño mínimo. Para ello completar la siguiente

tabla de combinaciones.

X Y Z F1 F2 F3

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 21

Práctica VI: Diseño y Análisis de

Circuitos Combinacionales MSI

Objetivos.

Esta práctica tiene como principal objetivo introducir al alumno en la problématica del

diseño y análisis de los circuitos combinacionales, utilizando dispositivos MSI.

Problema.

Una empresa de electrodomésticos desea cambiar la implementación de una función de

control. Esta función tiene la siguiente implementación:

1

F1

X0 0

0

X1 2 1

X2 1 2 X0 1

3 F2

X3 CS 0

Se pide lo siguiente:

• Obtener la función lógica que implementa dicho circuito. Para ello se debe llegar

como mínimo a la tabla de combinaciones.

• Simular el circuito anterior para comprobar el resultado obtenido en el punto anterior.

Para ello, se deberá poner las entradas como un bus (bit_vector, dirigirse al libro de

prácticas para más información) para que pueda servir de entrada a la instrucción de

alto nivel correspondiente.

• Comprobar mediante emulación dicho resultado. Para ello se deberá pasar la tabla de

combinaciones obtenida en el laboratorio a un cronograma.

X3

X2

X1

X0

F1

F2

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 22

• Implementar la función lógica obtenida utilizando únicamente un multiplexor de 1 a 8

e inversores, por cada salida.

• Comprobar mediante simulación el nuevo diseño de la función. Pasar del cronograma

obtenido a una tabla de combinaciones.

• Comprobar mediante emulación el nuevo diseño de la función. Pasar de la tabla obte-

nida a un cronograma equivalente.

X3

X2

X1

X0

F1

F2

• Implementar la función lógica obtenida utilizando únicamente un decodificador de 4 a

16 y puertas nand.

• Comprobar mediante simulación el nuevo diseño de la función. Pasar del cronograma

obtenido a una tabla de combinaciones.

• Comprobar mediante emulación el nuevo diseño de la función. Pasar de la tabla obte-

nida a un cronograma equivalente.

X3

X2

X1

X0

F1

F2

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Curso 2004/2005 23

Práctica VII: Diseño de Circuitos

Combinacionales MSI

Objetivos.

Esta práctica tiene como principal objetivo introducir al alumno en la problématica del

diseño de los circuitos combinacionales, utilizando dispositivos MSI.

Problema.

Una empresa de seguridad necesita implementar un circuito que determine la influencia

conjunta de humo y calor, para un sistema de alarma de incendios. Dicho sistema debe realizar

las siguientes operaciones:

• Sumar los valores de humo y calor

• Cuando dicha suma sea mayor a cuatro unidades, el sistema debe devolver el valor 4.

• Cuando dicha suma sea menor o igual a cuatro unidades, el sistema debe devolver el

valor de la suma.

Para este sistema existen dos sensores: calor (C) y humo (H); con una sensibilidad de dos bits.

La salida debe estar en un display de siete segmentos.

El diseño deberá abordar los siguientes puntos:

• Obtener un diagrama de flujo del comportamiento del sistema de seguridad.

• Pasar de dicho diagrama a una descripción de circuitos lógicos.

• Comprobar mediante emulación el comportamiento especificado. Para ello, completar

el cronograma siguiente.

C 0 0 0 0 1 1 1 1 2 2 2 2 3 3 3 3

H 0 1 2 3 0 1 2 3 0 1 2 3 0 1 2 3

Departamento de Ingeniería Electrónica de Sistemas Informáticos y Automática

Você também pode gostar

- Manual para Ser Profesional Técnico en Mecànica de Producción (2) - 1Documento46 páginasManual para Ser Profesional Técnico en Mecànica de Producción (2) - 1Liam JJAinda não há avaliações

- Motores de Induccion Monofasicos - Manual Del EstudianteDocumento46 páginasMotores de Induccion Monofasicos - Manual Del EstudianteLiam JJAinda não há avaliações

- Logo Temporizador TotalDocumento54 páginasLogo Temporizador TotalLiam JJAinda não há avaliações

- Logo Bit TotalDocumento40 páginasLogo Bit TotalLiam JJAinda não há avaliações

- Leydeldiscapacitado 27050Documento18 páginasLeydeldiscapacitado 27050Jorge García100% (1)

- Tesla Logo Set Reset 2008alumnoDocumento20 páginasTesla Logo Set Reset 2008alumnoLiam JJAinda não há avaliações

- Tabla de Verificacion e Inspeccion Del TornoDocumento20 páginasTabla de Verificacion e Inspeccion Del TornoLiam JJ63% (8)

- 55) Ley 28164 Modifica La Ley 27050Documento5 páginas55) Ley 28164 Modifica La Ley 27050Liam JJAinda não há avaliações

- 54) DS 003-2000-PROMUDEH Reglamento de La Ley 27050Documento20 páginas54) DS 003-2000-PROMUDEH Reglamento de La Ley 27050Liam JJAinda não há avaliações

- Tesla Logo Bit 2008Documento26 páginasTesla Logo Bit 2008Liam JJAinda não há avaliações

- Logo Contador TotalDocumento8 páginasLogo Contador TotalLiam JJAinda não há avaliações

- Logo Set Reset TotalDocumento49 páginasLogo Set Reset TotalLiam JJ100% (3)

- Tesla Logo Marca 2008alumnoDocumento21 páginasTesla Logo Marca 2008alumnoLiam JJAinda não há avaliações

- Tesla Logo Temporizador 2008alumnoDocumento21 páginasTesla Logo Temporizador 2008alumnoLiam JJAinda não há avaliações

- Tesla Logo Temporizador 2008Documento9 páginasTesla Logo Temporizador 2008Liam JJAinda não há avaliações

- Tesla Logo Bit 2008alumnoDocumento21 páginasTesla Logo Bit 2008alumnoLiam JJAinda não há avaliações

- Tesla Logo Set Reset 2008Documento11 páginasTesla Logo Set Reset 2008Liam JJAinda não há avaliações

- Tesla Logo Contador 2008alumnoDocumento22 páginasTesla Logo Contador 2008alumnoLiam JJ100% (2)

- Tesla Logo Marca 2008Documento6 páginasTesla Logo Marca 2008Liam JJ0% (1)

- Tesla Logo Contador 2008Documento10 páginasTesla Logo Contador 2008Liam JJAinda não há avaliações

- Tesla Logo Tarea 4Documento10 páginasTesla Logo Tarea 4Liam JJ0% (1)

- Tesla Logo Bit 2008Documento26 páginasTesla Logo Bit 2008Liam JJAinda não há avaliações

- Tesla Logo Tarea 0Documento13 páginasTesla Logo Tarea 0Liam JJAinda não há avaliações

- Tesla Logo Teoria 2008 - 2Documento28 páginasTesla Logo Teoria 2008 - 2Liam JJ100% (2)

- Tesla Logo Tarea 2Documento8 páginasTesla Logo Tarea 2Liam JJ100% (1)

- Intermedios Nano PLCDocumento61 páginasIntermedios Nano PLCLiam JJAinda não há avaliações

- Tesla Logo Teoria 2008 - 1Documento44 páginasTesla Logo Teoria 2008 - 1Liam JJAinda não há avaliações

- Tesla Logo Tarea 1Documento15 páginasTesla Logo Tarea 1Liam JJ100% (4)

- Tesla Logo ElectroneumaticaDocumento6 páginasTesla Logo ElectroneumaticaLiam JJ100% (1)

- Tesla Logo AplicacionesDocumento31 páginasTesla Logo AplicacionesGiovanni HFAinda não há avaliações

- Análisis de Trabajo Seguro (ATSDocumento2 páginasAnálisis de Trabajo Seguro (ATSMiguel GonzalesAinda não há avaliações

- Guarda y Custodia de Las EMODocumento5 páginasGuarda y Custodia de Las EMOYoni MachadoAinda não há avaliações

- Tarea2AE Nicolalde2Documento21 páginasTarea2AE Nicolalde2Javier Daniel NikolaldeAinda não há avaliações

- Soluciones buffersDocumento13 páginasSoluciones buffersAdrian Bermudez LoeraAinda não há avaliações

- ARTICULOSDocumento12 páginasARTICULOSHenry Omar Espinal VasquezAinda não há avaliações

- Punto LogicoDocumento11 páginasPunto LogicoMichael Palacios FloresAinda não há avaliações

- Reglamento 4-27 Sustancias Quimicas Controladas en VoladurasDocumento46 páginasReglamento 4-27 Sustancias Quimicas Controladas en VoladurasJose Noel Herrera RodriguezAinda não há avaliações

- Informe de SilviaDocumento42 páginasInforme de SilviaAnonymous uflnbN8SAinda não há avaliações

- Práctica de interés simpleDocumento7 páginasPráctica de interés simpleBernardoAinda não há avaliações

- Ejemplo de Planeacion Financiera CafeteriaDocumento27 páginasEjemplo de Planeacion Financiera CafeteriaKatia Peña Munive100% (1)

- Cotizacion 5833Documento1 páginaCotizacion 5833tiare pacaninsAinda não há avaliações

- Reporte de InvestigacionDocumento10 páginasReporte de InvestigacionRocio AguilarAinda não há avaliações

- Acuerdo pedagógico de Microeconomía en Gestión EmpresarialDocumento3 páginasAcuerdo pedagógico de Microeconomía en Gestión EmpresarialSofia CUBIDES VILLABONAAinda não há avaliações

- Ciencias Sociales - 6to - Actividades - Sec 2Documento31 páginasCiencias Sociales - 6to - Actividades - Sec 2Luciana CastronuovoAinda não há avaliações

- Trabajo Miel de Abeja peru-EE - UUDocumento15 páginasTrabajo Miel de Abeja peru-EE - UUcriztian lopezAinda não há avaliações

- 100 MontaditosDocumento3 páginas100 MontaditosjosemanuelAinda não há avaliações

- PROYECTO PENSAMIENTO ESTRATEGICO Y PROSPECTIVA - Entrega 2Documento42 páginasPROYECTO PENSAMIENTO ESTRATEGICO Y PROSPECTIVA - Entrega 2Astrid Escobar100% (8)

- PR. Modifica Res. 3753 de 2015 PRORROGA Reglamento Tecnico Vehiculos de PasajerosDocumento6 páginasPR. Modifica Res. 3753 de 2015 PRORROGA Reglamento Tecnico Vehiculos de PasajerosEduardo FlorezAinda não há avaliações

- Investigacion FormativaDocumento3 páginasInvestigacion FormativaJosep ChinchayAinda não há avaliações

- Semanario Todo Minería 06.03.2022Documento13 páginasSemanario Todo Minería 06.03.2022Abraham A. Monteza PeraltaAinda não há avaliações

- RetoDocumento3 páginasRetoCharly CalderónAinda não há avaliações

- Baran A Cister VolvoDocumento3 páginasBaran A Cister VolvoKevin Franco Quilla GutiérrezAinda não há avaliações

- Mapa ConceptualDocumento1 páginaMapa ConceptualLorena GalatiAinda não há avaliações

- Principio de Legalidad PresupuestarioDocumento24 páginasPrincipio de Legalidad PresupuestarioBryan SalazarAinda não há avaliações

- Economía en Un DíaDocumento17 páginasEconomía en Un DíaLaura Daniela MartinezAinda não há avaliações

- Laboratorio #1 Determinación de Densidad en Sólidos y LíquidosDocumento4 páginasLaboratorio #1 Determinación de Densidad en Sólidos y LíquidosErick TejadaAinda não há avaliações

- Cotizacion Navi-Toyota Agua y DesgaueDocumento3 páginasCotizacion Navi-Toyota Agua y DesgaueAngel LopezAinda não há avaliações

- Vicens Vives-La Sociedad BarrocaDocumento4 páginasVicens Vives-La Sociedad BarrocaAlan RickertAinda não há avaliações

- PC1 Estructuras determinar fuerzas cables candelabro vigasDocumento2 páginasPC1 Estructuras determinar fuerzas cables candelabro vigasJorge Valverde OlivaAinda não há avaliações

- Manual k6Documento6 páginasManual k6aquaicejuanAinda não há avaliações