Escolar Documentos

Profissional Documentos

Cultura Documentos

Apr 2006

Enviado por

Hafidz AnuwarDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Apr 2006

Enviado por

Hafidz AnuwarDireitos autorais:

Formatos disponíveis

CONFIDENTIAL CS/APR 2006/ITT270

UNIVERSITI TEKNOLOGI MARA

FINAL EXAMINATION

COURSE DIGITAL ELECTRONICS

COURSE CODE ITT270

EXAMINATION APRIL 2006

TIME 3 HOURS

INSTRUCTIONS TO CANDIDATES

1. This question paper consists of two (2) parts: PART A (6 Questions)

PART B (4 Questions)

2. Answer ALL questions from all two (2) parts the Answer Booklet. Start each answer on a

new page.

3. Do not bring any material into the examination room unless permission is given by the

invigilator.

4. Please check to make sure that this examination pack consists of:

i) the Question Paper

ii) an Answer Booklet - provided by the Faculty

DO NOT TURN THIS PAGE UNTIL YOU ARE TOLD TO DO SO

This examination paper consists of 9 printed pages

© Hak Cipta Universiti Teknologi MARA CONFIDENTIAL

CONFIDENTIAL 2 CS/APR 2006/ITT270

PART A (44 marks)

QUESTION 1

Convert the following numbers to hexadecimal:

a) Binary 1000100110.

(2 marks)

b) BCD 1000100110.

(2 marks)

c) Octal 226.

(2 marks)

d) Decimal 226.

(2 marks)

QUESTION 2

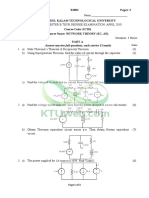

Given the logic circuit as shown below:

A

B

C

D

a) Write the expression for the output Y.

(2 marks)

b) Draw the circuit using AND and OR gates.

(2 marks)

© Hak Cipta Universiti Teknologi MARA CONFIDENTIAL

CONFIDENTIAL 3 CS/APR 2006/ITT270

QUESTION 3

Given the following Boolean expression:

Y = A.B + A.B + B.C

a) Simplify the expression.

(3 marks)

b) Derive the truth table.

(3 marks)

c) Draw the simplified expression using NAND gate.

(3 marks)

d) Draw the simplified expression using a 3:8 decoder and OR gate.

(3 marks)

QUESTION 4

Answer the following questions:

a) Proof the Boolean expression using Boolean algebra.

A.B + A.B + A.B.C = (B + A)(B + C)

(3 marks)

b) Proof the Boolean expression using Boolean algebra and DeMorgen's theorem.

A.B + A.B + B.C = B.C

(3 marks)

© Hak Cipta Universiti Teknologi MARA CONFIDENTIAL

CONFIDENTIAL 4 CS/APR 2006/ITT270

QUESTION 5

Answer the following questions:

a) Convert the two's complement number 1000100110p2 to a hexadecimal number.

(2 marks)

b) Subtract 1710- 5i0 using 8 bit two's complement number system.

(2 marks)

c) Derive the following full adder expressions.

S = A©B0Cin

Co = AB + BCin + ACin

(4 marks)

QUESTION 6

Given a 4K x 16 bit memory chip:

a) Determine the number of address lines.

(1 mark)

b) Draw the memory diagram.

(2 marks)

c) How many memory chips are needed to expand the capacity to 16K x 16 bit?

(1 mark)

d) Draw the memory diagram in (c).

(2 marks)

© Hak Cipta Universiti Teknologi MARA CONFIDENTIAL

CONFIDENTIAL CS/APR 2006/ITT270

PART B (56 marks)

QUESTION 1

The diagram shown below is an irrigation system for a paddy field. There are 6 valves to

direct water from the canal on to the field. A water level sensor will generate a water level

scale between 000 to 101. The following table shows the valves that will be activated based

on the water level scale.

Water Output of Output of logic circuit

Level Sensor

0 000 Activate all valves

1 001 Activate valve 1,2,3,4 and 5 only

2 010 Activate valve 1 , 2, 3 and 4 only

3 011 Activate valve 1 , 2 and 3 only

4 100 Activate valve 1 only

5 101 No valve are activated

Rain

irrigation canal

water

valve

5 ^\ I water flow

a 4 ^

(r n w

(j 2 L- _f

^ Water

Level

-fc Sensor — >

> Logic * 3 .

a 1r —*

rr 0

IE Generate _ w. ClfCUlt

*~ 000-101 ^ *5c , ^

N

(r —————— ' S~ ^< '

< J" 4J" 43=- 4J^ %1

—— \

Rain Water Collector V V Y Y T T

Y Y Y Y Y Y

V Y Y Y Y Y

Paddy Field

Design the logic circuit. Your solution must include:

a) Truth table.

(4 marks)

b) Simplified expression.

(6 marks)

c) Logic circuit.

(3 marks)

© Hak Cipta Universiti Teknologi MARA

CONFIDENTIAL

CONFIDENTIAL CS/APR 2006/ITT270

QUESTION 2

Design a synchronous counter using JK flip-flop to produce the following sequence:

7 -> 5-* 3— > 6-> 4 0 —|

Your solution must include:

a) Excitation table.

(6 marks)

b) Karnaugh map for J and K.

(6 marks)

c) Counter circuit.

(3 marks)

© Hak Cipta Universiti Teknologi MARA CONFIDENTIAL

CONFIDENTIAL 7 CS/APR 2006/ITT270

QUESTION 3

Determine the counting sequence for the following counter circuit.

fl c

}

Ei

V \

_E J

— o CP

K

4s

C

C O-

— > J

__ 0 CP

K

4

s

Q

Q 0—

^ J

r—O CP

K

4

S

Q

C

"

ni — •v

R R

5V R

V 7 V V

CPl Ql

-0 CP2 Q2 0-

Your solution must include:

a) Expressions for J and K.

(3 marks)

b) Excitation table.

(6 marks)

c) State diagram.

(4 marks)

© Hak Cipta Universiti Teknologi MARA CONFIDENTIAL

CONFIDENTIAL 8 CS/APR 2006/ITT270

QUESTION 4

The block diagram shown below is a simple Add/Subtract calculator.

Answer the following questions:

a) Derive the 10:4 encoder truth table and draw the circuit.

MSB

A

B

C

LSB

D

(5 marks)

© Hak Cipta Universiti Teknologi MARA CONFIDENTIAL

CONFIDENTIAL CS/APR 2006/ITT270

b) Derive the BCD to Seven Segment decoder truth table.

(5 marks)

c) Draw the calculator circuit.

(5 marks)

END OF QUESTION PAPER

© Hak Cipta Universiti Teknologi MARA

CONFIDENTIAL

Você também pode gostar

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNo EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesAinda não há avaliações

- S T L DDocumento12 páginasS T L DMohan Krishna0% (1)

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsNo EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsNota: 5 de 5 estrelas5/5 (1)

- IC Design and Applications Exam GuideDocumento2 páginasIC Design and Applications Exam GuidevijaykumarAinda não há avaliações

- Mid Term Sem 2 2014 - 2015Documento10 páginasMid Term Sem 2 2014 - 2015FARAZ ABDUL BASITAinda não há avaliações

- Ece361 - Ee 2010 S1Documento5 páginasEce361 - Ee 2010 S1Mu'izz KaharAinda não há avaliações

- r05220403 Switching Theory and Logic DesignDocumento8 páginasr05220403 Switching Theory and Logic DesignSRINIVASA RAO GANTAAinda não há avaliações

- Asn 3 EepDocumento1 páginaAsn 3 EepKudakwashe ChareraAinda não há avaliações

- Basic Electronics June 2012 NewDocumento4 páginasBasic Electronics June 2012 NewPrasad C MAinda não há avaliações

- I C Systems (ECE-2202) RCS (Makeup)Documento2 páginasI C Systems (ECE-2202) RCS (Makeup)1x1pAinda não há avaliações

- L-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Documento19 páginasL-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Sanjid ElahiAinda não há avaliações

- Tutorial 4 Combinational Logic Circuit Design and K-Map: C C C C D C D C D C CDDocumento2 páginasTutorial 4 Combinational Logic Circuit Design and K-Map: C C C C D C D C D C CDMustafidzul MustaphaAinda não há avaliações

- PLC and Industrial Networking PDFDocumento12 páginasPLC and Industrial Networking PDFSuzaini SupingatAinda não há avaliações

- 07af303 - Digital Integrated Circuits and Logical DesignDocumento3 páginas07af303 - Digital Integrated Circuits and Logical DesignChandru RamaswamyAinda não há avaliações

- EE202QDocumento7 páginasEE202QBelon Kaler Biyru IIAinda não há avaliações

- DLDDocumento8 páginasDLDandhracollegesAinda não há avaliações

- Digital System Component & Design DecDocumento5 páginasDigital System Component & Design DecNdiawo MusicianAinda não há avaliações

- NR-221103 - Digital Circuits Design and ApplictionDocumento5 páginasNR-221103 - Digital Circuits Design and ApplictionSrinivasa Rao G100% (1)

- Switching Theory and Logic DesignDocumento10 páginasSwitching Theory and Logic DesignRajkumarBattuAinda não há avaliações

- APJ Abdul Kalam Technological University third semester examDocumento3 páginasAPJ Abdul Kalam Technological University third semester examanuAinda não há avaliações

- Dcit 203 21Documento3 páginasDcit 203 21BrightAinda não há avaliações

- Philadelphia University Final Exam Logic CircuitsDocumento7 páginasPhiladelphia University Final Exam Logic Circuitsnada abdelrahmanAinda não há avaliações

- Basic Electronics November 2018 1920 103Documento5 páginasBasic Electronics November 2018 1920 103James MukhwanaAinda não há avaliações

- Ect203 Scheme 2020Documento8 páginasEct203 Scheme 2020ShakiraAinda não há avaliações

- Ect203 Scheme 2021Documento9 páginasEct203 Scheme 2021ShakiraAinda não há avaliações

- 2017S FE AM QuestionDocumento28 páginas2017S FE AM Questionfqnguyen8Ainda não há avaliações

- 08AB303 DIGITAL LOGIC CIRCUITSDocumento4 páginas08AB303 DIGITAL LOGIC CIRCUITSChandru RamaswamyAinda não há avaliações

- Guessing Papers 1-2-12th Electronics Sub Code C2Documento6 páginasGuessing Papers 1-2-12th Electronics Sub Code C2snigdhagulhane0922Ainda não há avaliações

- BKF2332 - Final Exam 20182019 Sem II (Set A)Documento5 páginasBKF2332 - Final Exam 20182019 Sem II (Set A)Abo AbdoAinda não há avaliações

- Logic Design Jan 2010 ESDocumento2 páginasLogic Design Jan 2010 ESPrasad C MAinda não há avaliações

- COMSATS Institute of Information Technology, Islamabad: Terminal Examination Fall2014Documento8 páginasCOMSATS Institute of Information Technology, Islamabad: Terminal Examination Fall2014Aalian KahoutAinda não há avaliações

- Digital TEST 28.06.23Documento2 páginasDigital TEST 28.06.23SUDHEER SAinda não há avaliações

- Phy340 4Documento7 páginasPhy340 4maggieAinda não há avaliações

- UOM Electrical Engineering ExamDocumento7 páginasUOM Electrical Engineering ExamchetsAinda não há avaliações

- 08AB303 DIGITAL LOGIC CIRCUITS_1Documento3 páginas08AB303 DIGITAL LOGIC CIRCUITS_1Chandru RamaswamyAinda não há avaliações

- Digital Electronics exam questionsDocumento8 páginasDigital Electronics exam questionsJc R. Poorana ChandranAinda não há avaliações

- BCA T 113 Digital Electronics Question BankDocumento9 páginasBCA T 113 Digital Electronics Question BankAhana MalhotraAinda não há avaliações

- Model Question Paper with Verilog HDLDocumento3 páginasModel Question Paper with Verilog HDLsha istaAinda não há avaliações

- ITC227 Signals and Systems Exam QuestionsDocumento5 páginasITC227 Signals and Systems Exam QuestionsMagical MKAinda não há avaliações

- APR2013P21Documento63 páginasAPR2013P21qsashutoshAinda não há avaliações

- Digital Electronic CircuitsDocumento2 páginasDigital Electronic Circuitsmohitg04Ainda não há avaliações

- Basic Electronics July 2019Documento4 páginasBasic Electronics July 2019James MukhwanaAinda não há avaliações

- 131911-3130704 - DF Nov-2019Documento1 página131911-3130704 - DF Nov-2019APOLLO Sem 4 I.T.Ainda não há avaliações

- Q 6Documento3 páginasQ 6Saranya MohanAinda não há avaliações

- de PDFDocumento2 páginasde PDFUnknown userAinda não há avaliações

- EEE 2202 ANALOGUE ELECTRONICS I - July17 - ExamDocumento5 páginasEEE 2202 ANALOGUE ELECTRONICS I - July17 - Exameric wahomeAinda não há avaliações

- DISTANCE EDUCATION BCA DEGREE EXAMINATION QUESTIONSDocumento2 páginasDISTANCE EDUCATION BCA DEGREE EXAMINATION QUESTIONSSakthiAinda não há avaliações

- CSC508 TEST2 16jan2023Documento4 páginasCSC508 TEST2 16jan2023Afiq IzzuddinAinda não há avaliações

- 08AB303 - DIGITAL LOGIC CIRCUITSDocumento3 páginas08AB303 - DIGITAL LOGIC CIRCUITSChandru RamaswamyAinda não há avaliações

- Digital Switching Systems Question PaperDocumento1 páginaDigital Switching Systems Question PaperLavanya R GowdaAinda não há avaliações

- Hours /-: ThirdDocumento3 páginasHours /-: ThirdAhmad UmarAinda não há avaliações

- 2018 Dec. EC202-D - Ktu QbankDocumento4 páginas2018 Dec. EC202-D - Ktu QbankSalim ShahulAinda não há avaliações

- Logic Circuit ExamsDocumento2 páginasLogic Circuit Examsclinton koechAinda não há avaliações

- Pulse and Digital Circuits NotesDocumento8 páginasPulse and Digital Circuits NotesLavanya_123Ainda não há avaliações

- HND 1 Electrical Measurement and Control EEI 311 2016Documento2 páginasHND 1 Electrical Measurement and Control EEI 311 2016iskeel75% (4)

- EDAIC Question Paper - 10th December, 2021Documento4 páginasEDAIC Question Paper - 10th December, 2021Tota OtaharadaAinda não há avaliações

- See Adld 2020Documento2 páginasSee Adld 20201ms21ec132Ainda não há avaliações

- December 2011: Amiete - Et (Old Scheme)Documento4 páginasDecember 2011: Amiete - Et (Old Scheme)Anurag RanaAinda não há avaliações

- THIAGARAJAR COLLEGE BASIC ELECTRONICS EXAMDocumento1 páginaTHIAGARAJAR COLLEGE BASIC ELECTRONICS EXAMloganathanAinda não há avaliações

- 01-EE001-3-2-AE-FE-QPDocumento5 páginas01-EE001-3-2-AE-FE-QPMohamed AltijaniAinda não há avaliações

- Glossary of Philosophical TermsDocumento34 páginasGlossary of Philosophical TermsPleasant KarlAinda não há avaliações

- Course 003: Basic Econometrics: Rohini Somanathan-Part 1 Sunil Kanwar - Part IIDocumento31 páginasCourse 003: Basic Econometrics: Rohini Somanathan-Part 1 Sunil Kanwar - Part IIz_k_j_vAinda não há avaliações

- Only AIDocumento6 páginasOnly AIThiyaga RajanAinda não há avaliações

- Summative Test 8 (3Q Review)Documento6 páginasSummative Test 8 (3Q Review)Elle Ma Rie100% (1)

- The Mathematics of Sentence StructureDocumento27 páginasThe Mathematics of Sentence StructureSergio Nishimura VallartaAinda não há avaliações

- Argumentative and Discursive EssayDocumento3 páginasArgumentative and Discursive Essaypumpkinroar100% (1)

- Soundness and Completeness For Sentence Derivations: LogicDocumento11 páginasSoundness and Completeness For Sentence Derivations: Logicxan30tosAinda não há avaliações

- CH 1 EthicsDocumento23 páginasCH 1 EthicsYash HoraAinda não há avaliações

- Solution ManualDocumento14 páginasSolution ManualdattadhanweAinda não há avaliações

- Electronics - Grade 10Documento7 páginasElectronics - Grade 10Roselyn TrixieAinda não há avaliações

- Arlyn Ragudos Bsa1 MathDocumento3 páginasArlyn Ragudos Bsa1 MathArlyn Ragudos BSA1Ainda não há avaliações

- Fuzzy QuantifiersDocumento18 páginasFuzzy Quantifierskrishnareddy_chintalaAinda não há avaliações

- Categorica L Syllogisms: Standard Form, Mood, and FigureDocumento51 páginasCategorica L Syllogisms: Standard Form, Mood, and FigureSalman RazaAinda não há avaliações

- Rule 6. From Two Universal Premises No Particular Conclusion May Be DrawnDocumento1 páginaRule 6. From Two Universal Premises No Particular Conclusion May Be DrawnLRBAinda não há avaliações

- Bslogic ReviewerDocumento6 páginasBslogic Reviewer4- Desiree FuaAinda não há avaliações

- Aristotle's Philosophy in 40 CharactersDocumento23 páginasAristotle's Philosophy in 40 CharactersTheHegelAinda não há avaliações

- Finding Wisdom Through ReflectionDocumento26 páginasFinding Wisdom Through ReflectionAndrea Yvonne JomadiaoAinda não há avaliações

- Equivalence in Translation Studies: A Critical EvaluationDocumento5 páginasEquivalence in Translation Studies: A Critical EvaluationXhéhzÂda saleem zehriAinda não há avaliações

- Logic 2: Modal Logics Course Guide (2020/2021)Documento3 páginasLogic 2: Modal Logics Course Guide (2020/2021)Marcos del RíoAinda não há avaliações

- Weak Slot and Filler - RichDocumento33 páginasWeak Slot and Filler - RichsriAinda não há avaliações

- Criticisms of The CogitoDocumento8 páginasCriticisms of The Cogitomaria_meAinda não há avaliações

- ConceptDocumento2 páginasConceptJonalet DelimaAinda não há avaliações

- IPTSTS 069 - Belo - Chance and Determinism in Avicenna and Averroes (2007) PDFDocumento265 páginasIPTSTS 069 - Belo - Chance and Determinism in Avicenna and Averroes (2007) PDFRes Arabica StudiosusAinda não há avaliações

- Emotivism & ExpressivismDocumento2 páginasEmotivism & ExpressivismEdward HadleyAinda não há avaliações

- Gava 44.4 Kant and PeirceDocumento30 páginasGava 44.4 Kant and PeirceDasNomoAinda não há avaliações

- Alfaisal University Digital Logic Systems AssignmentDocumento4 páginasAlfaisal University Digital Logic Systems Assignmentsarah alshAinda não há avaliações

- Three Laws of Thought ExplainedDocumento2 páginasThree Laws of Thought ExplainedAlexis John Solomon CastroAinda não há avaliações

- The Enigma of Reason by Hugo Mercier Dan Sperber-1 PDFDocumento370 páginasThe Enigma of Reason by Hugo Mercier Dan Sperber-1 PDFDouglas100% (1)

- Assignment #1 2023 SolutionDocumento7 páginasAssignment #1 2023 Solutiongavindennis97Ainda não há avaliações

- Medical English Dialogues: Clear & Simple Medical English Vocabulary for ESL/EFL LearnersNo EverandMedical English Dialogues: Clear & Simple Medical English Vocabulary for ESL/EFL LearnersAinda não há avaliações

- AP World History: Modern Premium, 2024: Comprehensive Review with 5 Practice Tests + an Online Timed Test OptionNo EverandAP World History: Modern Premium, 2024: Comprehensive Review with 5 Practice Tests + an Online Timed Test OptionNota: 5 de 5 estrelas5/5 (1)

- LSAT For Dummies (with Free Online Practice Tests)No EverandLSAT For Dummies (with Free Online Practice Tests)Nota: 4 de 5 estrelas4/5 (1)

- MCAT Biology & Biochemistry Practice Questions: High Yield MCAT QuestionsNo EverandMCAT Biology & Biochemistry Practice Questions: High Yield MCAT QuestionsAinda não há avaliações

- AP Computer Science A Premium, 2024: 6 Practice Tests + Comprehensive Review + Online PracticeNo EverandAP Computer Science A Premium, 2024: 6 Practice Tests + Comprehensive Review + Online PracticeAinda não há avaliações

- AP Calculus Premium, 2024: 12 Practice Tests + Comprehensive Review + Online PracticeNo EverandAP Calculus Premium, 2024: 12 Practice Tests + Comprehensive Review + Online PracticeAinda não há avaliações

- GMAT Prep 2024/2025 For Dummies with Online Practice (GMAT Focus Edition)No EverandGMAT Prep 2024/2025 For Dummies with Online Practice (GMAT Focus Edition)Ainda não há avaliações

- AP English Language and Composition Premium, 2024: 8 Practice Tests + Comprehensive Review + Online PracticeNo EverandAP English Language and Composition Premium, 2024: 8 Practice Tests + Comprehensive Review + Online PracticeAinda não há avaliações

- Digital SAT Prep 2024 For Dummies: Book + 4 Practice Tests Online, Updated for the NEW Digital FormatNo EverandDigital SAT Prep 2024 For Dummies: Book + 4 Practice Tests Online, Updated for the NEW Digital FormatAinda não há avaliações

- GMAT Foundations of Verbal: Practice Problems in Book and OnlineNo EverandGMAT Foundations of Verbal: Practice Problems in Book and OnlineAinda não há avaliações

- Digital SAT Reading and Writing Practice Questions: Test Prep SeriesNo EverandDigital SAT Reading and Writing Practice Questions: Test Prep SeriesNota: 5 de 5 estrelas5/5 (2)

- Digital SAT Preview: What to Expect + Tips and StrategiesNo EverandDigital SAT Preview: What to Expect + Tips and StrategiesNota: 5 de 5 estrelas5/5 (3)

- The LearnCurious Companion to the Digital SAT: VerbalNo EverandThe LearnCurious Companion to the Digital SAT: VerbalAinda não há avaliações

- Finish What You Start: The Art of Following Through, Taking Action, Executing, & Self-DisciplineNo EverandFinish What You Start: The Art of Following Through, Taking Action, Executing, & Self-DisciplineNota: 4.5 de 5 estrelas4.5/5 (94)

- The LSAT Law School Admission Test Study Guide Volume I - Reading Comprehension, Logical Reasoning, Writing Sample, and Analytical Reasoning Review Proven Methods for Passing the LSAT Exam With ConfidenceNo EverandThe LSAT Law School Admission Test Study Guide Volume I - Reading Comprehension, Logical Reasoning, Writing Sample, and Analytical Reasoning Review Proven Methods for Passing the LSAT Exam With ConfidenceAinda não há avaliações

- IELTS Academic Vocabulary Builder: Improve Your Band Score on the IELTS Academic ExamNo EverandIELTS Academic Vocabulary Builder: Improve Your Band Score on the IELTS Academic ExamAinda não há avaliações

- The Premed Playbook: Guide to the Medical School Personal StatementNo EverandThe Premed Playbook: Guide to the Medical School Personal StatementNota: 5 de 5 estrelas5/5 (1)

- The Ultimate UCAT Collection: 3 Books In One, 2,650 Practice Questions, Fully Worked Solutions, Includes 6 Mock Papers, 2019 Edition, UniAdmissions Aptitude Test, UniAdmissionsNo EverandThe Ultimate UCAT Collection: 3 Books In One, 2,650 Practice Questions, Fully Worked Solutions, Includes 6 Mock Papers, 2019 Edition, UniAdmissions Aptitude Test, UniAdmissionsNota: 4 de 5 estrelas4/5 (1)

- The LSAT Trainer Ultimate Study Guide: Simplified 3 Real LSAT PrepTests + Strategies to Ace the Exam The Complete Exam Prep with Practice Tests and Insider Tips & Tricks | Achieve a 98% Pass Rate on Your First Attempt!No EverandThe LSAT Trainer Ultimate Study Guide: Simplified 3 Real LSAT PrepTests + Strategies to Ace the Exam The Complete Exam Prep with Practice Tests and Insider Tips & Tricks | Achieve a 98% Pass Rate on Your First Attempt!Ainda não há avaliações

- GMAT Foundations of Math: Start Your GMAT Prep with Online Starter Kit and 900+ Practice ProblemsNo EverandGMAT Foundations of Math: Start Your GMAT Prep with Online Starter Kit and 900+ Practice ProblemsNota: 4 de 5 estrelas4/5 (7)

- AP Q&A Psychology, Second Edition: 600 Questions and AnswersNo EverandAP Q&A Psychology, Second Edition: 600 Questions and AnswersAinda não há avaliações

- AP Microeconomics/Macroeconomics Premium, 2024: 4 Practice Tests + Comprehensive Review + Online PracticeNo EverandAP Microeconomics/Macroeconomics Premium, 2024: 4 Practice Tests + Comprehensive Review + Online PracticeAinda não há avaliações

- Digital SAT Math Prep For Dummies, 3rd Edition: Book + 4 Practice Tests Online, Updated for the NEW Digital FormatNo EverandDigital SAT Math Prep For Dummies, 3rd Edition: Book + 4 Practice Tests Online, Updated for the NEW Digital FormatAinda não há avaliações

- Digital PSAT/NMSQT Study Guide Premium, 2024: 4 Practice Tests + Comprehensive Review + Online PracticeNo EverandDigital PSAT/NMSQT Study Guide Premium, 2024: 4 Practice Tests + Comprehensive Review + Online PracticeAinda não há avaliações