Escolar Documentos

Profissional Documentos

Cultura Documentos

Trabalho 3

Enviado por

Cassimo IsmaelTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Trabalho 3

Enviado por

Cassimo IsmaelDireitos autorais:

Formatos disponíveis

INSTITUTO SUPERIOR POLITÉCNICO DE SONGO

CURSO DE ENGENHARIA ELÉCTRICA

ELECTRÓNICA DIGITAL

SEMESTRE VII

TEMPORIZADOR 555

Discentes: Docente:

Esperança da F. André Nhar Engo. Igídio Mutemba

Songo, Agosto de 2019

INSTITUTO SUPERIOR POLITÉCNICO DE SONGO

CURSO DE ENGENHARIA ELÉCTRICA

ELECTRÓNICA DIGITAL

SEMESTRE VII

TEMPORIZADOR 555

Discente: Docente:

Esperança da F. André Nhar Engo. Igídio Mutemba

O presente trabalho foi elaborado

por estudante do Instituto Superior

Politécnico de Songo, do terceiro

ano do curso de Engenharia

Eléctrica, no âmbito da cadeira de

Electrónica Digital, para fins de

avaliação.

para fins de avaliação

Songo, Agosto de 2019

Índice

1. Introdução ............................................................................................................................................. 1

1.1. Objectivos ..................................................................................................................................... 2

1.1.1. Objectivo Geral ..................................................................................................................... 2

1.1.2. Objectivos Específicos ........................................................................................................... 2

1.2. Metodologia de pesquisa............................................................................................................... 2

2. Temorizador 555 ................................................................................................................................... 3

2.1. Características eléctricas do temporizador 555 ............................................................................. 7

2.2. Modos de operação do temporizador 555 ..................................................................................... 7

2.2.1. Operação Monoestável ......................................................................................................... 7

2.2.2. Operação Astável .................................................................................................................. 9

2.3. Aplicações do temporizador 555................................................................................................. 10

2.4. Vantagens do temporizador 555 ................................................................................................. 10

3. Conclusão............................................................................................................................................ 11

4. Bibliografia ............................................................................................................................................. 12

1. Introdução

Actualmente, pode-se encontrar no mercado circuitos integrados especialmente projectados para

implementar circuitos multivibradores em várias faixas de frequências. Um dos primeiros

circuitos integrados disponíveis é o temporizador 555.

Temporizador 555 é um circuito projectado para aplicações gerais de temporização. Dependendo

da sua forma de configuração podem gerar pulsos assim como gerar oscilações com frequências

reguláveis.

O presente trabalho propõe uma abordagem sobre Temporizador 555. Em primeiro lugar

apresentar-se-á o conceito e o diagrama funcional interno do dispositivo em estudo, explicando

sucintamente cada bloco que o compõe. E posteriormente apresentar as suas configurações

(monoestáveis e astáveis) e o respectivo funcionamento para as devidas aplicações.

Temporizador 555 – Trabalho III Página 1

1.1. Objectivos

1.1.1. Objectivo Geral

Fazer uma abordagem de forma coerente do temporizador 555.

1.1.2. Objectivos Específicos

Definir temporizador 555

Mostrar o diagrama funcional interno de um temporizador 555;

Apresentar o modo de operação do temporizador 555;

1.2. Metodologia de pesquisa

A elaboração do presente trabalho foi baseada em pesquisas científico-didácticas com base em

manuais, artigos electrónicos. As fontes foram todas devidamente referidas na bibliografia.

Temporizador 555 – Trabalho III Página 2

2. Temorizador 555

Temorizador 555 é um dispositivo, na forma de circuito integrado, versátil e amplamente usado

pois pode ser configurado em dois modos diferentes: multivibrador monoestável ou um

multivibrador astável (oscilador).

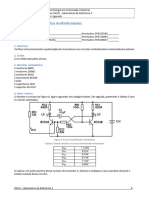

Um temporizador 555 é constituído basicamente por dois comparadores, um Flip-Flop do tipo

RS, um transístor de descarga e um divisor de tensão, como mostra la figura 1(a). A figura 1(b)

mostra um CI temporizador 555, e posteriormente a discrição e as funções de cada um dos pinos

do dispositivo.

(a) (b)

Figura 1: (a)Diagrama funcional interno de um temporizador 555, (b) Pinos do temporizador

555

Fonte :Valdir 2012

1 – GND - Deve ser ligado ao negativo da fonte de alimentação ou de uma bateria, também

conhecido como terra ou massa.

2 – Disparador/Trigger – É o gatilho usado para disparar o funcionamento do circuito.

3 – Saída /Output– É a saída dos pulsos gerados pelo circuito integrado e seu nível depende de

resistores e do capacitor ligados externamente ao C.I.

Temporizador 555 – Trabalho III Página 3

4 – Reactivador/Reset – Inibe o funcionamento do circuito. Quando colocado em nível baixo

(no GND), ele reinicia o funcionamento e mantém tudo parado até que seja colocado em nível

alto. Em funcionamento normal ele é mantido ao Vcc.

5 – Modulador – Também chamado de Controlo de tensão, é capaz de modular o sinal de

saída, onde o sinal gerado pela oscilação do 555 será a portadora e os sinais aplicados a este pino

realizará a modulação desse sinal.

6 – Limiar/Threshold – Quando este terminal recebe um sinal maior que 2/3 da tensão de

alimentação ele faz a saída (pino 3) ir ao nível baixo (zero volts).

7 – Descarga – Descarrega o capacitor externo para que se possa iniciar um novo ciclo de

trabalho.

8 – Vcc – Deve ser ligado ao positivo da fonte de alimentação ou de uma bateria.

Observando a figura 1(a), o temporizador 555 é constituído basicamente por quatro (4) blocos:

Dois Amplificadores operacionais funcionando como Comparadores de Tensão;

Um Divisor de Tensão formado por três Resistores de 5 K Ω;

Um Flip-Flop tipo RS;

Um transístor utilizado como Chave.

a) Comparadores de Tensão

O funcionamento dos Comparadores de tensão neste circuito é o seguinte:

Observando a figura, podemos ver que o componente possui duas entradas (Inversora ‘-’ e Não

Inversora ‘+’) e uma saída. O nível de tensão na saída poderá ser alto (1) ou baixo (0),

dependendo do nível de tensão nas entradas.

A saída será alta ( 1 ou +𝑉𝑐𝑐 ) sempre que a tensão na entrada não Inversora ‘ + ’ for mais alta do

que a tensão na entrada Inversora ‘ – ’

Temporizador 555 – Trabalho III Página 4

Figura 2: Comparador de tensão

Fonte: Valdir 2012

b) Divisor de Tensão

É formado por três resistores de5𝑘Ω. Sua função é fornecer as tensões de referência para os

comparadores de tensão. Sobre cada um dos resistores será aplicada uma tensão igual a um terço

da tensão de alimentação 𝑉𝑐𝑐 .

Sendo assim, entre o terminal do terra e o primeiro resistor (ponto A) teremos uma tensão igual a

𝑉𝑐𝑐

um terço de 𝑉𝑐𝑐 ( ) aplicada à entrada Não Inversora do primeiro comparador (Disparador).

3

Entre o terminal do terra e o segundo resistor (ponto B) teremos uma tensão igual a dois terços

𝑉𝑐𝑐

da tensão de alimentação (2 ∙ ) que é aplicada ao segundo comparador (Controle).

3

Figura 3: Divisor de Tensão

Fonte: Valdir 2012

Temporizador 555 – Trabalho III Página 5

c) Flip-Flop tipo RS

Trata-se de um componente Digital biestável, ou seja, suas saídas podem assumir apenas dois

níveis de tensão ou níveis lógicos (zero ou um). As saídas são complementares. Enquanto

𝑄 estiver em nível lógico zero, a saída complementar 𝑄 estará em nível lógico um e vice-versa.

Quando a entrada 𝑆 (𝑆𝑒𝑡) receber um nível lógico igual a um, a saída 𝑄 será levada para nível

lógico um, ou seja, a operação 𝑆𝑒𝑡 leva a saída 𝑄 para o nível de tensão igual a 𝑉𝑐𝑐. Quando a

entrada 𝑅 (𝑅𝑒𝑠𝑒𝑡) receber um nível lógico igual a um, a saída 𝑄 será levada para nível lógico

zero, ou seja, a operação 𝑅𝑒𝑠𝑒𝑡 leva a saída 𝑄 para o nível de tensão igual zero volts.

Figura 4: Flip-Flop tipo RS

Fonte: Valdir 2012

d) Transístor como Chave

Quando a saída Q estiver em nível lógico um, fará com que a corrente de base leve o transístor à

saturação, ou seja, a chave entre colector e emissor será fechada, aterrando o terminal de colector

do transístor.

Este transístor é utilizado para descarregar capacitores externos utilizados como base de tempo.

Figura 5: Transístor como Chave

Fonte: Valdir 2012

Temporizador 555 – Trabalho III Página 6

2.1. Características eléctricas do temporizador 555

A tensão de alimentação (𝑉𝑐𝑐) varia numa faixa de 4.5𝑉 a 18𝑉

A corrente máxima na saída (𝐼0 𝑚á𝑥 ) em estado ‘ON’ é de200𝑚𝐴;

Potencia dissipação máxima (𝑃𝑐 𝑚á𝑥 ) de 600𝑚𝑊;

Tensão de saída em estado alto (𝑉𝑂𝐻 ): 13.3𝑉(𝑉𝑐𝑐 = 15𝑉, 𝐼0 = 0.1𝐴 )

Tempo de subida e descida na saída (𝑡𝑟 𝑒 𝑡𝑓 ) é de 100𝑛𝑆.

2.2. Modos de operação do temporizador 555

Um temporizador 555 pode operar como um monoestável ou como um oscilador (astável).

2.2.1. Operação Monoestável

No modo de operação monoestável o temporizador 555 funciona como um disparador. A

configuração monoestável é um circuito que possui um estado estável e outro semi-estável.

Para configurar o temporizador 555 como monoestável não-redisparável são usados um resistor e

um capacitor externos como mostra a figura 6. A largura do pulso da saída é determinada pela

constante de tempo de 𝑅 e 𝐶 de acordo com a fórmula:

𝑡 = 1,1𝑅. 𝐶

𝑡 - tempo em segundos [𝑠]

𝑅 - Valor da Resistência externa em Ohms [𝛺]

𝐶 - Valor do Capacitor externo em Farads [𝐹]

O disparo do Monoestável ocorrerá toda vez que o pino 2 do CI for levado a zero volts. A figura

6 mostra o diagrama esquemático desta configuração.

Temporizador 555 – Trabalho III Página 7

Figura 6: configuração monoestável

Fonte: Valdir 2012

Enquanto o circuito não for disparado, a saída Q do Flip-Flop interno em nível lógico um fará

com que o transístor de descarga permaneça saturado, impedindo que o capacitor externo C seja

carregado através do resistor externo R. A saída permanecerá em zero volts.

Quando ocorrer o disparo, a tensão no pino 2 será inferior a um terço da alimentação Vcc,

activando o comparador interno de disparo e provocando a operação de Reset no Flip-Flop

interno.

Nesse momento a saída (Pino 3) será levada a nível lógico um (Vcc) e o transístor de descarga

entrará na região de corte, permitindo que o capacitor C possa ser carregado pelo resistor R. Esta

situação será mantida até que o capacitor atinja uma carga ligeiramente maior do que dois terços

da tensão de alimentação, o que activa o comparador de controlo e provoca a operação de Set no

Flip-Flop interno.

A saída então retorna ao nível lógico zero e o transístor interno satura, descarregando o capacitor

C através do pino 7 do CI. Resumindo, a saída é activada no momento do disparo, permanecendo

assim durante o tempo de carga do capacitor, retornando então ao estado inicial. É importante

observar que o pino 4 deve ser mantido em nível lógico alto (+Vcc) para permitir o

funcionamento do circuito.

Temporizador 555 – Trabalho III Página 8

2.2.2. Operação Astável

Esta configuração é utilizada com muita frequência como gerador de pulsos (Clock) para

circuitos digitais. Diferente do monoestável, este circuito não necessita de disparo, gerando uma

sequência de pulsos rectangulares contínua. Para interromper a sequência de pulsos, basta levar o

pino 4 do CI (Reset) a nível lógico zero (zero volts) .

Seu funcionamento não é muito diferente do Monoestável. Quando o capacitor estiver

descarregado, a tensão no pino 2 será menor do que um terço de Vcc, provocando o reset do

Flip-Flop interno. Isto leva a saída (pino 3) a nível lógico 1 e corta o transístor interno,

permitindo que o capacitor inicie seu ciclo de carga através de R1 e R2. Quando a tensão no

capacitor ultrapassar dois terços de Vcc, o comparador de controle efectua a operação de Set no

Flip-Flop interno, levando a saída a zero e saturando o transístor interno, fazendo com que o

capacitor inicie seu ciclo de descarga através de R2 pelo pino 7 do CI . o capacitor terá sua

tensão reduzida até que a mesma seja ligeiramente inferior a um terço de Vcc, o que activa o

comparador de disparo e provoca o reset do flip-flop interno, iniciando outro ciclo.

Figura 7: configuração astavel

Fonte : Valdir 2012

Observe na figura que o capacitor C é carregado através de R1 e R2 , enquanto que a descarga e

feita apenas através de R2 . Isto faz com que o tempo de carga seja maior do que o tempo de

descarga, provocando uma assimetria no sinal de saída, ou seja, a saída permanece mais tempo

em nível alto do que em nível baixo.

Temporizador 555 – Trabalho III Página 9

É possível determinar todos os períodos de tempo dos sinais gerados pelo circuito a partir da

expressão:

(𝑅1 + 2𝑅2 )𝐶1

𝑡=

1,44

2.3. Aplicações do temporizador 555

Pode-se citar como principais aplicações:

Temporizador de precisão;

Relógio (gerador de onda quadrada);

Delay (gerador de atrasos);

Modulador de largura de pulso;

Modulador de posição de pulsos;

Gerador de rampa.

2.4. Vantagens do temporizador 555

Fácil de utilizar em vários tipos de circuitos;

É de fácil aquisição no mercado de Electrónica;

Reduzido número de componentes externos para uma infinidade de aplicações;

A vantagem do ponto de vista industrial ainda pode-se citar a alta corrente de saída deste

CI, em torno de 200 𝑚𝐴. Corrente esta que pode accionar directamente relés, lâmpadas,

entre outros componentes que tenham demanda por potência elevadas;

Pode ser utilizado de inúmeras formas e configurações diferentes.

Temporizador 555 – Trabalho III Página 10

3. Conclusão

Terminado o trabalho, concluiu-se que o temporizador 555 é um circuito integrado muito

importante na electrónica, este circuito integrado tem aplicações que variam de equipamentos

domésticos à circuitos de sincronização de precisão.

Apesar de não se tratar de um componente digital, o temporizador 555 é largamente utilizado

como base de marcação de tempo em circuitos analógicos e também em circuitos digitais.

Devido à sua grande versatilidade, tornou-se um padrão Industrial, podendo ser utilizado de

inúmeras formas e configurações/modos de operação diferentes sendo as mais comuns: a

configuração monoestável e a configuração astável.

A configuração monoestável é um circuito que possui um estado estável e outro semi-estável.

Quando o circuito é levado ao estado semi-estável, através de alguma “perturbação” externa, ele

permanece um período de tempo neste estado e depois retorna ao seu estado estável,

permanecendo assim até que uma nova perturbação externa seja aplicada. Isto é, quando ele

recebe um sinal adequado no gatilho ele gera um pulso de duração específica na saída, depois ele

volta a deixar a saída desligada e fica pronto para receber outro estímulo. Caso durante o período

em que saída está ligada ele receber um sinal de reset ela é desligada imediatamente.

Diferente da monoestável, a configuração astável é um circuito que não necessita de disparo,

gerando uma sequência de pulsos rectangulares contínua. Isto é, não tem estado estável oscilando

entre dois estados estáveis sem qualquer disparo externo.

Temporizador 555 – Trabalho III Página 11

4. Bibliografia

[1] FLOYD, Thomas L. Sistemas Digitais: fundamentos e aplicações. Porto Alegre: Bookman

9a ed. 2007

[2] DEAECTO, Grace S. Circuitos Lógicos. Faculdade de Engenharia Mecânica/UNICAMP

2013

[3] MARTINS, Geomar Machado. Princípios de Automação Industrial. 2007

[4]TORTATO, Alexandre Zeglin. Circuito integrado 555

[5] MOURA, Adriano Ferreira de. Eletrônica Digital II. Brasília: NT Editora 1. ed.2017

Temporizador 555 – Trabalho III Página 12

Você também pode gostar

- TemporizadorDocumento17 páginasTemporizadorCassimo IsmaelAinda não há avaliações

- Jaime 555Documento18 páginasJaime 555Jaime TemboAinda não há avaliações

- Oscilador MonoestávelDocumento21 páginasOscilador MonoestávelSamuel JohnnyAinda não há avaliações

- Relatório Prática AmplificadoresDocumento23 páginasRelatório Prática AmplificadoresAnderson MirandaAinda não há avaliações

- Relatório TecnicoDocumento13 páginasRelatório TecnicoFernanda RodriguesAinda não há avaliações

- Controlador Temperatura Amp-OpDocumento10 páginasControlador Temperatura Amp-OpGerson MonteiroAinda não há avaliações

- TP1 Laboratório de Eletrônica II - PUC MinasDocumento19 páginasTP1 Laboratório de Eletrônica II - PUC MinasAlfredo FariaAinda não há avaliações

- Familiarização com o kit de eletrônica digitalDocumento11 páginasFamiliarização com o kit de eletrônica digitalAmíchelDeJesusSalomãoAinda não há avaliações

- Amplificador AB de 5W para áudioDocumento8 páginasAmplificador AB de 5W para áudioRAFAEL FREITAS FERREIRAAinda não há avaliações

- Temporizador 555 PDFDocumento13 páginasTemporizador 555 PDFAnonymous l6iWMguYAinda não há avaliações

- 2 - EL Potência - 2018Documento11 páginas2 - EL Potência - 2018Eleuterio de FatimaAinda não há avaliações

- Terceiro Relatorio Do LEI 26.03.2022Documento15 páginasTerceiro Relatorio Do LEI 26.03.2022SJB Record CompanyAinda não há avaliações

- Trabalho de Digital - Cassimo Devá PDFDocumento15 páginasTrabalho de Digital - Cassimo Devá PDFCassimo IsmaelAinda não há avaliações

- Simulação de transformadores trifásicosDocumento11 páginasSimulação de transformadores trifásicosBrianAinda não há avaliações

- 1-Apostila Eletrônica Aplicada - 15-06-2015Documento70 páginas1-Apostila Eletrônica Aplicada - 15-06-2015Robs100% (3)

- UNI-RN: Amplificadores Inversor, Não Inversor e ComparadorDocumento16 páginasUNI-RN: Amplificadores Inversor, Não Inversor e ComparadorMateus Arnaud GoldbargAinda não há avaliações

- Medição de defasagem em transformadorDocumento7 páginasMedição de defasagem em transformadorLeonardo Carlos Silva DiasAinda não há avaliações

- Caracterização de para-raios de ZnO e varistoresDocumento14 páginasCaracterização de para-raios de ZnO e varistoresWilliam PinheiroAinda não há avaliações

- EL2_AULA_15_LABDocumento3 páginasEL2_AULA_15_LABMatheus Eduardo TeschAinda não há avaliações

- Medições com multímetros e osciloscópiosDocumento4 páginasMedições com multímetros e osciloscópiosYimeAinda não há avaliações

- Lista 01 - Circuitos Com Diodos - TecDocumento3 páginasLista 01 - Circuitos Com Diodos - TecGustavo BorgesAinda não há avaliações

- Projeto VoltimetroDocumento9 páginasProjeto VoltimetroAlexsander CarneiroAinda não há avaliações

- Portas lógicas: Coletor aberto, Tri-state e Schmitt triggerDocumento6 páginasPortas lógicas: Coletor aberto, Tri-state e Schmitt triggerRobert MaxelAinda não há avaliações

- 04 Projeto 2 PotenciometroDocumento5 páginas04 Projeto 2 PotenciometroalexandreAinda não há avaliações

- EC-Relatorio I&IIDocumento11 páginasEC-Relatorio I&IIAlexandre UamusseAinda não há avaliações

- Análise do comportamento dos amplificadores em diferentes configuraçõesDocumento22 páginasAnálise do comportamento dos amplificadores em diferentes configuraçõesRofino PascoalAinda não há avaliações

- (Modelo) Relatorio-Aulas Lab EB UFR v02Documento9 páginas(Modelo) Relatorio-Aulas Lab EB UFR v02victor hugoAinda não há avaliações

- Prática 1 - Ponte de WheatstoneDocumento16 páginasPrática 1 - Ponte de WheatstoneGuilherme Pigato PaesAinda não há avaliações

- Modulador FM com amplificação e contador C.I 555Documento8 páginasModulador FM com amplificação e contador C.I 555suedcozersartorioAinda não há avaliações

- Relatório IntegradorDocumento5 páginasRelatório IntegradorJoão LucasAinda não há avaliações

- Tinkercad Atividade2Documento3 páginasTinkercad Atividade2MAS Attoyyibiyyah100% (1)

- Fonte Simétrica CEFET-MGDocumento14 páginasFonte Simétrica CEFET-MGGabriel De LelisAinda não há avaliações

- Aula 04Documento6 páginasAula 04joaovsaviAinda não há avaliações

- 2 Atividade - Instrumentação BásicaDocumento7 páginas2 Atividade - Instrumentação BásicaLucas SouzaAinda não há avaliações

- Circuito retificador meia ondaDocumento5 páginasCircuito retificador meia ondaBrunoAinda não há avaliações

- Apostila CEL030!2!2019Documento98 páginasApostila CEL030!2!2019Rita Elena de Assis SilvaAinda não há avaliações

- Aplicação dos diodos em circuitos retificadoresDocumento16 páginasAplicação dos diodos em circuitos retificadoresLuís NoahAinda não há avaliações

- LVDT PDFDocumento15 páginasLVDT PDFpeterson_msc5Ainda não há avaliações

- Partida compensadora de motor trifásicoDocumento9 páginasPartida compensadora de motor trifásicoAna AlvesAinda não há avaliações

- Projeto Fontes Chaveadas Apostila INVERSORDocumento16 páginasProjeto Fontes Chaveadas Apostila INVERSORcharlesfp1Ainda não há avaliações

- Parte Escrita ConversorDocumento16 páginasParte Escrita ConversorterevanAinda não há avaliações

- EL2_AULA_13_LABDocumento3 páginasEL2_AULA_13_LABMatheus Eduardo TeschAinda não há avaliações

- Relatório 1Documento15 páginasRelatório 1Denilson Adelino CossaAinda não há avaliações

- PesqDocumento7 páginasPesqsthefanyAinda não há avaliações

- Circuitos elétricos: análise de retificadores com carga RLDocumento8 páginasCircuitos elétricos: análise de retificadores com carga RLMaicon FrancoAinda não há avaliações

- Guia de Aulas Práticas de Laboratório de Eletrônica IDocumento49 páginasGuia de Aulas Práticas de Laboratório de Eletrônica Inathan bandeiraAinda não há avaliações

- PUC-GO Engenharia Aula Prática Retificador Onda CompletaDocumento3 páginasPUC-GO Engenharia Aula Prática Retificador Onda Completarenatomedeiros1971Ainda não há avaliações

- MA 2 Sistemas Digitais - 04-12Documento9 páginasMA 2 Sistemas Digitais - 04-12Ivan FilhoAinda não há avaliações

- Exp03 AULA 04 - Circuitos Multivibradores 18-08-2023 ANDRE ALEX MATHEUSDocumento6 páginasExp03 AULA 04 - Circuitos Multivibradores 18-08-2023 ANDRE ALEX MATHEUSALEX PESSOA PIMENTELAinda não há avaliações

- Equipamentos Laboratório Eletrônica DigitalDocumento8 páginasEquipamentos Laboratório Eletrônica DigitalJoão Pedro da Silva RodriguesAinda não há avaliações

- Relatório Do Projeto Fonte CCDocumento23 páginasRelatório Do Projeto Fonte CCRobert RonnesAinda não há avaliações

- Componentes CC e CADocumento4 páginasComponentes CC e CAFrancisco LopesAinda não há avaliações

- Introdução ao Multisim e Figuras de Lissajous no Circuito RL SérieDocumento10 páginasIntrodução ao Multisim e Figuras de Lissajous no Circuito RL SérieMAXWELL OLIVEIRA DOS SANTOSAinda não há avaliações

- Relatorio Eletronica Basica 1Documento15 páginasRelatorio Eletronica Basica 1Álex VieiraAinda não há avaliações

- Aplicações do CI 555Documento10 páginasAplicações do CI 555Filipe TheveninAinda não há avaliações

- Esquemas de ligação para bancada didática DK-8Documento38 páginasEsquemas de ligação para bancada didática DK-8Francisco MeloAinda não há avaliações

- AP Instrumentacao Eletronica Amplificador InversorDocumento7 páginasAP Instrumentacao Eletronica Amplificador InversorAprovouAinda não há avaliações

- Indução electromagnética: Fluxo magnético e f.e.m induzida em solenoides e espiraisDocumento3 páginasIndução electromagnética: Fluxo magnético e f.e.m induzida em solenoides e espiraisCassimo IsmaelAinda não há avaliações

- Corrente alternada e impedância elétricaDocumento3 páginasCorrente alternada e impedância elétricaCassimo IsmaelAinda não há avaliações

- .carta de disponibilidade_1708455462000Documento1 página.carta de disponibilidade_1708455462000Cassimo IsmaelAinda não há avaliações

- Perguntas e RespostasDocumento1 páginaPerguntas e RespostasCassimo IsmaelAinda não há avaliações

- Comunicação AssertivaDocumento13 páginasComunicação AssertivaCassimo IsmaelAinda não há avaliações

- Trabalho Mic Assertiva YE-1Documento10 páginasTrabalho Mic Assertiva YE-1Cassimo IsmaelAinda não há avaliações

- Trabalho Sobre Comunicacao Assertiva 2017Documento12 páginasTrabalho Sobre Comunicacao Assertiva 2017Cassimo IsmaelAinda não há avaliações

- Filogenia ArseniaDocumento2 páginasFilogenia ArseniaCassimo IsmaelAinda não há avaliações

- AulaTeoríca#1 2020.Ppt EMarraDocumento37 páginasAulaTeoríca#1 2020.Ppt EMarraCassimo IsmaelAinda não há avaliações

- CicloBryton 20171203105626 PDFDocumento73 páginasCicloBryton 20171203105626 PDFRichelliKemerAinda não há avaliações

- Anexo BiogeogDocumento2 páginasAnexo BiogeogCassimo IsmaelAinda não há avaliações

- AulaTeoríca#4 2020.Ppt EMarraDocumento50 páginasAulaTeoríca#4 2020.Ppt EMarraCassimo IsmaelAinda não há avaliações

- Parâmetros elétricos e tipos de disjuntoresDocumento3 páginasParâmetros elétricos e tipos de disjuntoresCassimo IsmaelAinda não há avaliações

- Introdução à Estatística: Noções GeraisDocumento94 páginasIntrodução à Estatística: Noções GeraisCassimo IsmaelAinda não há avaliações

- Resposta Sobre Resistencia AmbientalDocumento2 páginasResposta Sobre Resistencia AmbientalCassimo IsmaelAinda não há avaliações

- ArlindoDocumento1 páginaArlindoCassimo IsmaelAinda não há avaliações

- ISP de Tete MamoDocumento9 páginasISP de Tete MamoCassimo IsmaelAinda não há avaliações

- Capa 1Documento1 páginaCapa 1Cassimo IsmaelAinda não há avaliações

- TEXTO DE APOIO-03-Textos Jornalístcos-11. CLASSE-2021Documento4 páginasTEXTO DE APOIO-03-Textos Jornalístcos-11. CLASSE-2021Cassimo IsmaelAinda não há avaliações

- Otimização Multiobjectiva no Curso de Engenharia ElétricaDocumento14 páginasOtimização Multiobjectiva no Curso de Engenharia ElétricaCassimo IsmaelAinda não há avaliações

- Errata 2Documento2 páginasErrata 2Cassimo IsmaelAinda não há avaliações

- Circuito integrado temporizador 555 guia completoDocumento6 páginasCircuito integrado temporizador 555 guia completoClodoaldo SouzaAinda não há avaliações

- Mostradores digitais de 7 segmentos: introdução e aplicaçõesDocumento14 páginasMostradores digitais de 7 segmentos: introdução e aplicaçõesCassimo IsmaelAinda não há avaliações

- Cálculo correntes CC rede em vazio e cargaDocumento4 páginasCálculo correntes CC rede em vazio e cargaCassimo IsmaelAinda não há avaliações

- Job2 - NharDocumento13 páginasJob2 - NharCassimo IsmaelAinda não há avaliações

- Errata 1 GubudoDocumento1 páginaErrata 1 GubudoCassimo IsmaelAinda não há avaliações

- Cremosa 2Documento15 páginasCremosa 2Cassimo IsmaelAinda não há avaliações

- Amurildine IbraimoDocumento23 páginasAmurildine IbraimoCassimo IsmaelAinda não há avaliações

- ResistoresDocumento4 páginasResistoresAlos F. FernandesAinda não há avaliações

- Atividade 4 - MAT - 7 AnoDocumento2 páginasAtividade 4 - MAT - 7 AnoLusianny Chaves100% (1)

- MODELO DE FORMULARIO de Controle de VeiculosDocumento2 páginasMODELO DE FORMULARIO de Controle de VeiculosEduardo BausasAinda não há avaliações

- Leis ponderais e volumétricas na químicaDocumento5 páginasLeis ponderais e volumétricas na químicaJoão CarlosAinda não há avaliações

- 2000 Provao EletricaDocumento24 páginas2000 Provao EletricaLuis Cláudio LAAinda não há avaliações

- Automação de SistemasDocumento33 páginasAutomação de SistemasDanilo CruzAinda não há avaliações

- Resultado Preliminar Historico Escolar Ou EquivalenteDocumento263 páginasResultado Preliminar Historico Escolar Ou Equivalentemarcoshared1Ainda não há avaliações

- Guia Pratico Da Farmacia MagistralDocumento297 páginasGuia Pratico Da Farmacia Magistralluciana94% (16)

- RadiestesiaDocumento13 páginasRadiestesiasamuka765100% (1)

- Muros de Arrimo: Teorias, Tipos e Sistemas de DrenagemDocumento79 páginasMuros de Arrimo: Teorias, Tipos e Sistemas de DrenagemdaphneAinda não há avaliações

- Medidor eletrônico de energia com acesso remotoDocumento28 páginasMedidor eletrônico de energia com acesso remotoRobert MoraisAinda não há avaliações

- Prova Feira de Santana BA 2018 AOCPDocumento11 páginasProva Feira de Santana BA 2018 AOCPAna Paula FerreiraAinda não há avaliações

- Manual Estudantes Engenharia (Em Actualização)Documento175 páginasManual Estudantes Engenharia (Em Actualização)nelito lamuceneAinda não há avaliações

- Sistema Elétrico - Descrição do CBCUDocumento39 páginasSistema Elétrico - Descrição do CBCURolando Mancilla FloresAinda não há avaliações

- Unidade I - Design de Interiores: Representação (UNIP)Documento30 páginasUnidade I - Design de Interiores: Representação (UNIP)Debora Diana100% (1)

- Termostato digital TIC-17RGTiDocumento1 páginaTermostato digital TIC-17RGTimarcaometal100% (1)

- ABNT NBR 13543 Movimentação de Carga - Laços de Cabo de Aço - Utilização e ManutençãoDocumento12 páginasABNT NBR 13543 Movimentação de Carga - Laços de Cabo de Aço - Utilização e ManutençãoAntonio Fernando NavarroAinda não há avaliações

- Propriedades gerais da matéria explicadasDocumento2 páginasPropriedades gerais da matéria explicadasgracielma joiceAinda não há avaliações

- Livro Bombeamento HEBER PIMENTEL GOMES PDFDocumento13 páginasLivro Bombeamento HEBER PIMENTEL GOMES PDFÂngela BarrosAinda não há avaliações

- Análise de custos: ponto de equilíbrio e margem de contribuiçãoDocumento3 páginasAnálise de custos: ponto de equilíbrio e margem de contribuiçãoAntônio AlvesAinda não há avaliações

- Galileu 03Documento25 páginasGalileu 03Leonardo Rodrigues PietroAinda não há avaliações

- Exercícios PolinomiosDocumento3 páginasExercícios PolinomiosNathan RezendeAinda não há avaliações

- Instalar Docker Windows Linux MacDocumento2 páginasInstalar Docker Windows Linux MacDiogo Alves Miranda BarbosaAinda não há avaliações

- Central Mini-Hídrica no Rio Dão - Elementos para Localização e DimensionamentoDocumento20 páginasCentral Mini-Hídrica no Rio Dão - Elementos para Localização e DimensionamentoMiguel PereiraAinda não há avaliações

- Humanismos contemporâneos: sentidos e paradigmasDocumento1 páginaHumanismos contemporâneos: sentidos e paradigmasLucas SouzaAinda não há avaliações

- CROMATISMODocumento5 páginasCROMATISMOJoão Francisco ZamboniAinda não há avaliações

- Aula 2.2 - Principio Funcionamento MIM e MIT.Documento14 páginasAula 2.2 - Principio Funcionamento MIM e MIT.GUILHERME FERREIRA DOS SANTOSAinda não há avaliações

- Comandos do WordDocumento4 páginasComandos do WordjorgeAinda não há avaliações

- Kit de ferramentas OTC-Bosch para manutenção de baterias e sistemas automotivosDocumento13 páginasKit de ferramentas OTC-Bosch para manutenção de baterias e sistemas automotivosAlex BernardiAinda não há avaliações

- 30 Exercícios de GeologiaDocumento8 páginas30 Exercícios de GeologiaAlice Nardoni MarteliAinda não há avaliações