Escolar Documentos

Profissional Documentos

Cultura Documentos

Micro Control Ad or Pic

Enviado por

Cézar AngelitonDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Micro Control Ad or Pic

Enviado por

Cézar AngelitonDireitos autorais:

Formatos disponíveis

DEPARTAMENTO DE ELECTROTECNIA

M I C R OC ON T R OL A D OR E S

Joo Paulo Baptista

Curso de Engenharia Electrotcnica Electrnica e Computadores Sistemas Digitais / 2001

MICROCONTROLADORES

1 Arquitectura Base de um Computador

O projecto de qualquer computador pode ser conseguido atravs da implementao de 3 blocos funcionais, interligados entre si, como se representa na fig.1.

Figura 1 Arquitectura base de um computador 1.1 CPU O CPU (Unidade de Processamento Central) o responsvel pela correcta execuo das instrues de um programa, efectuando as transferncias de dados e as operaes lgicas e aritmticas implcitas nessas instrues. Este CPU constitudo por: Unidade de Controlo, que gera todos os sinais necessrios execuo de cada uma das instrues includas no programa. Processador ALU Unidade Lgica e Aritmtica, onde se encontram implementadas as unidades que permitem efectuar as operaes lgicas e aritmticas; Registos, utilizados para o armazenamento temporrio de operandos e resultados de operaes; Controlo de Barramentos, permitindo gerir o trfego de informao para o acesso aos dispositivos exteriores.

Num computador, as funes do CPU so desempenhadas normalmente por um microprocessador (p. ex. Z80).

1.2 Memria Este bloco, constitudo por dispositivos de memria (ROM, EPROM, E2PROM, FLASH EPROM, RAM, NVRAM, etc.) permite o armazenamento de instrues de programa e dados e pode ser logicamente dividida em: Memria de Programa, onde so guardadas as instrues a executar pelo CPU; Memria de Dados, onde so guardados todos os dados necessrios ao processamento ou provenientes do processamento.

1.3 E/S (Entradas/Sadas) Este bloco do computador permite a sua interligao com dispositivos perifricos para entrada ou sada de dados (teclado, monitor, impressora, sensores, conversores A/D ou D/A, etc.). Fisicamente constitudo por hardware que permite a transmisso/recepo de dados e, em alguns casos, a sua formatao. 1.4 Barramento de Memria e Barramento de E/S Embora logicamente diferentes, normalmente estes 2 barramentos no so distintos fisicamente. So constitudos por condutores que permitem a transferncia da informao entre o CPU e a memria ou os dispositivos de E/S. A constituio destes barramentos a seguinte: Barramento de Endereos, unidireccional, onde o CPU coloca o endereo de memria ou do dispositivo de onde quer ler ou onde quer escrever (p. ex. no Z80 constitudo pelas linhas A0..A15); Barramento de Dados, bidireccional, onde circulam os dados resultantes da comunicao de ou para o CPU (p. ex. linhas D0..D7 no Z80); Barramento de Controlo, bidireccional, que contm os sinais necessrios para uma correcta implementao do protocolo de comunicao (p. ex. no Z80 as linhas WR, RD, MREQ, IOREQ, etc.).

1.5 Barramento de DMA (Direct Memory Access) Na maior parte dos computadores, a transferncia de dados entre os dispositivos de E/S e a memria pode ser feita sem a interveno directa do CPU, libertando-o assim para outras tarefas que podem ser feitas em paralelo. Esta transferncia de informao, que utiliza controladores especficos, feita atravs do barramento de acesso directo memria. 1.6 MicroControladores O aumento da capacidade de integrao, permitiu aos fabricantes a insero, num nico circuito integrado, dos diferentes componentes que implementam um computador. Assim, hoje em dia possvel encontrar uma infinidade de dispositivos que contm CPU, memria, portos de entrada/sada de dados e perifricos especficos para determinadas aplicaes (conversores A/D e D/A, portos de comunicao srie, geradores de PWM, temporizadores e contadores, dispositivos de watchdog, etc.). A maior parte das vezes estes Controladores disponibilizam os barramentos para o exterior permitindo assim a sua expanso atravs da

adio de circuitos perifricos. Na fig. 1 est indicada a constituio destes dispositivos de processamento, dos quais iremos estudar em pormenor 2 exemplos tpicos.

2 Controlador PIC16F84A

Trata-se de um micro controlador desenvolvido pela Microchip (www.microchip.com), cuja implementao conseguida num integrado de 18 pinos como se mostra na fig. 2.

Figura 2 O C PIC16F84A

Neste circuito so disponibilizados para o exterior 2 portos de entrada/sada de dados RB0..RB7 e RA0..RA4 o que permite a utilizao de 13 bits de I/O, programveis individualmente como entrada ou sada. Atravs de 5 destes bits de I/O possvel aceder do exterior ao sistema de interrupes do micro controlador (RB0 e RB4..RB7). Dado que estes circuitos possuem j um oscilador interno, a referncia de oscilao conseguida atravs da ligao de um cristal ou de uma malha RC nos pinos OSC1 e OSC2. Isto vai determinar, como ser visto mais frente, a velocidade de funcionamento do C. A entrada CLKIN permite ainda que o sinal de relgio do C seja fornecido a partir de um oscilador externo. Uma tenso de 0V aplicada entrada MCLR permite colocar o C em estado de reset. Logo que esta tenso comute para VDD, o C sai da situao de reset, comeando a execuo do programa a partir da instruo que se encontra no endereo 0 (vector de reset). Os valores com que os diferentes registos so carregados nesta operao sero apresentados nos pargrafos seguintes. O bit RA4 pode funcionar alternativamente como entrada de um sinal de relgio para um contador crescente de 8 bits que se encontra integrado no C. O funcionamento deste contador / temporizador (TMR0) ser objecto de um estudo mais aprofundado no pargrafo 4.

2.1 Arquitectura do PIC16F84 A fig. 3 apresenta um diagrama de blocos que traduz a arquitectura deste C.

Figure 3 Arquitectura do PIC16F84A Neste diagrama de blocos podem ser identificados os diferentes componentes de um computador como foram apresentados no pargrafo 1. A constituio de cada um dos componentes ser a seguinte: CPU Processador ALU, reg W, reg STATUS, reg FSR Unidade de Controlo reg de instrues, descodificador de instrues, contador de programa, stack Memria Memria de programa E2PROM (1K x 14 bits) Memria de dados RAM (68 x 8 bits) Barramentos barramentos internos, independentes, um para a memria de programa (14 bits de largura) e um para a memria de dados (8 bits de largura) Perifricos portos de E/S (I/O) 1 temporizador / contador de 8 bits (TMR0) Memria de dados E2PROM (64 x 8 bits) Temporizador Watchdog

2.1.1 Arquitectura de Harvard Uma das particularidades deste C tem a ver com o tipo de arquitectura especfica normalmente denominada de arquitectura de Harvard. Neste tipo de arquitectura, a memria de programa e a memria de dados esto fisicamente separadas o mesmo acontecendo com os respectivos barramentos de interligao com o CPU. Dado que o acesso a estas memrias feito atravs de barramentos diferentes, possvel a utilizao da memria de dados ao mesmo tempo que feita a pesquisa de uma instruo da memria de programa. Ao contrrio dos CPUs que utilizam uma arquitectura de Von-Newman, em que aquela distino fsica no verificada e o ciclo de funcionamento feito atravs do sequenciamento de operaes de fetch e de execuo, nos CPUs com arquitectura de Harvard a execuo da instruo actual pode ser feita em simultneo com o fetch da prxima instruo. Este tipo de operao, que se esquematiza no diagrama temporal apresentado na fig. 4, permite obter uma velocidade de processamento que, teoricamente, ser o dobro da obtida com um CPU com arquitectura Von-Newman.

Figure 4 Execuo com sobreposio Claro que s teoricamente que o aumento de velocidade de 2 vezes. Com determinado tipo de instrues, todas aquelas que provocam uma alterao do contador de programa (Program Counter), esta sobreposio do fetch e da execuo falha, havendo necessidade de efectuar um novo fetch. Este problema apresentado na fig. 5.

Figura 5 Execuo de instrues que alteram o PC Quando est a ser executada a instruo 3 est em simultneo a ser feito o fetch da instruo 4. Dado que o resultado da execuo de 3 um salto para uma instruo que no a 4, a instruo pesquisada tem de ser rejeitada para dar origem pesquisa de uma nova instruo. Podemos ver aqui que a instruo CALL (assim como outras instrues) demora o dobro do tempo a ser executada.

2.2 Memria de Programa O PIC16F84 dispe de um contador de programa com 13 bits capaz de enderear 8K posies de memria de 14 bits. Neste C s se encontra implementado 1K com endereos de 0000h a 03FFh. A estrutura desta memria apresentada na fig. 6. A estrutura de stack apresenta um mximo de 8 nveis o que impe uma limitao em termos de chamadas a subrotinas dentro de outras subrotinas. O vector de reset corresponde posio de memria 0000h enquanto que o vector de interrupo se encontra atribudo posio 0004h.

Figura 6 Memria de programa

Figura 7 Memria de dados

2.3 Memria de Dados A memria de dados do 16F84 encontra-se dividida em duas reas, conforme se pode ver na fig. 7. A primeira a rea correspondente aos Registos de Funo Especial (SFR) enquanto que a segunda diz respeito aos Registos de Uso Geral. Os SFRs so utilizados para o controlo do C. Uma das particularidades desta memria a sua diviso em dois Bancos (Banco 0 e Banco 1) sendo o acesso a cada um destes bancos controlado a partir do bit 5 do registo STATUS (RP0). De notar que, no que diz respeito aos registos de uso geral, o banco 1 destes registos encontra-se mapeado no banco 0 o que quer dizer que qualquer acesso ao banco 1 feito na realidade sobre o banco 0.

2.3.1 Registos de Uso Geral Cada registo de uso geral tem uma largura de 8 bits e pode ser acedido directamente ou indirectamente atravs do registo FSR (ver mais frente). Como foi dito anteriormente, os endereos do banco 1 encontram-se mapeados no banco 0. Por exemplo, o endereamento da posio de memria 0Ch ou 8Ch acede ao mesmo registo de uso geral. 2.3.2 Registos de Funo Especial Os Registos de Funo Especial (Fig.7 e Tabela1) so utilizados pelo CPU e pelos perifricos para o controlo do C. Estes registos so implementados em RAM esttica. Os SFRs que fazem parte do ncleo do C sero analisados nesta seco enquanto que os SFRs ligados aos dispositivos perifricos sero descritos em seces posteriores.

Tabela 1 Registos de funo especial (SFR)

2.3.2.1 Registo STATUS O registo STATUS contm as flags ligadas ALU, as flags de RESET e os bits de seleco do banco da memria de dados.

R = bit de leitura W = bit de escrita U = no implementado -n = valor de reset

Bit 7 Bit 6-5

IRP Bit de seleco de banco (endereamento indirecto) Este bit no utilizado no PIC16F84(A) RP1:RP0 Bit de seleco de banco (endereamento directo) 00 = Banco 0 (00h 7Fh) 01 = Banco 1 (80h FFh) No PIC16F84(A) s utilizado o RP0 TO Bit de time-out 1 = a seguir a um power-up, a uma instruo CLRWDT, a uma instruo SLEEP 0 = ocorreu um time-out do WDT PD Bit de power-down 1 = a seguir a um power-up ou a uma instruo CLWDT 0 = depois da execuo de uma instruo de sleep Z flag de zero 1 = o resultado de uma operao lgica ou aritmtica zero 0 = o resultado de uma operao lgica ou aritmtica diferente de zero DC Digit carry / borrow 1 = carry existente do bit 3 para o bit 4 do resultado 0 = no existe carry do bit 3 para o bit 4 do resultado C Bit de carry / borrow 1 = existe carry do bit mais significativo do resultado 0 = no existe carry do bit mais significativo do resultado Figura 8 Registo STATUS (endereo 03h, 83h)

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

2.3.2.2 Registo OPTION_REG Trata-se de um registo que permite escrita e leitura e que contm vrios bits de controlo para a configurao do divisor de frequncia (prescaler) do TMR0 / WDT, da interrupo externa INT, do TMR0 e das polarizaes (pull-ups) do PORTB.

R = bit de leitura W = bit de escrita U = no implementado -n = valor de reset

Bit 7

RBPU Activao dos pull-ups internos do PORTB 1 = pull-ups internos desactivados 0 = pull-ups internos activados INTEDG Seleco do flanco de activao da interrupo INT 0 = interrupo no flanco descendente do sinal em RB0/INT 1 = interrupo no flanco ascendente do sinal em RB0/INT T0CS Seleco da fonte do sinal para o TMR0 1 = transio no pino RA4/T0CKI 0 = ciclo interno de instruo T0SE Seleco do flanco do sinal que activa o TMR0 1 = incrementa no flanco descendente do sinal em RA4/T0CKI 0 = incrementa no flanco ascendente do sinal em RA4/T0CKI PSA Bit de atribuio do prescaler (divisor de frequncia) 1 = prescaler atribudo ao WDT 0 = prescaler atribudo ao TMR0 PS2: PS0 Programao do prescaler (divisor de frequncia)

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2-0

Figura 9 Registo OPTION-REG (endereo 81h)

10

2.3.2.3 Registo INTCON O registo INTCON contm os diferentes bits que permitem configurar o sistema de interrupes (enable /disable) e as flags de pedido de interrupo. Este registo pode ser lido ou escrito.

R = bit de leitura W = bit de escrita U = no implementado -n = valor de reset

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

GIE Enable / Disable global das interrupes 1 = Permite todas as interrupes que no se encontram mascaradas 0 = Desactiva todas as interrupes EEIE Bit de autorizao da interrupo de fim de escrita na E2PROM de dados 1 = permite a interrupo EE 0 = desactiva a interrupo EE T0IE Bit de autorizao da interrupo do TMR0 1 = permite a interrupo do TMR0 0 = desactiva a interrupo do TMR0 INTE Bit de autorizao da interrupo INT 1 = permite a interrupo INT 0 = desactiva a interrupo INT RBIE Bit de autorizao da interrupo gerada pela alterao de RB4:RB7 1 = permite a interrupo de RB4:RB7 0 = desactiva a interrupo de RB4:RB7 T0IF Flag de pedido de interrupo do TMR0 (quando existe overflow) 1 = overflow do TMR0 ( necessrio limpar a flag por software) 0 = no h overflow do TMR0 INTF Flag de pedido de interrupo externa INT 1 = h um pedido de interrupo ( necessrio limpar a flag por software) 0 = no existe pedido de interrupo INT RBIF Flag de pedido de interrupo por alterao de RB4:RB7 1 = h um pedido de interrupo ( necessrio limpar a flag por software) 0 = no existe pedido de interrupo RB Figura 10 Registo INTCON (endereo 0Bh, 8Bh)

11

2.4 Registos PCL e PCLATH O contador de programa (PC) especifica o endereo da instruo a ser pesquisada (fetch) da memria de programa para ser executada. No PIC16F84 o PC tem uma largura de 13 bits, estando os 8 bits menos significativos colocados no registo PCL. Este registo pode ser lido ou escrito por software. O byte mais significativo do PC designado por PCH e contm os bits 12:8 do contador de programa. Este registo no pode ser escrito ou lido directamente. Todas as operaes que seja necessrio efectuar sobre ele so feitas indirectamente sobre o registo PCLATH. 2.4.1 STACK A estrutura de stack implementada no PIC16F84 permite a ocorrncia de combinaes de at 8 chamadas de subrotinas ou interrupes, permitindo armazenar os respectivos endereos de retorno. De notar que a utilizao desta estrutura da exclusiva responsabilidade da unidade de controlo do C, no havendo por isso qualquer instruo de software que a permita manipular. 2.5 Endereamento Indirecto: registos INDF e FSR O registo INDF (endereo 00h / 80H) no um registo fsico. O acesso a este registo (leitura ou escrita) acede realmente ao registo cujo endereo se encontra no registo FSR. Este ltimo registo o ponteiro para as operaes com endereamento indirecto.

3 Portos de I/O

Alguns dos pinos dos portos de I/O apresentam funes alternativas para a utilizao com alguns perifricos do C. Geralmente, quando essas funes so utilizadas, o respectivo bit no pode ser utilizado como I/O. 3.1 Registos PORTA e TRISA O registo PORTA implementa um porto de I/O bidireccional com 5 bits, estando ligado aos pinos exteriores do C, RA0:RA4. O correspondente registo onde se define, para cada bit, se se trata de entrada ou sada de dados o TRISA. Colocando um bit do registo TRISA a 1 permite programar o respectivo bit do PORTA como entrada de dados j que, como se pode ver nas figs. 11 e 12, o correspondente andar de sada fica em estado de alta impedncia. A escrita de um 0 num bit do registo TRISA programa o respectivo bit do PORTA como sada de dados (o estado do andar de sada vai depender do valor que se escreve na Data Latch). De notar que, aps uma operao de reset, qualquer um dos bits de I/O fica programado como entrada de dados. A leitura do registo PORTA permite fazer a leitura do estado dos pinos exteriores enquanto que uma operao de escrita sobre o mesmo registo coloca os valores de escrita nas Data Latch de sada.

12

O bit RA4 apresenta uma multiplexagem com o sinal de entrada para o TMR0. Como entrada de dados este bit apresenta uma entrada do tipo Schmitt Trigger e como sada do tipo dreno aberto.

Figura 11 RA3:RA0

Figura 12 RA4

Exemplo de programao do PORTA com RA0:RA1 como sada de dados e RA2:RA4 como entrada de dados: clrf bsf movlw movwf bcf PORTA STATUS,RP0 b00011100 TRISA STATUS,RP0 ;Escreve 0s nas Data Latch ;Muda para o banco 1 ;Palavra de programao ;para ser colocada no TRISA ;Regressa ao banco 0

Caractersticas de corrente para o PORTA: Corrente mxima fornecida por cada pino .. IOHmax = 20mA Corrente mxima absorvida por cada pino ...... IOLmax = 25mA Corrente mxima total fornecida pelo PORTA ... IOHmax = 50mA Corrente mxima total absorvida pelo PORTA ... IOLmax = 80mA

13

3.2 Registos PORTB e TRISB PORTB um porto bidireccional de 8 bits que, como acontece com o PORTA, dispe tambm de um registo TRISB para a configurao dos bits como entrada ou sada de dados. Nas figuras 13 e 14 representam-se os diagramas de blocos dos bits que compe este porto.

Figura 13 RB3:RB0

Figura 14 RB7:RB4

Cada um dos bits do PORTB dispe de um pull-up interno que controlado pelo bit 7 do registo OPTION (RBPU). Quando este bit igual a 0, todos os pull-ups esto activados. A configurao de um bit como sada de dados provoca automaticamente a desactivao do respectivo pull-up. Quando feito o power-on reset, os pull-ups so desactivados. Quatro dos bits do PORTB, RB7:RB4, permitem gerar uma interrupo sempre que h uma mudana de estado em qualquer um deles, desde que estejam programados como entrada de dados. Os bits de entrada so permanentemente comparados com o ltimo valor lido do porto. Desde que seja encontrada uma diferena em qualquer um desses bits, activada a flag RBIF de pedido de interrupo. Na rotina de servio da interrupo deve ser feita uma leitura do porto de maneira a anular a situao de diferena de bits, permitindo assim fazer o clear da flag por software. Caractersticas de corrente para o PORTB: Corrente mxima fornecida por cada pino .. IOHmax = 20mA Corrente mxima absorvida por cada pino ...... IOLmax = 25mA Corrente mxima total fornecida pelo PORTB ... IOHmax = 100mA Corrente mxima total absorvida pelo PORTB ... IOLmax = 150mA

14

4 Temporizador / Contador TMR0

O perifrico TMR0 apresenta as seguintes caractersticas principais: Funes de temporizador ou contador de 8 bits Possibilidade de leitura e de escrita do registo Possibilidade de seleco de relgio interno ou externo Seleco do flanco do sinal externo que incrementa o contador Divisor de frequncia de 8 bits programvel por software Permite gerar uma interrupo quando se verificar uma situao de overflow (passagem de FFh a 00h)

A figura seguinte apresenta um diagrama simplificado deste perifrico.

Figura 15 Diagrama de blocos do TIMER0

4.1 Funcionamento O Timer0 pode funcionar como temporizador ou como contador. A seleco do modo de funcionamento feita atravs do bit T0CS ( Timer0 Clock Sourse, bit 5 do OPTION_REG). No modo de temporizador, T0CS=0, o registo TMR0 incrementa em cada ciclo de instruo desde que no seja utilizado o Prescaler (divisor de frequncia). Se, por software, se efectuar uma escrita do registo TMR0, o incremento ser inibido durante 2 ciclos de instruo. Por exemplo, se o relgio do C funcionar a 4MHz, e se no for utilizado o Prescaler, o incremento verifica-se de 1 em 1S. No modo de contador, T0CS=1, o registo TMR0 incrementa em cada flanco ascendente ou descendente do sinal presente no pino exterior RA4/T0CKI. O flanco que provoca o incremento definido pelo bit T0SE (Timer0 Source Edge, bit 4 do OPTION_REG). Se T0SE=0 o flanco activo o ascendente. Neste modo de funcionamento, o sinal proveniente do exterior deve obedecer a determinados requisitos que lhe permite uma sincronizao com o relgio interno do C. 4.2 Prescaler O prescaler no mais que um divisor de frequncia programvel e constitudo por um contador de 8 bits associado a um multiplexer de 8 1, como se mostra na figura 16. Este prescaler partilhado pelo Timer0 e pelo Watchdog Timer, no podendo contudo ser usado

15

em simultneo pelos dois perifricos. Sendo assim, a atribuio do prescaler ao Timer0 significa que o Watchdog Timer funciona sem prescaler, e vice-versa. O valor do prescaler no pode ser lido nem alterado por uma operao de escrita. O bit PSA (PreScaler Assignement, bit 3 do OPTION_REG) permite fazer a atribuio do Prescaler ao Timer0 (PSA=0) ou ao Watchdog (PSA=1). Os bits PS2:PS0 definem a taxa de diviso de frequncia que ser aplicada ao sinal de entrada. Quando o Prescaler est atribudo ao Timer0, podem ser utilizadas as taxas de 1:2, 1:4, , 1:256. Para o caso do Watchdog as taxas possveis so 1:1, 1:2, , 1:128. Estes 3 bits encontram-se mapeados nos 3 bits menos significativos do OPTION_REG.

Figura 16 Prescaler / Postscaler para TIMER0 e Watchdog Quando o Prescaler estiver ligado ao Timer0, qualquer instruo que implemente uma escrita no registo TMR0 provoca um reset do Prescaler. No caso de estar ligado ao Watchdog, a instruo CLRWDT tambm provoca o reset do Prescaler. 4.3 Interrupo do Timer0 Sempre que o incremento do registo TMR0 provocar a passagem de FFh para 00h (overflow) activada a flag de interrupo T0IF (Timer0 Interrupt Flag, bit 2 do registo INCON). Se a respectiva interrupo estiver autorizada, como veremos mais frente, desencadeado um processo de interrupo do C. Esta flag deve ser colocada em 0 por software.

16

Tabela 2 Registos associados ao TIMER0

5 Memria de Dados EEPROM

Trata-se de um conjunto de 64 bytes implementados em memria no voltil do tipo EEPROM. Estas posies de memria podem ser lidas ou escritas durante o funcionamento normal do C, dispondo do seu prprio espao de endereamento. O acesso a esta zona de memria feita indirectamente atravs de 4 SFRs (registos de funo especial): EECON1 EECON2 EEDATA EEADR

O registo EEDATA recebe os 8 bits lidos de um determinado endereo ou contm os 8 bits destinados a ser escritos num determinado endereo. Este endereo deve estar escrito no registo EEADR. Dado que s dispomos de 64 bytes. Os endereos podem variar entre 00h e 3Fh. A escrita de um byte provoca o automtico apagamento da respectiva posio de memria antes que o novo byte seja escrito (erase before write). Esta memria de dados permite um nmero bastante elevado de operaes de apagamento/escrita, tipicamente de 10 milhes de operaes, sendo estas operaes controladas por um temporizador interno ao dispositivo de memria. O tempo destas operaes pode variar com a tenso de alimentao, com a temperatura e de C para C.

Tabela 3 Registos associados memria de dados E2PROM

17

5.1 Leitura da memria de dados EEPROM Para ler uma posio de memria basta para isso colocar em EEADR o endereo pretendido e colocar em 1 o bit RD do registo EECON1 (bit 0). O resultado da leitura fica disponvel no registo EEDATA no prximo ciclo de instruo.

R = bit de leitura W = bit de escrita U = no implementado -n = valor de reset

Bit 7:5 Bit 4

No implementados Lidos como 0 EEIF Flag de interrupo da operao de escrita na EEPROM 1 = operao de escrita terminada ( deve ser colocada em 0 por software) 0 = a operao de escrita no est completa ou no comeou WRERR Flag de erro da EEPROM 1 = a operao de escrita foi terminada prematuramente 0 = operao de escrita terminada correctamente WREN Bit de autorizao de escrita na EEPROM 1 = operao de escrita autorizada 0 = operao de escrita no autorizada WR Bit de controlo de escrita 1 = inicia uma operao de escrita. Este bit colocado em 0 pelo hardware no fim da operao de escrita 0 = o ciclo de escrita na EEPROM est completo RD Bit de controlo de leitura 1 = inicia uma operao de leitura. Este bit colocado em 0 pelo hardware no fim da operao de leitura 0 = operao de leitura no iniciada Figura 17 Registo EECON1

Bit 3

Bit 2

Bit 1

Bit 0

Exemplo de leitura: movlw movwf bsf bsf bcf movf endereo EEADR STATUS,RP0 EECON1,RD STATUS,RP0 EEDATA,W ;Endereo em EEADR ;Comuta para banco 1 ;Activa bit de leitura ;Retorna ao banco 0 ;L dados de EEDATA

5.2 Escrita na memria de dados EEPROM O procedimento de escrita iniciado com o preenchimento do registo de endereo e do registo de dados. A seguir deve ser iniciada uma sequncia especfica de instrues que permitem a escrita real do byte na posio de memria endereada por EEADR.

18

Exemplo de escrita: bsf bcf bsf movlw movwf movlw movwf bsf bsf bcf bcf STATUS,RP0 INTCON,GIE EECON1,WREN 55h EECON2 0AAh EECON2 EECON1,WR INTCON,GIE EECON1,WREN STATUS,RP0 ;Comuta para banco 1 ;Desactiva interrupes ;Autoriza escrita ;Inicia processo de escrita

;Ordem de escrita ;Autoriza interrupes ;Inibe escrita Comuta para banco 0

A operao de escrita no ser iniciada se a sequncia mostrada acima no for executada (escrever 55h em EECON2, escrever AAh em EECON2, activar o bit WR). Dado que a sequncia de escrita no deve ser interrompida, as interrupes, se activas, devem ser desactivadas. Logo que a operao de escrita estiver terminada, o bit WR colocado a 0 pelo hardware e o bit EEIF colocado a 1 para sinalizar o fim da operao. Este bit, que pode ser utilizado pelo sistema de interrupes do C, deve ser colocado a 0 por software. Dado que o bit WREN (WRite ENable) funciona como uma segurana para o processo de escrita, prevenindo que, por um funcionamento deficiente, haja escritas espordicas na memria, deve ser colocado a zero logo a seguir a ter dado a ordem de escrita.

6 Atributos especficos do CPU

O que permite distinguir um C de outros processadores o conjunto de circuitos internos que lhe permitem lidar com aplicaes de tempo real. O PIC16F84 dispe de um conjunto de atributos que permitem maximizar a fiabilidade do sistema onde est inserido, minimizar os custos atravs da possibilidade de eliminao de componentes externos, e uma poupana de energia atravs de modos de funcionamento especficos. Estes atributos so: Seleco do oscilador Reset Power-on Reset (POR) Power-up Timer (PWRT) Oscilator Start-up Timer (OST) Interrupes Watchdog Timer (WDT) SLEEP Proteco do cdigo Identificao Programao srie no circuito (In-circuit serial programming)

19

6.1 Bits de configurao Os bits de configurao podem ser programados de maneira a seleccionar diferentes tipos de configurao do micro controlador. Estes bits esto mapeados na posio de memria 2007h e s podem ser acedidos durante a programao.

R = bit de leitura W = bit de escrita U = no implementado -n = valor de reset

u = no modificado

Bit 13:4

CP Bits de proteco do cdigo 1 = proteco de cdigo desligada 0 = memria de cdigo protegida (o cdigo no pode ser copiado) PWRTE Bit de activao do temporizador de power-up 1 = temporizador no activado 0 = temporizador activado WDTE Bit de activao do watchdog 1 = watchdog no activado 0 = watchdog activado FOSC1:FOSC0 Bits de seleco do tipo de oscilador 11 = oscilador RC 10 = oscilador HS 01 = oscilador XT 00 = oscilador LP Figura 18 Palavra de Configurao

Bit 3

Bit 2

Bit 1:0

6.2 Configuraes do oscilador O modo de funcionamento do oscilador do PIC16F84A pode ser programado em 4 modos diferentes, utilizando-se para isso os bits FOSC1 e FOSC0 da palavra de configurao. LP - Cristal low power XT Cristal HS Cristal high speed RC Malha RC (resistncia + condensador)

Caso seja utilizado um cristal, este deve ser ligado aos pinos OSC1 e OSC2 de acordo com a figura seguinte. Na tabela anexa figura indica-se o tipo de programao a efectuar de acordo com a frequncia de trabalho pretendida, dando-se ainda uma ideia dos valores a utilizar para os condensadores C1 e C2.

20

Figura 19 Oscilador com cristal

Nos modos de funcionamento XT, LP ou HS, o C aceita um sinal de relgio externo como se mostra na fig. 20.

Figura 20 Oscilador externo

Figura 21 Oscilador RC

Para aplicaes em que no so necessrias temporizaes precisas, a opo do oscilador controlado por uma malha RC a soluo mais barata, como se mostra na fig. 21. Neste caso, a frequncia de oscilao uma funo da tenso de alimentao, dos valores de R e C e da temperatura. Mais ainda, esta frequncia pode variar de um C para outro C devido a variaes de parmetros internos. 6.3 Reset O PIC16F84A permite vrios tipos de reset: Power-on reset (POR) Reset pelo pino MCLR durante o funcionamento normal do C Reset pelo pino MCLR quando o C se encontra em SLEEP Reset provocado pelo WDT durante o funcionamento normal do C Reset provocado pelo WDT quando o C se encontra em SLEEP

Os valores que so colocados nos diferentes registos internos aps estas operaes de reset podem ser consultados em tabelas que so apresentadas nas folhas de especificao (datasheet) do micro controlador.

21

6.4 Power-on Reset (POR) Sempre que o hardware interno do C detecta uma subida da tenso de alimentao, mais precisamente quando essa tenso se encontra entre 1.2V e 1.7V, gerado um impulso de RESET desde que o pino exterior MCLR esteja ligado directamente (ou atravs de uma resistncia) a VDD. Isto permite eliminar os componentes externos que implementam a malha RC normalmente necessria para provocar o reset do C quando ligada a alimentao. De notar que, para um correcto funcionamento deste sistema de reset, necessrio que o tempo de subida da tenso de alimentao seja inferior a um limite mnimo que consta das especificaes elctricas do C (cerca de 0.05V/ms). No caso em que o tempo de subida da tenso de alimentao no obedea s caractersticas definidas anteriormente, ser necessria a utilizao de uma malha RC externa para provocar o power-on reset do C, com se representa na figura ao lado. Para que a queda de tenso na resistncia R no seja superior a 0.2V, o valor de R deve ser inferior a 40K. O valor de R1, para proteco da entrada, dever estar entre 100 e 1K. O dodo D permite a descarga do condensador quando se verifica o power-down.

Figura 22 Malha de Reset exterior

6.5 Temporizador de Power-up (PWRT) O temporizador de Power-up permite uma temporizao fixa de cerca de 72 ms (TPWRT) a partir da situao de POR (ver figuras 23, 24, 25 e 26). Este temporizador, feito a partir de um oscilador RC interno, permite manter o C em situao de reset durante aquele tempo, permitindo assim que a tenso de alimentao atinja uma situao de estabilidade antes do C entrar em funcionamento. A utilizao deste temporizador pode ou no ser permitida atravs do bit PWRTE da palavra de configurao (ver pargrafo 6.1). 6.6 Temporizador para incio do oscilador (OST) Este temporizador permite um atraso na entrada em funcionamento do C de 1024 ciclos de relgio (TOST), a partir do final da temporizao do PWRT (ver figuras 23, 24, 25 e 26). Isto permite uma melhor estabilizao do oscilador interno depois de uma operao de entrada em funcionamento. Este temporizador s existe nos modos de funcionamento XT, LP e HS. Quando o tempo de subida da tenso de alimentao muito grande, possvel que no final das duas temporizaes, TPWRT + TOST, ainda no tenha sido conseguida a situao de estabilidade, isto , se se verificar ainda que VDD < VDDmin. Neste caso necessrio utilizar a malha externa RC para aumentar o tempo do power-on reset do C.

22

Figura 23 Sequncia de Reset (MCLR no ligado a VDD): caso 1

Figura 24 - Sequncia de Reset (MCLR no ligado a VDD): caso 2

Figura 25 - Sequncia de Reset (MCLR ligado a VDD): VDD com tempo de subida baixo

23

Quando VDD tem um tempo de subida alto, possvel que TPWRT + TOST terminem antes de VDD ter atinjido o seu valor final. Neste exemplo, o reset ser correcto se V1 VDDmin.

Figura 26 - Sequncia de Reset (MCLR ligado a VDD): VDD com tempo de subida alto

6.7 Bits de estado de Power-down (TO/PD) A tabela seguinte mostra os valores que podero ser encontrados nos bits TO e PD do registo STATUS depois de uma operao de Reset ou de retoma de funcionamento depois de uma operao de SLEEP. TO PD Condio 1 1 Power-on Reset ou reset por MCLR durante o funcionamento normal 0 1 Reset provocado pelo WDT durante funcionamento normal 1 0 Reset por MCLR durante SLEEP ou sada de SLEEP provocada por interrupo 0 0 Sada de SLEEP por WDT Tabela 4 Bits de estado e seu significado

6.8 Interrupes O PIC16F84A dispe de um nico nvel de interrupo com 4 fontes de interrupo: Interrupo externa atravs do pino RB0/INT Interrupo provocada pelo overflow do TMR0 Interrupo provocada pela mudana de estado do PORTB (RB7:RB4) Interrupo provocada pelo fim da operao de escrita na E2PROM de dados

O registo de controlo das interrupes (INTCON) contm as diferentes flags de pedido de interrupo e os bits que permitem activar ou desactivar individualmente ou na globalidade as diferentes interrupes. A lgica que permite o desencadeamento do processo de interrupo est representada na figura seguinte.

24

Figure 27 Lgica associada s interrupes Na situao de reset, todos os bits correspondentes autorizao individual ou global das interrupes encontram-se desactivados (T0IE = INTE = RBIE = EEIE = GIE = 0). A rotina de servio de qualquer interrupo deve terminar sempre com a instruo RETFIE (RETurn From Interrupt Enable) que, alm de fazer o sistema retornar ao programa no local onde se verificou a interrupo, coloca tambm GIE = 1 permitindo de novo o acesso dos perifricos s interrupes. Quando o C responde a um pedido de interrupo, o bit GIE colocado em 0 para no permitir mais nenhuma interrupo, o endereo de retorno colocado na stack e o PC carregado com o valor 0004h que o vector de interrupo para este C. Ser a partir desta posio da memria de programa que dever ser escrita a rotina de servio da interrupo. Nesta rotina de servio, caso haja mais do que uma interrupo autorizada, ser necessrio ler as flags de pedido de interrupo para se poder determinar qual o perifrico que requisitou os servios do sistema de interrupes. As flags de interrupo activadas devem ser colocadas em 0 por software de maneira a que, quando o C sair da rotina de servio, no seja interrompido novamente. Para as interrupes externas, o tempo de latncia ser de 3 a 4 ciclos de instruo, dependendo do exacto momento em que foi efectuado o pedido. De notar ainda que as diferentes flags de pedido de interrupo podem ser activadas independentemente de as respectivas interrupes estarem ou no autorizadas ou do estado do bit GIE. 6.8.1 Interrupo INT A interrupo externa INT activada por flanco: ascendente se INTEDG = 1 (OPTIN_REG.6) descendente se INTEDG = 0

Sempre que um flanco vlido aparece no pino RB0/INT a flag INTF activada. Esta flag deve ser desactivada por software. A autorizao desta interrupo feita atravs do bit INTE (INTCON.4).

25

A interrupo INT pode acordar o C do estado de SLEEP se a interrupo estiver autorizada. O estado do bit GIE decide qual o procedimento a ter depois de acordar (ver 6.11). 6.8.2 Interrupo do TMR0 O overflow do TMR0 (FFh 00h) coloca em 1 a flag T0IF (INTCON.2). A Autorizao desta interrupo feita custa do bit T0IE (INTCON.5). 6.8.3 Interrupo do PORTB A mudana de estado em qualquer um dos bits RB7:4 coloca em 1 a flag RBIF (INTCON.0). A autorizao da interrupo pode ser feita atravs do bit RBIE (INTCON.3). 6.8.4 Interrupo da EEPROM de Dados Quando a EEPROM termina o processo interno de escrita, activa a flag EEIF (EECON1.4). A autorizao da interrupo feita atravs do bit EEIE (INTCON.6). 6.9 Temporizador Watchdog (WDT) O temporizador Watchdog constitudo por um oscilador interno RC, no necessitando de quaisquer outros componentes externos. Este oscilador totalmente independente do oscilador do C. Isto quer dizer que, mesmo que o oscilador principal no funcione (por exemplo no caso do C se encontrar no estado de SLEEP), o WDT continuar em funcionamento. O diagrama de blocos deste perifrico pode ser visto na figura seguinte.

Figura 28 Diagrama de blocos do sistema WatchDog

26

Durante o funcionamento normal, um timeout deste temporizador provoca um RESET do C. Se o C se encontrar em SLEEP, o timeout do WDT provoca o acordar do C, continuando o programa na instruo seguinte instruo de SLEEP. A activao / desactivao do WDT feita atravs do bit WDTE da palavra de configurao. 6.9.1 Perodo do WDT Este temporizador tem um perodo nominal de 18 ms (sem prescaler). Este perodo pode sofrer variaes pois est dependente de alguns parmetros como a tenso de alimentao, a temperatura e outros parmetros inerentes ao prprio C. Se forem necessrios perodos superiores, pode ser utilizado o prescaler com uma taxa de diviso de 1 at 128. Desta maneira podemos conseguir perodos de timeout at cerca de 2.3 segundos. As instrues CLRWDT e SLEEP fazem o reset do tempo de watchdog e do postscaler se este estiver atribudo ao WDT. 6.9.2 Uma utilizao possvel para o WDT Um dos problemas que se pode por no funcionamento de um C a alterao sbita do PC devida a diversos tipos de fenmenos, como por exemplo rudo elctrico. Esta alterao no controlada por programa faz com que, a partir desse momento, as tarefas desempenhadas pelo C nada tenham a ver com o programa que foi desenhado pelo utilizador. S uma operao de RESET poder repor o normal funcionamento do sistema. A utilizao do WDT pode remediar este tipo de situaes, desde que se encontre activado. O programador dever espalhar criteriosamente pelo programa instrues CLRWDT de maneira a que nunca se verifique o timeout do temporizador em qualquer situao de funcionamento normal. Logo que se verifique uma falha, provvel que essas instrues no sejam executadas provocando assim um timeout do WDT com o consecutivo RESET do C. 6.10 Modo de funcionamento Power-down (SLEEP) O PIC16F84 pode ser colocado em power-down (SLEEP) podendo mais tarde ser de novo colocado em funcionamento normal (Wake-up). 6.10.1 SLEEP A instruo SLEEP utilizada para fazer com que o C entre em power-down. Quando isto acontece, feito o reset do WDT (se estiver activo), os bits PD e TO so colocados respectivamente em 0 e 1 e desactivado o oscilador interno. Os portos de I/O mantm o estado que tinham antes da execuo da instruo SLEEP. Para que o consumo de energia seja minimizado, todos os pinos I/O devem estar a VSS ou a VDD, devendo-se garantir ainda que nenhum circuito exterior esteja a receber corrente do C. Os pinos programados como alta impedncia (entrada) devem ter pull-up ou pull-down exterior para se evitarem flutuaes na entrada.

27

6.10.2 Wake-up O C pode sair do modo de SLEEP atravs de um dos acontecimentos seguintes: Reset exterior por activao do pino MCLR Timeout do WDT se estiver activo Interrupes RB0/INT, RB7:4 ou fim de escrita na EEPROM O TMR0 no pode gerar interrupo pois o seu funcionamento depende do oscilador interno que, em power-down, se encontra parado. No primeiro caso, reset por MCLR, provoca o RESET do C. Os dois casos restantes so considerados como uma continuao da execuo do programa. Os bits TO e PD permitem determinar a causa do reset do C. Enquanto est a ser executada a instruo SLEEP, a prxima instruo est a ser pesquisada (PC + 1). Para que o C acorde a partir de uma interrupo necessrio que esta esteja autorizada. A sada de sleep acontece independentemente do estado do bit GIE. Se GIE estiver a 0, o programa continua na instruo seguinte ao SLEEP. Se GIE = 1 ento o C executa a instruo seguinte ao SLEEP e salta para o vector de interrupo (0004h) onde se encontra a rotina de servio da interrupo. Caso no haja interesse na instruo seguinte ao SLEEP, essa instruo poder ser um NOP. Na figura seguinte mostra-se o diagrama temporal do processo descrito.

Figura 29 Wake-up por interrupo

6.11 Proteco de cdigo Quando se faz a programao do C, possvel programar os bits de proteco de cdigo. Se isto acontecer no ser mais possvel fazer a leitura do cdigo gravado. S uma nova gravao poder desactivar a proteco. Caso se opte por cdigo desprotegido ento em qualquer altura esse cdigo pode ser lido quer para comparao quer para efectuar cpias do C. 6.12 Identificador As posies de memria 2000h 2004h so usadas para guardar um identificador do produto (n de srie, checksum, etc.). Estas posies de memria s podem ser acedidas durante o processo de gravao.

28

6.13 Programao srie in-circuit Estes Cs podem ser programados na placa onde esto inseridos, atravs de uma comunicao srie. Isto permite que as placas sejam totalmente montadas (incluindo o prprio C) sendo posteriormente efectuada a gravao do cdigo no C. Este processo utiliza unicamente 2 linhas para sinal de relgio e para dados e mais trs linhas para a tenso de alimentao e para a tenso de programao. A Microchip fornece o protocolo e todas as especificaes tcnicas necessrias para este tipo de programao.

7 Tabela de Instrues

Você também pode gostar

- Controle de Vazão de Um ChuveiroDocumento54 páginasControle de Vazão de Um ChuveiroAlvaro AlvesAinda não há avaliações

- Dicionario TecnicoDocumento33 páginasDicionario TecnicoClaudio CorreaAinda não há avaliações

- Instrução Suplementar - IsDocumento47 páginasInstrução Suplementar - IsCézar AngelitonAinda não há avaliações

- Controle de Vazão de Um ChuveiroDocumento54 páginasControle de Vazão de Um ChuveiroAlvaro AlvesAinda não há avaliações

- Caixa CDLivre 4.0Documento1 páginaCaixa CDLivre 4.0Cézar AngelitonAinda não há avaliações

- Regula Men To de Corridas de ObstáculosDocumento10 páginasRegula Men To de Corridas de ObstáculosCézar AngelitonAinda não há avaliações

- Controle de Vazão de Um ChuveiroDocumento54 páginasControle de Vazão de Um ChuveiroAlvaro AlvesAinda não há avaliações

- Controle de Vazão de Um ChuveiroDocumento54 páginasControle de Vazão de Um ChuveiroAlvaro AlvesAinda não há avaliações

- Manual FaroldeBuscaDocumento11 páginasManual FaroldeBuscapolicetotalAinda não há avaliações

- Configurando o Mach3 emDocumento4 páginasConfigurando o Mach3 emCézar AngelitonAinda não há avaliações

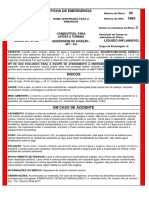

- Ficha de EmergênciaDocumento1 páginaFicha de EmergênciaCézar AngelitonAinda não há avaliações

- Micro Control Ad or PicDocumento30 páginasMicro Control Ad or PicCézar AngelitonAinda não há avaliações

- Acidente Vascular CerebralDocumento9 páginasAcidente Vascular CerebralHeli LimaAinda não há avaliações

- Construa Sua Fonte Chaveada Uns 13 PDFDocumento27 páginasConstrua Sua Fonte Chaveada Uns 13 PDFFabiane Ferreira QueirozAinda não há avaliações

- Burlando o Tubo Defeituoso Da Philips (PT)Documento2 páginasBurlando o Tubo Defeituoso Da Philips (PT)Cézar AngelitonAinda não há avaliações

- Terapia de casais e a sombra na contemporaneidadeDocumento28 páginasTerapia de casais e a sombra na contemporaneidadeJoãoCarlosMajorAinda não há avaliações

- Acidente Vascular CerebralDocumento16 páginasAcidente Vascular CerebralAlexandre Cardoso KatesAinda não há avaliações

- A perseverança de CalebeDocumento2 páginasA perseverança de CalebeWaldson Junior100% (2)

- Anne Krauze - Um Amor de CEO PDFDocumento567 páginasAnne Krauze - Um Amor de CEO PDFKarla Vitória Rodrigues Carvalho92% (26)

- Correção Enunciado Exercício 4263 PDFDocumento2 páginasCorreção Enunciado Exercício 4263 PDFAna MacedoAinda não há avaliações

- O conto de Vergílio Ferreira entre prosa e poesiaDocumento5 páginasO conto de Vergílio Ferreira entre prosa e poesiaHerick Martins SchaiblichAinda não há avaliações

- Sede Meus ImitadoresDocumento14 páginasSede Meus Imitadoresmaf2612Ainda não há avaliações

- Epistemologia e OntologiaDocumento40 páginasEpistemologia e OntologiaDILON SILVINIOAinda não há avaliações

- Métodos de Ensino Nos Jogos EsportivosDocumento10 páginasMétodos de Ensino Nos Jogos EsportivosPaulo TsunetaAinda não há avaliações

- Balanceamento de reações químicas pelo método das tentativasDocumento2 páginasBalanceamento de reações químicas pelo método das tentativasVictor ZanchettAinda não há avaliações

- Modulo 05Documento587 páginasModulo 05Luis HenriqueAinda não há avaliações

- Plano de Aula Arte 3º Ano - (Roteiro Amanda e Lays)Documento3 páginasPlano de Aula Arte 3º Ano - (Roteiro Amanda e Lays)Amanda CoutoAinda não há avaliações

- Jogos, Brinquedos e BrincadeirasDocumento2 páginasJogos, Brinquedos e BrincadeirasAndré CamposAinda não há avaliações

- Estratégias para lidar com comportamentos desafiadores em casos de Transtorno de Personalidade BorderlineDocumento10 páginasEstratégias para lidar com comportamentos desafiadores em casos de Transtorno de Personalidade BorderlinekzuzaAinda não há avaliações

- Resolução Prova UFSM 2011Documento20 páginasResolução Prova UFSM 2011joferr100% (1)

- Conto - Antonio Mota - Pedro Alecrim - Guiao de LeituraDocumento20 páginasConto - Antonio Mota - Pedro Alecrim - Guiao de Leituranoeminha_2000Ainda não há avaliações

- Revisão de LiteraturaDocumento14 páginasRevisão de LiteraturaChristiane MendesAinda não há avaliações

- 01 - A Chamada de MoisesDocumento7 páginas01 - A Chamada de MoisesSilvania MirandaAinda não há avaliações

- Suplementos Alimentares - 7 - EdicaoDocumento123 páginasSuplementos Alimentares - 7 - EdicaoAdriana SilvestreAinda não há avaliações

- Cálculo Numérico Com PythonDocumento369 páginasCálculo Numérico Com PythonLuan Moreira0% (1)

- Decisão Mandado de SegurançaDocumento11 páginasDecisão Mandado de SegurançaMetropolesAinda não há avaliações

- Sinais Vitais e Exame FísicoDocumento34 páginasSinais Vitais e Exame Físicolua_susan100% (2)

- Biomecânica para Fisioterapeutas - 69pDocumento69 páginasBiomecânica para Fisioterapeutas - 69pivanfersantosAinda não há avaliações

- Negociação e Gestão de ConflitosDocumento178 páginasNegociação e Gestão de ConflitosEllenAinda não há avaliações

- Calendário de Vacinas para Crianças Com Síndrome de Down Do Estado de São PauloDocumento3 páginasCalendário de Vacinas para Crianças Com Síndrome de Down Do Estado de São PauloFernando AlvesAinda não há avaliações

- Histórico das Pesquisas Paleontológicas na Bacia do AraripeDocumento20 páginasHistórico das Pesquisas Paleontológicas na Bacia do AraripelschavesAinda não há avaliações

- Livro de Richard FeynmanDocumento147 páginasLivro de Richard FeynmanJanice CollinsAinda não há avaliações

- Noções de Manipulação Vertebral e Mobilização ArticularDocumento32 páginasNoções de Manipulação Vertebral e Mobilização ArticularIgor Sombra Pacheco0% (1)

- Síndrome de Burnout em profissionais de saúde: fatores e prevençãoDocumento18 páginasSíndrome de Burnout em profissionais de saúde: fatores e prevençãohenriqueAinda não há avaliações

- O Repórter de Um Tempo Mau: Marginalidade e Espacialidade em Plinio MarcosDocumento16 páginasO Repórter de Um Tempo Mau: Marginalidade e Espacialidade em Plinio MarcosRenan Ramires de AzevedoAinda não há avaliações