Escolar Documentos

Profissional Documentos

Cultura Documentos

Nvidia

Enviado por

abhijeet_chandratreDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Nvidia

Enviado por

abhijeet_chandratreDireitos autorais:

Formatos disponíveis

Test questions of nVidia: 1. Some question on calculating the depth of FIFO in an interrupt based microcontroller based system.

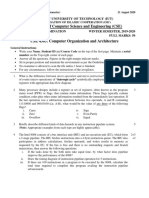

The question was too long to read and had to be skipped initially. 2. Write a C program to: i). find the last instance of a character in a string. ii). determine how many bits are set in a given integer 3. Question on setup/hold time. A very good question. The circuit had two f/fs with a programmable tap (providing programmable delay in terms of n) in between the clock line of the two f/f. two conditions best case and worst case timing details (tclk-q, tsetup, thold and programmable delaymin )were given and accordingly the range of values of the n was to be calculated. Part ii) dealt with the jitter in the clock. Was asked to determine how the max clock frequency would change. 4. Write a pseudo-code to determine the union of two sets A and B. all the necessary functions were defined by them. One of easiest questions of the paper. 5. A problem of finding tag, offset index of cache. I did not try to read this question as I had no idea of cache memory then. 6. A pmos circuit interms of graph was given. Had to find the nmos part of it to make it a complete cmos circuit. Part ii) find the equation implemented by the cmos circuit. 7. Two blank nand gates (ie., no i/p were given) and only one i/p was present. Find two different implementations of an inverter using a NAND gate. Part ii). Which implementation was faster and why? Probably the easiest question of the lot. 8. A bridge fault was present between a 2i/p AND gate and OR gate (with all four different i/ps being unique). Find the number of i/p patterns required to determine the presence of a fault. Part ii). What is the number of patterns required now if the above gates are replaced with 3-i/p gates. 9. A 8bit vector is given to the 1s counter which counts the number of 1s. it is then given to a comparator which compares and sets a dbi indicator to high if the count is greater than 4. However this is a small mistake and dbi should be high if the count is greater than or equal to 4. Design the additional circuit that should be connected with the existing one so as to correct this mistake using minimum number of 2-i/p gates. Interview questions in nVidia: 1. There is a clock and a i/p. Design a circuit such that it filters out a single cycle positive and negative (if any) pulse and passes non-single cycle pulses with a one-clock delay. 2. There is a Unit A. i/p 32 bits and o/p 8 bits. Write operations happen on the i/p and Read operations happen on the o/p. write operations happen at 40MHz clock frequency and Read operations happen at 160 MHz clock frequency. Determine the size of memory to be allocated in Unit A such that no overflow occurs. Part ii) Change the Write clock frequency to 160Mhz. Hence find the same. 3. What is setup/hold time? Explain. Why have you not considered hold time while calculating the max clock frequency? Is hold time not important??? The test paper question on setup hold time was again asked with different parameter values and asked question on hold time. 4. What are the different aspects of Power dissipation in a cmos. What is dynamic power dissipation? Assume that I have a laptop running on a battery (charging off). What measures should the system take so as to have minimum power consumption? What is static power dissipation? How to minimize it? 5. Design a circuit that divides the clock frequency by 3. Some non-technical questions: where did you do your engineering from? What are you doing in BITS Goa if you are from BITS Hyd? Where are you from? Are you not interested in software as you have not solved programming questions well (except for the pseudo code question). There were no HR questions. HR lady was sitting with laptop and entering details as well as noting the body language of the interviewed person. --Abhijeet Chandratre M.E. Microelectronics BITS Pilani Hyderabad campus

Você também pode gostar

- Bebop to the Boolean Boogie: An Unconventional Guide to ElectronicsNo EverandBebop to the Boolean Boogie: An Unconventional Guide to ElectronicsNota: 4 de 5 estrelas4/5 (3)

- CSC 204 - Final Study GuideDocumento12 páginasCSC 204 - Final Study GuideFVCproductionsAinda não há avaliações

- NVIDIA QuestionsDocumento5 páginasNVIDIA QuestionsJibin P John0% (1)

- IntelDocumento5 páginasIntelrAM67% (3)

- Digital Design Interview Questions & AnswersDocumento5 páginasDigital Design Interview Questions & AnswersSahil KhanAinda não há avaliações

- Questions 3Documento28 páginasQuestions 3Anbarasan AnbuAinda não há avaliações

- Electronic Engineer Interview QuestionsDocumento4 páginasElectronic Engineer Interview QuestionsAbhilashPadmanabhanAinda não há avaliações

- QnsDocumento3 páginasQnsAnonymous gZjDZkAinda não há avaliações

- Roll#: - Name: - Section: - Due Date: 25 InstructorsDocumento8 páginasRoll#: - Name: - Section: - Due Date: 25 InstructorsShiza SiddiqueAinda não há avaliações

- What Are The Various Registers in 8085Documento9 páginasWhat Are The Various Registers in 8085kunalsekhri123100% (1)

- Ovn MainDocumento54 páginasOvn MainAvenir BajraktariAinda não há avaliações

- Assignment Nov 19Documento7 páginasAssignment Nov 19CSE AAinda não há avaliações

- Assignment 1Documento4 páginasAssignment 1akttripathiAinda não há avaliações

- Digital Principle and System Design 2marks and 12 MarksDocumento43 páginasDigital Principle and System Design 2marks and 12 MarksTamil Mani100% (1)

- 7 Intel Paper - AlDocumento11 páginas7 Intel Paper - Alks25021995Ainda não há avaliações

- Ilovepdf MergedDocumento510 páginasIlovepdf MergedChristopher crAinda não há avaliações

- Numerical ProblemsDocumento3 páginasNumerical Problemsaman rajAinda não há avaliações

- Su 2011 Final SolDocumento19 páginasSu 2011 Final SolmissionchocolateAinda não há avaliações

- Worksheet 4-Input+OutputDocumento5 páginasWorksheet 4-Input+OutputShiza SiddiqueAinda não há avaliações

- Placement PapersDocumento4 páginasPlacement PapersDivyam GargAinda não há avaliações

- Sample Final Exam EECS388 - Fall 2020Documento19 páginasSample Final Exam EECS388 - Fall 2020Jeren ChenAinda não há avaliações

- BFE Final Organization Fall 2014 AnswerDocumento8 páginasBFE Final Organization Fall 2014 AnswerArpan DesaiAinda não há avaliações

- DGD 8Documento2 páginasDGD 8Dolores MakaruinaAinda não há avaliações

- Prime TimeDocumento2 páginasPrime Timedarshilshah88Ainda não há avaliações

- Sample Paper Spring 08 FinalDocumento23 páginasSample Paper Spring 08 FinalManish ThakraniAinda não há avaliações

- Ecen 248 Lab 9 ReportDocumento5 páginasEcen 248 Lab 9 ReportRebecca Sontheimer100% (1)

- 06 CS81 ACADec 10Documento2 páginas06 CS81 ACADec 10Mohammed YasinAinda não há avaliações

- What Are The Differences Between SIMULATION and SYNTHESISDocumento12 páginasWhat Are The Differences Between SIMULATION and SYNTHESISiyanduraiAinda não há avaliações

- DrillsDocumento5 páginasDrillsalomarianas52Ainda não há avaliações

- Puzzlesand QuestionDocumento2 páginasPuzzlesand QuestionmohitAinda não há avaliações

- EE380 Spring 2004 Sample Final Exam: Direct Connection (Aka, Fully Connected) Networ Ks Offer Ver y Good Latency andDocumento7 páginasEE380 Spring 2004 Sample Final Exam: Direct Connection (Aka, Fully Connected) Networ Ks Offer Ver y Good Latency andJaxzen42Ainda não há avaliações

- Subject: Digital VLSI Design II - BackendDocumento3 páginasSubject: Digital VLSI Design II - Backendకిరణ్ కుమార్ పగడాలAinda não há avaliações

- Nvidia Placement PaperDocumento4 páginasNvidia Placement PaperSaurabh Verma100% (2)

- Qualcomm QnsDocumento9 páginasQualcomm QnsPrincy MurugesanAinda não há avaliações

- Interview QnsDocumento5 páginasInterview Qnssaikirannani277Ainda não há avaliações

- Attempt All of The Following QuestionsDocumento5 páginasAttempt All of The Following Questionssoli0snakeAinda não há avaliações

- SIT202 Assignment1Documento3 páginasSIT202 Assignment1Ramana MurugaAinda não há avaliações

- UntitledDocumento10 páginasUntitledAnanya KumariAinda não há avaliações

- Practice Final ExamDocumento3 páginasPractice Final ExamThành ThảoAinda não há avaliações

- ECE 127 Homework 1 Problem 1: Moore's LawDocumento2 páginasECE 127 Homework 1 Problem 1: Moore's LawRobin ScherbatskyAinda não há avaliações

- Tutorial Module 4Documento9 páginasTutorial Module 4Neupane Er KrishnaAinda não há avaliações

- Itr3g1 - CoaDocumento5 páginasItr3g1 - Coaanish231003Ainda não há avaliações

- Wa0004.Documento11 páginasWa0004.Reeshma.GogulaAinda não há avaliações

- Computer Organization Jan 2010Documento2 páginasComputer Organization Jan 2010Prasad C MAinda não há avaliações

- p2301 PDFDocumento1 páginap2301 PDFGopinath BalamuruganAinda não há avaliações

- Digital Principels and System DesignDocumento53 páginasDigital Principels and System Designnofeelingrahul100% (1)

- Arid Agriculture University, RawalpindiDocumento7 páginasArid Agriculture University, RawalpindiRao HarisAinda não há avaliações

- CSE 380: Introduction To Operating Systems: Final Exam 17 December 2003Documento6 páginasCSE 380: Introduction To Operating Systems: Final Exam 17 December 2003Yosef GalavizAinda não há avaliações

- AMP Lab ManualDocumento22 páginasAMP Lab ManualSatish PawarAinda não há avaliações

- Assignment Two AshishDocumento12 páginasAssignment Two Ashishapi-3710084Ainda não há avaliações

- DSDV 18ec644Documento5 páginasDSDV 18ec644Abhishek nAinda não há avaliações

- System Hardware SOEN228Documento5 páginasSystem Hardware SOEN228Hichem SehabiAinda não há avaliações

- Main Porject Phase LL ContentDocumento44 páginasMain Porject Phase LL ContentRumana NajeerullaahAinda não há avaliações

- Unit I-Basic Structure of A Computer: SystemDocumento64 páginasUnit I-Basic Structure of A Computer: SystemPavithra JanarthananAinda não há avaliações

- PR301 MF Sample Questions - 1 SET CicsDocumento12 páginasPR301 MF Sample Questions - 1 SET CicsPinank ParikhAinda não há avaliações

- Department of Computer Science and Engineering (CSE) : Islamic University of Technology (Iut)Documento3 páginasDepartment of Computer Science and Engineering (CSE) : Islamic University of Technology (Iut)Manus HumanAinda não há avaliações

- CSC 101 - Quiz 1Documento3 páginasCSC 101 - Quiz 1Shehu AbdullahiAinda não há avaliações

- C QuestionsDocumento19 páginasC Questionsramya53919Ainda não há avaliações

- C QuestionsDocumento19 páginasC Questionsramya53919Ainda não há avaliações

- MTR - (Masti Torrents Releasers)Documento1 páginaMTR - (Masti Torrents Releasers)Ritika ParnamiAinda não há avaliações

- BrainBashers Brain Teasers and Puzzles2Documento4 páginasBrainBashers Brain Teasers and Puzzles2Deepanshu RastogiAinda não há avaliações

- SfmssDocumento1 páginaSfmssDeepanshu RastogiAinda não há avaliações