Escolar Documentos

Profissional Documentos

Cultura Documentos

Lab 5

Enviado por

Harish RamasubramanianDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Lab 5

Enviado por

Harish RamasubramanianDireitos autorais:

Formatos disponíveis

EXPERIMENT #5 Multiplexers in Combinational logic design

Objective:

The goal of this experiment is to introduce multiplexers in the implementation of combinational logic design. In addition, procedural programming in VERILOG will be introduced to the student.

Discussion:

Multiplexer or Selector: The basic function of the circuit is to select one of several inputs to connect to a single output line. Typical multiplexers (MUXs) come in 2:1, 4:1, 8:1 and 16:1. A MUX is composed of n selections bits that maps 2n inputs to a single output. A TTL series 8:1 MUX is 74151, which is an eight to one (8:1) multiplexer. Examine the spec sheet in Appendix A for 74151. The data select lines are S 2, S1, and S0 (often called the control / selection lines). Each of the 8 possible combinations of S 2, S1, and S0 selects one of the 8 AND gates which maps one of 8 possible inputs to the output Y. The output of the selected AND gate will be the same as the input signal on the corresponding data input line. All other AND gate outputs will be 0. The output of the OR function will be the same as the output of the selected AND gate. In this way, the input data associated with a selected line is routed to the output signal line. This operation is called Multiplexing. The 74151 has another input called the Enable Input (). The bar on the symbol specifies that the Enable input is active low. This means the output is enabled when the input signal is zero. Otherwise, the output is set to one when the recommended pull-up resistor is used. The input allows two cascaded 8:1 multiplexers to be combined together to form a single 16:1 multiplexer. Although multiplexers are primarily used for switching data paths they can also be used to realize general logic functions. Function: F(w,x,y,z) = (To be given out by the laboratory instructor.)

Pre-Laboratory Assignment:

1. Given the Function F(w, x, y, z) generate this functions truth table. Next, determine the min-terms (the combination of w, x, y, and z for which the output function F is one). These combinations determine the input locations of the multiplexer which are set to one. The combinations, for which the output is zero, form the input locations of the multiplexer which are set to zero.

5- 1

2. Draw a logic schematic in your notebook using two 8:1 multiplexers. Consider the enable input as active high (Xilinx has the Enable input as active high - E). Three of the input variables in the given function F(w,x,y,z) are used as control inputs to the selection / control inputs of each of the 8:1 multiplexers and the fourth input variable is used to select between the two 8:1 multiplexers using the E input. An OR gate is used to OR the two 8:1 multiplexer outputs. 3. Write the test plan of this experiment on how it should be tested. 4. Write the Design Specification Plan for this experiment 5. Read this experiment carefully to become familiar with the experiment.

Procedure:

1. Using Xilinxs ISE and its schematic capture tool, design a 16:1 multiplexer using two 8:1 multiplexers (symbol M8_1E is located in the MUX category). Three of the input variables in the given function F(w,x,y,z) are used as control inputs to the selection / control inputs of each of the 8:1 multiplexers and the fourth input variable is used to select between the two 8:1 multiplexers using the E input (active high). An OR gate is used to OR the two 8:1 multiplexer outputs. 2. Define a four bit input BUS S and a single output O. This four bit bus should be connected to SW0, SW1, SW2, and SW3 and the O output should be linked to LED7 on the BASYS board. 3. The sixteen inputs should be hard coded as 0 = ground and 1 = VCC using the gnd and vcc from the Add Symbol Tool next to the Add Instance tool. There should only be four bits for input S and one bit for output O for this experiment. 4. Use the count up option in the test bench waveform tool to vary the select input S from 0000 binary to 1111 binary. Download the implemented design of Steps 1-3 to the FPGA using the EXPORT program. Create a new truth table to verify that the design has implemented correctly. 5. At this point, steps 1 to 4 need to be repeated but this time using the VERILOG programming language. For the previous experiments 1 to 4, the VERILOG modules created thus far have been combinational logic designs. Another area of VERILOG programming is procedural programming, wherein if statement, for loops, and case statements can be used. For this experiment, a procedural program will be written that implements a 16:1 multiplexer. All procedural programs begin with the always function: always @( argument) 5- 2

The argument can be posedge (for positive edge) or negedge (for negative edge) of a signal or just the signal name, as shown below: always @( posedge clock) always @( S) In the first line, the procedure is executed every positive edge of the clock and in the second case whenever S changes. The or and the and operators can be used to combine signals together. The or and the and operators are spelled out here as shown below: always @(S or Q) always @( S and Q) Unlike C programming, which uses open and closed brackets to define a function, VERILOG uses the begin and the end statement: always @( posedge clock) begin insert code here end All procedural code must have on the left side of an equation, variables that are defined as register. The FPGA needs a method to store these values between executions of the code depending on the always command: reg A; reg [3:0] B; wire I, T; assign I = 1; assign T = 0; always @( posedge clock) begin B[0] = T; B[1] <= I; A <= 0; end This short piece of code defines the variables I and T as wires and then assigns them the value of 1 and 0 respectively. This code also defines the variables A as a 1 bit register (1 flip-flop) and B as a 4 bit register. The reader may notice two types of assignment declarations in the program. First, only combinational logic uses the assign operator. The second set of operators = and <= are used within the always

5- 3

procedure. The equals (=) only assignment is called a blocking operation. No other parts of the always procedure is executed until this operation is executed. All other operations are blocked until this line of code is executed, just like a regular C program. The greater than equals assignment (<=) implies parallelism. All <= assignments are executed in parallel. For the above code, B[0] = T is executed first followed by B[1] <= T and A <= 0 executed at the same time. Unlike C programming, timing is important here. For example, consider a wire A is assigned a value of 5 (A = 5), a register C is assigned a value of 10 (C=10) and a register B is defined. Consider the execution of the following lines: C = A; B = C; After execution of the above code, C = 5 and then B = 5. Each line of code is executed one line at a time. Now consider the code with A, B, and C defined as shown below: C <= A; B <= C; Now since both the lines of code are executed in parallel, C = 5 and B = 10. If conditional statements, for loops and case statements can be used within a procedural block. The code below shows an example of using a case statement for a two-bit input B: reg A; wire [1:0] B; always @( posedge clock) begin case (B) 2'b00: A = 0; 2'b01: A = 1; 2'b10: A = 1; 2'b11: A = 0; endcase end After studying the above VERILOG programming examples, write a VERILOG programming module that implements a 16:1 multiplexer using procedural programming. Assign a 4-bit bus S for the select lines of the multiplexer and a signal O for the output (O needs to be reg type). For the sixteen inputs, hardcode the function F(w, x, y, z) using the assign operator. Simulate this VERILOG 16:1 multiplexer and compare the simulation output to the truth table developed for the

5- 4

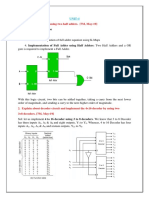

experiment. Use the count up option in the test bench waveform tool to vary the select input S from 0000 binary to 1111 binary. 6. At this point, the VERILOG version of the multiplexer should be implemented assigning S[0] to S[3] to SW0 - SW3 and the output O to LED0. NOTE: An interesting thing may happen depending on the set of 16 inputs to multiplexer. The figure below shows the pace program for one set of 16 inputs to multiplexer. The output O appears along with the bus S bits 0 and 3. Bits 1 and 2 of bus S are missing. What happened is that the VERILOG compiler optimized the design by evaluating the 16 inputs to the multiplexer for the 4 bits of selection / control to the multiplexer and determined that S[1] and S[2] are do not cares terms X. If the 16 inputs to the multiplexer change, the Select bus bits used in the implementation will change.

The real question is that the user designed a 16:1 multiplexer, what did the compiler implement since inputs S[1] and S[2] were ignored? This can be found by looking under View Technology Schematic under the Synthesize-XST in the Processes window. Double click this option and the following window appears showing the top level schematic representation. Make sure the design has been synthesized and implemented first. This schematic shows the top-level diagram of what was implemented. It is a good check to make sure that all inputs and outputs are defined as expected. The schematic shows an input bus S of four bits and an output O. Double click the schematic to obtain the next level of detail as shown in the next Figure. Both the Processes and the Sources windows were closed to make it easier to see the detailed schematic. This schematic shows what is actually implemented within the FPGA. The FPGA selected to use a 4 word by 1 bit lookup table (LUT) to implement the 5- 5

multiplexer and used only two bits S[3] and S[0] to address this lookup table (more on using a memory device to perform logic functions is discussed later in this manual). The output from the lookup table is then fed to a buffer and to the output O. Bits S[1] and S[2] are not used in this design. The actual bus bits used can be determined by placing the mouse cursor over the bus tap and reading which bit is used as displayed in the highlight popup window.

5- 6

Using only the available bits for the select input S as defined by the PACE program assign these bits to SW0 - SW3 appropriately and assign the output O to LED0. For example, if S[2] is missing in the input and output list in the PACE program, leave SW2 blank. Next re-build the VERILOG 16:1 multiplexer so that the synthesis and implementation is up to date. Finally, generate the programming files to be downloaded to the BASYS board. 7. Download the *.BIT file to the BASYS board and verify that the VERLOG version of the 16:1 multiplexer works as designed.

Questions:

(To be incorporated within the Conclusion section of your lab report) 1. Investigate the function of a lookup table and describe how one works. 2. Consider a 16 word by 1 bit lookup table. Give the values stored in each location 0000 binary (word zero) to 1111 binary (word fifteen) for the function F(w, x, y, z). The truth table that was generated in the pre-laboratory will help here. 3. Have you met all the requirements of this lab (Design Specification Plan)? 4. How should your design be tested (Test Plan)?

5- 7

Você também pode gostar

- Cs Important Questions by UjjwalDocumento19 páginasCs Important Questions by Ujjwalkumawatujjwal18Ainda não há avaliações

- STLD Lab Manual R19Documento40 páginasSTLD Lab Manual R19RockRahil100% (3)

- University of Essex: School of Computer Science andDocumento6 páginasUniversity of Essex: School of Computer Science andVlad SimizeanuAinda não há avaliações

- Lab Report 4Documento10 páginasLab Report 4abdulbabulAinda não há avaliações

- Design A Full Adder by Using Two Half Adders. (7M, May-19)Documento10 páginasDesign A Full Adder by Using Two Half Adders. (7M, May-19)Sri Silpa Padmanabhuni100% (1)

- 17 - de Journal - EcsDocumento48 páginas17 - de Journal - EcsPrakalp JhaAinda não há avaliações

- DCS-2 Practical File Part-1Documento26 páginasDCS-2 Practical File Part-1ykr007Ainda não há avaliações

- CaseDocumento25 páginasCaseDeepanshu Midha5140Ainda não há avaliações

- ECNG 3016 Advanced Digital Electronics: Eneral NformationDocumento10 páginasECNG 3016 Advanced Digital Electronics: Eneral NformationMarlon BoucaudAinda não há avaliações

- Vlsi Es Lab Manual 4TH Year 2018 PDFDocumento103 páginasVlsi Es Lab Manual 4TH Year 2018 PDFబొమ్మిరెడ్డి రాంబాబుAinda não há avaliações

- Appendix A. Verilog Examples: A.1 Combinational Logic StructuresDocumento14 páginasAppendix A. Verilog Examples: A.1 Combinational Logic StructuresTrenton LindholmAinda não há avaliações

- VLSI LAB Manual 2014 PDFDocumento67 páginasVLSI LAB Manual 2014 PDFraghvendrmAinda não há avaliações

- VO FinalDocumento140 páginasVO Finalsudhasesh2000Ainda não há avaliações

- Lab 07Documento10 páginasLab 07api-241454978Ainda não há avaliações

- CO Lab Manual-MinDocumento40 páginasCO Lab Manual-MinMatheen TabidAinda não há avaliações

- 1-Microcontroller Based System Design - CompleteDocumento55 páginas1-Microcontroller Based System Design - CompleteWasif Bin ArifAinda não há avaliações

- 17 - de Exp Journal - EcsDocumento48 páginas17 - de Exp Journal - EcsPrakalp JhaAinda não há avaliações

- Comb LogicDocumento3 páginasComb LogicTeeJaaAinda não há avaliações

- Programmable Logic Devices (PLDS) : Lesson ObjectivesDocumento10 páginasProgrammable Logic Devices (PLDS) : Lesson ObjectivesjamaalnasirAinda não há avaliações

- Multiplexer and DemultiplexerDocumento18 páginasMultiplexer and DemultiplexerTara SharmaAinda não há avaliações

- Advanced Digital Design Using Verilog (KEC-054) Notes - Unit 5Documento9 páginasAdvanced Digital Design Using Verilog (KEC-054) Notes - Unit 5nishant mishraAinda não há avaliações

- DDCO Model Paper SolvedDocumento33 páginasDDCO Model Paper SolvedPraneethAinda não há avaliações

- Experiment No. 1: Switch and Gate Level Modeling Pre Lab TaskDocumento17 páginasExperiment No. 1: Switch and Gate Level Modeling Pre Lab TaskMuhammad ShoaibAinda não há avaliações

- CSE20221 Keyboard Interface ProjectDocumento2 páginasCSE20221 Keyboard Interface ProjectpranjalAinda não há avaliações

- Function BlocksDocumento43 páginasFunction BlocksAamir Ahmed Ali SalihAinda não há avaliações

- Experiment 17: in and Out Instructions (Unit 6)Documento15 páginasExperiment 17: in and Out Instructions (Unit 6)Emerson Jr CumlatAinda não há avaliações

- Verilog ExercisesheetDocumento6 páginasVerilog ExercisesheetFionna ImmaculateAinda não há avaliações

- DCS Assignment 1Documento5 páginasDCS Assignment 1Aayush JainAinda não há avaliações

- 4-Cominational Circuit Design With Decoders, Multiplexers, and EncodersDocumento14 páginas4-Cominational Circuit Design With Decoders, Multiplexers, and EncodersHadeer GamalAinda não há avaliações

- VerilogDocumento61 páginasVerilogSathish Kumar100% (1)

- Practica5 - Resultados Digital SystemsDocumento4 páginasPractica5 - Resultados Digital SystemslaramecaAinda não há avaliações

- Combinational and Sequential Circuits DesignDocumento25 páginasCombinational and Sequential Circuits DesignJadesh ChandaAinda não há avaliações

- Experiment-5: Software RequiredDocumento51 páginasExperiment-5: Software RequiredVikasAinda não há avaliações

- Bode V 2.31 SG: by Thomas ReitmayrDocumento16 páginasBode V 2.31 SG: by Thomas ReitmayrFrank ParkerAinda não há avaliações

- Multiplexer Circuit and How It WorksDocumento9 páginasMultiplexer Circuit and How It WorksEpnixAinda não há avaliações

- Implement A Verilog Model and Display The Output For A Set of Sample Data Together With The Wave Form Obtained For The Problems Given BelowDocumento6 páginasImplement A Verilog Model and Display The Output For A Set of Sample Data Together With The Wave Form Obtained For The Problems Given Belowlilly pushparaniAinda não há avaliações

- DCD QB Dec 2023 StudentDocumento7 páginasDCD QB Dec 2023 StudentPranav VasudevAinda não há avaliações

- Ee529 Asg2Documento16 páginasEe529 Asg2dd23015Ainda não há avaliações

- Lab 2 - myRIO Analog Basics PDFDocumento6 páginasLab 2 - myRIO Analog Basics PDFguigo170_321273986Ainda não há avaliações

- Lab 6Documento7 páginasLab 6Koteswara Rao VaddempudiAinda não há avaliações

- ECAD Lab Manual (ECAD and VLSI Lab)Documento105 páginasECAD Lab Manual (ECAD and VLSI Lab)Swaminathan Kathirvel0% (1)

- Digital ElectronicsDocumento32 páginasDigital ElectronicsMd. Tanvir Ahmed0% (1)

- VLSI Lab Manual Student Copy 21-22 04.10.21Documento76 páginasVLSI Lab Manual Student Copy 21-22 04.10.21RanjithAinda não há avaliações

- VLSI Lab Manual V Sem July16Documento65 páginasVLSI Lab Manual V Sem July16Aditya RanjanAinda não há avaliações

- ELCE231 Labscript 2Documento8 páginasELCE231 Labscript 2Little VoiceAinda não há avaliações

- CSC C85 Summer 2004: Assembly Language ProgrammingDocumento45 páginasCSC C85 Summer 2004: Assembly Language ProgrammingAli AhmadAinda não há avaliações

- Cadence Nclaunch LabDocumento86 páginasCadence Nclaunch Labsweety987Ainda não há avaliações

- Using Programmable Logic and The PALCE22V10 Programmable Logic Chips (LikeDocumento5 páginasUsing Programmable Logic and The PALCE22V10 Programmable Logic Chips (LikeStephenVincentGAinda não há avaliações

- Damson University College of Engineering Computer Engineering DepartmentDocumento5 páginasDamson University College of Engineering Computer Engineering DepartmentZedrik MojicaAinda não há avaliações

- Simple 8051 Programming and Digital Design With VHDLDocumento17 páginasSimple 8051 Programming and Digital Design With VHDLAlaso Braun-wezAinda não há avaliações

- Data Flow Modelling, Mux and Adders: Gate DelaysDocumento15 páginasData Flow Modelling, Mux and Adders: Gate DelaysMuhammad Usman RafiqAinda não há avaliações

- Verilog Hardware Description Language (HDL) : Why Use A HDLDocumento16 páginasVerilog Hardware Description Language (HDL) : Why Use A HDLkeyurAinda não há avaliações

- Verilog HDL: Dr. Shoab KhanDocumento61 páginasVerilog HDL: Dr. Shoab KhanSufyan AsgharAinda não há avaliações

- UntitledDocumento63 páginasUntitled魏延任Ainda não há avaliações

- ADE Lecture11Documento12 páginasADE Lecture11Baraa MuhammadAinda não há avaliações

- Projects With Microcontrollers And PICCNo EverandProjects With Microcontrollers And PICCNota: 5 de 5 estrelas5/5 (1)

- Anais Do Workshop De Micro-ondasNo EverandAnais Do Workshop De Micro-ondasAinda não há avaliações

- Delhi Schedule of Rates E&M - 2014Documento104 páginasDelhi Schedule of Rates E&M - 2014Jaisree Balu Pydi86% (7)

- Os D201Documento92 páginasOs D201jacmgmorgan100% (1)

- Paper - 062 - INTEGRATION OF SOLAR PHOTOVOLTAIC DISTRIBUTED GENERATION IN NIGERIAN POWER SYSTEM NETWORKDocumento6 páginasPaper - 062 - INTEGRATION OF SOLAR PHOTOVOLTAIC DISTRIBUTED GENERATION IN NIGERIAN POWER SYSTEM NETWORKabera alemayehuAinda não há avaliações

- Upper Control Card Repair ManualDocumento17 páginasUpper Control Card Repair ManualimmortalAinda não há avaliações

- Siemens D6 Platform 6.0-MW.Documento8 páginasSiemens D6 Platform 6.0-MW.Uhrin ImreAinda não há avaliações

- 3.4 Diagnosis Code and Backup: 0.5V Boost Sensor 4.8VDocumento1 página3.4 Diagnosis Code and Backup: 0.5V Boost Sensor 4.8VchinhAinda não há avaliações

- Deltalite II 2510-4: Neodymium SeriesDocumento2 páginasDeltalite II 2510-4: Neodymium SeriesAji VerdeAinda não há avaliações

- FTDI Chip: USB SolutionsDocumento20 páginasFTDI Chip: USB SolutionsPaloma Sousa100% (1)

- Advanced SensorsDocumento23 páginasAdvanced SensorsAzharuddin MansooriAinda não há avaliações

- PS-1250 (Batería 12 V) - DatasheetDocumento2 páginasPS-1250 (Batería 12 V) - DatasheetnandosinternetAinda não há avaliações

- Errores HitachiDocumento4 páginasErrores HitachiToni Pérez Lago50% (2)

- Toshiba (TV) 46H84 PDFDocumento46 páginasToshiba (TV) 46H84 PDFDan PrewittAinda não há avaliações

- Read and Interpret PlansDocumento64 páginasRead and Interpret PlansAdugnaw EnkuahoneAinda não há avaliações

- Electrostatic 1 (Mcq. For Board)Documento9 páginasElectrostatic 1 (Mcq. For Board)Sheetal meenaAinda não há avaliações

- JH-HE3416 Guide v1.3.1 enDocumento112 páginasJH-HE3416 Guide v1.3.1 enDavid Santiago Ortiz Rodriguez100% (2)

- Power Semiconductor Devices (Power Switches)Documento17 páginasPower Semiconductor Devices (Power Switches)yesar laftaAinda não há avaliações

- Alternating Current DPPsDocumento2 páginasAlternating Current DPPsMayur BelsareAinda não há avaliações

- Attach 8 - CPDS Type 2ADocumento401 páginasAttach 8 - CPDS Type 2AGlenn Adalia BonitaAinda não há avaliações

- Composite RLH MetamatrialsDocumento3 páginasComposite RLH MetamatrialsmenguemengueAinda não há avaliações

- RiverSurveyor Live ManualDocumento151 páginasRiverSurveyor Live Manualsequeira60Ainda não há avaliações

- Mechatronic System DesignDocumento30 páginasMechatronic System DesignNor AzlanAinda não há avaliações

- Reading Transistor MarkingsDocumento2 páginasReading Transistor Markingsthomas.vivet6396Ainda não há avaliações

- Brochure HD67701-HD67702 ENGDocumento21 páginasBrochure HD67701-HD67702 ENGNirmal PakhiraAinda não há avaliações

- Ap326310 Tc1765bootstraploader v1.0 2002 03Documento32 páginasAp326310 Tc1765bootstraploader v1.0 2002 03Poon Electronic Training CentreAinda não há avaliações

- LM317L DatasheetDocumento20 páginasLM317L Datasheetg0ierAinda não há avaliações

- Graphic Adapters and Monitors - The SummaryDocumento9 páginasGraphic Adapters and Monitors - The SummaryCiprian Laurentiu CazanelAinda não há avaliações

- Multiple Choice Practice Questions/Answer For Online/Omr AITT-2020 2 Year Electronics Mech. Trade TheoryDocumento66 páginasMultiple Choice Practice Questions/Answer For Online/Omr AITT-2020 2 Year Electronics Mech. Trade TheoryAbcAinda não há avaliações

- ARUM504DTE5: (A) ARUM121DTE5 (B) ARUM168DTE5 Multi V™ 5 460V ODU (C) ARUM216DTE5Documento2 páginasARUM504DTE5: (A) ARUM121DTE5 (B) ARUM168DTE5 Multi V™ 5 460V ODU (C) ARUM216DTE5RedHammerAinda não há avaliações

- Datasheet LTC1286 FsDocumento25 páginasDatasheet LTC1286 FsRamonAinda não há avaliações

- RTD2122LDocumento52 páginasRTD2122LadriantxeAinda não há avaliações