Escolar Documentos

Profissional Documentos

Cultura Documentos

Datasheet 2

Enviado por

Muhammad Muavia KhanDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Datasheet 2

Enviado por

Muhammad Muavia KhanDireitos autorais:

Formatos disponíveis

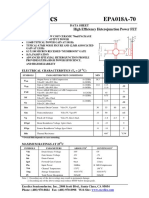

Data Sheet, March 2009

Control integrated Power System (CIPOS)

IKCS12F60B2A IKCS12F60B2C

http://www.infineon.com/cipos

Power Management & Drives

N e v e r

s t o p

t h i n k i n g .

CIPOS IKCS12F60B2A IKCS12F60B2C

Revision History: Previous Version: Page 4 10 14

2009-04 2.1 Subjects (major changes since last revision) Added UL certification Change VIT,HYS Updated Zth-diagram of diode

Rev. 2.2

Authors: W. Frank, W. Brunnbauer Edition 2008-03 Published by Infineon Technologies AG 85579 Neubiberg, Germany Infineon Technologies AG 4/6/09. All Rights Reserved. Attention please! The information given in this data sheet shall in no event be regarded as a guarantee of conditions or characteristics (Beschaffenheitsgarantie). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party. Information For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office or representatives (http://www.infineon.com). Warnings Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office or representatives. Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered. TRENCHSTOP is a registered trademark of Infineon Technologies AG. CIPOS, CoolMOS, CoolSET, DuoPack and thinQ! are trademarks of Infineon Technologies AG.

Data Sheet

2/18

Rev. 2.2, March 2009

CIPOS IKCS12F60B2A IKCS12F60B2C Table of Contents

CIPOS Control integrated Power System..................................................................................................4 Features........................................................................................................................................................4 Target Applications .....................................................................................................................................4 Description...................................................................................................................................................4 System Configuration .................................................................................................................................4 Internal Electrical Schematic...........................................................................................................................5 Pin Assignment.................................................................................................................................................6 Pin Description ............................................................................................................................................6 /HIN1,2,3 and /LIN1,2,3 (Low side and high side control pins, Pin 15 - 20) .............................................. 6 TEMP (temperature NTC, Pin 24) .............................................................................................................. 7 ITRIP (Over-current detection function, Pin 21) ......................................................................................... 7 VDD, VSS (control side supply and reference, Pin 22, 23)........................................................................ 7 VB1,2,3 and VS1,2,3 (High side supplies, Pin 1, 2, 4, 5, 7, 8)................................................................... 7 VRU, VRV, VRW (low side emitter, Pin 12, 13, 14) ................................................................................... 7 V+ (positive bus input voltage, Pin 10)....................................................................................................... 7 Absolute Maximum Ratings ............................................................................................................................8 Module Section ............................................................................................................................................8 IGBT and Diode Section .............................................................................................................................8 Control Section............................................................................................................................................9 Recommended Operation Conditions............................................................................................................9 Static Characteristics.....................................................................................................................................10 Dynamic Characteristics................................................................................................................................11 Integrated Components .................................................................................................................................12 Characteristics................................................................................................................................................13 Test Circuits and Parameter Definition ........................................................................................................15 Package Outline IKCS12F60B2A ..................................................................................................................17 Package Outline IKCS12F60B2C ..................................................................................................................18

Data Sheet

3/18

Rev. 2.2, March 2009

CIPOS IKCS12F60B2A IKCS12F60B2C

CIPOS Control integrated Power System

Single In-Line Intelligent Power Module 3-bridge 600V / 12A @ 25C

Features

Fully isolated Single In-Line molded module TrenchStop IGBTs with lowest VCE(sat) Optimal adapted antiparallel diode for low EMI Integrated bootstrap diode and capacitor Rugged SOI gate driver technology with stability against transient and negative voltage Fully compliant to 3.3V and 5V microcontrollers Temperature sense Undervoltage lockout at all channels Matched propagation delay for all channels Low side emitter pins accessible for all phase current monitoring (open emitter) Cross-conduction prevention Lead-free terminal plating; RoHS compliant Qualified according to JEDEC1 (high temperature stress tests for 1000h) for target applications The CIPOS module family offers the chance for integrating various power and control components to increase reliability, optimize PCB size and system costs. This SIL-IPM is designed to control AC motors in variable speed drives for applications like air conditioning, compressors and washing machines. The package concept is specially adapted to power applications, which need extremely good thermal conduction and electrical isolation, but also EMI-save control and overload protection. The features of Infineon TrenchStop IGBTs and antiparallel diodes are combined with a new optimized Infineon SOI gate driver for excellent electrical performance.

System Configuration

3 halfbridges with TrenchStop IGBT & FWdiodes 3 SOI gate driver Bootstrap diodes for high side supply Integrated 100nF bootstrap capacitance Temperature sensor, passive components for adaptions Isolated heatsink Creepage distance typ 3.2mm

Target Applications

Washing machines Consumer Fans and Consumer Compressors

Certification

UL 1577 (UL file E314539)

Description

1

J-STD-020 and JESD-022 4/18 Rev. 2.2, March 2009

Data Sheet

CIPOS IKCS12F60B2A IKCS12F60B2C

Internal Electrical Schematic

V+ (10)

Tr1, U-HS D1 Cge = 390 pF Cge1 Tr3, V-HS D3 Cge3 Tr5, W-HS D5 Cge5

Tr2, U-LS D2 Cge2

Tr4, V-LS D4 Cge4

Tr6, W-LS D6 Cge6

VRU (12) VRV (13) VRW (14) U, VS1 (8) V, VS2 (5) W, VS3 (2)

RH1 RL1 RH2 RL2 RH3 RL3

VB3 (1) VB2 (4) VB1 (7)

CbsH1 Dbs1Dbs3 CbsH2 CbsH3

Rbs

VDD (22) /HIN1 (15) /HIN2 (16) /HIN3 (17) /LIN1 (18) /LIN2 (19) /LIN3 (20) ITRIP (21) TEMP (24) VSS (23)

C1 Dz

VCC /HIN1 /HIN2 /HIN3 /LIN1 /LIN2 /LIN3 R2-R8 R1 RTS

Driver-IC

C2

Figure 1: Internal Schematic

Data Sheet

5/18

Rev. 2.2, March 2009

CIPOS IKCS12F60B2A IKCS12F60B2C Pin Assignment

Pin Number 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 Pin Name VB3 W,VS3 n.a. VB2 V,VS2 n.a. VB1 U,VS1 n.a. V+ n.a. VRU VRV VRW /HIN1 /HIN2 /HIN3 /LIN1 /LIN2 /LIN3 ITRIP VDD VSS TEMP Pin Description high side floating IC supply voltage motor output W, high side floating IC supply offset voltage None high side floating IC supply voltage motor output V, high side floating IC supply offset voltage None high side floating IC supply voltage motor output U, high side floating IC supply offset voltage None positive bus input voltage None low side emitter low side emitter low side emitter input gate driver high side 1/U input gate driver high side 2/V input gate driver high side 3/W input gate driver low side 1/U input gate driver low side 2/V input gate driver low side 3/W input overcurrent shutdown module control supply module negative supply temperature monitoring

Pin Description

/HIN1,2,3 and /LIN1,2,3 (Low side and high side control pins, Pin 15 - 20) These pins are active low and they are responsible for the control of the integrated IGBT The Schmitt-trigger input threshold of them are such to guarantee LSTTL and CMOS compatibility

down to 3.3V controller outputs. The maximum voltage at these pins is 5.5V and therefore fully compliant to 3.3V-microcontrollers. Pull-up resistor of about 75 k is internally provided to pre-bias inputs during supply start-up and a zener clamp is provided for pin protection purposes. Input schmitt-trigger and noise filter provide beneficial noise rejection to short input pulses. It is recommended for proper work of CIPOS not to provide an input pulse-width and PWM deadtimes lower than 1us. The integrated gate drive provides additionally a shoot through prevention capability which avoids the simultaneous on-state of two gate drivers of the same leg (i.e. HO1 and LO1, HO2 and LO2, HO3 and LO3).

Figure 2: Input pin structure Data Sheet 6/18

Rev. 2.2, March 2009

CIPOS IKCS12F60B2A IKCS12F60B2C

A minimum deadtime insertion of typ 380ns is also provided, in order to reduce cross-conduction of the external power switches. TEMP (temperature NTC, Pin 24) The TEMP terminal provides direct access to the NTC, which is referenced to VSS. An external pull-up resistor connected to +5V ensures, that the resulting voltage can be directly connected to the microcontroller. switches from critically low gate voltage levels during on-state and therefore from excessive power dissipation. VB1,2,3 and VS1,2,3 (High side supplies, Pin 1, 2, 4, 5, 7, 8) VB to VS is the high side supply voltage. The high side circuit can float with respect to VSS following the external high side power device emitter/source voltage. Due to the low power consumption, the floating driver stage is supplied by an integrated bootstrap circuit connected to VDD. This includes also integrated bootstrap capacitors of 100 nF at each floating supply, which are located very close to the gate drive circuit.

TEMP VSS

RNTC

CIPOS

Figure 3: Internal Circuit at pin TEMP

ITRIP (Over-current detection function, Pin 21) CIPOS provides an over-current detection function by connecting the ITRIP input with the motor current feedback. The ITRIP comparator threshold (typ 0.46V) is referenced to VSS ground. A input noise filter (typ: tITRIPMIN = 225ns) prevents the driver to detect false over-current events. Over-current detection generates a hard shut down of all outputs of the gate driver after the shutdown propagation delay of typically 900ns. The fault-clear time is set to typically to 4.7ms. VDD, VSS (control side supply and reference, Pin 22, 23) VDD is the low side supply and it provides power both to input logic and to low side output power stage. Input logic is referenced to VSS ground as well as the under-voltage detection circuit. The under-voltage circuit enables the device to operate at power on when a supply voltage of at least a typical voltage of VDDUV+ = 12.1 V is at least present. The IC shuts down all the gate drivers power outputs, when the VCC supply voltage is below VDDUV- = 10.4 V. This prevents the external power

Figure 4: Input filter timing diagram The under-voltage detection operates with a rising supply threshold of typical VBSUV+ = 12.1 V and a falling threshold of VDDUV- = 10.4 V according to Figure 4. VS1,2,3 provide a high robustness against negative voltage in respect of VSS of -50 V. This ensures very stable designs even under rough conditions. VRU, VRV, VRW (low side emitter, Pin 12, 13, 14) The low side emitters are available for current measurements of each phase leg. It is recommended to keep the connection to pin VSS as short as possible in order to avoid unnecessary inductive voltage drops. V+ (positive bus input voltage, Pin 10) The high side IGBT are connected to the bus voltage. It is recommended, that the bus voltage does not exceed 500 V.

Data Sheet

7/18

Rev. 2.2, March 2009

CIPOS IKCS12F60B2A IKCS12F60B2C

Absolute Maximum Ratings

(Tc = 25C, if not stated otherwise) Module Section Description Condition Symbol Min Storage temperature range Operating temperature control PCB Solder temperature Insulation test voltage Mounting torque Mounting pressure on surface Creepage distance Max. peak power of bootstrap resistor tp = 100s Tc= 100C

1

Value max 125 125 260 0.6 150 90

Unit

Tstg TPCB

Wave soldering, 1.6mm (0.063in.) from case for 10s

-40 2500 3.1

C C C V Nm N/mm mm W

Tsol VISOL

RMS, f=50Hz, t =1min

M3 screw and washer MS Package flat on mounting surface NMC dS PBRpeak

IGBT and Diode Section Description Condition Symbol min Max. Blocking Voltage Tc = 25C,TvJ < 150C Tc = 80C,TvJ < 150C tp limited by TvJmax

VDD = 15V,VDC = 400V, TvJ = 150C VDD = 15V,VDC 500V, TvJ = 150C, IC = 6A VCEmax = 600V

Value max 12 6 18 5 Full Square

Unit

VCES Iu, Iv, Iw Iu, Iv, Iw tsc

600 -12 -6 -18 -

DC output current

Repetitive peak collector current Short circuit withstand time2 IGBT reverse bias safe operating area (RBSOA) Power dissipation per IGBT Operating junction temperature range

A s

Tc = 25C IGBT Diode

Ptot TvjI TvjD

-40 -40

35 150 150

W C

1 2

Monitored by pin 24 Allowed number of short circuits: <1000; time between short circuits: >1s. 8/18 Rev. 2.2, March 2009

Data Sheet

CIPOS IKCS12F60B2A IKCS12F60B2C

Description

Condition

Symbol

Value min max 3.0 4.2

Unit

Single IGBT thermal resistance, junction-case Single diode thermal resistance, junction-case

RthJC RthJCD

K/W

Control Section Description Condition Symbol Value min Module supply voltage High side floating supply voltage (VB vs. VS) High side floating IC supply offset voltage ITRIP Input voltage /HIN, /LIN Input voltage Operating junction temperature Max. switching frequency

1

Unit max 20 20 600 10 5.5 125 20 C kHz V

VDD VBS tp < 500ns VS1,2,3 VIN,ITRIP VIN = float VIN TJ,IC fPWM

-1 -1 VDD-VBS-6 VDD-VBS-50 -1 -1 -

Recommended Operation Conditions

All voltages are absolute voltages referenced to VSS -Potential unless otherwise specified. Description Symbol Value min High side floating supply offset voltage High side floating supply voltage (VB vs. VS) Low side power supply Logic input voltages LIN, HIN, ITRIP VS VBS VDD VIN -3 12.5 12.5 0 max 500 17.5 17.5 5 V Unit

Monitored by pin 24 9/18 Rev. 2.2, March 2009

Data Sheet

CIPOS IKCS12F60B2A IKCS12F60B2C

Static Characteristics

(Tc = 25C, VDD = 15V, if not stated otherwise) Description Condition Symbol min Collector-Emitter breakdown voltage Collector-Emitter saturation voltage VIN = 5V, IC = 0.25mA VDD = 15V, Iout = +/- 6A TvJ = 25C TvJ = 150C VIN = 5V, Iout = +/- 6A TvJ = 25C TvJ = 150C VCE = 600V, VGE = 5V TvJ = 25C TvJ = 150C VDD = 15V, tSC 5s VCC = 300V, Tj = 150C V(BR)CES VCE(sat) 600 Value typ max V V 1.7 0.7 360 45 11.0 9.5 1.2 1.6 1.8 1.65 1.6 40 2.1 0.9 460 75 12.1 10.4 1.7 10.4 10.6 300 2.4 55 220 75 30 2.1 Unit

Diode forward voltage

VF

2.05

V A

Zero gate voltage collector current of IGBT Short circuit collector current1 Logic "0" input voltage (LIN,HIN) Logic "1" input voltage (LIN,HIN) ITRIP positive going threshold ITRIP input hysteresis VDD and VBS supply undervoltage positive going threshold VDD and VBS supply undervoltage negative going threshold VCC and VBS supply undervoltage lockout hysteresis Input clamp voltage (/HIN, /LIN) Input clamp voltage (ITRIP) Quiescent VBx supply current (VBx only) Quiescent VDD supply current (VDD only) Input bias current Input bias current ITRIP Input bias current Leakage current of high side

ICES

40 1000 2.4 1.1 540 12.8 11 13 13 550 3.4 100 400 120 A V V mV mV V V V V V A mA A A A A

IC(SC) 2 VIH VIL VIT,TH+ VIT,HYS VDDUV+ VBSUV+2 VDDUVVBSUV-2 VDDUVH VBSUVH2

IIN = 4mA IIN = 4mA VIN = low VIN = float VIN = 5V VIN = 0V VITRIP = 5V Tj,IC = 125C

VINCLAMP VINCLAMP2 IQB IQDD IIN+ IINIITRIP+ ILVS2

1 2

Allowed number of short circuits: <1000; time between short circuits: >1s. Test is not subject of product test, verified by characterisation 10/18 Rev. 2.2, March 2009

Data Sheet

CIPOS IKCS12F60B2A IKCS12F60B2C

Dynamic Characteristics

(Tc = 25C, VDD = 15V, if not stated otherwise) Description Condition Symbol min Turn-on propagation delay High side or low side Turn-on rise time High side or low side Turn-off propagation delay High side or low side Turn-off fall time High side or low side Shutdown propagation delay ITRIP Input filter time ITRIP Input filter time at LIN for turn on and off and input filter time at HIN for turn on only Input filter time at HIN for turn off Input filter time at HIN for turn off Fault clear time after ITRIP-fault Min. deadtime between low side and high side Deadtime of gate drive circuit IGBT Turn-on Energy (includes reverse recovery of diode) IGBT Turn-off Energy Iout = 6A, VDC = 300V TvJ = 25C TvJ = 150C Iout = 6A, VDC = 300V TvJ = 25C TvJ = 150C Iout = 6A, VDC = 300V TvJ = 25C TvJ = 150C VLIN,HIN = 0V; Iout = 6A, VDC = 300V VLIN,HIN = 5V Iout = 6A, VDC = 300V VLIN,HIN = 5V; Iout = 6A, VDC = 300V VLIN,HIN = 0V Iout = 6A, VDC = 300V VITRIP = 1V, Iu, Iv, Iw = 6A VITRIP = 1V VLIN,HIN = 0 V & 5V td(on) tr td(off) tf tITRIP tITRIPmin tFILIN 155 120 Value typ 638 22 812 30 900 210 270 max 380 ns Unit

VHIN = 5V VHIN = 5 V VLIN,HIN = 0 V & 5V VITRIP = 0 V

tFILIN1 tFILIN2 tFLTCLR DTPWM DTIC Eon

220 400 4.7 1 380 138 188 117 151 33 84

ms s ns J

Eoff

Diode recovery Energy

Erec

Data Sheet

11/18

Rev. 2.2, March 2009

CIPOS IKCS12F60B2A IKCS12F60B2C

Integrated Components

Description Condition Symbol1 min Resistor Resistor B-Constant of NTC (Negative Temperature Coefficient) Bootstrap diode forward voltage Capacitor Capacitor Bootstrap Capacitor TNTC = 25C TNTC = 25C IFDbs = 100mA Rbs RTS B25 VFDbs C1 Cgex CbsHx Value typ 10 100 4250 1.9 100 0.39 100 max 2.05 k K V nF Unit

Symbols according to Figure 1 12/18 Rev. 2.2, March 2009

Data Sheet

CIPOS IKCS12F60B2A IKCS12F60B2C

Characteristics

15A VGE=25C

15A

IC, COLLECTOR CURRENT

IF, forward CURRENT

12A

125C 150C

12A

9A

9A

6A

6A VGE=25C 3A 125C 150C

3A

0A 0V 1V 2V 3V

0A 0V 1V 2V

VCE, COLLECTOR EMITTER VOLTAGE Figure 5. Typical IGBT output characteristic (VDD = 15V)

VF FORWARD VOLTAGE Figure 6. Typical diode forward current as a function of forward voltage

1000ns

td(off) td(on)

1000ns

td(off)

td(on)

t, SWITCHING TIMES

100ns

tr

t, SWITCHING TIMES

100ns

tf

tf

10ns

tr 10ns 25C

0A

5A

10A

15A

50C

75C

100C

125C

IC, COLLECTOR CURRENT Figure 7. Typical switching times as a function of collector current (inductive load, TJ=150C, VCE = 300V, VDD = 15V Dynamic test circuit in Figure A)

TvJ, JUNCTION TEMPERATURE Figure 8. Typical switching times as a function of junction temperature (inductive load, VCE = 300V, VDD = 15V, IC = 6A Dynamic test circuit in Figure A)

Data Sheet

13/18

Rev. 2.2, March 2009

CIPOS IKCS12F60B2A IKCS12F60B2C

1.25mJ

Eon

Eon 0.15mJ

E, SWITCHING ENERGY

E, SWITCHING ENERGY

1.00mJ

Eoff

0.75mJ

0.10mJ

0.50mJ

Eoff

0.05mJ

Erec

0.25mJ

Erec

0.00mJ 25C 50C 75C 100C 125C

0.00mJ

0A

5A

10A

15A

IC, COLLECTOR CURRENT Figure 9. Typical switching energy losses as a function of collector current (inductive load, TvJ = 150C, VCE = 300V, VDD = 15V Dynamic test circuit in Figure A)

TvJ, JUNCTION TEMPERATURE Figure 10. Typical switching energy losses as a function of junction temperature (inductive load, VCE = 300V, VDD = 15V, IC = 6A Dynamic test circuit in Figure A)

1000kOhm

ZthJC, TRANSIENT THERMAL RESISTANCE

Single Pulse IGBT Diode 10 K/W

0

RTS, NTC resistance

100kOhm

10kOhm

10 K/W

-1

1kOhm -25C 0C

min typ max

25C

50C

75C

100C

10 K/W

-2

1s

10s

100s

1ms

10ms 100ms

1s

TNTC, NTC TEMPERATURE Figure 11. Characteristic of NTC as a function of NTC temperature

tP, PULSE WIDTH Figure 12. Transient thermal impedance as a function of pulse width (D=tP/T)

Data Sheet

14/18

Rev. 2.2, March 2009

CIPOS IKCS12F60B2A IKCS12F60B2C

Test Circuits and Parameter Definition

Erec = vD i F dt

0

t Erec

Figure A: Dynamic test circuit Leakage inductance L =180nH Stray capacitance C =39pF

Figure B: Definition of diodes switching characteristics

Figure C: Definition of ITIRP propagation delay

LIN1,2,3 HIN1,2,3

2.1V 0.9V td(off) tf td(on) tr 90% 10% tEoff

t Eoff

iCU, iCV, iCW vCEU, vCEV, vCEW

90%

10%

10% tEon

2%

2%

Eoff =

vCEx i Cx dt

0

Eon = vCEx i Cx dt

0

t Eon

Figure D: Switching times definition and switching energy definition

Data Sheet

15/18

Rev. 2.2, March 2009

CIPOS IKCS12F60B2A IKCS12F60B2C

tFILIN HIN LIN

tFILIN

LIN

on

off

on

off

high LO HO LO low

a) HIN

tFILIN1 toff,HINx

tFILIN2

toff,HINx < tFILIN1 high

HO b) HIN toff,HINx toFILIN1 < toff,HINx < tFILIN2 HO c) HIN toff,HINx toff,HINx > tFILIN2 HO

Figure E: Short Pulse suppression

Data Sheet

16/18

Rev. 2.2, March 2009

CIPOS IKCS12F60B2A IKCS12F60B2C

Package Outline IKCS12F60B2A

Note: There may occur discolourations on the copper surface without any effect of the thermal properties.

Data Sheet

17/18

Rev. 2.2, March 2009

CIPOS IKCS12F60B2A IKCS12F60B2C

Package Outline IKCS12F60B2C

Description

Condition

Symbol min

Value typ 17 max -

Unit

Weight

mP

Note: There may occur discolourations on the copper surface without any effect of the thermal properties. Data Sheet 18/18 Rev. 2.2, March 2009

Você também pode gostar

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Robotic & Artificial IntelligenceDocumento21 páginasRobotic & Artificial IntelligenceMuhammad Muavia KhanAinda não há avaliações

- Robotic & Artificial IntelligenceDocumento12 páginasRobotic & Artificial IntelligenceMuhammad Muavia KhanAinda não há avaliações

- Pak Elektron Ltd. (Pel) - Internship Report To HR Dept. 03Documento11 páginasPak Elektron Ltd. (Pel) - Internship Report To HR Dept. 03Muhammad Muavia KhanAinda não há avaliações

- KFC - Facility Location and Layout (Operation Management Project) .Documento24 páginasKFC - Facility Location and Layout (Operation Management Project) .Muhammad Muavia Khan100% (1)

- Meezan Bank Internship ReportDocumento65 páginasMeezan Bank Internship ReportMuhammad Muavia Khan100% (1)

- Pak Elektron Ltd. (Pel) - Internship Report To HR Dept.Documento10 páginasPak Elektron Ltd. (Pel) - Internship Report To HR Dept.Muhammad Muavia KhanAinda não há avaliações

- KFC - Facility Location and Layout (Operation Management Project) .Documento17 páginasKFC - Facility Location and Layout (Operation Management Project) .Muhammad Muavia Khan91% (35)

- Operation Management Project On KFCDocumento16 páginasOperation Management Project On KFCMuhammad Muavia Khan57% (14)

- COMSATS Internship Evaluation FormDocumento3 páginasCOMSATS Internship Evaluation FormMuhammad Muavia KhanAinda não há avaliações

- COMSATS Internship Report FormatDocumento4 páginasCOMSATS Internship Report FormatMuhammad Muavia Khan50% (2)

- Republic of Cuba: COMSATS Institute of Information Technology, LahoreDocumento23 páginasRepublic of Cuba: COMSATS Institute of Information Technology, LahoreMuhammad Muavia KhanAinda não há avaliações

- Factors Influencing Customers Preference Regarding Milk ProductsDocumento28 páginasFactors Influencing Customers Preference Regarding Milk ProductsMuhammad Muavia Khan100% (2)

- Countries SWOT AnalysisDocumento12 páginasCountries SWOT AnalysisMuhammad Muavia Khan100% (5)

- BrazilDocumento13 páginasBrazilMuhammad Muavia KhanAinda não há avaliações

- Meezan Bank & Fayasl Bank Product Comparison Offer To CustomersDocumento21 páginasMeezan Bank & Fayasl Bank Product Comparison Offer To CustomersMuhammad Muavia Khan88% (8)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- Ap326310 Tc1765bootstraploader v1.0 2002 03Documento32 páginasAp326310 Tc1765bootstraploader v1.0 2002 03Poon Electronic Training CentreAinda não há avaliações

- FlowMaster User Manual V2.0Documento36 páginasFlowMaster User Manual V2.0Agus MulyadiAinda não há avaliações

- Ee2403-Special Electrical Machines Unit I - Synchronous Reluctance Motor Synchronous Reluctance Motor ConstructionDocumento8 páginasEe2403-Special Electrical Machines Unit I - Synchronous Reluctance Motor Synchronous Reluctance Motor ConstructionVijaya KumarAinda não há avaliações

- Instruction Book (AIB) Qc4003 Spain 2954 6330 02 EnglishDocumento40 páginasInstruction Book (AIB) Qc4003 Spain 2954 6330 02 EnglishGem RAinda não há avaliações

- 1SDC007408G0201 - WP Ats 021 022 enDocumento36 páginas1SDC007408G0201 - WP Ats 021 022 enSemih GençAinda não há avaliações

- Sport & Fitness User Manual MultiDocumento185 páginasSport & Fitness User Manual MultibeoAinda não há avaliações

- 605B Quick StartDocumento6 páginas605B Quick StartNguyen Hoàng HuyAinda não há avaliações

- Automatic Table Cleaning RobotDocumento39 páginasAutomatic Table Cleaning RobotKartheek BandiAinda não há avaliações

- Analysis of Silicon Solar Cell Device PaDocumento9 páginasAnalysis of Silicon Solar Cell Device PaHoucine NaimAinda não há avaliações

- Device To Device CommunicationDocumento19 páginasDevice To Device CommunicationabdelAinda não há avaliações

- Vacuum TubeDocumento1 páginaVacuum Tubejose condoriAinda não há avaliações

- Multi-Port Flow Selector Valve: KitsnetDocumento14 páginasMulti-Port Flow Selector Valve: KitsnetNigin ParambathAinda não há avaliações

- June 2019 (IAL) QPDocumento28 páginasJune 2019 (IAL) QPivyAinda não há avaliações

- C&D KCR Manual PDFDocumento6 páginasC&D KCR Manual PDFSteven MarksAinda não há avaliações

- Pressure SwitchDocumento2 páginasPressure Switchayyaz123Ainda não há avaliações

- خطوات عمل جداول الحسابات Panel SchedulesDocumento6 páginasخطوات عمل جداول الحسابات Panel SchedulesMOAZ ASHRAFAinda não há avaliações

- Harmonics HODocumento16 páginasHarmonics HOSSJN INTAN ZAHARAH RAHIMAinda não há avaliações

- VSP Seismic OkDocumento11 páginasVSP Seismic OkAlfi CahyaAinda não há avaliações

- General Characteristics: DescriptiveDocumento5 páginasGeneral Characteristics: DescriptiveXuân Huy Nguyễn100% (1)

- UntitledDocumento41 páginasUntitled203005 ANANTHIKA MAinda não há avaliações

- Adc 5100 SeriesDocumento2 páginasAdc 5100 SeriesLaurentiu IacobAinda não há avaliações

- Epa 018Documento2 páginasEpa 018curzAinda não há avaliações

- Zeme India Earthing BroucherDocumento8 páginasZeme India Earthing BrouchervipinAinda não há avaliações

- General Specification: 2017 EDITION (Incorporating Corrigendum No. Gsee02-2017)Documento4 páginasGeneral Specification: 2017 EDITION (Incorporating Corrigendum No. Gsee02-2017)Kin Ming ChungAinda não há avaliações

- Westermo Ds md-45 PDFDocumento2 páginasWestermo Ds md-45 PDFPablo TeránAinda não há avaliações

- Pioneer PDP-501MX Plasma DisplayDocumento96 páginasPioneer PDP-501MX Plasma DisplayJavier RodriguezAinda não há avaliações

- Beyer Dt300 HeadphonesDocumento2 páginasBeyer Dt300 HeadphonesJames Joyce100% (1)

- NX200Documento102 páginasNX200FABIANAinda não há avaliações

- Digital Electronics Ece 213 PDFDocumento15 páginasDigital Electronics Ece 213 PDFAlisha AgarwalAinda não há avaliações

- Pages From CIGREDocumento8 páginasPages From CIGREiman tabataba'iAinda não há avaliações