Escolar Documentos

Profissional Documentos

Cultura Documentos

Automated Implementation of Digital Circuits in Current-Mode FPGA Chips

Enviado por

Nguyen SumDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Automated Implementation of Digital Circuits in Current-Mode FPGA Chips

Enviado por

Nguyen SumDireitos autorais:

Formatos disponíveis

223

Automated Implementation of Digital Circuits In Current-Mode FPGA Chips

Oleg Maslennikow, Przemyslaw Soltan

Abstracf In this paper, the automated, procedure to implementation of target digital circuits into current-mode FPGA chips liked to Xilinx FF'GAs is proposed. The paper purpose is the investigation of the possibility of designing and realization the whole programmable mixed analog-digital system

classical voltage-mode gates. Therefore, in the paper [SI, we use the approach to designing.current-mode digital circuits for synthesizing of the functional prototype of the hasic block of Xilinx FPGA cells the Spartan 11 FPGA's slice [3]. Results of VHDL-model simulations and results of experimental verification of the full-custom ASIC chip consisted of the current-mode slice, InOut block (IOB) and configuration memory block have shown the correct work of this circuit. This enables to construct the whole current-mode FPGA chip with the internal smcture and functional possibilities liked to Spartan-II FPGAs. However, because physical and logical properties of the current-mode gates as well as approaches to designing current-mode digital circuits are unknown to most designers. Therefore, in this paper, we propose the approach to automatic implementation of the target digital circuits in the currentmode FPGA chips. In this approach we assume, that currentmode FPGA chip is the functional prototype of an arbitrary

on a single die without substrate interference effect. Keywords Mixed analog-digital system, Field programmable gate array ( P G A ) , Current-mode gate, Computer-aided design, Mapping, placement and routing procedures.

I. INTRODUCTION

Modem application specific systems contain both digital and analog parts, where the first part usually is the specialized parallel processor, while the analog part is the preprocessing and interface unit between digital part and external world. Advances of the modem VLSl technology permit to implement such mixed systems on a single die. However, the problem of influence of digital part on the analog part of such a system-on-chip must be solved during system design. Switching transients (noise) of the digital part can perturb the analog part of a system owing to the coupling through the substrate [1,2]. Radical reduction of this noise is based on the implementation of the mixed system digital part with the current mode gates [4,5]. Due to the nearly constant value of the power supply current at the different gate states, the level of its noise is essentially lower in comparison with the classical voltage type gates. Moreover, based on the currentmode gates, several digital circuits were designed, which are characterized by smaller number of gates in comparison with their prototypes constructed with classical voltage CMOStype gates [ 5 ] . Note that physical and logical properties of the current-mode gates differ flom corresponding properties of Oleg Maslennikow, Przemyslaw Soltan - Electronics Depmment, Technical University ofKosralin, Partyzantow se.,17, Korzalin, 7541 1, POLAND, e-mails: olee~ie.hl.koszalin.DI, kerk@ie.tu.koszalin.pl

known FPGA chip, for example from Spartan or Virtex FPGA

families [3]. In this case, the proposed procedure consists of the following steps: design of the VHDL-model of the target circuit in the classical voltage technique and its verification using arbitrary taken VHDL simulator; synthesis ofthe verified model (mapping, placement and routing procedures) in the selected FPGA chip. n e result of this step is the . n d file and the .xdl file (when Xilinx Foundation environment is used). These files include information about used slices, IOBs, switches, etc. and their interconnections; analysis of the obtained .xdl file and its conversion to the corresponding file for selected current-mode FPGA chip based on currentmode blocks libmy. To realize it, the corresponding program-converter is used, which also

CADSM'2003, February 18-22,2003, Lviv-Slasko, Ukraine

allows generate the VHDL description of the target circuit in the current-mode technique. Ilis enables to simulate the obtained VDHL-model in the arbitrary VHDL simulator (for example, Active-HDL environment), in which current-mode table of resolution and current-mode gate libraries were included. The paper purpose is the investigation of the possibility of designing and realization the whole programmable mixed analog-digital system on a single die.

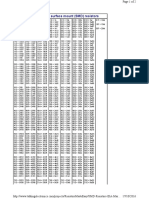

information about slices, IOBs, switches and others blocks, which have been used, and their interconnections. The fragment of the..xdl tile for the two-inputs AND function C=A and B is presented in the Fig. 2.

design ""U" xc2s1Scs144-6 "2.46

i

inst "a" "IOB"

, , ,

placed LRB K3

,

"i

cfg "PAD:a: 1NBUF:c-a: uNx::1

inst "b" "108"

inst " c " "108"

placed LR8 L1 ,

"i

cfg "PAD:b: 1NBUF:C-b: IMWX::l

placed LR8 K2

PAD:=: cMJX::O 0UTMUX::l;

11. PROCESS OF DESIGNING AND IMPLEMENTATION OF CURRENT-MODE VHDL PROJECT

In this designing process, we assume, that we have the current-mode FPGA chip, which is the functional prototype of an arbitrary Xilinx FPGA chip, for example from Spartan or Virtex families. In this case, the design of the VHDL-model of the target circuit in the standard classical voltage technique and its verification is performed in fust, using arbitrary taken VHDL simulator. Then the Xilinx Foundation environment is used for mapping, placement and routing of the target digital circuit in the selected FPGA chip. Fig. 1 illustrates the result

cfg "0mBUF:C-c:

inst "N-C"

"SLICE" , placed R8C1 CLB-R8Cl.S0,

cfg "YUSED::O G:C3:ILUT:D=(AZ*Al) - : : G " ;

net "N-a", outpin rtat'I, inpin "N-c" G Z ;

net "N-b", outpin "b" I, inpin "N-c" Gli

net "N-c", outpin "N-c" Y, inpin

'"E"

0;

Fig. 2. The fragment of the xdl tile for project of two-inputs AND function Each of used blocks from Fig. 1 is respectively configured. Information about FPGA cells is represented in the .xdl file as the text string, where keywords SLICE, IOB and PAD denote names of corresponding FPGA blocks, while keywords NET. OUTPIN and INPIN fmd the interconnections between used blocks (see Fig. 2). Keyword CFG denotes here the operation mode of the corresponding FPGA block. Fig. 3 illustrates the example of configuration and interconnections for the SLICE block, which have been used in the project of the two-inputs AND function. Next stage is analysis of the obtained .xdl file and its conversion to the corresponding file for selected current-mode FPGA chip based on current-mode blocks library. To realize it, the corresponding program-converter GEDEON was

of implementation of the two-inputs AND function C = A and

Bin the Spartan I1 FPGA

designed. For each used SLICE block this program defmes the logical function realized in the look-up-table blocks (LUTs) MATRIX OF SWITCKES and configuration data of all multiplexers. For each used IOB block program defines the configuration data of PAD and multiplexers blocks. Then program GEDEON transforms obtained data to the binary data stream, which are saved as the configuration file for the currentmode FPGA chip. In an order for this, the library of the current-mode gates is used.

Fig.1. Result of implementation ofthe two-inputs AND function in the SPARTAN II FPGA

The result of this stage is the .ncd file, which further should be transformed to the .xdl file format. The last file includes the

CADSM'2003, Fetiruary 18-22,2003. Lviv-Slasko; Ukraine

225

- A4 - A3

G 2 GI-

0x0

D

cfg "yUSED::O

G:C3:MLUT:D-(~*All

A2

AI

WS

I

DI

I

'

D=A2 and A1

=..... I1

-A2

. . . a A3

- ....

..

-

= a4 ......

.....

..... ... C 0.2 -.......

'FfO ............

a DIl

..

8AH

........

Configuration mode Fig. 3. The example of configuration and simulation for the SLICE block The proposed program also allows generate the V F L description of the target circuit in the current-mode technique. This enables to simulate'the obtained VDHL-model in the arbitrary VHDL simulator (for example, Active-HDL environment), in which current-mode table of resolution and current-mode gate libraries were included.

Work mode

REFERENCES

[I] R. Gonzalez, B.M. Gordon, M.A. Horowitz, "Supply and

Threshold Voltage Scaling for Low Power CMOS, IEEE

I. Solid-state Circuits, 1997, vol. 32, No. 8, pp. 12101215.

[2] M. Ingels, M.S.J. Steyaen, "Design strategies and de-

. 111. CONCLUSIONS

In this paper, the automated procedure to implementation of

target digital circuits into current-mode FPGA chips is

coupling techniques for reducing the effects of electrical interference in mixed-mode Ics", IEEE J. O Solid-state f Circuits, 1997, N7, pp. 1136-1 141. [3] "The Programmable Logic Data Book", X i l h , Inc., 2001.

[4] A. Guzinski, P. Pawlowski, D. Cnvyrow, J. Kaniewski, 0.

proposed. This procedure is suitable for currentmode FPGA chips, which are the functional prototypes of known FPGA chips of Spanan or Virtex families. Proposed procedure is based on the GEDEON prografn, which inalyses the input file ,. with information ahout slices, IOBs, switches, and others FPGA blocks, which have been used in the project, and theG interconnections. Then program transforms obtained data to the binary data stream, which are-saved as the configuration tile for the current-mode FPGA chip. In an order for this, the library of the currentmode gates is used. The paper purpose is the investigation of the possibility of designing and realization the whole programmable mixed analog-digital system on a single die without substrate interference effect.

Maslennikow, N. Maslennikowa, D. Rataj, "Design of Digital Circuits with Current-Mode Gates," Bulletin of the Polish Academy of Sciences, Technical Sciences, vol. 48,

. . .

no. I, pp.73-91,2000.

[SI 0. MaSkMikOW, "Approaches to Designing and Examples of Digital Circuits Based on the Current-Mode Gates,"

Data Recording, Storage & Processing, vol. 3, no. 2, pp.84-98,2001,

-

The work is supported by the grant KBN 7TI I B 004 20.

CADSM'2003, February 18-22,2003, Lviv-Slasko, Ukraine

Você também pode gostar

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- EIA Marking Code For Surface Mount (SMD) ResistorsDocumento2 páginasEIA Marking Code For Surface Mount (SMD) Resistorsqashqai q100% (1)

- Immo Off FilesDocumento6 páginasImmo Off Filesاليزيد بن توهامي100% (1)

- Chapter 3: Computer Instructions: ObjectivesDocumento7 páginasChapter 3: Computer Instructions: ObjectivesSteffany RoqueAinda não há avaliações

- Second Generation Intel Xeon Scalable Processors: Specification UpdateDocumento35 páginasSecond Generation Intel Xeon Scalable Processors: Specification Update劉紀寒Ainda não há avaliações

- Advanced Assembly: The AVR Microcontroller and Embedded SystemsDocumento26 páginasAdvanced Assembly: The AVR Microcontroller and Embedded SystemsLuqmanMaraabaAinda não há avaliações

- DriverEasy PCInfoDocumento3 páginasDriverEasy PCInfoDiego GómezAinda não há avaliações

- Master Slave Flip FlopDocumento3 páginasMaster Slave Flip FloplakshmiraniAinda não há avaliações

- Print Verilog CodeDocumento24 páginasPrint Verilog CodeShruthi DyavegowdaAinda não há avaliações

- NUCLEO-F767ZI - STM32 Nucleo-144 Development Board With STM32F767ZI MCU, Supports Arduino, ST Zio and Morpho Connectivity - STMiDocumento1 páginaNUCLEO-F767ZI - STM32 Nucleo-144 Development Board With STM32F767ZI MCU, Supports Arduino, ST Zio and Morpho Connectivity - STMijanespenicoAinda não há avaliações

- Basic Processing UnitDocumento35 páginasBasic Processing UnitPinky BhaiAinda não há avaliações

- Intel CPU-The Instruction Set ArchitectureDocumento2 páginasIntel CPU-The Instruction Set ArchitecturePauliniAinda não há avaliações

- 1131 Mohdyazidbinkamis2006Documento141 páginas1131 Mohdyazidbinkamis2006Fauzan AriqAinda não há avaliações

- Lesson 1 - Components of ComputerDocumento17 páginasLesson 1 - Components of Computerkimchen edenelleAinda não há avaliações

- 25AA640A 25LC640A 64K SPI Bus Serial EEPROM 200018-2449118Documento39 páginas25AA640A 25LC640A 64K SPI Bus Serial EEPROM 200018-2449118ManunoghiAinda não há avaliações

- SubtitleDocumento3 páginasSubtitleTrần Ngọc KhoaAinda não há avaliações

- Introduction To Pic MicrocontrollerDocumento16 páginasIntroduction To Pic MicrocontrollernothingtohideAinda não há avaliações

- Question Bank in Microprocessors & Applications I. Internal Architecture & Functional Description of 8085Documento2 páginasQuestion Bank in Microprocessors & Applications I. Internal Architecture & Functional Description of 8085Raghunadh ReddyAinda não há avaliações

- DIBUJO CON CODIGO GRBL (Figura Geométrica) : Trabajo Tercera Fase-Dibujo en CN: 1Documento614 páginasDIBUJO CON CODIGO GRBL (Figura Geométrica) : Trabajo Tercera Fase-Dibujo en CN: 1antonioAinda não há avaliações

- P7 (Analysis 4-Korea & Taiwan) (Auto-Saved)Documento68 páginasP7 (Analysis 4-Korea & Taiwan) (Auto-Saved)changmin shimAinda não há avaliações

- Experiment No. 1: 1. AIM: Write An 8086 Assembly Level Program To PerformDocumento12 páginasExperiment No. 1: 1. AIM: Write An 8086 Assembly Level Program To PerformgokulAinda não há avaliações

- Instruction Groups: The 8051 Has 255 Instructions - Every 8-Bit Opcode From 00 To FF Is Used Except For A5.Documento30 páginasInstruction Groups: The 8051 Has 255 Instructions - Every 8-Bit Opcode From 00 To FF Is Used Except For A5.VLC350ZAinda não há avaliações

- 68HC11 Assembly ProgrammingDocumento50 páginas68HC11 Assembly ProgrammingAmine EssakenAinda não há avaliações

- Atmel 0052Documento1 páginaAtmel 0052namerAinda não há avaliações

- Counters and Time DelaysDocumento12 páginasCounters and Time DelaysNiveditha KAinda não há avaliações

- Mosfet NotesDocumento65 páginasMosfet NotesAnmol DubeyAinda não há avaliações

- 1 - 30 - VLSI Major Project Titles List 2021Documento3 páginas1 - 30 - VLSI Major Project Titles List 2021Chakhila 123Ainda não há avaliações

- 6105 Computer Architecture FinalDocumento39 páginas6105 Computer Architecture FinalNISHANTAinda não há avaliações

- DVLSI Lab EXPT1 ManualDocumento8 páginasDVLSI Lab EXPT1 ManualApoorvaAinda não há avaliações

- What Is FlynnDocumento3 páginasWhat Is FlynnjvAinda não há avaliações

- Intel Moores Law Investor Meeting Paper FinalDocumento4 páginasIntel Moores Law Investor Meeting Paper FinalVale Ignacia TapiaAinda não há avaliações