Escolar Documentos

Profissional Documentos

Cultura Documentos

Hardware - Montagem - RAM - Estudo Detalhado

Enviado por

api-3813826Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Hardware - Montagem - RAM - Estudo Detalhado

Enviado por

api-3813826Direitos autorais:

Formatos disponíveis

CURSO TÉCNICO EM INFORMÁTICA -Acesso a RAM

Prof.º Adriano Queiroz Sobrinho – 3648-4152 / 9125-9909 – Rua Altair Severiano, 104, Eldorado

ESTUDO A FUNDO DAS MEMÓRIAS DINÂMICAS

FUNCIONAMENTO DAS MEMÓRIAS DINÂMICAS

Entender o funcionamento das memórias dinâmicas

e fundamentais para compreender o avanço tecno-

lógico trazido por novas tecnologias de construção

de memória RAM, como FPM, EDO, BEDO, SDRAM,

RDRAM e muitas outras, bem como para compre-

ender toda a questão do desempenho e a necessi-

dade do cache de memória. Vimos que, dentro do

circuito integrado da memória dinâmica, os dados

são armazenados em minúsculos capacitores. Co-

mo os capacitores se descarregam com o tempo, é

necessário um período de recarga, chamado refre-

sh rate. Durante o período de refresh, que dura

alguns milisegundos (esse valor varia de acordo

com a memória), a memória não pode ser

.acessada. Dentro da memória, os capacitores são

organizados em uma matriz. Como sabemos, uma

matriz é composta de linhas e colunas. Os endereços dentro da matriz crescerão da esquerda para a direita e de

cima para baixo. Quando o processador (ou o controlador de cache,) precisa ler algum dado da memória, ele colo-

ca o dado no barramento de dados, o endereço no barramento de endereços e aciona apropriadamente o barra-

mento de controle. O controlador de memória do chipset percebe que e uma operação de leitura em memória e

pega o valor do endereço e o divide em dois: a parte mais significativa (ou seja, mais alta) do endereço seleciona-

rá a linha, e a parte menos significativa (ou seja, mais baixa) do endereço selecionará a coluna (como vimos, in-

ternamente a memória é uma matriz de capacitores dispostos em linhas e colunas). Essa seleção ocorre em con-

junto com dois sinais básicos para o controle das memórias: RAS (Row Address Strobe) e CAS (Column Address

Strobe). O primeiro sinal indica que o valor presente no barramento de endereços de memória (MA) está infor-

PandaTitan Informática Página 1 Manaus / Amazonas

CURSO TÉCNICO EM INFORMÁTICA -Acesso a RAM

Prof.º Adriano Queiroz Sobrinho – 3648-4152 / 9125-9909 – Rua Altair Severiano, 104, Eldorado

mando a linha de onde o dado deverá ser lido, enquanto o segundo sinal indica que o valor está informando a

coluna de onde o dado deverá ser lido. Você pode observar os detalhes desse esquema através da figura.

Observe a Figura a seguir para acompanhar o funcionamento da memória RAM do micro:

1. Quando o processador (ou o controlador de cache) lê um dado da memória, o controlador de memória

(presente no chipset) aciona a linha RAS e coloca, no barramento de endereços da memória (barramento

MA,), o valor da linha.

2. Um pouco depois aciona a linha CAS (mantendo a linha RAS acionada) e coloca no barramento de endere-

ços da memória (barramento MA) o valor da coluna.

3. Quando RAS e CAS são desabilitados, o dado solicitado estará presente no barramento de dados da me-

mória (barramento MD).

4. O processo de escrita em memória funciona de maneira análoga (idêntica).

As novas tecnologias de construção de memórias dinâmicas são alterações na estrutura básica do funcionamento

da memória, de modo a ganhar mais desempenho, como veremos mais adiante.

TEMPO DE ACESSO

Quando o processador ordena o armazenamento de um dado na memória, este não é imediato; a memória demo-

ra um pouco para armazená-lo no endereço solicitado. O mesmo ocorre quando o processador pede que a memó-

ria devolva um dado que está

nela armazenado. Essa demora

é chamada “Tempo de Aces-

so” e é uma característica

inerente a todas as memórias,

ou seja, é uma característica

física. O tempo de acesso é o

período de tempo que demora

entre o início da ativação do

sinal RAS e a efetiva entrega

(ou armazenamento) do dado

solicitado, como ilustra a figu-

ra. O tempo de acesso tam-

bém é chamado TRAC ou so-

mente RAC em manuais técni-

cos. As memórias dinâmicas

têm tipicamente tempo de

acesso de 70 ou 60 ns. Já as

PandaTitan Informática Página 2 Manaus / Amazonas

CURSO TÉCNICO EM INFORMÁTICA -Acesso a RAM

Prof.º Adriano Queiroz Sobrinho – 3648-4152 / 9125-9909 – Rua Altair Severiano, 104, Eldorado

memórias estáticas são bem mais rápidas, apresentando tempo de acesso de 20 ns ou menor (as que são utiliza-

das no cache de memória dos micros modernos possuem um tempo de acesso de apenas 5 ns!). Lembre-se: quan-

to menor o tempo de acesso, melhor! Em circuitos de memória dinâmica assíncronos, como FPM, EDO e BEDO, O

tempo de acesso vem estampado na nomenclatura do circuito integrado, como sufixo. O sufixo “6” em uma memó-

ria dinâmica assíncrona significa que esta tem 60 ns de tempo de acesso, por exemplo. A Figura mostra exemplos

de circuitos de memória assíncrona com 70 ns de tempo de acesso. Você deve observar que em circuitos de me-

mória RAM síncrona — como a SDRAM —, por ser sincronizado com o clock do barramento local, o que há escrito

no circuito integrado não é o seu tempo de acesso, mas sim a sua freqüência de operação máxima, expressa em

nanossegundos. Para obter o valor em Megahertz, basta fazer a seguinte conta:

RAM Mhz = 1000 / Valor estampado.

CICLO DE ACESSO

O processador gasta dois pulsos de

clock para acessar a memória RAM.

Dessa forma, pelo menos teorica-

mente, a memória RAM do micro

deverá ser capaz de entregar ou

armazenar um dado dentro desse

tempo — ou seja, o tempo de a-

cesso da memória RAM deverá ser

menor ou igual a dois pulsos de

clock. É claro que estamos nos

referindo ao clock do barramento

local do micro (clock externo, ou

seja, o clock utilizado na placa-mãe

e que será usado na comunicação

do processador com a memória), e

não ao clock interno do processa-

dor. Em um micro com processador

486DX-25, em que o clock do bar-

ramento local é de 25 Mhz, cada

pulso de clock demorará 40 ns

(1/f: período é o inverso da fre-

qüência — no caso, 1/25.000.000

= 0,000.000.04 = 40 ns). Isso

significa que o tempo de acesso da

memória deverá ser, no mínimo, de

80 ns, ou seja, uma memória de 70

ns ou mesmo de 60 não funciona-

ria perfeitamente bem nesse micro.

Já em um micro com processador 486DX-33 (ou DX2-66

ou DX4-l00, pois todos trabalham externamente a 33

MHz), cada pulso de clock demorará 30 ns. A memória

deverá ter, no mínimo, 60 ns de tempo de acesso. Ten-

tar utilizar uma memória com um tempo de acesso mai-

or faria com que houvesse travamentos no micro ou até

mesmo que o micro nem ligasse. À medida que o clock

do barramento local aumenta, menor deverá ser o tem-

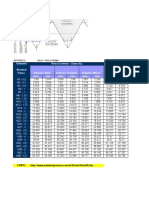

po de acesso da memória. Observe a tabela e o gráfico.

No caso dos processadores que trabalham com 66 MHz de freqüência de operação do barramento local (Pentium—

100, Pentium-133, Pentium-166, Pentium-200 e superiores, ou seja, a maioria dos processadores disponíveis hoje),

PandaTitan Informática Página 3 Manaus / Amazonas

CURSO TÉCNICO EM INFORMÁTICA -Acesso a RAM

Prof.º Adriano Queiroz Sobrinho – 3648-4152 / 9125-9909 – Rua Altair Severiano, 104, Eldorado

a memória deverá ter, no mínimo, 30,3 ns de tempo de acesso! A solução para essa situação — e diversas outras,

como a instalação de memória RAM com 70 ns de tempo de acesso em um simples 486DX-33 — está na utilização

de pulsos de clock extras, chamados wait states. Esses pulsos de clock extras têm como objetivo fazer com que o

processador — que e mais rápido que a memória RAM — espere o tempo necessário para que a memória fique

pronta para receber ou entregar dados, O grande problema é que, durante esse período, o processador fica ocio-

so, fazendo com que haja queda no desempenho. Em outras palavras, como o processador não irá ficar fazendo

nada, estaremos desperdiçando esse tempo de ociosidade, que poderia estar sendo utilizado para executar alguma

tarefa. Estudaremos os wait states e a sua influência no desempenho do micro a seguir.

WAIT STATES

Um wait state é um pulso de clock extra adicionado ao ciclo de leitura ou escrita da memória. Como o ciclo de

acesso à memória RAM dura dois pulsos de clock, com a adição de 1 wait state o ciclo passaria a ter três pulsos de

clock. Se adicionarmos dois wait states ao ciclo de leitura em memória, este passa a ter quatro pulsos de clock de

duração e assim sucessivamente. Aumentar a duração do ciclo de acesso à memória faz com que memórias com

tempos de acesso maiores possam ser utilizadas. Por exemplo, se utilizarmos um processador que trabalhe exter-

namente a 66 Mhz, teremos de adicionar 2 wait states para que o ciclo passe a ser de 60 ns, fazendo com que

memórias com tempo de acesso de 60 ns possam ser utilizadas. Cálculo usado: cada pulso de clock terá 15 ns; a

memória deve ser capaz de responder em dois pulsos de clock, ou seja, em 30 ns. Precisamos adicionar dois pul-

sos extras (ou seja, dois wait states) para que o ciclo passe a ser de 60 ns, fazendo com que memórias de 60 ns

consigam responder. Esse exemplo está esquematizado na figura da próxima página . No caso da utilização de

uma memória com 70 ns de tempo de acesso, teremos de adicionar mais um wait state (ou seja, um total de três

wait states), para que o ciclo de acesso à memória seja de 75 ns e esta possa acompanhar a transferência de da-

dos com o processador. Em outras palavras, para que o processador consiga comunicar-se corretamente com a

memória RAM, o ciclo de leitura deverá ser igual ou maior que o tempo de acesso da memória RAM. Caso isso não

ocorra, e necessária a adição de pulsos de clock extras, chamados wait states. Deverão ser adicionados tantos wait

states quantos forem necessários para que essa condição seja atingida. Nesses exemplos estamos assumindo que

a memória RAM (do tipo assíncrona (FPM ou EDO). As memórias RAM do tipo síncrona (SDRAM) utilizam um mé-

todo de funcionamento diferente. Como são sincronizadas pelo clock do barramento, não apresentam esse tipo de

problema de sincronização. Em compensação, continuam possuindo um tempo de resposta (tempo de acesso. Isto

e, o tempo demorado entre o processador pedir um dado e a memória entregá-lo) relativamente alto, normalmen-

te de dois ou três pulsos de clock (entre 30 e 45 ns, no caso de barramentos de 66Mhz ou 20 e 30 ns, no caso de

barramentos de 100 MHz). Essa característica não é chamada de ‘tempo de acesso “, mas sim latência do CAS. A

utilização de wait states faz com que as lentas memórias dinâmicas consigam ser utilizadas mesmo em micros mais

modernos. No entanto, temos um grande problema: durante um pulso de wait state, o processador fica ocioso,

esperando que a memória esteja pronta para armazenar o próximo dado ou então entregar o)”. (dado) “. solicita-

do. Na utilização de apenas um wait state, reduzimos o desempenho do computador em 1/3: o processador utiliza

três pulsos de clock para acessar à memória, porém somente dois pulsos são efetivamente utilizados; no outro

pulso, o processador fica ocioso. No caso da adição de dois wait states, reduzimos o desempenho em 1/2, ou seja,

50%, pois metade dos pulsos utilizados no acesso à memória não são utilizados. E assim sucessivamente, ou seja,

quanto mais wait states utilizamos, menor será o desempenho do micro. Na Figura temos um gráfico demonstran-

do essa queda de desempenho. É claro que estamos nos referindo ao desempenho exclusivamente do acesso à

memória. Porém, como o processador esta acessando memória na maior parte das vezes, o desempenho total do

micro é brutalmente atingido. Utilizar memória com o menor tempo de acesso possível faz com que o micro utilize

menos wait states, melhorando o problema de desempenho. Contudo, mesmo utilizando as memórias dinâmicas”.

assíncronas mais rápidas existentes no mercado, não é possível acessar a memória sem utilizar wait states. Se

você resolver trocar a memória de seu micro por uma com tempo de acesso menor, não se esqueça de configurar

o micro de forma que ele efetivamente utilize menos Wait States. Caso Contrario, o micro continuara utilizando o

mesmo nu/mero de wait states que estava configurado anteriormente. mesmo que você tenha trocado as memó-

rias por modelos mais rápidos. Em outras palavras, trocar simplesmente sua memória de 70 ns de tempo de aces-

so por uma de 60ns não fará com que o seu micro fique mais rápido; você deverá reconfigurar o numero de wait

states no setup da BIOS do micro. A solução para o impacto no desempenho é a utilização de uma memória que

consiga “falar” com o processador na mesma velocidade — a memória estática. Utilizamos uma pequena quantida-

de de memória estática no micro: o cache de memória. Quando o processador for armazenar ou buscar dados, ele

estará na verdade “conversando” com a memória cache (memória estática), e não com a memória dinâmica, fa-

PandaTitan Informática Página 4 Manaus / Amazonas

CURSO TÉCNICO EM INFORMÁTICA -Acesso a RAM

Prof.º Adriano Queiroz Sobrinho – 3648-4152 / 9125-9909 – Rua Altair Severiano, 104, Eldorado

zendo com que ele não precise utilizar wait states e, conseqüentemente, não comprometendo o desempenho no

micro. Em pelo menos 60% a 80% do tempo o processador acessa a memória cache e não a memória RAM. Nos

exemplos práticos que demos, em um micro com processador que trabalhe a 66 MHz e utilize dois wait states

(memória de 60 ns), a conversa do processador com a memória equivale a um processador trabalhando externa-

mente a apenas 33 MHz. No caso da utilização de cinco wait states (memória de 70 ns), o desempenho seria de

um processador trabalhando a apenas 26,4 MHz. Colocamos esses valores para você se impressionar e perceber

que atualmente não podemos dispensar o uso do cache de memória. Quanto maior a freqüência de operação do

barramento local (isto é, a freqüência externa do processador), pior é essa situação. Novas tecnologias — como a

EDO e a SDRAM — tiveram de ser criadas para diminuir a quantidade de wait states utilizada pelo processador no

acesso a memória RAM, como veremos. É importante notar que todos esses cálculos são teóricos. A utilização do

controlador de memória RAM gera um atraso no sinal enviado pelo processador, que acaba aumentando o tempo

de acesso da memória RAM da maneira que é vista pelo processador. Por causa dessa situação, uma memória de

70 ns pode ter o efeito de uma memória de 75 ou 80 ns de tempo de acesso. As especificações técnicas do chipset

(ponte norte) trazem o período mínimo de acesso à memória RAM, expressa em pulsos de clock. Além disso, mais

importante do que saber o tempo de acesso da memória RAM, é saber o seu tempo de ciclo de acesso aleatório

(também chamado TRC). Esse valor mede a capacidade de dois acessos consecutivos a endereços diferentes da

memória RAM e varia de acordo com o tipo de circuito, modelo e fabricante. Por exemplo, um circuito de memória

FPM de 70 ns tipicamente possui um tempo de ciclo de 130 ns (esse tempo cai para 110 ns se a memória for de 60

ns). Isso quer dizer que dois acessos consecutivos à memória RAM deverão possuir um espaço de tempo de 130

ns entre eles! Nesse caso, o processador terá de esperar ainda mais!

PandaTitan Informática Página 5 Manaus / Amazonas

CURSO TÉCNICO EM INFORMÁTICA -Acesso a RAM

Prof.º Adriano Queiroz Sobrinho – 3648-4152 / 9125-9909 – Rua Altair Severiano, 104, Eldorado

NOVAS TECNOLOGIAS DE MEMÓRIA RAM

Mesmo não podendo baixar o tempo de acesso da memória dinâmica (sobretudo por causa da necessidade de

ciclos de refresh), os fabricantes conseguiram desenvolver diversas novas tecnologias de construção de circuitos

de memória RAM. Embora tenha o mesmo tempo de acesso, (circuitos com tecnologias de construção) diferentes

podem apresentar velocidades diferentes. Uma memória EDO, por exemplo, e mais rápida que uma memória FPM,

mesmo quando as duas apresentam o mesmo tempo ele acesso. Quando dizemos “tecnologia de construção de

memória‘, estamos nos referindo ao tipo de circuito integrado de memória utilizado (FPM, EDO, BEDO. SDRAM,

RDRAM). Estes circuitos poderão ser montados em qualquer tipo de módulo de memória, em especial SIMM-72 e

DIMM — ou seja,você pode encontrar módulos de memória SIMM-72 ou DIMM construídos utilizando circuitos

FPM, EDO, BEDO ou SDRAM. Muitos leigos confundem os dois grupos, não entendendo a diferença entre um mó-

dulo SIMM e um” módulo EDO “(não existe esse tipo de módulo, embora a memória EDO possa ser utilizada em

módulo SIMM)”.

PandaTitan Informática Página 6 Manaus / Amazonas

Você também pode gostar

- Como Efetuar Testes Na Placa T-CON Dos Televisores LG - PORTAL DA ELETRÔNICAComo Efetuar Testes Na Placa T-CON Dos Televisores LG - PORTAL DA ELETRÔNICADocumento6 páginasComo Efetuar Testes Na Placa T-CON Dos Televisores LG - PORTAL DA ELETRÔNICAComo Efetuar Testes Na Placa T-CON Dos Televisores LG - PORTAL DA ELETRÔNICAAlã Matos BarbosaAinda não há avaliações

- Electrolux LT 50 e 60 - Desmontagem e Testes Dos ComponentesDocumento26 páginasElectrolux LT 50 e 60 - Desmontagem e Testes Dos Componentesajaquilante67% (3)

- Atalhos Do TecladoDocumento17 páginasAtalhos Do TecladoRodrigo Chaves100% (1)

- Procedimento de Reset Dos Dados de NC e PLC PDFDocumento6 páginasProcedimento de Reset Dos Dados de NC e PLC PDFTheo SouzaAinda não há avaliações

- Diagnóstico do sistema CFI através de códigos de pisca e memóriasDocumento44 páginasDiagnóstico do sistema CFI através de códigos de pisca e memóriasEder santosAinda não há avaliações

- Se 284 PDFDocumento68 páginasSe 284 PDFCesarLimaAinda não há avaliações

- Análise de Risco Construção CivilDocumento6 páginasAnálise de Risco Construção CivilVanderclan QuarantaAinda não há avaliações

- Hardware - Montagem - TECLADODocumento5 páginasHardware - Montagem - TECLADOapi-3813826100% (2)

- Hardware - Montagem - Verdadeiro FuncionamentoDocumento3 páginasHardware - Montagem - Verdadeiro Funcionamentoapi-3813826Ainda não há avaliações

- Hardware - Montagem - Seriais e ParalelaDocumento5 páginasHardware - Montagem - Seriais e Paralelaapi-3813826100% (1)

- Hardware - Montagem - Sistemas de VideoDocumento10 páginasHardware - Montagem - Sistemas de Videoapi-3813826100% (1)

- Hardware - Montagem - PLACAS de SOMDocumento14 páginasHardware - Montagem - PLACAS de SOMapi-3813826100% (4)

- Hardware - Montagem - MouseDocumento4 páginasHardware - Montagem - Mouseapi-3813826100% (2)

- Hardware - Montagem - Placa Mãe - ReforçoDocumento3 páginasHardware - Montagem - Placa Mãe - Reforçoapi-3813826100% (1)

- Hardware - Montagem - Process Adores 6º GeraçãoDocumento12 páginasHardware - Montagem - Process Adores 6º Geraçãoapi-3813826100% (1)

- Hardware - Montagem - Gerenciamento ElétricoDocumento10 páginasHardware - Montagem - Gerenciamento Elétricoapi-3813826100% (2)

- Hardware - Montagem - O MonitorDocumento5 páginasHardware - Montagem - O Monitorapi-3813826100% (1)

- Hardware - Montagem - HD - IDE - PartiçõesDocumento7 páginasHardware - Montagem - HD - IDE - Partiçõesapi-3813826Ainda não há avaliações

- Hardware - Montagem - Memória - Chipsets e Circuitos de ApDocumento8 páginasHardware - Montagem - Memória - Chipsets e Circuitos de Apapi-3813826100% (2)

- Hardware - Montagem - FDISKDocumento5 páginasHardware - Montagem - FDISKapi-3813826100% (1)

- MSN 2Documento1 páginaMSN 2api-3813826Ainda não há avaliações

- Pasta 1Documento1 páginaPasta 1api-3813826Ainda não há avaliações

- ScrapDocumento1 páginaScrapapi-3813826Ainda não há avaliações

- A Bofetada Do Ano (Som)Documento16 páginasA Bofetada Do Ano (Som)api-26743468Ainda não há avaliações

- Mariana FraijiDocumento2 páginasMariana Fraijiapi-3813826Ainda não há avaliações

- Confie 1Documento6 páginasConfie 1api-3813826Ainda não há avaliações

- ConversaDocumento6 páginasConversaapi-3813826Ainda não há avaliações

- Amigosparasempre IvaelDocumento4 páginasAmigosparasempre Ivaelapi-3706703Ainda não há avaliações

- Normas Elementos FixaçãoDocumento6 páginasNormas Elementos FixaçãoGuilherme MendonçaAinda não há avaliações

- Controle Máquina XXXX - JunhoDocumento11 páginasControle Máquina XXXX - JunhoAdriana CaldasAinda não há avaliações

- Cilindro de deslocamento lateral - remoção e instalaçãoDocumento8 páginasCilindro de deslocamento lateral - remoção e instalaçãoDouglas FernandesAinda não há avaliações

- Tarefa 1: O Conceito de Multimédia. Tecnologias Multimédia. Recursos Necessários.Documento18 páginasTarefa 1: O Conceito de Multimédia. Tecnologias Multimédia. Recursos Necessários.clourecoAinda não há avaliações

- Arduino UNO - Conheça o Hardware Da Placa Arduino em DetalhesDocumento23 páginasArduino UNO - Conheça o Hardware Da Placa Arduino em DetalhesJudáAmorimAinda não há avaliações

- Manual Do Usuário GNSS South Galaxy G1plus - PTBRDocumento102 páginasManual Do Usuário GNSS South Galaxy G1plus - PTBRRicardo Marcel UescarAinda não há avaliações

- Análise de falhas no circuito de fonte do televisor LC3246(B)WDADocumento12 páginasAnálise de falhas no circuito de fonte do televisor LC3246(B)WDAGilmar FerreiraAinda não há avaliações

- Avaliação Final Imc 1FDocumento1 páginaAvaliação Final Imc 1Fjose tartanharAinda não há avaliações

- Circuitos AritmeticosDocumento44 páginasCircuitos AritmeticosFrancisco SantosAinda não há avaliações

- Windows ALL AIO 287in1 (x86x64) (Dezembro2021)Documento6 páginasWindows ALL AIO 287in1 (x86x64) (Dezembro2021)Domingos CristóvãoAinda não há avaliações

- Conceitos Básicos de Operação Com Arquivos No Sistema Operacional Linux (Ubuntu Versão 14 Ou Superior)Documento8 páginasConceitos Básicos de Operação Com Arquivos No Sistema Operacional Linux (Ubuntu Versão 14 Ou Superior)Lucas SosnitzkiAinda não há avaliações

- Configurar xkey REV7-2Documento4 páginasConfigurar xkey REV7-2lordpixelsAinda não há avaliações

- Ofertas de eletrônicos e acessóriosDocumento26 páginasOfertas de eletrônicos e acessóriosdavidAinda não há avaliações

- Procedimento Geração SISPAG Itau 999999Documento2 páginasProcedimento Geração SISPAG Itau 999999csescobarAinda não há avaliações

- Computadores e InformaçãoDocumento14 páginasComputadores e InformaçãoFrancisco Manuel JoaoAinda não há avaliações

- Principais Serviços Do LinuxDocumento2 páginasPrincipais Serviços Do LinuxAugusto CerqueiraAinda não há avaliações

- Manual HDD Re GeneratorDocumento5 páginasManual HDD Re GeneratorGuilherme GonzalezAinda não há avaliações

- Contagem até o infinito e protocolos DVDocumento7 páginasContagem até o infinito e protocolos DVChristian Aparecido PedrosoAinda não há avaliações

- LinuxDocumento96 páginasLinuxMagno MachadoAinda não há avaliações

- Programas Analise Acustica PDFDocumento10 páginasProgramas Analise Acustica PDFSadraque OliveiraAinda não há avaliações

- Lista de Ci's para Gravadora WillemDocumento6 páginasLista de Ci's para Gravadora WillemPREVISTOAinda não há avaliações

- Arrancadores Suaves PseDocumento196 páginasArrancadores Suaves PseVladimir Jhobanny Chivata100% (3)

- Material Didático FranzininhoDocumento24 páginasMaterial Didático FranzininhorurounikenshinAinda não há avaliações