Escolar Documentos

Profissional Documentos

Cultura Documentos

A 6275 Eat

Enviado por

n_t_162Descrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

A 6275 Eat

Enviado por

n_t_162Direitos autorais:

Formatos disponíveis

6275

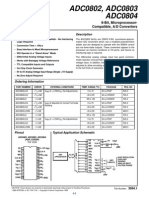

8-BIT SERIAL-INPUT, CONSTANTCURRENT LATCHED LED DRIVER

A6275ELW

GROUND SERIAL DATA IN CLOCK LATCH ENABLE OUT 0 OUT 1 OUT 2 OUT 3 1 2 3 4 5 6 7 8 CK L REGISTER LATCHES 12 11 10 9 OE VDD IO REGULATOR 16 15 14 13 LOGIC SUPPLY REXT SERIAL DATA OUT OUTPUT ENABLE OUT 7 OUT 6 OUT 5 OUT 4

The A6275EA and A6275ELW are specifically designed for LEDdisplay applications. Each BiCMOS device includes an 8-bit CMOS shift register, accompanying data latches, and eight npn constantcurrent sink drivers. Except for package style and allowable package power dissipation, the two devices are identical. The CMOS shift register and latches allow direct interfacing with microprocessor-based systems. With a 5 V logic supply, typical serial data-input rates are up to 20 MHz. The LED drive current is determined by the users selection of a single resistor. A CMOS serial data output permits cascade connections in applications requiring additional drive lines. For inter-digit blanking, all output drivers can be disabled with an ENABLE input high. Similar 16-bit devices are available as the A6276EA and A6276ELW. Two package styles are provided for through-hole DIP (suffix A) or surface-mount SOIC (suffix LW). Under normal applications, copper lead frames and low logic-power dissipation allow these devices to sink maximum rated current through all outputs continuously over the operating temperature range (90 mA, 0.9 V drop, +85C). Both devices are also available for operation over the standard temperature range of -20C to +85C. To order, change the suffix letter E to S.

Data Sheet 26185.200

Dwg. PP-029-10

Note that the A6275EA (DIP) and the A6275ELW (SOIC) are electrically identical and share a common terminal number assignment.

ABSOLUTE MAXIMUM RATINGS

Supply Voltage, VDD ...................... 7.0 V Output Voltage Range, VO ............................ -0.5 V to +17 V Output Current, IO ........................ 90 mA Ground Current, IGND ................. 750 mA Input Voltage Range, VI .................... -0.4 V to VDD + 0.4 V Package Power Dissipation, PD ..................................... See Graph Operating Temperature Range, TA ............................. -40C to +85C Storage Temperature Range, TS ........................... -55C to +150C

Caution: These CMOS devices have input static protection (Class 2) but are still susceptible to damage if exposed to extremely high static electrical charges.

FEATURES

I I I I I To 90 mA Constant-Current Outputs Under-Voltage Lockout Low-Power CMOS Logic and Latches High Data Input Rate Pin-Compatible with TB62705CP

Always order by complete part number, e.g., A6275EA .

6275 8-BIT SERIAL-INPUT, CONSTANT-CURRENT LATCHED LED DRIVER

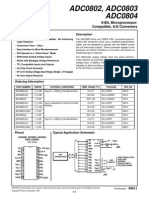

ALLOWABLE PACKAGE POWER DISSIPATION IN WATTS

2.5

2.0

SUFFIX 'A', R JA = 60C/W

1.5

1.0

SUFFIX 'LW', R

0.5

JA

= 80C/W

0 25

50 75 100 125 AMBIENT TEMPERATURE IN C

150

Dwg. GP-018B

FUNCTIONAL BLOCK DIAGRAM

VDD CLOCK SERIAL DATA IN LATCH ENABLE

UVLO

LOGIC SUPPLY SERIAL DATA OUT

SERIAL-PARALLEL SHIFT REGISTER

LATCHES OUTPUT ENABLE (ACTIVE LOW) MOS BIPOLAR

GROUND

IO REGULATOR

EXT

OUT 0 OUT 1 OUT 2

OUT N

Dwg. FP-013-3

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000 Copyright 2000, Allegro MicroSystems, Inc.

6275 8-BIT SERIAL-INPUT, CONSTANT-CURRENT LATCHED LED DRIVER

DD

DD

IN

IN

Dwg. EP-010-7

Dwg. EP-010-6

OUTPUT ENABLE (active low)

VDD

LATCH ENABLE

VDD

IN

OUT

Dwg. EP-063-1

Dwg. EP-010-5

CLOCK and SERIAL DATA IN TRUTH TABLE

Serial Shift Register Contents Data Clock Input Input I1 I2 I3 ... IN-1 IN H L X H L R1 R2 ... R1 R2 ... RN-2 RN-1 RN-2 RN-1 RN-1 RN X X Serial Latch Data Enable Output Input RN-1 RN-1 RN X PN L H R1 R2 R3 ... P1 P2 P3 ... X L = Low Logic (Voltage) Level H = High Logic (Voltage) Level X X ... Latch Contents I1 I2 I3 ...

SERIAL DATA OUT

IN-1 IN

Output Enable Input

Output Contents I1 I2 I3 ... IN-1 IN

R1 R2 R3 ... X X X ...

RN-1 RN PN-1 PN X X L H P1 P2 P3 ... PN-1 PN H H H ... H R = Previous State H

P1 P2 P3 ...

PN-1 PN

X = Irrelevant

P = Present State

www.allegromicro.com

6275 8-BIT SERIAL-INPUT, CONSTANT-CURRENT LATCHED LED DRIVER

ELECTRICAL CHARACTERISTICS at TA = +25C, VDD = 5 V (unless otherwise noted).

Limits Characteristic Supply Voltage Range Under-Voltage Lockout Output Current (any single output) Output Current Matching (difference between any two outputs at same VCE) Output Leakage Current Logic Input Voltage ICEX VIH VIL SERIAL DATA OUT Voltage Input Resistance VOL VOH RI IOL = 500 A IOH = -500 4A ENABLE Input, Pull Up LATCH Input, Pull Down Supply Current IDD(OFF) REXT = open, VOE = 5 V REXT = 470 , VOE = 5 V REXT = 250 , VOE = 5 V IDD(ON) REXT = 470 , VOE = 0 V REXT = 250 , VOE = 0 V Typical Data is at VDD = 5 V and is for design information only. Symbol VDD VDD(UV) IO Test Conditions Operating VDD = 0 5 V VCE = 0.7 V, REXT = 250 VCE = 0.7 V, REXT = 470 IO 0.4 V VCE(A) = VCE(B) 0.7 V: REXT = 250 REXT = 470 VOH = 15 V 0.7VDD GND 4.6 150 100 3.5 6.5 5.0 8.0 1.5 1.5 1.0 300 200 0.8 6.0 11 10 16 6.0 6.0 5.0 VDD 0.3VDD 0.4 600 400 1.4 8.0 15 14 24 % % A V V V V k k mA mA mA mA mA Min. 4.5 3.4 64.2 34.1 Typ. 5.0 75.5 40.0 Max. 5.5 4.0 86.8 45.9 Unit V V mA mA

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000

6275 8-BIT SERIAL-INPUT, CONSTANT-CURRENT LATCHED LED DRIVER

SWITCHING CHARACTERISTICS at TA = 25C, VDD = VIH = 5 V, VCE = 0.4 V, VIL = 0 V, REXT = 470 , IO = 40 mA, VL = 3 V, RL = 65 , CL = 10.5 pF.

Limits Characteristic Propagation Delay Time Symbol tpHL Test Conditions CLOCK-OUTn LATCH-OUTn ENABLE-OUTn CLOCK-SERIAL DATA OUT Propagation Delay Time tpLH CLOCK-OUTn LATCH-OUTn ENABLE-OUTn CLOCK-SERIAL DATA OUT Output Fall Time Output Rise Time tf tr 90% to 10% voltage 10% to 90% voltage Min. 150 150 Typ. 350 350 350 80 300 300 300 80 350 300 Max. 1000 1000 1000 110 1000 1000 1000 110 1000 600 Unit ns ns ns ns ns ns ns ns ns ns

RECOMMENDED OPERATING CONDITIONS

Characteristic Supply Voltage Output Voltage Output Current Symbol VDD VO IO IOH IOL Logic Input Voltage VIH VIL Clock Frequency fCK Cascade operation Continuous, any one output SERIAL DATA OUT SERIAL DATA OUT Conditions Min. 4.5 0.7VDD -0.3 Typ. 5.0 1.0 Max. 5.5 4.0 90 -1.0 1.0 VDD + 0.3 0.3VDD 10 Unit V V mA mA mA V V MHz

www.allegromicro.com

6275 8-BIT SERIAL-INPUT, CONSTANT-CURRENT LATCHED LED DRIVER

TIMING REQUIREMENTS and SPECIFICATIONS

(Logic Levels are VDD and Ground)

C CLOCK A SERIAL DATA IN DATA tp SERIAL DATA OUT D LATCH ENABLE

50% 50% 50%

B

50%

DATA E

OUTPUT ENABLE

LOW = ALL OUTPUTS ENABLED

tp OUT N

HIGH = OUTPUT OFF

50%

DATA

LOW = OUTPUT ON

Dwg. WP-029-1

HIGH = ALL OUTPUTS DISABLED (BLANKED) OUTPUT ENABLE

50%

F t en(BQ)

90%

t dis(BQ) tf DATA

10%

tr

OUT N

Dwg. WP-030-1

A. Data Active Time Before Clock Pulse (Data Set-Up Time), tsu(D) .......................................... 60 ns B. Data Active Time After Clock Pulse (Data Hold Time), th(D) .............................................. 20 ns C. Clock Pulse Width, tw(CK) ............................................... 50 ns D. Time Between Clock Activation and Latch Enable, tsu(L) ............................................ 100 ns E. Latch Enable Pulse Width, tw(L) ................................... 100 ns F. Output Enable Pulse Width, tw(OE) ................................ 4.5 s NOTE Timing is representative of a 10 MHz clock. Significantly higher speeds are attainable. Max. Clock Transition Time, tr or tf .............................. 10 s

Information present at any register is transferred to the respective latch when the LATCH ENABLE is high (serial-toparallel conversion). The latches will continue to accept new data as long as the LATCH ENABLE is held high. Applications where the latches are bypassed (LATCH ENABLE tied high) will require that the OUTPUT ENABLE input be high during serial data entry. When the OUTPUT ENABLE input is high, the output source drivers are disabled (OFF). The information stored in the latches is not affected by the OUTPUT ENABLE input. With the OUTPUT ENABLE input low, the outputs are controlled by the state of their respective latches.

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000

6275 8-BIT SERIAL-INPUT, CONSTANT-CURRENT LATCHED LED DRIVER

ALLOWABLE OUTPUT CURRENT AS A FUNCTION OF DUTY CYCLE A6275EA A6275ELW

100 VCE = 2 V

100 VCE = 1 V

ALLOWABLE OUTPUT CURRENT IN mA/BIT

ALLOWABLE OUTPUT CURRENT IN mA/BIT

80

VCE = 3 V

VCE = 2 V 80 VCE = 3 V

VCE = 4 V 60

60

VCE = 4 V

40

40

20

TA = +25C VDD = 5 V RJA = 60C/W

20

TA = +25C VDD = 5 V RJA = 80C/W

0 0 20 40 60 80 100

Dwg. GP-062-5

0 0 20 40 60 80 100

Dwg. GP-062-4

DUTY CYCLE IN PER CENT

DUTY CYCLE IN PER CENT

100 VCE = 2 V

100 VCE = 1 V

ALLOWABLE OUTPUT CURRENT IN mA/BIT

ALLOWABLE OUTPUT CURRENT IN mA/BIT

80

VCE = 3 V

80 VCE = 3 V 60 VCE = 4 V

VCE = 2 V

60

VCE = 4 V

40

40

20

TA = +50C VDD = 5 V RJA = 60C/W

20

TA = +50C VDD = 5 V RJA = 80C/W

0 0 20 40 60 80 100

Dwg. GP-062-3

0 0 20 40 60 80 100

Dwg. GP-062-2

DUTY CYCLE IN PER CENT

DUTY CYCLE IN PER CENT

www.allegromicro.com

6275 8-BIT SERIAL-INPUT, CONSTANT-CURRENT LATCHED LED DRIVER

ALLOWABLE OUTPUT CURRENT AS A FUNCTION OF DUTY CYCLE (cont.) A6275EA A6275ELW

100 VCE = 1 V

100 VCE = 0.7 V

ALLOWABLE OUTPUT CURRENT IN mA/BIT

ALLOWABLE OUTPUT CURRENT IN mA/BIT

80

VCE = 2 V

80

VCE = 1 V

VCE = 3 V 60 VCE = 4 V 40

VCE = 2 V 60 VCE = 3 V

40

VCE = 4 V

20

TA = +85C VDD = 5 V RJA = 60C/W

20

TA = +85C VDD = 5 V RJA = 80C/W

0 0 20 40 60 80 100

Dwg. GP-062-1

0 0 20 40 60 80 100

Dwg. GP-062

DUTY CYCLE IN PER CENT

DUTY CYCLE IN PER CENT

TYPICAL CHARACTERISTICS

60

OUTPUT CURRENT IN mA/BIT

40

20

TA = +25C REXT = 500

0 0 0.5 1.0 VCE IN VOLTS

Dwg. GP-063

1.5

2.0

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000

6275 8-BIT SERIAL-INPUT, CONSTANT-CURRENT LATCHED LED DRIVER

TERMINAL DESCRIPTION

Terminal No. 1 2 3 4 5-12 13 14 15 16 Terminal Name GND SERIAL DATA IN CLOCK LATCH ENABLE OUT0-7 OUTPUT ENABLE SERIAL DATA OUT REXT SUPPLY Function Reference terminal for control logic. Serial-data input to the shift-register. Clock input terminal for data shift on rising edge. Data strobe input terminal; serial data is latched with high-level input. The eight current-sinking output terminals. When (active) low, the output drivers are enabled; when high, all output drivers are turned OFF (blanked). CMOS serial-data output to the following shift-register. An external resistor at this terminal establishes the output current for all sink drivers. (VDD) The logic supply voltage (typically 5 V).

The products described here are manufactured under one or more U.S. patents or U.S. patents pending. Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current. Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

www.allegromicro.com

6275 8-BIT SERIAL-INPUT, CONSTANT-CURRENT LATCHED LED DRIVER

Applications Information

The load current per bit (IO) is set by the external resistor (REXT) as shown in the figure below.

100

VCE = 0.7 V 80

0.7 V per diode) for a group of drivers. If the available voltage source will cause unacceptable dissipation and series resistors or diode(s) are undesirable, a regulator such as the Sanken Series SAI or Series SI can be used to provide supply voltages as low as 3.3 V. For reference, typical LED forward voltages are: Blue 3.0 4.0 V Green 1.8 2.2 V Yellow 2.0 2.1 V Amber 1.9 2.65 V Red 1.6 2.25 V Infrared 1.2 1.5 V Pattern Layout. This device has a common logicground and power-ground terminal. If ground pattern layout contains large common-mode resistance, and the voltage between the system ground and the LATCH ENABLE or CLOCK terminals exceeds 2.5 V (because of switching noise), these devices may not operate correctly.

OUTPUT CURRENT IN mA/BIT

60

40

20

0 100

200

300

500

700

1k

EXT

2k

3k

5k

CURRENT-CONTROL RESISTANCE, R

IN OHMS

Dwg. GP-061

Package Power Dissipation (PD). The maximum allowable package power dissipation is determined as PD(max) = (150 - TA)/RJA. The actual package power dissipation is PD(act) = dc(VCE IO 8) + (VDD IDD). When the load supply voltage is greater than 3 V to 5 V, considering the package power dissipating limits of these devices, or if PD(act) > PD(max), an external voltage reducer (VDROP) should be used. Load Supply Voltage (VLED). These devices are designed to operate with driver voltage drops (VCE) of 0.4 V to 0.7 V with LED forward voltages (VF) of 1.2 V to 4.0 V. If higher voltages are dropped across the driver, package power dissipation will be increased significantly. To minimize package power dissipation, it is recommended to use the lowest possible load supply voltage or to set any series dropping voltage (VDROP) as VDROP = VLED - VF - VCE with VDROP = Io RDROP for a single driver, or a Zener diode (VZ), or a series string of diodes (approximately

VLED

V DROP

VF

V CE

Dwg. EP-064

10

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000

6275 8-BIT SERIAL-INPUT, CONSTANT-CURRENT LATCHED LED DRIVER

A6275EA

Dimensions in Inches (controlling dimensions)

0.014 0.008

16

0.430 0.280 0.240

MAX

0.300

BSC

1 0.070 0.045

0.100 0.775 0.735

BSC

8 0.005

MIN

0.210

MAX

0.015

MIN

0.150 0.115 0.022 0.014

Dwg. MA-001-16A in

Dimensions in Millimeters (for reference only)

16

0.355 0.204

10.92 7.11 6.10

MAX

7.62

BSC

1 1.77 1.15

2.54 19.68 18.67

BSC

8 0.13

MIN

5.33

MAX

0.39

MIN

3.81 2.93 0.558 0.356

Dwg. MA-001-16A mm

NOTES: 1. Exact body and lead configuration at vendors option within limits shown. 2. Lead spacing tolerance is non-cumulative 3. Lead thickness is measured at seating plane or below.

www.allegromicro.com

11

6275 8-BIT SERIAL-INPUT, CONSTANT-CURRENT LATCHED LED DRIVER

A6275ELW

Dimensions in Inches (for reference only)

16 9 0.0125 0.0091

0.2992 0.2914

0.419 0.394

0.050 0.016 0.020 0.013

3 0.4133 0.3977

0.050

BSC

0 TO 8

0.0926 0.1043 0.0040 MIN.

Dwg. MA-008-16A in

Dimensions in Millimeters (controlling dimensions)

16 9 0.32 0.23

7.60 7.40

10.65 10.00

1.27 0.40 0.51 0.33

3 10.50 10.10

1.27

BSC

0 TO 8

2.65 2.35 0.10 MIN.

Dwg. MA-008-16A mm

NOTES: 1. Exact body and lead configuration at vendors option within limits shown. 2. Lead spacing tolerance is non-cumulative.

12

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000

Você também pode gostar

- +2.7 V To +5.5 V, 350 KSPS, 10-Bit 4-/8-Channel Sampling AdcsDocumento20 páginas+2.7 V To +5.5 V, 350 KSPS, 10-Bit 4-/8-Channel Sampling AdcsAbhishek ChaudharyAinda não há avaliações

- Ucn 5821 ADocumento7 páginasUcn 5821 ACelso Conceição100% (1)

- DS1307 Real Time ClockDocumento14 páginasDS1307 Real Time Clockpraveen_kodgirwarAinda não há avaliações

- LC Mos High Speed 4-And 8-Channel 8-Bit Adcs Ad7824/Ad7828Documento16 páginasLC Mos High Speed 4-And 8-Channel 8-Bit Adcs Ad7824/Ad7828meroka2000Ainda não há avaliações

- ISL6565A, ISL6565B: Multi-Phase PWM Controller With Precision R or DCR Current Sensing For VR10.X Application FeaturesDocumento28 páginasISL6565A, ISL6565B: Multi-Phase PWM Controller With Precision R or DCR Current Sensing For VR10.X Application FeaturesFranciscoGomezAinda não há avaliações

- tsc2046 DsDocumento32 páginastsc2046 DsBobby ChippingAinda não há avaliações

- MC 14521Documento12 páginasMC 14521rrebollarAinda não há avaliações

- 40V Precision Low Power Operational Amplifiers: ISL28117, ISL28217 FeaturesDocumento25 páginas40V Precision Low Power Operational Amplifiers: ISL28117, ISL28217 FeaturesNikole Cueva CevallosAinda não há avaliações

- Ca3306 (A, C)Documento17 páginasCa3306 (A, C)notaden1849Ainda não há avaliações

- CD4070B, CD4077B: Features Ordering InformationDocumento29 páginasCD4070B, CD4077B: Features Ordering Informationsuperpuma86Ainda não há avaliações

- CD 74 HCT 164 MDocumento16 páginasCD 74 HCT 164 MfabriziocasAinda não há avaliações

- CD4094BCDocumento7 páginasCD4094BCEdgar MendezAinda não há avaliações

- CA3161EDocumento4 páginasCA3161EAlejandro Borrego DominguezAinda não há avaliações

- CD4553 Datasheet OKDocumento13 páginasCD4553 Datasheet OKCong ThoAinda não há avaliações

- HCF4026B: Decade Counter/Divider With Decoded 7-Segment Display Output and Display EnableDocumento11 páginasHCF4026B: Decade Counter/Divider With Decoded 7-Segment Display Output and Display EnableBima Richardo SihombingAinda não há avaliações

- SN 75174Documento18 páginasSN 75174Odiin Antonhy MarthAinda não há avaliações

- Nte 4013Documento4 páginasNte 4013Codinasound CaAinda não há avaliações

- Semiconductor Technical Data: L SuffixDocumento7 páginasSemiconductor Technical Data: L SuffixMerényi OszkárAinda não há avaliações

- CD54/74HC688, CD54/74HCT688: Features DescriptionDocumento6 páginasCD54/74HC688, CD54/74HCT688: Features Descriptionbhavsar_vaibhavAinda não há avaliações

- Ansys Workbench TutorialsDocumento13 páginasAnsys Workbench Tutorialsmech118Ainda não há avaliações

- Ca3260, Ca3260A: 4Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesDocumento4 páginasCa3260, Ca3260A: 4Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesPaulo Cesar SimonettiAinda não há avaliações

- 2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial InterfaceDocumento20 páginas2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial Interfacejoseleomi_limaAinda não há avaliações

- Ad 7524Documento8 páginasAd 7524Giovanny ContrerasAinda não há avaliações

- Nte 4053Documento4 páginasNte 4053Codinasound CaAinda não há avaliações

- 2.5v - 2.6v Phase Locked DifferantialDocumento15 páginas2.5v - 2.6v Phase Locked DifferantialMehdi RabbaniAinda não há avaliações

- LC MOS Precision Quad SPST Switches ADG411/ADG412/ADG413: 615 V Analog Signal Range V) MW)Documento8 páginasLC MOS Precision Quad SPST Switches ADG411/ADG412/ADG413: 615 V Analog Signal Range V) MW)Fer TgAinda não há avaliações

- Cmos Sram K6T1008C2E Family: Document TitleDocumento11 páginasCmos Sram K6T1008C2E Family: Document TitleOmar LeonAinda não há avaliações

- 750 MHZ, 16 × 16 Analog Crosspoint Switch Adv3226/Adv3227: Features Functional Block DiagramDocumento24 páginas750 MHZ, 16 × 16 Analog Crosspoint Switch Adv3226/Adv3227: Features Functional Block Diagramwcma57Ainda não há avaliações

- 74HC 93 TiDocumento7 páginas74HC 93 TicataclgAinda não há avaliações

- ADC128S022Documento20 páginasADC128S022Jorge WattesAinda não há avaliações

- CD74HC238Documento7 páginasCD74HC238roozbehxoxAinda não há avaliações

- Adc 0804 PDFDocumento18 páginasAdc 0804 PDFCinthya VillenaAinda não há avaliações

- 7LB176Documento22 páginas7LB176Michael LiuAinda não há avaliações

- A5800 and A5801: Discontinued ProductDocumento13 páginasA5800 and A5801: Discontinued Productitamar_123Ainda não há avaliações

- AM26C32CDocumento17 páginasAM26C32Cvanhuong87Ainda não há avaliações

- ADC0802, ADC0803 ADC0804: Features DescriptionDocumento17 páginasADC0802, ADC0803 ADC0804: Features DescriptionSuryananda PadmadinataAinda não há avaliações

- 7805 Regulator DescriptionDocumento4 páginas7805 Regulator DescriptionyeateshwarriorAinda não há avaliações

- FAN73832 (Half-Bridge Dead Time Control)Documento16 páginasFAN73832 (Half-Bridge Dead Time Control)Ismael StarkAinda não há avaliações

- Adc0804 PDFDocumento16 páginasAdc0804 PDFbudicw0% (1)

- 14-Channel Programmable Switchable I C TFT-LCD Reference Voltage Generator With Integrated 4-Channel Static Gamma Drivers FeaturesDocumento10 páginas14-Channel Programmable Switchable I C TFT-LCD Reference Voltage Generator With Integrated 4-Channel Static Gamma Drivers FeaturesRepararelcd LcdAinda não há avaliações

- CD22100 - DataSheetDocumento10 páginasCD22100 - DataSheetHao ChungAinda não há avaliações

- Ad7524 Ep PDFDocumento8 páginasAd7524 Ep PDFjlfepeAinda não há avaliações

- DG 201Documento9 páginasDG 201Brzata PticaAinda não há avaliações

- AD775Documento12 páginasAD775Shiwam IsrieAinda não há avaliações

- Irf 630Documento7 páginasIrf 630Uriel EutimioAinda não há avaliações

- ADP3180Documento20 páginasADP3180chrizzcloAinda não há avaliações

- 196 124334 HT16C21Documento34 páginas196 124334 HT16C21jeeep32Ainda não há avaliações

- Octal Configurable Low/High Side Driver: DescriptionDocumento18 páginasOctal Configurable Low/High Side Driver: DescriptionDan Esenther100% (1)

- OpAmp - MCP6241Documento28 páginasOpAmp - MCP6241Ludwig SchmidtAinda não há avaliações

- D D D D D D D D D D D D: CD4066B Cmos Quad Bilateral SwitchDocumento20 páginasD D D D D D D D D D D D: CD4066B Cmos Quad Bilateral SwitchAnna Kaye Sapanhila AninAinda não há avaliações

- DatasheetDocumento13 páginasDatasheetkishore kumarAinda não há avaliações

- CD4047Documento9 páginasCD4047Haryadi VjAinda não há avaliações

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsAinda não há avaliações

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1No EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Nota: 2.5 de 5 estrelas2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Ainda não há avaliações

- SPA-ZC22 Bus connection module User's manualDocumento8 páginasSPA-ZC22 Bus connection module User's manualTrần ĐìnhAinda não há avaliações

- 2924-ATT-1388C-PCD-0001 - R0.1 - FAT Procedure For HVAC PanelDocumento14 páginas2924-ATT-1388C-PCD-0001 - R0.1 - FAT Procedure For HVAC PanelAdrian IrawanAinda não há avaliações

- Irg 4 PC 40 UdDocumento11 páginasIrg 4 PC 40 Udait ijjaAinda não há avaliações

- 226B3 MWD00899 e PDFDocumento33 páginas226B3 MWD00899 e PDFamanda amandaAinda não há avaliações

- GE OHV AC Control System Events For 17KG537 and Counters - ProlfilesDocumento74 páginasGE OHV AC Control System Events For 17KG537 and Counters - ProlfilesFrancisco Tello Montero100% (1)

- Field Effect TransistorDocumento117 páginasField Effect TransistorChristine Torrepenida RasimoAinda não há avaliações

- Berrys TransrformerDocumento3 páginasBerrys Transrformerjamil670Ainda não há avaliações

- Yai Kaeps80000123 PDFDocumento536 páginasYai Kaeps80000123 PDFIrving CurasantaAinda não há avaliações

- Electrical Design Analysis for a Two Storey ResidenceDocumento3 páginasElectrical Design Analysis for a Two Storey ResidencePaeng PaloganAinda não há avaliações

- A1n1 MM en PDFDocumento12 páginasA1n1 MM en PDFluis tocoraAinda não há avaliações

- RL Optica P 80 Led PDFDocumento1 páginaRL Optica P 80 Led PDFDek AmeAinda não há avaliações

- TT2190LS: Color TV Horizontal Deflection Output ApplicationsDocumento4 páginasTT2190LS: Color TV Horizontal Deflection Output ApplicationsFreddyAinda não há avaliações

- Silo - Tips - Tigertronics Signalink Usb Digital Interface Cable Interface ListingDocumento15 páginasSilo - Tips - Tigertronics Signalink Usb Digital Interface Cable Interface ListingLoop AntenasAinda não há avaliações

- G8U1E4 Gherkin Lamp - Its A PickleDocumento1 páginaG8U1E4 Gherkin Lamp - Its A PickleGiacomoAinda não há avaliações

- R.M.K. College of Engineering and TechnologyDocumento7 páginasR.M.K. College of Engineering and TechnologyvlkumashankardeekshithAinda não há avaliações

- 11kV CB Control Panel Scheme DrawingDocumento6 páginas11kV CB Control Panel Scheme Drawingshaik gouseAinda não há avaliações

- Synchronous Rectification For Forward ConvertersDocumento19 páginasSynchronous Rectification For Forward ConvertersfabianoaddorAinda não há avaliações

- 15-Step Digital Power SupplyDocumento2 páginas15-Step Digital Power Supplyapi-3736447100% (1)

- 2001 SEBRING/STRATUS Chime Diagnosis GuideDocumento4 páginas2001 SEBRING/STRATUS Chime Diagnosis GuideMuhammad Januar SusantoAinda não há avaliações

- MCQ in Philippine Electrical Code PEC Part 1 REE Board Exam PDFDocumento20 páginasMCQ in Philippine Electrical Code PEC Part 1 REE Board Exam PDFLee Robert OlivarAinda não há avaliações

- NEC Sizing ConductorsDocumento18 páginasNEC Sizing ConductorsAriel DimacaliAinda não há avaliações

- Makita Vista Explodida.Documento2 páginasMakita Vista Explodida.Mauro SérgioAinda não há avaliações

- CapacitorsDocumento24 páginasCapacitorsRatnesh Chandra PandeyAinda não há avaliações

- Elotrain Course "Semiconductor Components"Documento198 páginasElotrain Course "Semiconductor Components"A aaa AaaAinda não há avaliações

- AO4801ADocumento5 páginasAO4801AAlfredo Valencia RodriguezAinda não há avaliações

- Lundahl: Amorphous Core Moving Coil Input Transformer LL1931Documento1 páginaLundahl: Amorphous Core Moving Coil Input Transformer LL1931Giapy Phuc TranAinda não há avaliações

- 14 Sensor Vibration Switch Sw-18010pDocumento2 páginas14 Sensor Vibration Switch Sw-18010pgreg rezaAinda não há avaliações

- SSL Mixbus Compressor CloneDocumento11 páginasSSL Mixbus Compressor CloneShane CampbellAinda não há avaliações

- 2SD2137, 2SD2137A: Silicon NPN Triple Diffusion Planar TypeDocumento3 páginas2SD2137, 2SD2137A: Silicon NPN Triple Diffusion Planar TypeLuis Eduardo Martinez RuizAinda não há avaliações

- Tmi-Sti3508 C708881Documento7 páginasTmi-Sti3508 C708881Fafa MangstabAinda não há avaliações