Escolar Documentos

Profissional Documentos

Cultura Documentos

Elexa 11 M 6

Enviado por

Anuj BodheDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Elexa 11 M 6

Enviado por

Anuj BodheDireitos autorais:

Formatos disponíveis

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology

(An Autonomous Institute affiliated to University of Pune)

Structure & Syllabus of

B.E. (Electronics)

Pattern A11 Effective from Academic Year 2011-12

Prepared by: - Board of Studies in Electronics Engineering Approved by: - Academic Board, Vishwakarma Institute of Technology, Pune

Signed by,

Chairman BOS

Chairman Academic Board

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 1

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

Content

Sr. No.

1 2

Title

Program Educational Objectives ! Course Structure & Syllabi for Courses - Module I & Module II

Page No.

6

Module III

3 4 4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8 4.9 4.10 4.11 4.12 4.13 5 6 6.1 6.2 6.3 6.4 6.5 6.6 EC21101 EC20105 EC20106 EC20107 EC21201 EC20203 Course Structure Course Syllabi For Courses - Module III

EC20101 EC20102 EC20103 EC20104 EC20201 EC20202 EC20301 EC20302 EC27401 EC243XX EC20401

7 8

Theory Course Semiconductor Devices And Circuits Analog Communication Linear Algebra And Statistics Signals And Systems Tutorial Semiconductor Devices And Circuits Analog Communication Practicals Semiconductor Devices & Circuits* Analog Communication $ Mini Project Department Specific Electives SD3 @ Elective Soft Skills $ Comprehensive Viva Voce @ Institute Elective-OE3

9 11 13 16 18 19 20 21 22

Module IV

Course Structure Course Syllabi for courses - Module IV Theory Course Control Systems (MD) Digital Electronics Data Structures And Algorithm Networks And Lines Tutorial Control Systems (MD) Digital Electronics Practicals

26 27

28 30 32 34 36 37

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 2

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering 6.7 6.8 6.0 6.10 6.11 6.12 6.13 7 8 8.1 8.2 8.3 8.4 8.5 8.6 8.7 8.9 8.10 8.11 8.12 8.13 9 10 10.1 10.2 10.3 10.4 10.5 10.6 10.7 10.8 10.9 10.10 10.11 10.12 10.13 EC30104 EC30105 EC30106 EC30107 EC30203 EC30204 EC30303 EC30304 EC37402 EC30402 EC37302 EC30101 EC30102 EC30103 EC31101 EC30201 EC30202 EC30301 EC30302 EC37401 EC30401 EC37301 EC20303 EC20304 EC27402 EC243XX EC20402 Digital Electronics Data Structures And Algorithm $ Mini Project Department Specific Electives SD4 @ Elective Health & Hobby $ Comprehensive Viva Voce @ Institute Elective OE3 38 39 41

Module V

Course Structure Course Syllabi For Courses - Module V Theory Course Microcontroller & Applications Digital Communication Digital Signal Processing Mechatronics (MD) Tutorial Digital Communication Microcontroller & Digital Communication Practicals Microcontroller & Mechatronics Lab Signal Processing And Communication Lab. $ Mini Project @ Professional Development Course $ Comprehensive Viva Voce $ Seminar

45 46 47 49 51 53 55 56 57 58

Module VI

Course Structure Course Syllabi For Courses Module VI Theory Course Electromagnetic Engineering Analog Circuits Power Electronics Digital Integrated Circuits Tutorial Electromagnetic Engineering Analog Circuits Practicals Analog Circuits Power & Integrated Circuits Lab $ Mini Project @ Professional Development Course $ Comprehensive Viva Voce $ Project Stage I

595 60 61 63 65 67 69 70 71 72

Module VII

73

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 3

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering 11 12 12.1 12.2 12.3 12.4 12.5 15.6 12.7 12.8 12.9 12.10 12.11 12.12 12.13 12.14 12.15 12.16 12.17 13 14 14.1 14.2 14.3 14.4 14.5 14.6 14.7 14.8 14.9 14.10 14.11 14.12 14.13 14.14 EC40104 EC41101 EC42107 EC42109 EC42110 EC42111 EC42112 EC42113 EC42114 EC40203 EC42204 EC42206 EC42207 EC42208 EC40101 EC40103 EC42101 EC42102 EC42103 EC42104 EC42105 EC42106 EC40201 EC42201 EC42202 EC42203 EC40301 EC42301 EC42302 EC42303 EC47301 Course Structure Course Syllabi For Courses - Module VII Theory Course Electronic Circuit Design Coding & Data Compression Elective I - Theory Course Remote Sensing Artificial Intelligence Pattern Recognition Elective II - Theory Course Fibre Optic Communication VLSI Design Digital Image Processing Tutorial Electronic Circuit Design Remote Sensing Artificial Intelligence Pattern Recognition Practicals Coding & Data Compression Practicals Elective - II Fibre Optic Communication VLSI Design Digital Image Processing Project Stage - II 74 76 79 81 82 84 86 88 89 91 93 95 96 97 98 99 100 101 102 103 104 105 107 109 111 112 114 116 118 120 121 123 125 127 128 129 130 131

Module VIII

Course Structure Course Syllabi For Courses - Module VIII Theory Course Computer Networks Embedded Systems (MD) Elective III - Theory Microwave Engineering Electronic Automation Artificial Neural Networks And Fuzzy Logic Wireless Sensor Networks Elective IV - Theory Course Audio Video Engineering Advanced Power Electronics Biomedical Electronics Tutorial Computer Networks Microwave Engineering Electronic Automation Artificial Neural Networks And Fuzzy Logic Wireless Sensor Networks Practicals

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 4

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering 14.15 14.16 14.17 14.18 14.19 EC41301 Embedded Systems Practicals Elective - IV Audio Video Engineering Advanced Power Electronics Biomedical Electronics Project Stage-III 132 133 134 135 136 137

EC42304 EC42305 EC42306 EC47302 ACADEMIC INFORMATION 15 $ Please Refer Academic Information ! Please Refer F.Y. B.Tech. Structure and Syllabi Booklet @ Please Refer GP-PD-OE Structure & Syllabi Booklet

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 5

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

Program Educational Objectives (PEO) (Electronics Engineering)

PEO No.

1

Description of the Objective

Apply knowledge in Mathematics , Science and Engineering to solve Electronics Engineering problems. Ability to analyze and interpret data out of experimental findings. Ability to understand professional & ethical responsibilities and

preparation to be a part of multidisciplinary team. Ability to communicate effectively. Knowledge of contemporary issues. Ability to use the techniques, skills and modern Engineering tools

4 5

necessary for Engineering practice. Provide students with a solid foundation in Electronics Engineering,

preparing them for career and professional growth. To provide Engineering design experience, enabling students to explore

relationship between theory and practices. Challenge traditional thinking and invent new approaches to solve

technical problems.

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 6

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 59

MODULE - VI

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

Structure, T.E. (Module VI)

FF653, Issue No. 3, Rev 1, dt 02/04/2011

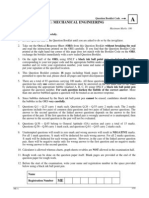

Subject No. S5 S6 S7 S8 T3 T4 P3 P4 MP6 * PD2 CVV4 PS1 Subject Code EC30104 EC30105 EC30106 EC30107 EC30203 EC30204 EC30303 EC30304 EC37402 EC333XX EC30402 EC37302 Subject Name Teaching Scheme (Hrs/week) Lect. Electromagnetic Engineering Analog Circuits Power Electronics Digital Integrated Circuits Electromagnetic Engineering Analog Circuits Analog Circuits Power & Integrated Circuits Lab Mini Project Institute Level Elective Comprehensive Viva Voce Project stage - I Total 3 3 3 3 0 0 0 0 0 0 Tutorial 0 0 0 0 1 1 0 0 0 0 Practical 0 0 0 0 0 0 2 2 2 2 3 3 3 3 1 1 1 1 1 1 1 2 21 Credits

Based on Courses S7 & S8 0 12 0 2 4 12

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 60

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering FF No. : 654

EC30104:: ELECTROMAGNETIC ENGINEERING

Credits: 03 Teaching Scheme: - Theory 3 Hrs/Week

Prerequisites: Basics of C Programming Language Objectives: To study force experienced by a charge(s) in electrostatic, magnetostatic and electromagnetic fields To study power transmitted by electromagnetic waves in different media Mapping with PEO : 1,2,6,7,8

Unit I Vectors and Coordinate Systems

(4 Hrs)

Addition, subtraction, dot product and vector product of vectors, unit vectors, position and displacement vectors, Cartesian, cylindrical and spherical coordinate systems

Unit II Electrostatics

(12 Hrs)

A. Coulombs Law, Concept of Electric Field intensity, Electric Field Intensity due to various charge distributions, Gausss law and its applications, Divergence theorem, Work, Energy, Potential, Gradient, Electric Fields in conductors and dielectrics, Continuity Equation, Boundary Conditions B. Laplace, Poissons equations Unit III Applications of Linear Data Structures (10 Hrs)

A. Biot Savart law, Magnetic Field Intensity due to various current distributions, Amperes circuital law and its applications, Curl, Stokes theorem, Magnetic Flux and magnetic flux density, Scalar and vector magnetic potentials, Forces due to magnetic fields, Magnetization and Permeability, Boundary conditions, Magnetic Energy

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 61

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering Unit IV Maxwells Equations & Time Varying Fields (06 Hrs)

A. Faradays law, Displacement current, Maxwells equations, Time varying fields, Unit V Uniform Plane Wave And Propagation (8 Hrs)

A. Wave equation, Wave propagation in free space, dielectrics and conductors, Skin Effect, Polarization, Reflection of uniform plane waves at normal and oblique incidence, Standing wave ratio, Wave reflection from multiple interfaces B. Wave propagation in dispersive media

Text Books

1. Sadiku Matthew N O, Elements of Electromagnetics, Oxford University Press,

3rd edition, 2002/2003.

2. Hayt W H, Engineering Electromagnetics, Mc_graw Hill Book Co., 7 edition,

th

1981 Reference Books 1. Kruse R L, Leung B P & Tondo C L: Data Structure And Programming Design In C. Prentice Hall Of India Pvt.ltd. 2. Kakde O G & Deshpande , Data Structures And Algorithms. Indian Society For Technical E 3. Sahni S: Data Structures, Algorithms,& Applications In C++. Mcgraw Hill Boston.

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 62

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering FF No. : 654

EC30105 :: ANALOG CIRCUITS

Credits: 03 Prerequisites: Nil Objectives: To provide clear explanation to students regarding analysis of electronic circuits using discrete transistors and operational amplifiers. Mapping with PEO : 1,2,5,6,7,8 Teaching Scheme: - Theory 3 Hrs/Week

Unit I Feedback Amplifiers and Oscillators

(9 Hrs)

A. Concept of feedback, Negative feedback, Four Feedback topologies, Transfer gain with feedback, Advantages and disadvantages of negative feedback, Effect of feedback on input and output impedances and bandwidth of an amplifier. Analysis of one circuit for each feedback topology. OSCILLATORS: Positive feedback, Oscillator startup mechanism, need for amplitude limiting. Study of LC oscillators - General form of LC oscillator. Hartley oscillator, Colpitt,s oscillator, Clapps oscillator. B. RC Oscillator, Wein Bridge Oscillator, Crystal oscillator. Unit II Large Signal AF Power Amplifiers (8 Hrs)

A. Classes of power amplifiers - Class A, Class B, Class AB, class C, class D. Class A with resistive load, Transformer coupled class A amplifier, Class B Push-pull, Class AB, Complementary symmetry. Efficiency analysis for all, Comparison of efficiencies, Distortions in amplifiers, Nonlinearities and harmonics, Total Harmonic Distortion. B. Quasi-complementary configurations Higher order harmonic generation Unit III OP-AMP Fundamentals (8 Hrs)

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 63

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering A. Basic building blocks of operational amplifier, differential amplifier, current sources like widlar, wilson and mosfet sources, voltage sources, active level shifters, output stage, open loop and closed loop operation, inverting and non-inverting configurations of opamp, concept of virtual short and virtual ground. ideal op-amp parameters like input offset voltage, output offset voltage, input offset current, bias current, CMRR, PSRR, slew rate, open loop gain, input resistance, output resistance, frequency response, small signal and power bandwidth, non-ideal op-amp behavior in terms of ac and dc parameters and its effect on performance. offset nulling techniques. B. Measurement of op-amp parameters, Frequency Compensation Unit IV Linear Applications of OP-AMP (6 Hrs)

A. Summing amplifier, difference amplifier, voltage follower, Signal phase shifter, AC amplifier, Instrumentation amplifier, Guard Shield circuits, Integrator and applications, Integrator set, run and hold modes, Differentiator and applications, voltage to current and current to voltage converters, Log Amplifier and Antilog amplifier with log ratio and temperature compensation circuits. B. Isolation Amplifier Unit V Non Linear Applications of OP-AMP (9 Hrs)

A. Precision half wave and full wave rectifiers, True RMS converter, Comparators, Limitations of op-amp as comparator, Comparator IC LM 339, Window Comparator, Schmitt Triggers, Peak Detectors, Sample and Hold circuits, Astable, Mono-stable and Bi-stable multi-vibrator and its applications, Design of sine, square, triangular, sawtooth and ramp waveform generators, V to F and F to V converters. B. Timer ICs 555/556, block diagram and applications. Text Books 1. Integrated Electronics , Millman Halkias , Tata McGraw Hill1. 2. Design with opearational amplifiers and analog integrated circuits ,Sergio Franco, TMH, Third edition 3. Op- amp and Integrated Circuits, Ramakant Gayakwad, PHI Reference Books 1. Electronic circuit analysis & Design , Donald A. Neamen , Tata McGraw Hill 2. Operational Amplifiers, G. B. Clayton, Mc Graw hill International Edition 3. Opearational Amplifiers and Linear Integrated Circuits, Coughlin, Discroll, PHI

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 64

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering FF No. : 654

EC30106:: POWER ELECTRONICS

Credits: 03 Teaching Scheme: - Theory 3 Hrs/Week

Prerequisites: Basics of semiconductor devices, Fourier series analysis approach Objectives: To explain the necessity of power conversion. To discuss physics & applications of various devices used for conversion To explain techniques & control of power conversions To apply analytical tools for performance evaluation Mapping with PEO : 1,2,3,6,7,8,9 Unit I POWER DEVICES (10 Hrs)

A. Structural modifications for power devices. Structure, Characteristics, ratings of Power Diode SCR, GTO, IGBT Comparison of above devices with Power MOSFET & Power BJT Driver Circuits (isolated & non-isolated) for IGBT & SCR Commutation circuits for SCR Protection circuits for IGBT & SCR B. Comparison of all power devices and suitability for applications. Silicon Carbide (SiC), Gallium Nitride (GaN)-based power devices. Suitability of these devices for high power circuits. Unit II CONTROLLED RECTIFIER (8 Hrs)

A. Concept of line commutation. Single-phase half wave and full wave controlled rectifier: Circuit diagram, operation, waveforms for resistive and level (highly inductive) loads. Single phase semi and full bridge controlled rectifier: Circuit diagram, operation, waveforms for R, L and RLE loads. Average and RMS expressions for o/p voltage. Fourier analysis of supply current. Performance metrics : Fundamental power factor, Current distortion factor, Active, reactive & apparent power. B. Numericals based on converters. Unit III INVERTERS DC / AC (8 Hrs)

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 65

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering A. Half bridge and push pull type inverters : Circuit diagram, operation & waveforms. Full bridge inverters: Circuit diagram, operation & waveforms for R & RL loads. Switching techniques for obtaining square, quasi-square o/p waveforms. Fourier analysis of square and quasi-square voltage waveform & harmonics. Harmonic reduction techniques. Advantage of sine weighted PWM over single pulse PWM techniques. Inverter configuration for IM drive B. Numericals based on Inverter performance. Unit IV SWITCHED & RESONANT DC/ DC CONVERTERS (8 Hrs)

A. Step Up / Down chopper: Circuit diagram, operation and waveforms for R and L load. Load voltage calculations. Two-quadrant, Four-quadrant chopper. Circuit diagram, operation and waveforms for R and L load. Chopper DC motor drives. SMPS : Circuit diagram, operation and waveforms, of Fly back converter and forward converter. Need for resonant converters. ZVS, ZCS Switches. B. Comparison of linear, switched and resonant power supplies. Unit V APPLICATIONS OF POWER ELECTRONICS (6 Hrs)

A. Study of power circuits for Electronic ballast , HF induction heating, RF heating, Welding. ON-line and OFF line UPS, battery selection and design considerations. HVDC transmission, twelve pulse converter, and advantages over HVAC transmission. Stator voltage control for IM motors. B. Industrial applications of motor drives, Study of Cycloconverter.

Text Books 1. M. H. Rashid, POWER ELECTRONICS circuits devices and applications, PHI, 3rd edition, 2004. 2. M D Singh, K B Khanchandani, POWER ELECTRONICS,2nd Ed. TMH. Reference Books 1. N. Mohan, T. M. Undeland & W. P. Robbins, POWER ELECTRONICS, Converters Applications and Design John Willey and sons, 3rd edition, Singapore 2. P. C. Sen,MODERN POWER ELECTRONICS, S Chand & Co., New Delhi

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 66

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering FF No. : 654

EC30107 :: DIGITAL INTREGRATED CIRCUITS

Credits: 03 Prerequisites: Nil Objectives: - To study behavior of CMOS inverter in detail. - To draw NAND, NOR, XOR gates using CMOS logic. - To study VHDL as EDA Tool. - Mapping with PEO :2,3,6,7,8,9 Teaching Scheme: - Theory 3 Hrs/Week

Unit I : Introduction to HDL

(8 Hr)

A] What is HDL, VHDL, role of hardware description languages, motivation. Describing Hardware in VHDL- data types, data objects data operators, Event and transactions, attributes. Concurrency, Entity, Architecture, concurrent Signal assignments, resolved signals, conditional signal assignment statement, selected signal assignment statement, constructing VHDL models. Delays- Inertial Delay, transport delay, Delta delay, waveform and timing. B] predefined attributes. Unit II: Modeling in VHDL (8 Hr)

A] Behavior Modeling- Process construct, programming constructs-If then else statements, case statement, loop statements, more on process, wait statement, using signal in process, state machine modeling. Structural modeling, component declaration, instantiation, Generics, configuration and binding. B] Generate statement. Unit III: Advanced Topics (7 Hr)

A] Sub-programs and overloading -Functions, Procedures. Packages and libraries. Basic principles of Synthesis,. Test benches-test bench for combinational and test bench for sequential circuits. B] Synthesizable and non-synthesizable statements.

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 67

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

Unit IV: Static CMOS

(8 Hr)

A] Recap of I-V characteristics for MOS , CMOS inverter, VTC, detail analysis of VTC, noise Margin, Regenerative property, performance, Power and energy consumption, Power consumption and Power delay product, CMOS logic design, Transmission gate, Ratioed logic, Pass transistor logic, power consumption in CMOS. B] Resistive MOS Inverter. Unit V: Dynamic CMOS design (9 Hr)

A] Dynamic logic basic principles, Domino logic, Zipper CMOS, DCVSL logic, CMOS Sequential circuit Design- CMOS flip-flops, dynamic sequential circuits- Pseudo static Latch, C2MOS Latch, NORA CMOS, TSPCL, Non-Bistable. B] Two phase Flip-flop, schmitt trigger

Text Books 1. Digital Integrated Circuits: A Design Perspective, J. Rabaey, Prentice Hall India, 1997. 2. VHDL Primer, J Bhaskar , Addison Wesley Longman, 2000.

Reference Books 1. Principles of CMOS VLSI Design, N. Weste and K. Eshranghian, Addison Wesley. 2.CMOS Digital Integrated Circuits, Kang S. M.,TMH, 3rd edition, 2003. 3. VHDL, D. Perry, 2nd Ed., McGraw Hill International, 1995. 4. Introductory VHDL from simulation to synthesisSudhakar Yalamanchili, , Pearson education.

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 68

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering FF No. : 654 EC30203 :: ELECTROMAGNETIC ENGINEERING Credits: 01 Teaching Scheme: - Tutorial 1 Hrs/Week Prerequisites: Basics of C Programming Language Objectives: To study force experienced by a charge(s) in electrostatic, magnetostatic and electromagnetic fields To study power transmitted by electromagnetic waves in different media Mapping with PEO : 1,2,7,8,9

1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12.

Coordinate Systems Coulombs Law Gauss Law Work, Energy, Potential Boundary Conditions Amperes Law Magnetization and Boundary Conditions Maxwells Equation and Wave Equation Polarization Wave reflection (normal incidence) Wave reflection (oblique incidence) VSWR

Text Books

1. Sadiku Matthew N O, Elements of Electromagnetics, Oxford University Press, 3rd

edition, 2002/2003.

2. Hayt W H, Engineering Electromagnetics, Mc_graw Hill Book Co., 7th edition,

1981

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 69

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering FF No. : 654

EC30204 :: ANALOG CIRCUITS

Credits: 01 Prerequisites: : Nil Objectives: To provide clear explanation to students regarding analysis of electronic circuits using discrete transistors and operational amplifiers. Mapping with PEO : 1,2,5,6,7,8 List of Contents 1. Feedback amplifiers 2. Feedback amplifiers 3. Oscillators 4. Power amplifiers 5. Power Amplifiers 6. Opamp parameters 7. Opamp parameters 8. Instrumentation Amplifiers 9. Log Amplifier 10. Multivibrators 11. IC 555 12. IC 555 Text Books 1. Integrated Electronics , Millman Halkias , Tata McGraw Hill1. 2. Design with opearational amplifiers and analog integrated circuits ,Sergio Franco, TMH, Third edition 3. Op- amp and Integrated Circuits, Ramakant Gayakwad, PHI Teaching Scheme: - - Tutorial 1 Hr/Week

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 70

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering FF No. : 654

EC30303:: ANALOG CIRCUITS

Credits: 01 Prerequisites: Nil Objectives: Students should learn to verify analytical aspects of circuits using discrete transistors and design operational amplifier based circuits. Mapping with PEO : 1 to 7 List of Practical 1. 2. 3. 4. 5. 6. 7. 8. 9. Voltage Series Amplifier Current Shunt amplifier LC Oscillators Design of Integrator and Differentiator circuit Design of V to I and I to V converters Design of Comparator and Schmitt Trigger Design of Precision Rectifier Design of Waveform Generator Miniproject Teaching Scheme: - Laboratory 2 Hrs/Week

Text Books 1. Integrated Electronics , Millman Halkias , Tata McGraw Hill1. 2. Design with opearational amplifiers and analog integrated circuits ,Sergio Franco, TMH, Third edition 3. Op- amp and Integrated Circuits, Ramakant Gayakwad, PHI Reference Books 1. Electronic circuit analysis & Design , Donald A. Neamen , Tata McGraw Hill 2. Operational Amplifiers, G. B. Clayton, Mc Graw hill International Edition 3. Opearational Amplifiers and Linear Integrated Circuits, Coughlin, Discroll, PHI, 4th ed 4. Linear Integrated Circuits, D. Roy Choudhary

FF No. : 654

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 71

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

EC 30304: POWER & INTEGRATED CIRCUITS LAB

Credits: 1 Part A :: Power Electronics Objectives: To study characteristics of Power devices To study power circuits and control circuits. Mapping with PEO : 2,3,5,6,7,8,9

Teaching Scheme: - Laboratory 2 Hrs/Week

To study Triggering circuits for SCR. To study Driver circuits for IGBT / MOSFET. To simulate power electronic conversion system (AC-DC/DC-DC/DC-AC), with suitable load. To study power electronic conversion system with R/L/E load (AC-DC/DC-DC/DCAC). Course Project based on power electronic circuit design. To write VHDL code, simulate and implement 1 bit full adder/ Multiplexer/decoder To write VHDL code, simulate and implement D Flip flop/ Shift register/BCD Counter To write VHDL code, simulate and implement a state machine description sequence detector / counter. To study the characteristics of CMOS logic gate. Course Project based on Hardware description language and simulation tool.

Text Books 1. M. H. Rashid, POWER ELECTRONICS circuits devices and applications, PHI, 3rd edition, 2004, New Delhi. 2. A VHDL Primer, J Bhaskar, Pearson,2000.

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 72

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 137

ACADEMIC INFORMATION

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

A)

Mid Semester Examination

1. Students reporting in morning slot will have examination in morning slot. Those in evening slot will have examination in evening slot. 2. 20 multiple choice based questions to be attempted in 30 minutes x no. of theory courses i.e. 100 questions in 150 minutes for F.E., 80 questions in 120 minutes for S.E., T.E.,B.E.,M.E., 20 questions in 30 minutes for Honors, Minor, Fast Track, etc. 3. A scrambled mix of questions will be generated through software. 4. Mid Semester Examination will be based on Unit II & Unit III. 5. There will be one mark for each correct answer and (-) 0.25 marks for every wrong answer. 6. For a typical 3 hour Mid Semester Examination, first 15 minutes would be used for student attendance, record keeping, seat allocation, log in procedure if any, etc. Next 150 minutes for actual examination. A timer indicating time remaining to be provided by ERP. 15 minutes for processing & results. 7. A visual alarm / flash would be given 10 minutes before completion of 150 minutes as a warning. For auto generation of every theory course result out of 20 and dispatch of the marks on student mobile and mail ID as well as parent mail ID. 8. No repeat examination under any circumstances.

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 138

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

B) Seminar Conduct, Evaluation, etc.

Seminar (T.E.- Semester I)

1. Review I: during Mid Semester Examination (Compulsory) as per the Academic Calendar. 2. Review II : The last week of November (Optional) 3. For poor performing students identified by the examination panel, a second review to be taken. Review II optional for other students. For Review II, deduction of 10 marks will take place. 4. Seminar is an individual activity with separate topic and presentation. 5. Duration of presentation 20 minutes Question and answer session 10 minutes

Seminar Evaluation Scheme :

1. Attendance during Semester 2. Attendance during Seminar presentation self & peer 3. Relevance of Seminar topic 4. Timely Abstract submission 5. Literature review 6. Technical contents 7. Presentation 8. Question & answer Session

10 marks 10 marks 10 marks 10 marks 10 marks 10 marks 25 marks 15 marks --------------100 marks =========

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 139

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

C) Equivalence

For the courses belonging to 2008 structure counseling sessions for failure students will be arranged. The Head of Department will appoint faculty identified as subject experts as counselors. The previous examination scheme i.e.

Class Test 10 marks T.A. through Home assignment 10 marks A written paper MSE 30 marks A written paper ESE 50 marks

Will be followed. The entire processing based on 2008 structure related coding scheme will be followed. Counseling + Administration + Examination charges will be the basis for fees considered for such students.

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 140

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

D) Extra Credits

A student planning to take extra credits may be considered under following categories :

(a) A student carrying a backlog and re-registering for the previous course Re-registration charges as applicable. Consideration of all courses registered for during that Semester of Academic Year for SPI calculation. (b) Student planning to take extra courses as a fast track opportunity Administration, processing and examination charges will be considered. In any case the student has to pay the college fees for four years. This fast track facility would enable the student to undergo an industrial training, an exchange programme, research contribution in I.I.T. under scheme such as KVPY without any academic compromises for credit transfer. The phasewise development and completion of project activity cannot be considered at an accelerated pace under fast track scheme. The registration under fast track is subject to having a CPI 8.0 or above and no backlog for consideration of registration to an additional course. (c) Students opting for earning extra credits by selection of courses in addition to the courses prescribed by respective BOS which are single Semester activities and not the part of Honors / Minor scheme. Such students will be expected to pay charges equivalent to re-registration (proportionate credit based payment). The registration for such courses is subject to permission given by the Chairman BOS of the Board in the purview of which the subject is identified. Such permissions will be given based on meeting with prerequisite subject. 1. In any case (a), (b) or (c) the candidate cannot register for more than 8 credits. 2. A suitable reflection of completion of the said course will be made in the candidates Grade statement.

For part (c) a separate grade & GPA will be calculated. That GPA will not be clubbed with the other regular courses for SPI, CPI calculation.

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 141

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering E) Home Assignment

A Home Assignment Calendar for Semester is prepared as under:

Week No. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

Activity No Home Assignments No Home Assignments No Home Assignments S1 / S2 HA1 S3 / S4 / S5* - HA1 S1 / S2 HA2 S3 / S4 / S5* - HA2 S1 / S2 HA3 S3 / S4 / S5* - HA3 S1 / S2 HA4 S3 / S4 / S5* - HA4 S1 / S2 HA5 S3 / S4 / S5* - HA5 No Home Assignments No Home Assignments No Home Assignments

The Home Assignments will be based on the self study component i.e. part B of every theory course syllabus. The Saturday or last working day will be the default deadline for submission of Home Assignment of that week. For example by the Saturday ending Week No. 9, Home Assignment No. 3 for subject S3/ S4/ S5 (if applicable) must be submitted.

1. *S5 can be OE1 / OE2 / OE3 / Honors/ Minor / Re-registration category (a) / Category (b) / Category (c). 2. For subjects S1, S2, S3, S4 & S5 (if any), the composition of the Teacher Assessment marks will be as follows :

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 142

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

S1,S2 with Tutorial

S3,S4,S5 without Tutorial

Home Assignment Tutorial Test Attendance :

(a) > 90% (b) 75% to 90% (c) <75%

30 marks 30 marks 30 marks

30 marks

30 marks

10 marks 5 marks 0 marks

10 marks 5 marks 0 marks

100 marks converted to 70 marks converted to 15 15 marks marks

Explanation :

1. Tutorials to be conducted with continuous assessment throughout the Semester. Final assessment out of 30 marks for Tutorial. 2. Class Test to be conducted during a regular theory class within the time period mentioned in the Academic Calendar. 3. Class Test marks are to be entered immediately as mentioned in Academic Calendar. 4. Attendance percentage to be calculated at the end of Semester after completing all lectures as per the lesson plan.

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 143

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

F) Mini Project

Teaching Scheme: Theory 0 ; Tutorial 0 ; Laboratory 2 Hrs / week

For F.E., S.E. & T.E. students in every Semester a Mini Project be carried out. The objectives behind the Mini Project are:

1. Scope for creativity 2. Hands on experience 3. Academic occupancy

Mini Project will be based on all subjects of that Semester except GP.

1. The Semester Mini Project will be for a group of 3 to 5 students. Head of Department to appoint Mini Project Guides. 1 credit will be awarded to the candidate after the viva voce and project demonstration at the End of Semester. 2. Group formation, discussion with faculty advisor, formation of the Semester Mini Project statement, resource requirement, if any should be carried out in the earlier part of the Semester. The students are expected to utilize the laboratory resources before or after their contact hours as per the prescribed module.

The Assessment Scheme will be: (a) Continuous Assessment 50 marks (b) End Semester 50 marks

--------------100 marks ==========

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 144

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

G) Project Stage I Evaluation

The project activity is broken in 3 stages:

The Project Stage I will be in T.E Semester II irrespective of student module. The evaluation of Project Stage I will be as follows:

Group formation & attendance / reporting to guide Topic finalization / Statement Literature Survey Abstract Presentation

20 marks 20 marks 20 marks 20 marks 20 marks

Project Stage II and Project Stage III evaluations will be based on Department specific norms.

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 145

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

H) Composition for Selection of 5 Credits for Honors / Minor Course (Applicable for B11 and A11 Patterns) (A) Comprehensive Viva Voce Compulsory at the end of Semester VIII 1 Credit (B) Elective Component a. Laboratory courses Maximum Credits - 2 (for award of 1 Credit the lab course would have a teaching scheme of 2 Hrs. / week and a plan of 12 practicals). The credit to be awarded as per the ISA and ESA guidelines for the compulsory lab courses. b. Research publication Maximum Credits 1 (Research Publication in a Magazine / Transaction / Journal as decided by the honors / minor co-ordinator) c. Seminar - Maximum Credits 1 (Seminar to be given on a topic consistent with the scope of the Honors or Minor. The topic Selection is to be approved by the honors / minor co-ordinator. The assessment and

evaluation scheme would as per the guidelines used for Technical Seminar at UG level by respective Dept.) d. Honors / Minors Project Maximum Credits 2 (Project Topic and Scope, its progress and final assessment consistent with the scope of the Honors or Minor. The topic Selection is to be approved by the honors / minor co-ordinator. The assessment would as per the guidelines and evaluation scheme used for Project Work at UG level by respective Dept.) e. Industrial Training Maximum credits 4 (An Industrial Training in an Industry identified by the student, approved by the honors / minor co-ordinator & Head of Department. The assessment would as per the guidelines and evaluation scheme used for Industrial Training at UG level by respective Dept.)

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 146

Bansilal Ramnath Agarwal Charitable Trusts

Vishwakarma Institute of Technology, Pune 411 037

Department of Electronics Engineering

Note : a. 4 Credits would be awarded to the students for a complete 12 Week Industrial Training and meeting with the assessment and evaluation requirements b. Provision can be made for the students unable to procure a 12 week Industrial Training. A 4 week or 8 week Industrial Training may also be offered. 2 credits will be awarded for 8 week Industrial Training and 1 Credit would be awarded to the students for a 4 Week Industrial Training, meeting with the assessment and evaluation requirements c.No Industrial Training less than 4 weeks be considered for award of 1 Credit d. No cumulative addition of Industrial Training period would be considered for award of credits The student is expected to earn 1 Credit from Part (A) and remaining 4 Credits from Part (B)

Structure & Syllabus of B.E. (Electronics) Program Pattern A11, Issue No.3, Rev No.1 dated 2/4/2011 147

Você também pode gostar

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- EC 2214: Coding & Data Compression: Vishwakarma Institute of TechnologyDocumento35 páginasEC 2214: Coding & Data Compression: Vishwakarma Institute of TechnologyAnuj BodheAinda não há avaliações

- QpmeDocumento16 páginasQpmeSandeep PandeyAinda não há avaliações

- The MPEG Video StandardsDocumento3 páginasThe MPEG Video StandardsAnuj BodheAinda não há avaliações

- The NMEA 0183 ProtocolDocumento28 páginasThe NMEA 0183 ProtocolMarco Cocco100% (5)

- The NMEA 0183 ProtocolDocumento28 páginasThe NMEA 0183 ProtocolMarco Cocco100% (5)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- TEACHeXCELS Required ReadingsDocumento69 páginasTEACHeXCELS Required ReadingsJessica MarieAinda não há avaliações

- Informatica Certification Prep ListDocumento5 páginasInformatica Certification Prep ListRabindra P.SinghAinda não há avaliações

- Free W3 Blog TemplateDocumento4 páginasFree W3 Blog TemplateMaseko CharuzuAinda não há avaliações

- Solid 186Documento23 páginasSolid 186structure123Ainda não há avaliações

- Finding Answers Through Data Collection: Data Collection Procedure and Skills Using Varied InstrumentsDocumento4 páginasFinding Answers Through Data Collection: Data Collection Procedure and Skills Using Varied InstrumentsJude BautistaAinda não há avaliações

- STRUCTURAL - Chapter 14 - Explicit Dynamics Analysis (UP19980818)Documento26 páginasSTRUCTURAL - Chapter 14 - Explicit Dynamics Analysis (UP19980818)Rory Cristian Cordero RojoAinda não há avaliações

- Lloyds Register Type Approval ST PDFDocumento4 páginasLloyds Register Type Approval ST PDFJuan SantosAinda não há avaliações

- Finding Herself. KelloggDocumento12 páginasFinding Herself. KelloggMinerva MinasAinda não há avaliações

- FIITJEE Class VIII Practice PaperDocumento8 páginasFIITJEE Class VIII Practice PaperD Samy100% (1)

- Data Communications: ECE 583 LectureDocumento6 páginasData Communications: ECE 583 Lecturechloe005Ainda não há avaliações

- Script PDFDocumento14 páginasScript PDFSachin SaraswatiAinda não há avaliações

- Anth 1020 Natural Selection Lab ReportDocumento4 páginasAnth 1020 Natural Selection Lab Reportapi-272845435Ainda não há avaliações

- TrainingGuide Geomatica 1 2017Documento132 páginasTrainingGuide Geomatica 1 2017sam.scribdAinda não há avaliações

- Performance Lawn EquipmentDocumento6 páginasPerformance Lawn Equipmentrddavis3100% (2)

- Using Keyframe SynfigDocumento1 páginaUsing Keyframe SynfigNdandungAinda não há avaliações

- English - Chapter 6 - The Making of A Scientist - Junoon - English - Chapter 6 - The Making of A Scientist - JunoonDocumento10 páginasEnglish - Chapter 6 - The Making of A Scientist - Junoon - English - Chapter 6 - The Making of A Scientist - JunoonSaket RajAinda não há avaliações

- HW CFK ModellerDocumento7 páginasHW CFK ModellerKillgusAinda não há avaliações

- Backup Exec 2010, 2010 R2 and 2010 R3 Hardware Compatibility List (HCL)Documento248 páginasBackup Exec 2010, 2010 R2 and 2010 R3 Hardware Compatibility List (HCL)Brian SvendsenAinda não há avaliações

- White Paper - ICM - CMII Model - RevBDocumento8 páginasWhite Paper - ICM - CMII Model - RevBtomjones777Ainda não há avaliações

- Pedometer ManualDocumento4 páginasPedometer Manualkwano007Ainda não há avaliações

- (Ebook PDF) - Statistics. .Spss - TutorialDocumento15 páginas(Ebook PDF) - Statistics. .Spss - TutorialMASAIER4394% (17)

- Managing The Multigenerational Workplace White PaperDocumento19 páginasManaging The Multigenerational Workplace White PaperSanghamitra DanAinda não há avaliações

- Lec21 2011Documento25 páginasLec21 2011ireall3017Ainda não há avaliações

- Samuel Amirtharaj - Evangelistic Sermon4Documento5 páginasSamuel Amirtharaj - Evangelistic Sermon4Samuel DavidAinda não há avaliações

- Chapter 3 Physical Resources PDFDocumento15 páginasChapter 3 Physical Resources PDFfloAinda não há avaliações

- Dtu BrochureDocumento15 páginasDtu BrochureShefalimodiAinda não há avaliações

- How To Modify Standard PF-Status of ALV GridDocumento4 páginasHow To Modify Standard PF-Status of ALV GridAshish MohapatraAinda não há avaliações

- The Isolation Approach To Elliott Wave Analysis: by Steve GriffithsDocumento6 páginasThe Isolation Approach To Elliott Wave Analysis: by Steve Griffithssam2976Ainda não há avaliações

- Advances Chemical Engineering PDFDocumento248 páginasAdvances Chemical Engineering PDFDaiane SantanaAinda não há avaliações

- Records Manager: Job DescriptionDocumento3 páginasRecords Manager: Job DescriptionMario Rieger100% (113)