Escolar Documentos

Profissional Documentos

Cultura Documentos

Experiment No. 5 Programmed Time Delays: Objectives

Enviado por

Harekrushna PatraDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Experiment No. 5 Programmed Time Delays: Objectives

Enviado por

Harekrushna PatraDireitos autorais:

Formatos disponíveis

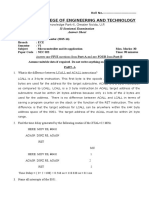

University of Technology Laser and Optoelectronics Engineering Department 8085 Microprocessor Lab.

2010-2011

EXPERIMENT NO. 5 PROGRAMMED TIME DELAYS

OBJECTIVES:

Compute the time required to execute an 8085 assembly language program. Design nested delay loops to generate a precise delay time. Generate a repetitive digital signal having a precise frequency.

INTRODUCTION

Each 8085 instruction requires a specific amount of execution time. In most applications, the programmer will attempt to minimize this execution time by writing the program in an efficient manner. There are many situations however, in which desirable to generate a time delay. This delay time can serve as a time to generate periodic waveforms or to sequence an industrial process. The execution time required by each instruction is function of the number of (T-states) in its instruction cycle. Each T-state is equal to one period of the 8085 system clock. For example, if an 8085 microprocessor has a clock frequency of 2 MHz, then each T-state equal 0.5 s. assuming this clock frequency, the instruction MVI A,byte, which consumes seven T-states, would be executed in Clock frequency of the system f=2MHZ Clock period T=1/f= 1/2 *10-6=0.5 s /T-states Time to execute MVI=7 T-states*0.5s / T-states =3.5 s

Note:Compute the same calculation when clock frequency=3.125MHZ, then each T-state equal 320ns. The time delay generated by a program is compounded by nesting loops within other loops. The total delay will then be the product of the individual delay for each loop. If longer loops are required, register pairs may be used for loop counters. Statements such as XTHL are often placed inside delay loops as "padding", to increase the total delay time.

University of Technology Laser and Optoelectronics Engineering Department 8085 Microprocessor Lab. 2010-2011

Note: INX rp and DCX rp instruction do not modify the Z flag. In other words, a JZ or JNZ instruction immediately following a DCX rp or INX rp instruction is not satisfactory, and an arithmetic or logic operation must be executed first

Useful instructions:

NOP: No operation is performed. The instruction is fetched and decoded; however, no operation is executed. The instruction is used to fill in time delays and insert instructions while troubleshooting. Instruction NOP Type

Machine control

No. of Bytes 1

Function No operation

Effect None

Example:T-states MVI C,0FFh Loop: DCR C JNZ loop 7 5 10

In this example, register C is loaded with the count ff (255) by the instruction MVI, which is executed once and takes seven T-states. The next two instructions, DCR and JNZ, from a loop with a total of fifteen (5+10) T-states. The loop is repeated 255 times until C=0. The time delay in the loop TL with 2 MHZ clock frequency is calculated as:TL= (T* loop T-states * N10) Where TL : Time delay in the loop T: system clock period N10: equivalent decimal number of the hexadecimal count loaded in the delay register. =(0.5*10-6 *15*255) = 1912.5s

University of Technology Laser and Optoelectronics Engineering Department 8085 Microprocessor Lab. 2010-2011

However, to calculate the time delay more accurately, the time for the execution of the initial instruction MVI should be included in the total time delay TD as: Delay TD = Time to execute instructions outside loop + time to execute loop instructions = T0+ TL = (7*0.5s)+1912.5s = 1916s

Home Work

1. The following program uses register pair (BC) to control the time delay length. Explain why the program as written does not perform properly. Correct the program so that it functions as required. LXI B,0FFFF h Loop: DCX B JNZ Loop RST1 : Initialize loop counter. : Decrement loop counter. : Loop until reaches zero. : Stop.

2. Calculate the total time required to execute the following delay subroutine. Delay: LXI Loop: DCX MOV ORA JNZ RST1 D,02F1h D A,E D Loop

Você também pode gostar

- Experiment - 3: Aim: Using 8051 Generate Square Wave Having 50% and 75% Duty Cycle andDocumento3 páginasExperiment - 3: Aim: Using 8051 Generate Square Wave Having 50% and 75% Duty Cycle andDevashishGuptaAinda não há avaliações

- The International University of Scholars: Department of Computer Science & EngineeringDocumento1 páginaThe International University of Scholars: Department of Computer Science & EngineeringGK KaderyeAinda não há avaliações

- Unit - IvDocumento48 páginasUnit - IvJit AggAinda não há avaliações

- Exp - 08 Flight86Documento6 páginasExp - 08 Flight86Muhammad SaqibAinda não há avaliações

- Algoritmo Velocidade PDFDocumento11 páginasAlgoritmo Velocidade PDFPaulo César RibeiroAinda não há avaliações

- Counters and Time Delays: by Dr. Syed Sahal Nazli AlhadyDocumento21 páginasCounters and Time Delays: by Dr. Syed Sahal Nazli AlhadyMunie RosnanAinda não há avaliações

- Time Delay CalculationsDocumento16 páginasTime Delay Calculationsraghuramu23456100% (1)

- LAB7Documento5 páginasLAB7REHAM DEE CAMAMAAinda não há avaliações

- Accessing Timer Registers in C: Example 9-20Documento12 páginasAccessing Timer Registers in C: Example 9-20MusTaFa QuReShiAinda não há avaliações

- 8051 Timers: Microcontroller and ApplicationsDocumento7 páginas8051 Timers: Microcontroller and ApplicationsKaushal FaujdarAinda não há avaliações

- Exp7 ReportDocumento8 páginasExp7 ReportMEGHANA R 20BEC1042Ainda não há avaliações

- Chapter 11Documento21 páginasChapter 11Khalid MasoodAinda não há avaliações

- Lect 19 F ETDocumento11 páginasLect 19 F ETAbhiJeetSinh GhariyaAinda não há avaliações

- Electronic Circuits and Diagram-Electronics Projects and DesignDocumento8 páginasElectronic Circuits and Diagram-Electronics Projects and DesignEric MelendezAinda não há avaliações

- Counters & Time Delays: Mca 1 Year 2 Semester 2020Documento21 páginasCounters & Time Delays: Mca 1 Year 2 Semester 2020JapAinda não há avaliações

- Eet 303 M2Documento9 páginasEet 303 M2Rabi khanAinda não há avaliações

- Timers and Interrupts ExperimentDocumento7 páginasTimers and Interrupts ExperimentPrakash PrasadAinda não há avaliações

- Microprocessor 8086 MPA4Documento37 páginasMicroprocessor 8086 MPA4ParveshAinda não há avaliações

- PIC Architecture and Assembler Programming: (Including Software Time Delay Subroutine)Documento16 páginasPIC Architecture and Assembler Programming: (Including Software Time Delay Subroutine)Ashim KumarAinda não há avaliações

- RP Tip Print NewDocumento5 páginasRP Tip Print NewNishant RajAinda não há avaliações

- 8052com Tutorial Reference Page 34-125Documento92 páginas8052com Tutorial Reference Page 34-125indusrilankaAinda não há avaliações

- Delay 8051Documento8 páginasDelay 8051MARIANOAinda não há avaliações

- Unit 5-Microcontroller ALPDocumento44 páginasUnit 5-Microcontroller ALPsenthilAinda não há avaliações

- Mpes Solved Dec 2017Documento13 páginasMpes Solved Dec 2017masterjiynAinda não há avaliações

- Microcontroller and Its Appl Ans (NEC 022-IiS)Documento5 páginasMicrocontroller and Its Appl Ans (NEC 022-IiS)Sachin PalAinda não há avaliações

- MPMC - LAB - W4.E4 8051 Keil - TimersDocumento35 páginasMPMC - LAB - W4.E4 8051 Keil - TimersDhanashree PanchawatkarAinda não há avaliações

- 8.1 Notes Crystal FrequencyDocumento3 páginas8.1 Notes Crystal Frequencyjinto007Ainda não há avaliações

- Delay Using 8051 TimerDocumento6 páginasDelay Using 8051 TimerDK White LionAinda não há avaliações

- Microcontroller and Embedded System DE-42 Mechatronics: Lab Report Week 11Documento4 páginasMicrocontroller and Embedded System DE-42 Mechatronics: Lab Report Week 11azeem niaziAinda não há avaliações

- Timer Wheel PDFDocumento24 páginasTimer Wheel PDFSarah ColemanAinda não há avaliações

- Timer and CounterDocumento30 páginasTimer and Countercleopatra2121Ainda não há avaliações

- Active Learning Assignment FOR The Subject "Microprocessor & Interfacing"Documento33 páginasActive Learning Assignment FOR The Subject "Microprocessor & Interfacing"Nirmal AcharyaAinda não há avaliações

- Programming Embedded Systems Seminar 4: Real-Time ConstrainsDocumento18 páginasProgramming Embedded Systems Seminar 4: Real-Time Constrainskt8815Ainda não há avaliações

- Timers PLCDocumento12 páginasTimers PLCdilippedAinda não há avaliações

- Illinois Exam2 Practice Solfa08Documento4 páginasIllinois Exam2 Practice Solfa08bittronicAinda não há avaliações

- 8051 CDocumento7 páginas8051 CTrieu Do MinhAinda não há avaliações

- Exp-05Documento6 páginasExp-05Prisha SinghaniaAinda não há avaliações

- 08.601 MBSD Module 2Documento86 páginas08.601 MBSD Module 2Assini HussainAinda não há avaliações

- Lect 20 EtDocumento10 páginasLect 20 EtmadhavAinda não há avaliações

- Building TCL-TK Guis For Hrt-Hood Systems: Juancarl@Unex - EsDocumento10 páginasBuilding TCL-TK Guis For Hrt-Hood Systems: Juancarl@Unex - EsKenny Rojas SalasAinda não há avaliações

- Practical 2 PicDocumento7 páginasPractical 2 PicPrerna Sanjivan MhatreAinda não há avaliações

- Delay Using 8051 TimerDocumento6 páginasDelay Using 8051 TimerVinothkumar UrumanAinda não há avaliações

- Fifth Semester B.Tech Degree Examination: Answer All QuestionsDocumento3 páginasFifth Semester B.Tech Degree Examination: Answer All Questionsrajkiran_rajAinda não há avaliações

- Fifth Semester B.Tech Degree Examination: Answer All QuestionsDocumento3 páginasFifth Semester B.Tech Degree Examination: Answer All QuestionsUrsap BuddyAinda não há avaliações

- 4 Timer 8051 02 02 2023Documento10 páginas4 Timer 8051 02 02 2023Kruthika JAinda não há avaliações

- Timer2 AsmDocumento11 páginasTimer2 AsmCesar Matos100% (2)

- Developing Counter and Time Delay RoutineDocumento24 páginasDeveloping Counter and Time Delay RoutineDilip KenAinda não há avaliações

- UNIT-5: Pipeline and Vector ProcessingDocumento63 páginasUNIT-5: Pipeline and Vector ProcessingAkash KankariaAinda não há avaliações

- Microprocessors and Microcontrollers Lab: Title: ComponentsDocumento8 páginasMicroprocessors and Microcontrollers Lab: Title: ComponentsGhulam E Muhammad UsmanAinda não há avaliações

- CIM Unit 3.1Documento96 páginasCIM Unit 3.1vrushAinda não há avaliações

- Cpe355 04 DDocumento15 páginasCpe355 04 Dobula863Ainda não há avaliações

- Microcontrollers and Its Applications: Shivaum Heranjal L27+28 17BEC0315 Padmini T NDocumento6 páginasMicrocontrollers and Its Applications: Shivaum Heranjal L27+28 17BEC0315 Padmini T NShivaum Heranjal100% (1)

- St. Joseph College of EngineeringDocumento15 páginasSt. Joseph College of EngineeringjaisathiAinda não há avaliações

- Unit III 8051 - Timer CoutnersDocumento37 páginasUnit III 8051 - Timer Coutnersanila kumaraAinda não há avaliações

- Benghazi University Faculty of Engineering: Power System Protection & Control LabDocumento4 páginasBenghazi University Faculty of Engineering: Power System Protection & Control Labarwa zeglamAinda não há avaliações

- Problemset 2solutionsDocumento6 páginasProblemset 2solutionsSushAinda não há avaliações

- Arduino TimerDocumento16 páginasArduino TimerAhnaf HassanAinda não há avaliações

- IES APR-18 (Sol) (E-Next - In)Documento6 páginasIES APR-18 (Sol) (E-Next - In)thakursurbhi2005Ainda não há avaliações

- Cse3666 MT1S F12Documento5 páginasCse3666 MT1S F12dimpal_3221Ainda não há avaliações

- Projects With Microcontrollers And PICCNo EverandProjects With Microcontrollers And PICCNota: 5 de 5 estrelas5/5 (1)

- Model Paper 1Documento2 páginasModel Paper 1nsharma_968751Ainda não há avaliações

- Quizez cs401Documento59 páginasQuizez cs401Abu Mohammad100% (4)

- Advanced Microprocessor and Microcontroller: Mechatronics MechatronicsDocumento8 páginasAdvanced Microprocessor and Microcontroller: Mechatronics MechatronicsAhmed Khalid MudawiAinda não há avaliações

- 8085 Microprocessor Architecture and Programming-1Documento92 páginas8085 Microprocessor Architecture and Programming-1ShubhamAinda não há avaliações

- Brief History of The X86 Family:: Evolution From 8080/8085 To 8086Documento15 páginasBrief History of The X86 Family:: Evolution From 8080/8085 To 8086vadla77Ainda não há avaliações

- Digital Electronics ExamDocumento4 páginasDigital Electronics ExamAlbin peterAinda não há avaliações

- 8085 Microprocessor - M B RajparaDocumento67 páginas8085 Microprocessor - M B RajparaSS0% (1)

- 25th August Revised Final B.tech. 3rd Year Electrical Engineering AICTE Model Curriculum 2020-21Documento49 páginas25th August Revised Final B.tech. 3rd Year Electrical Engineering AICTE Model Curriculum 2020-21rudraee41Ainda não há avaliações

- ECE Microprocessors 8086Documento16 páginasECE Microprocessors 8086Lokesh VeeramallaAinda não há avaliações

- Bme 2022Documento58 páginasBme 2022Generation GenerationAinda não há avaliações

- 2023-24 S.Y. B.sc. ElectronicsDocumento14 páginas2023-24 S.Y. B.sc. Electronicsanil sonawaneAinda não há avaliações

- Microprocessor Ppt1Documento36 páginasMicroprocessor Ppt1alfred calaunan100% (1)

- 8085 - Short SummaryDocumento14 páginas8085 - Short SummaryTarunVarmaAinda não há avaliações

- Computer 2018 5th6thDocumento20 páginasComputer 2018 5th6thAnmol JandyalAinda não há avaliações

- Objective 8085Documento18 páginasObjective 8085Raghu RamAinda não há avaliações

- EE6502 MPMC UNIT 1-5 (Read-Only)Documento607 páginasEE6502 MPMC UNIT 1-5 (Read-Only)Nive DossAinda não há avaliações

- Microprocessor 8085 VivaDocumento38 páginasMicroprocessor 8085 VivavlsiprabhuAinda não há avaliações

- Programming The 8085Documento79 páginasProgramming The 8085Jaimin JaniAinda não há avaliações

- A - MEDIA TO GET - ALL DATAS IN ELECTRICAL SCIENCE... !! - Transformer Stability Test Procedure PDFDocumento1 páginaA - MEDIA TO GET - ALL DATAS IN ELECTRICAL SCIENCE... !! - Transformer Stability Test Procedure PDFRK KAinda não há avaliações

- Computer Science Syllabus Pondicherry UniversityDocumento51 páginasComputer Science Syllabus Pondicherry UniversityBalayogi G0% (1)

- CSALDocumento1 páginaCSALDarrius Dela PeñaAinda não há avaliações

- CseDocumento55 páginasCseMamta VermaAinda não há avaliações

- M&M 3160904 LabManual LatestDocumento40 páginasM&M 3160904 LabManual LatestKvAinda não há avaliações

- Interrupts in 8085Documento17 páginasInterrupts in 8085JAAPA100% (2)

- Bus Organization of 8085Documento14 páginasBus Organization of 8085michaeledem_royalAinda não há avaliações

- Microprosessor NotesDocumento334 páginasMicroprosessor Notesskyverma0709Ainda não há avaliações

- Noc18 Ee33 Assignment12Documento5 páginasNoc18 Ee33 Assignment12Ayush mondalAinda não há avaliações