Escolar Documentos

Profissional Documentos

Cultura Documentos

Memory Tshooting

Enviado por

Drift GeeDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Memory Tshooting

Enviado por

Drift GeeDireitos autorais:

Formatos disponíveis

23

MEMORY TROUBLESHOOTING

CONTENTS AT A GLANCE Essential Memory Concepts

Memory organization Memory signals Circumventing parity Abuse and detection of fake memory Alternative error correction

Memory Package Styles and Structures

Add-on memory devices Megabytes and memory layout

Memory Installation and Options

Getting the right amount Filling banks Bank requirements

Memory Organization

Conventional memory Extended memory Expanded memory Upper memory area (UMA) High memory

Recycling Older Memory Devices

Memory speed Memory type SIMM stackers Mixing composite and non-composite SIMMS Remounting and rebuilding memory

Memory Considerations

Memory speed and wait states Determining memory speed Presence detect (PD) Understanding memory refresh Memory types Memory techniques

Memory Troubleshooting

Memory test equipment Repairing SIMM sockets Contact corrosion Parity errors Troubleshooting classic XT memory Troubleshooting classic at memory Troubleshooting contemporary memory errors

The Issue of Parity

The parity principle Even vs. odd The problems with parity

Further Study

744

ESSENTIAL MEMORY CONCEPTS

745

Memory is a cornerstone of the modern PC.

Memory that holds the program code and data that is processed by the CPUand it is this intimate relationship between memory and the CPU that forms the basis of computer performance. With larger and faster CPUs constantly being introduced, and more complex software is developed to take advantage of the processing power. In turn, the more complex software demands larger amounts of faster memory. With the explosive growth of Windows (and more recently, Windows 95) the demands made on memory performance are more acute than ever. These demands have resulted in a proliferation of memory types that go far beyond the simple, traditional DRAM. Cache (SRAM), fast page-mode (FPM) memory, extended data output (EDO) memory, video memory (VRAM), synchronous DRAM (SDRAM), flash BIOS, and other exotic memory types (such as RAMBUS) now compete for the attention of PC technicians. These new forms of memory also present some new problems. This chapter will provide you an understanding of memory types, configurations, installation concerns, and troubleshooting options.

2

SYSTEM DATA AND TROUBLESHOOTING

Essential Memory Concepts

The first step in any discussion of memory is to understand basically how memory works. If you already have a good grasp of memory basics, feel free to skip this part of the chapter.

MEMORY ORGANIZATION

All memory is basically an array organized as rows and columns (Fig. 23-1). Each row is known as an addressone million or more addresses might be on a single memory IC. The columns represent data bitsa typical high-density memory IC has 1 bit, but might have 2 or 4 bits, depending on the overall amount of memory required.

M data bits (8-bit data word) D0 Address 0 Address 1 Columns D7

Rows

Address N Cell matrix array FIGURE 23-1 Simplified diagram of a memory array.

746

MEMORY TROUBLESHOOTING

As you probably see in Fig. 23-1, the intersection of each column and row is an individual memory bit (known as a cell). This is important because the number of components in a celland the way those components are fabricated onto the memory ICwill have a profound impact on memory performance. For example, a classic DRAM cell is a single MOS transistor, and static RAM (or SRAM) cells often pack several transistors and other components onto the IC die. Although you do not have to be an expert on IC design, you should realize that the internal fabrication of a memory IC has more to do with its performance than just the way it is soldered into your computer.

MEMORY SIGNALS

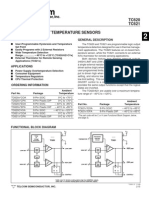

A memory IC communicates with the outside world through three sets of signals: address lines, data lines, and control lines. Figure 23-2 illustrates these signal types. Address lines define which row of the memory array will be active. In actuality, the address is specified as a binary number, and conversion circuitry inside the memory IC translates the binary number into a specific row signal. Data lines pass binary values back and forth to the defined address. Control lines are used to operate the memory IC. A Read/Write (R/W) line defines whether data is being read from the specified address or written to it. A Chip Select (CS) signal makes a memory IC active or inactive (this ability to disconnect from a circuit is what allows a myriad of memory ICs to all share common address and data signals in the computer). Some memory types require additional signals, such as Row Address-Select (RAS) and Column Address-Select (CAS), for refresh operations. More exotic memory types might require additional control signals.

Vcc Gnd

Address row select Address Address buffer

Storage cell array

Address column select

Cell I/O circuitry

CS Control circuit R/W

Bi-directional data buffer Data FIGURE 23-2 Diagram of a typical memory IC.

MEMORY PACKAGE STYLES AND STRUCTURES

747

Memory Package Styles and Structures

Ultimately, the memory die is mounted in a package just like any other IC. The completed memory packages can then be soldered to your motherboard or attached to plug-in structures, such as SIMMs, DIMMs, and memory cards. Only four package styles are normally used for memory devices:

s DIP (Dual In-line Package) This classic IC package is used for through-hole mounting

(prior to surface-mount technology). The advantage of DIP ICs is their compatibility with IC sockets, which allows ICs to be inserted or removed as required. Unfortunately, the long metal pins can bend and break if the IC is inserted or removed incorrectly. Also, the overall size of the package demands extra space. DIP ICs were used in older PCs (286 and earlier systems) and older VGA/SVGA video boards. DIPs are still sometimes used on motherboards to provide cache RAM. s SIP (Single In-line Package) This type of IC package is rarely used todaythere are simply not enough pins. However, they did make a short appearance with memory devices in late-model 286 and early 386 systems, which flirted with proprietary memory expansions. I remember NEC using such devices in a 2MB add-on for their 386SX/20 and you needed to add that module before you added even more memory in the form of proprietary SIMMs. SIPs can be troublesome because they are difficult to find replacements for, so expect replacement memory modules using them to cost a premium. s SOJ (Small-Outline J Lead) This is the contemporary package style for surfacemount circuits. The leads protrude from the package like a DIP, but are bent around just under the package in the form of a j. Sockets for SOJ packages are often used for replaceable memory ICs, such as the BIOS ROM, but most RAM devices are soldered directly to the motherboard as system memory (or a video board as video RAM). SIMMs often use SOJ memory components. s TSOP (Thin, Small-Outline Package) Like the SOJ, a TSOP is also a surface-mount package style. However, its small, thin body makes TSOP memory ideal for narrow spaces. Expect to find such devices serving as memory in notebook/sub-notebook systems or PCMCIA cards (a.k.a., PC Cards).

2

SYSTEM DATA AND TROUBLESHOOTING

ADD-ON MEMORY DEVICES

Memory has always pushed the envelope of IC design. This trend has given us tremendous amounts of memory in very small packages, but it also has kept memory relatively expensive. Manufacturers responded by providing a minimum amount of memory with the system, then selling more memory as an add-on optionthis keeps the cost of a basic machine down and increases profit through add-on sales. As a technician, you should understand the three basic types of add-on memory.

Proprietary add-on modules Once the Intel i286 opened the door for more than

1MB of memory, PC makers scrambled to fill the void. However, the rush to more memory resulted in a proliferation of non-standard (and incompatible) memory modules. Each new motherboard came with a new add-on memory schemethis invariably led to a great deal of confusion among PC users and makers alike. You will likely find proprietary memory modules in 286 and early 386 systems.

748

MEMORY TROUBLESHOOTING

SIMMs and DIMMs By the time 386 systems took hold in the PC industry, proprietary

memory modules had been largely abandoned in favor of the Memory Module (Fig. 23-3). A SIMM (Single In-line Memory Module) is light, small, and contains a relatively large block of memory, but perhaps the greatest advantage of a SIMM is standardization. Using a standard pin layout, a SIMM from one PC can be installed in any other PC. The 30-pin SIMM (Table 23-1) provides 8 data bits, and generally holds up to 4MB of RAM. The 30A 72-pin SIMM

A 168-pin DIMM

FIGURE 23-3

Comparison of SIMMs and DIMMs.

TABLE 23-1 PINOUT OF A STANDARD 30-PIN SIMM PIN NAME 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 VCC CAS DQ0 A0 A1 DQ1 A2 A3 GND DQ2 A4 A5 DQ3 A6 A7 DQ4 A8 A9 A10 DQ5 WE DESCRIPTION +5 VDC Column address strobe Data 0 Address 0 Address 1 Data 1 Address 2 Address 3 Ground Data 2 Address 4 Address 5 Data 3 Address 6 Address 7 Data 4 Address 8 Address 9 Address 10 Data 5 W it bl

MEMORY PACKAGE STYLES AND STRUCTURES

749

TABLE 23-1 PINOUT OF A STANDARD 30-PIN SIMM (CONTINUED) PIN NAME 21 1 22 23 24 25 26 27 28 29 30 VCC WE GND DQ6 n/c DQ7 QP RAS CASP DP VCC DESCRIPTION Write enable 5 VDC Ground Data 6 Not connected Data 7 Data parity out Row address strobe Parity control Data parity in +5 Vdc

2

SYSTEM DATA AND TROUBLESHOOTING

pin SIMM proved its worth in 386 and early 486 systems, but fell short when providing more memory to later-model PCs. The 72-pin SIMM (Table 23-2) supplanted the 30-pin version by providing 32 data bits, and it could hold up to 32MB (or more). Table 23-3 outlines a variation of the standard 72-pin SIMM highlighting the use of Error-Correction Code (ECC) instead of parity. You might also find such structures referred to as DIMMs (Dual In-Line Memory Modules). DIMMs appear virtually identical to SIMMs, but they are larger. And where each electrical contact on the SIMM is tied together between the front and back, the DIMM keeps front and back contacts separateeffectively doubling the number of contacts available on the device. For example, if you look at a 72-pin SIMM, you will see 72 electrical contacts on both sides of the device (144 contacts total)but these are tied together, so there are only 72 signals (even with 144 contacts). On the other hand, a DIMM keeps the front and back contacts electrically separate (and usually adds some additional pins to keep SIMMs and DIMMs from accidentally being mixed). Table 23-4 outlines a 144-pin DIMM. Today, virtually all DIMM versions provide 168 pins (84 pins on each side). DIMMs are appearing in high-end 64-bit data-bus PCs (such as Pentiums and PowerPC RISC workstations). As PCs move from 64 to 128 bits over the next few years, DIMMs will likely replace SIMMs as the preferred memory-expansion device. Table 23-5 lists the pinout for an unbuffered DRAM DIMM and Table 23-6 presents the pinout for an unbuffered SDRAM DIMM. Finally, you might see SIMMs and DIMMs referred to as composite or non-composite modules. These terms are used infrequently to describe the technology level of the memory module. For example, a composite module uses older, lower-density memory, so more ICs are required to achieve the required storage capacity. Conversely, a non-composite module uses newer memory technology, so fewer ICs are needed to reach the same storage capacity. In other words, if you encounter a high-density SIMM with only a few ICs on it, chances are that the SIMM is non-composite.

MEGABYTES AND MEMORY LAYOUT

Now is a good time to explain the idea of bytes and megabytes. Very simply, a byte is 8 bits (binary 1s and 0s), and a megabyte is one million of those bytes (1,048,576 bytes

750

MEMORY TROUBLESHOOTING

TABLE 23-2 PINOUT OF A STANDARD 72-PIN SIMM PIN NON-PARITY 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 VSS DQ0 DQ18 DQ1 DQ19 DQ2 DQ20 DQ3 DQ21 VCC n/c A0 A1 A2 A3 A4 A5 A6 A10 DQ4 DQ22 DQ5 DQ23 DQ6 DQ24 DQ7 DQ25 A7 A11 VCC A8 A9 RAS3 RAS2 n/c n/c n/c n/c VSS CAS0 CAS2 CAS3 CAS1 PARITY VSS DQ0 DQ18 DQ1 DQ19 DQ2 DQ20 DQ3 DQ21 VCC n/c A0 A1 A2 A3 A4 A5 A6 A10 DQ4 DQ22 DQ5 DQ23 DQ6 DQ24 DQ7 DQ25 A7 A11 VCC A8 A9 RAS3 RAS2 PQ26 PQ8 PQ17 PQ35 VSS CAS0 CAS2 CAS3 CAS1 DESCRIPTION Ground Data 0 Data 18 Data 1 Data 19 Data 2 Data 20 Data 3 Data 21 +5 Vdc Not connected Address 0 Address 1 Address 2 Address 3 Address 4 Address 5 Address 6 Address 10 Data 4 Data 22 Data 5 Data 23 Data 6 Data 24 Data 7 Data 25 Address 7 Address 11 +5 VDC Address 8 Address 9 Row address strobe 3 Row address strobe 2 Parity 26 (3rd) Parity 8 (1st) Parity 26 (3rd) Parity 35 (4th) Ground Column address strobe 0 Column address strobe 2 Column address strobe 3 Column address strobe 1

MEMORY PACKAGE STYLES AND STRUCTURES

751

TABLE 23-2 PINOUT OF A STANDARD 72-PIN SIMM (CONTINUED) PIN NON-PARITY 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 RAS0 RAS1 n/c WE n/c DQ9 DQ27 DQ10 DQ28 DQ11 DQ29 DQ12 DQ30 DQ13 DQ31 VCC DQ32 DQ14 DQ33 DQ15 DQ34 DQ16 n/c PD1 PD2 PD3 PD4 n/c VSS PARITY RAS0 RAS1 n/c WE n/c DQ9 DQ27 DQ10 DQ28 DQ11 DQ29 DQ12 DQ30 DQ13 DQ31 VCC DQ32 DQ14 DQ33 DQ15 DQ34 DQ16 n/c PD1 PD2 PD3 PD4 n/c VSS DESCRIPTION Row address strobe 0 Row address strobe 1 Not connected Read/-write Not connected Data 9 Data 27 Data 10 Data 28 Data 11 Data 29 Data 12 Data 30 Data 13 Data 31 +5 Vdc Data 32 Data 14 Data 33 Data 15 Data 34 Data 16 Not connected Presence detect 1 Presence detect 2 Presence detect 3 Presence detect 4 Not connected Ground

2

SYSTEM DATA AND TROUBLESHOOTING

SIZE: (PRESENCE DETECT LINES) PD2 GND GND NC NC PD1 GND NC GND NC SIZE 4 or 64MB 2 or 32MB 1 or 16MB 8 MB

ACCESSTIME: (PRESENCE DETECT LINES)

PD4 GND GND NC NC PD3 GND NC GND NC ACCESSTIME 50, 100 ns 80 ns 70 ns 60 ns

752

MEMORY TROUBLESHOOTING

TABLE 23-3 PINOUT OF A 72-PIN ECC SIMM PIN ECC 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 VSS DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 VCC PD5 A0 A1 A2 A3 A4 A5 A6 n/c DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 A7 DQ16 VCC A8 A9 n/c RAS1 DQ17 DQ18 DQ19 DQ20 VSS CAS0 A10 A11 CAS1 RAS0 OPTIMIZED VSS DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 VCC PD5 A0 A1 A2 A3 A4 A5 A6 n/c DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 A7 DQ16 VCC A8 A9 n/c RAS1 DQ17 DQ18 DQ19 DQ20 VSS CAS0 A10 A11 CAS1 RAS0 DESCRIPTION Ground Data 0 Data 1 Data 2 Data 3 Data 4 Data 5 Data 6 Data 7 +5 Vdc Presence detect 5 Address 0 Address 1 Address 2 Address 3 Address 4 Address 5 Address 6 Not connected Data 8 Data 9 Data 10 Data 11 Data 12 Data 13 Data 14 Data 15 Address 7 Data 16 +5 Vdc Address 8 Address 9 Not connected Row address strobe 1 Data 17 Data 18 Data 19 Data 20 Ground Column address strobe 0 Address 10 Address 11 Column address strobe 1 Row Address Strobe 0

MEMORY PACKAGE STYLES AND STRUCTURES

753

TABLE 23-3 PINOUT OF A 72-PIN ECC SIMM (CONTINUED) PIN ECC 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 RAS1 DQ21 WE ECC DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 VCC DQ32 DQ33 DQ34 DQ35 n/c n/c n/c PD1 PD2 PD3 PD4 n/c VSS OPTIMIZED RAS1 DQ21 WE ECC DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 VCC DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 PD1 PD2 PD3 PD4 DQ39 VSS DESCRIPTION Row address strobe 1 Data 21 Read/-write Error-correction control Data 22 Data 23 Data 24 Data 25 Data 26 Data 27 Data 28 Data 29 Data 30 Data 31 +5 Vdc Data 32 Data 33 Data 34 Data 35 Data 36 Data 37 Data 38 Presence detect 1 Presence detect 2 Presence detect 3 Presence detect 4 Data 39 Ground

2

SYSTEM DATA AND TROUBLESHOOTING

TABLE 23-4 PINOUT FOR AN OLDER 144-PIN SMALL-OUTLINE (SO) DIMM PIN 1 2 3 4 5 6 7 8 9 10 NORMAL VSS VSS DQ0 DQ32 DQ1 DQ33 DQ2 DQ34 DQ3 DQ35 ECC VSS VSS DQ0 DQ32 DQ1 DQ33 DQ2 DQ34 DQ3 DQ35 DESCRIPTION Ground Ground Data 0 Data 32 Data 1 Data 33 Data 2 Data 34 Data 3 Data 35

754

MEMORY TROUBLESHOOTING

TABLE 23-4 PINOUT FOR AN OLDER 144-PIN SMALL-OUTLINE (SO) DIMM (CONTINUED) PIN 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 NORMAL VCC VCC DQ4 DQ36 DQ5 DQ37 DQ6 DQ38 DQ7 DQ39 VSS VSS CAS0 CAS4 CAS1 CAS5 VCC VCC A0 A3 A1 A4 A2 A5 VSS VSS DQ8 DQ40 DQ9 DQ41 DQ10 DQ42 DQ11 DQ43 VCC VCC DQ12 DQ44 DQ13 DQ45 DQ14 DQ46 DQ15 DQ47 ECC VCC VCC DQ4 DQ36 DQ5 DQ37 DQ6 DQ38 DQ7 DQ39 VSS VSS CAS0 CAS4 CAS1 CAS5 VCC VCC A0 A3 A1 A4 A2 A5 VSS VSS DQ8 DQ40 DQ9 DQ41 DQ10 DQ42 DQ11 DQ43 VCC VCC DQ12 DQ44 DQ13 DQ45 DQ14 DQ46 DQ15 DQ47 DESCRIPTION +5 Vdc +5 Vdc Data 4 Data 36 Data 5 Data 37 Data 6 Data 38 Data 7 Data 39 Ground Ground Column address strobe 0 Column address strobe 4 Column address strobe 1 Column address strobe 5 +5 Vdc +5 Vdc Address 0 Address 3 Address 1 Address 4 Address 2 Address 5 Ground Ground Data 8 Data 40 Data 9 Data 41 Data 10 Data 42 Data 11 Data 43 +5 Vdc +5 Vdc Data 12 Data 44 Data 13 Data 45 Data 14 Data 46 Data 15 Data 47

MEMORY PACKAGE STYLES AND STRUCTURES

755

TABLE 23-4 PINOUT FOR AN OLDER 144-PIN SMALL-OUTLINE (SO) DIMM (CONTINUED) PIN 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 NORMAL VSS VSS n/c n/c n/c n/c DU DU VCC VCC DU DU WE n/c RAS0 n/c RAS1 n/c OE n/c VSS VSS n/c n/c n/c n/c VCC VCC DQ16 DQ48 DQ17 DQ49 DQ18 DQ50 DQ19 DQ51 VSS VSS DQ20 DQ52 DQ21 DQ53 DQ22 DQ54 DQ23 ECC VSS VSS CB0 CB4 CB1 CB5 DU DU VCC VCC DU DU WE n/c RAS0 n/c RAS1 n/c OE n/c VSS VSS CB2 CB6 CB3 CB7 VCC VCC DQ16 DQ48 DQ17 DQ49 DQ18 DQ50 DQ19 DQ51 VSS VSS DQ20 DQ52 DQ21 DQ53 DQ22 DQ54 DQ23 DESCRIPTION Ground Ground

Dont use Dont use +5 Vdc +5 Vdc Dont use Dont use Read/-write Not connected Row address strobe 0 Not connected Row address strobe 1 Not connected Output enable Not connected Ground Ground

2

SYSTEM DATA AND TROUBLESHOOTING

+5 Vdc +5 Vdc Data 16 Data 48 Data 17 Data 49 Data 18 Data 50 Data 19 Data 51 Ground Ground Data 20 Data 52 Data 21 Data 53 Data 22 Data 54 Data 23

756

MEMORY TROUBLESHOOTING

TABLE 23-4 PINOUT FOR AN OLDER 144-PIN SMALL-OUTLINE (SO) DIMM (CONTINUED) PIN 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 NORMAL DQ55 VCC VCC A6 A7 A8 A11 VSS VSS A9 A12 A10 A13 VCC VCC CAS2 CAS6 CAS3 CAS7 VSS VSS DQ24 DQ56 DQ25 DQ57 DQ26 DQ58 DQ27 DQ59 VCC VCC DQ28 DQ60 DQ29 DQ61 DQ30 DQ62 DQ31 DQ63 VSS VSS SDA SCL VCC VCC ECC DQ55 VCC VCC A6 A7 A8 A11 VSS VSS A9 A12 A10 A13 VCC VCC CAS2 CAS6 CAS3 CAS7 VSS VSS DQ24 DQ56 DQ25 DQ57 DQ26 DQ58 DQ27 DQ59 VCC VCC DQ28 DQ60 DQ29 DQ61 DQ30 DQ62 DQ31 DQ63 VSS VSS SDA SCL VCC VCC DESCRIPTION Data 55 +5 Vdc +5 Vdc Address 6 Address 7 Address 8 Address 11 Ground Ground Address 9 Address 12 Address 10 Address 13 +5 Vdc +5 Vdc Column address strobe 2 Column address strobe 6 Column address strobe 3 Column address strobe 7 Ground Ground Data 24 Data 56 Data 25 Data 57 Data 26 Data 58 Data 27 Data 59 +5 Vdc +5 Vdc Data 28 Data 60 Data 29 Data 61 Data 30 Data 62 Data 31 Data 63 Ground Ground

+5 Vdc +5 Vdc

MEMORY PACKAGE STYLES AND STRUCTURES

757

TABLE 23-5 PINOUT OF A 168-PIN UNBUFFERED DRAM DIMM PIN 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 NON-PARITY VSS DQ0 DQ1 DQ2 DQ3 VCC DQ4 DQ5 DQ6 DQ7 DQ8 VSS DQ9 DQ10 DQ11 DQ12 DQ13 VCC DQ14 DQ15 n/c n/c VSS n/c n/c VCC WE0 CAS0 CAS1 RAS0 OE0 VSS A0 A2 A4 A6 A8 A10 A12 VCC VCC DU VSS OE2 PARITY VSS DQ0 DQ1 DQ2 DQ3 VCC DQ4 DQ5 DQ6 DQ7 DQ8 VSS DQ9 DQ10 DQ11 DQ12 DQ13 VCC DQ14 DQ15 CB0 CB1 VSS n/c n/c VCC WE0 CAS0 CAS1 RAS0 OE0 VSS A0 A2 A4 A6 A8 A10 A12 VCC VCC DU VSS OE2 72 ECC VSS DQ0 DQ1 DQ2 DQ3 VCC DQ4 DQ5 DQ6 DQ7 DQ8 VSS DQ9 DQ10 DQ11 DQ12 DQ13 VCC DQ14 DQ15 CB0 CB1 VSS n/c n/c VCC WE0 CAS0 CAS1 RAS0 OE0 VSS A0 A2 A4 A6 A8 A10 A12 VCC VCC DU VSS OE2 80 ECC VSS DQ0 DQ1 DQ2 DQ3 VCC DQ4 DQ5 DQ6 DQ7 DQ8 VSS DQ9 DQ10 DQ11 DQ12 DQ13 VCC DQ14 DQ15 CB0 CB1 VSS CB8 CB9 VCC WE0 CAS0 CAS1 RAS0 OE0 VSS A0 A2 A4 A6 A8 A10 A12 VCC VCC DU VSS OE2 DESCRIPTION Ground Data 0 Data 1 Data 2 Data 3 +5 Vdc or +3.3 Vdc Data 4 Data 5 Data 6 Data 7 Data 8 Ground Data 9 Data 10 Data 11 Data 12 Data 13 +5 Vdc or +3.3 Vdc Data 14 Data 15 Parity/check-bit input/output 0 Parity/check-bit input/output 1 Ground Parity/check-bit input/output 8 Parity/check-bit input/output 9 +5 Vdc or +3.3 Vdc Read/write input Column address strobe 0 Column address strobe 1 Row address strobe 0 Output enable Ground Address 0 Address 2 Address 4 Address 6 Address 8 Address 10 Address 12 +5 Vdc or +3.3 Vdc +5 Vdc or +3.3 Vdc Dont use Ground Output enable 2

2

SYSTEM DATA AND TROUBLESHOOTING

758

MEMORY TROUBLESHOOTING

TABLE 23-5 PINOUT OF A 168-PIN UNBUFFERED DRAM DIMM (CONTINUED) PIN 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 NON-PARITY RAS2 CAS2 CAS3 WE2 VCC n/c n/c n/c n/c VSS DQ16 DQ17 DQ18 DQ19 VCC DQ20 n/c DU n/c VSS DQ21 DQ22 DQ23 VSS DQ24 DQ25 DQ26 DQ27 VCC DQ28 DQ29 DQ30 DQ31 VSS n/c n/c n/c SDA SCL VCC VSS DQ32 DQ33 DQ34 PARITY RAS2 CAS2 CAS3 WE2 VCC n/c n/c CB2 CB3 VSS DQ16 DQ17 DQ18 DQ19 VCC DQ20 n/c DU n/c VSS DQ21 DQ22 DQ23 VSS DQ24 DQ25 DQ26 DQ27 VCC DQ28 DQ29 DQ30 DQ31 VSS n/c n/c n/c SDA SCL VCC VSS DQ32 DQ33 DQ34 72 ECC RAS2 CAS2 CAS3 WE2 VCC n/c n/c CB2 CB3 VSS DQ16 DQ17 DQ18 DQ19 VCC DQ20 n/c DU n/c VSS DQ21 DQ22 DQ23 VSS DQ24 DQ25 DQ26 DQ27 VCC DQ28 DQ29 DQ30 DQ31 VSS n/c n/c n/c SDA SCL VCC VSS DQ32 DQ33 DQ34 80 ECC RAS2 CAS2 CAS3 WE2 VCC CB10 CB11 CB2 CB3 VSS DQ16 DQ17 DQ18 DQ19 VCC DQ20 n/c DU n/c VSS DQ21 DQ22 DQ23 VSS DQ24 DQ25 DQ26 DQ27 VCC DQ28 DQ29 DQ30 DQ31 VSS n/c n/c n/c SDA SCL VCC VSS DQ32 DQ33 DQ34 DESCRIPTION Row address strobe 2 Column address strobe 2 Column address strobe 3 Read/write Input 2 +5 Vdc or +3.3 Vdc Parity/check bit input/output 10 Parity/check bit input/output 11 Parity/check bit input/output 2 Parity/check bit input/output 3 Ground Data 16 Data 17 Data 18 Data 19 +5 Vdc or +3.3 Vdc Data 20 Not connected Dont use Not connected Ground Data 21 Data 22 Data 23 Ground Data 24 Data 25 Data 26 Data 27 +5 Vdc or +3.3 Vdc Data 28 Data 29 Data 30 Data 31 Ground Not connected Not connected Not connected Serial data Serial clock +5 Vdc or +3.3 Vdc Ground Data 32 Data 33 Data 34

MEMORY PACKAGE STYLES AND STRUCTURES

759

TABLE 23-5 PINOUT OF A 168-PIN UNBUFFERED DRAM DIMM (CONTINUED) PIN 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 NON-PARITY DQ35 VCC DQ36 DQ37 DQ38 DQ39 DQ40 VSS DQ41 DQ42 DQ43 DQ44 DQ45 VCC DQ46 DQ47 n/c n/c VSS n/c n/c VCC DU CAS4 CAS5 RAS1 DU VSS A1 A3 A5 A7 A9 A11 A13 VCC DU DU VSS DU RAS3 CAS6 CAS7 DU PARITY DQ35 VCC DQ36 DQ37 DQ38 DQ39 DQ40 VSS DQ41 DQ42 DQ43 DQ44 DQ45 VCC DQ46 DQ47 CB4 CB5 VSS n/c n/c VCC DU CAS4 CAS5 RAS1 DU VSS A1 A3 A5 A7 A9 A11 A13 VCC DU DU VSS DU RAS3 CAS6 CAS7 DU 72 ECC DQ35 VCC DQ36 DQ37 DQ38 DQ39 DQ40 VSS DQ41 DQ42 DQ43 DQ44 DQ45 VCC DQ46 DQ47 CB4 CB5 VSS n/c n/c VCC DU CAS4 CAS5 RAS1 DU VSS A1 A3 A5 A7 A9 A11 A13 VCC DU DU VSS DU RAS3 CAS6 CAS7 DU 80 ECC DQ35 VCC DQ36 DQ37 DQ38 DQ39 DQ40 VSS DQ41 DQ42 DQ43 DQ44 DQ45 VCC DQ46 DQ47 CB4 CB5 VSS CB12 CB13 VCC DU CAS4 CAS5 RAS1 DU VSS A1 A3 A5 A7 A9 A11 A13 VCC DU DU VSS DU RAS3 CAS6 CAS7 DU DESCRIPTION Data 35 +5 Vdc or +3.3 Vdc Data 36 Data 37 Data 38 Data 39 Data 40 Ground Data 41 Data 42 Data 43 Data 44 Data 45 +5 Vdc or +3.3 Vdc Data 46 Data 47 Parity/check bit input/output 4 Parity/check bit input/output 5 Ground Parity/check bit input/output 12 Parity/check bit input/output 13 +5 Vdc or +3.3 Vdc Dont use Column address strobe 4 Column address strobe 5 Row address strobe 1 Dont use Ground Address 1 Address 3 Address 5 Address 7 Address 9 Address 11 Address 13 +5 Vdc or +3.3 Vdc Dont use Dont use Ground Dont use Column address strobe 3 Column address strobe 6 Column address strobe 7 Dont use

2

SYSTEM DATA AND TROUBLESHOOTING

760

MEMORY TROUBLESHOOTING

TABLE 23-5 PINOUT OF A 168-PIN UNBUFFERED DRAM DIMM (CONTINUED) PIN 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 NON-PARITY VCC n/c n/c n/c n/c VSS DQ48 DQ49 DQ50 DQ51 VCC DQ52 n/c DU n/c VSS DQ53 DQ54 DQ55 VSS DQ56 DQ57 DQ58 DQ59 VCC DQ60 DQ61 DQ62 DQ63 VSS CK3 n/c SA0 SA1 SA2 VCC PARITY VCC n/c n/c CB6 CB7 VSS DQ48 DQ49 DQ50 DQ51 VCC DQ52 n/c DU n/c VSS DQ53 DQ54 DQ55 VSS DQ56 DQ57 DQ58 DQ59 VCC DQ60 DQ61 DQ62 DQ63 VSS CK3 n/c SA0 SA1 SA2 VCC 72 ECC VCC n/c n/c CB6 CB7 VSS DQ48 DQ49 DQ50 DQ51 VCC DQ52 n/c DU n/c VSS DQ53 DQ54 DQ55 VSS DQ56 DQ57 DQ58 DQ59 VCC DQ60 DQ61 DQ62 DQ63 VSS CK3 n/c SA0 SA1 SA2 VCC 80 ECC VCC CB14 CB15 CB6 CB7 VSS DQ48 DQ49 DQ50 DQ51 VCC DQ52 n/c DU n/c VSS DQ53 DQ54 DQ55 VSS DQ56 DQ57 DQ58 DQ59 VCC DQ60 DQ61 DQ62 DQ63 VSS CK3 n/c SA0 SA1 SA2 VCC DESCRIPTION +5 Vdc or +3.3 Vdc Parity/check bit input/output 14 Parity/check bit input/output 15 Parity/check bit input/output 6 Parity/check bit input/output 7 Ground Data 48 Data 49 Data 50 Data 51 +5 Vdc or +3.3 Vdc Data 52 Not connected Dont use Not connected Ground Data 53 Data 54 Data 55 Ground Data 56 Data 57 Data 58 Data 59 +5 Vdc or +3.3 Vdc Data 60 Data 61 Data 62 Data 63 Ground Not connected Serial address 0 Serial address 1 Serial address 2 +5 Vdc or +3.3 Vdc

TABLE 23-6 PINOUT OF A 168-PIN UNBUFFERED SDRAM DIMM PIN 1 2 3 4 NON-PARITY VSS DQ0 DQ1 DQ2 72 ECC VSS DQ0 DQ1 DQ2 80 ECC VSS DQ0 DQ1 DQ2 DESCRIPTION Ground Data 0 Data 1 Data 2

MEMORY PACKAGE STYLES AND STRUCTURES

761

TABLE 23-6 PINOUT OF A 168-PIN UNBUFFERED SDRAM DIMM (CONTINUED) PIN 4 48 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 NON-PARITY DQ2 DU DQ3 VDD DQ4 DQ5 DQ6 DQ7 DQ8 VSS DQ9 DQ10 DQ11 DQ12 DQ13 VDD DQ14 DQ15 n/c n/c VSS n/c n/c VDD WE DQMB0 DQMB1 S0 DU VSS A0 A2 A4 A6 A8 A10/AP BA1 VDD VDD CK0 VSS DU S2 DQMB2 DQMB3 72 ECC DQ2 DU DQ3 VDD DQ4 DQ5 DQ6 DQ7 DQ8 VSS DQ9 DQ10 DQ11 DQ12 DQ13 VDD DQ14 DQ15 CB0 CB1 VSS n/c n/c VDD WE DQMB0 DQMB1 S0 DU VSS A0 A2 A4 A6 A8 A10/AP BA1 VDD VDD CK0 VSS DU S2 DQMB2 DQMB3 80 ECC DQ2 DU DQ3 VDD DQ4 DQ5 DQ6 DQ7 DQ8 VSS DQ9 DQ10 DQ11 DQ12 DQ13 VDD DQ14 DQ15 CB0 CB1 VSS CB8 CB9 VDD WE DQMB0 DQMB1 S0 DU VSS A0 A2 A4 A6 A8 A10/AP BA1 VDD VDD CK0 VSS DU S2 DQMB2 DQMB3 DESCRIPTION Data 2 Dont use Data 3 +5 Vdc or +3.3 Vdc Data 4 Data 5 Data 6 Data 7 Data 8 Ground Data 9 Data 10 Data 11 Data 12 Data 13 +5 Vdc or +3.3 Vdc Data 14 Data 15 Parity/check-bit input/output 0 Parity/check-bit input/output 1 Ground Parity/check-bit input/output 8 Parity/check-bit input/output 9 +5 Vdc or +3.3 Vdc Read/-write Byte mask signal 0 Byte mask signal 1 Chip select Dont use Ground Address 0 Address 2 Address 4 Address 6 Address 8 Address 10 Bank address 1 +5 Vdc or +3.3 Vdc +5 Vdc or +3.3 Vdc Clock signal 0 Ground Dont use Chip select 2 Byte mask signal 2 Byte mask signal 3

2

SYSTEM DATA AND TROUBLESHOOTING

762

MEMORY TROUBLESHOOTING

TABLE 23-6 PINOUT OF A 168-PIN UNBUFFERED SDRAM DIMM (CONTINUED) PIN 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82S 83S 84 85 86 87 88 89 90 91 92 NON-PARITY DU VDD n/c n/c n/c n/c VSS DQ16 DQ17 DQ18 DQ19 VDD DQ20 n/c Vref,NC CKE1 VSS DQ21 DQ22 DQ23 VSS DQ24 DQ25 DQ26 DQ27 VDD DQ28 DQ29 DQ30 DQ31 VSS CK2 n/c n/c DAS CLS VDD VSS DQ32 DQ33 DQ34 DQ35 VDD DQ36 DQ37 72 ECC DU VDD n/c n/c CB2 CB3 VSS DQ16 DQ17 DQ18 DQ19 VDD DQ20 n/c Vref,NC CKE1 VSS DQ21 DQ22 DQ23 VSS DQ24 DQ25 DQ26 DQ27 VDD DQ28 DQ29 DQ30 DQ31 VSS CK2 n/c n/c DAS CLS VDD VSS DQ32 DQ33 DQ34 DQ35 VDD DQ36 DQ37 80 ECC DU VDD CB10 CB11 CB2 CB3 VSS DQ16 DQ17 DQ18 DQ19 VDD DQ20 n/c Vref,NC CKE1 VSS DQ21 DQ22 DQ23 VSS DQ24 DQ25 DQ26 DQ27 VDD DQ28 DQ29 DQ30 DQ31 VSS CK2 n/c n/c DAS CLS VDD VSS DQ32 DQ33 DQ34 DQ35 VDD DQ36 DQ37 DESCRIPTION Dont use +5 Vdc or +3.3 Vdc Parity/check-bit input/output 10 Parity/check-bit input/output 11 Parity/check-bit input/output 2 Parity/check-bit input/output 3 Ground Data 16 Data 17 Data 18 Data 19 +5 Vdc or +3.3 Vdc Data 20 Not connected Clock enable signal 1 Ground Data 21 Data 22 Data 23 Ground Data 24 Data 25 Data 26 Data 27 +5 Vdc or +3.3 Vdc Data 28 Data 29 Data 30 Data 31 Ground Clock signal 2 Not connected Not connected Serial data Serial clock +5 Vdc or +3.3 Vdc Ground Data 32 Data 33 Data 34 Data 35 +5 Vdc or +3.3 Vdc Data 36 Data 37

MEMORY PACKAGE STYLES AND STRUCTURES

763

TABLE 23-6 PINOUT OF A 168-PIN UNBUFFERED SDRAM DIMM (CONTINUED) PIN 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 NON-PARITY DQ38 DQ39 DQ40 VSS DQ41 DQ42 DQ43 DQ44 DQ45 VDD DQ46 DQ47 n/c n/c VSS n/c n/c VDD CAS DQMB4 DQMB5 S1 RAS VSS A1 A3 A5 A7 A9 BA0 A11 VDD CK1 A12 VSS CKE0 S3 DQMB6 DQMB7 A13 VDD n/c n/c n/c n/c 72 ECC DQ38 DQ39 DQ40 VSS DQ41 DQ42 DQ43 DQ44 DQ45 VDD DQ46 DQ47 CB4 CB5 VSS n/c n/c VDD CAS DQMB4 DQMB5 S1 RAS VSS A1 A3 A5 A7 A9 BA0 A11 VDD CK1 A12 VSS CKE0 S3 DQMB6 DQMB7 A13 VDD n/c n/c CB6 CB7 80 ECC DQ38 DQ39 DQ40 VSS DQ41 DQ42 DQ43 DQ44 DQ45 VDD DQ46 DQ47 CB4 CB5 VSS CB12 CB13 VDD CAS DQMB4 DQMB5 S1 RAS VSS A1 A3 A5 A7 A9 BA0 A11 VDD CK1 A12 VSS CKE0 S3 DQMB6 DQMB7 A13 VDD CB14 CB15 CB6 CB7 DESCRIPTION Data 38 Data 39 Data 40 Ground Data 41 Data 42 Data 43 Data 44 Data 45 +5 Vdc or +3.3 Vdc Data 46 Data 47 Parity/check-bit input/output 4 Parity/check-bit input/output 5 Ground Parity/check-bit input/output 12 Parity/check-bit input/output 13 +5 Vdc or +3.3 Vdc Column address strobe Byte mask signal 4 Byte mask signal 5 Chip select 1 Row address strobe Ground Address 1 Address 3 Address 5 Address 7 Address 9 Bank address 0 Address 11 +5 Vdc or +3.3 Vdc Clock signal 1 Address 12 Ground Clock enable signal 0 Chip Select 3 Byte mask signal 6 Byte mask signal 7 Address 13 +5 Vdc or +3.3 Vdc Parity/check-bit input/output 14 Parity/check-bit input/output 15 Parity/check-bit input/output 6 Parity/check-bit input/output 7

2

SYSTEM DATA AND TROUBLESHOOTING

764

MEMORY TROUBLESHOOTING

TABLE 23-6 PINOUT OF A 168-PIN UNBUFFERED SDRAM DIMM (CONTINUED) PIN 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 NON-PARITY VSS DQ48 DQ49 DQ50 DQ51 VDD DQ52 n/c Vref,NC n/c VSS DQ53 DQ54 DQ55 VSS DQ56 DQ57 DQ58 DQ59 VDD DQ60 DQ61 DQ62 DQ63 VSS CK3 n/c SA0 SA1 SA2 VDD 72 ECC VSS DQ48 DQ49 DQ50 DQ51 VDD DQ52 n/c Vref,NC n/c VSS DQ53 DQ54 DQ55 VSS DQ56 DQ57 DQ58 DQ59 VDD DQ60 DQ61 DQ62 DQ63 VSS CK3 n/c SA0 SA1 SA2 VDD 80 ECC VSS DQ48 DQ49 DQ50 DQ51 VDD DQ52 n/c Vref,NC n/c VSS DQ53 DQ54 DQ55 VSS DQ56 DQ57 DQ58 DQ59 VDD DQ60 DQ61 DQ62 DQ63 VSS CK3 n/c SA0 SA1 SA2 VDD DESCRIPTION Ground Data 48 Data 49 Data 50 Data 51 +5 Vdc or +3.3 Vdc Data 52 Not connected Not connected Ground Data 53 Data 54 Data 55 Ground Data 56 Data 57 Data 58 Data 59 +5 Vdc or +3.3 Vdc Data 60 Data 61 Data 62 Data 63 Ground Clock signal 3 Not connected Serial address 0 Serial address 1 Serial address 2 +5 Vdc or +3.3 Vdc

to be exactbut manufacturers often round down to the nearest million or so). The idea of megabytes (MB) is important when measuring memory in your PC. For example, if a SIMM is laid out as 1M by 8 bits, it has 1MB. If the SIMM is laid out as 4M by 8 bits, it has 4MB. Unfortunately, memory has not been laid out as 8 bits since the IBM XT. More practical memory layouts involve 32-bit memory (for 486 and OverDrive processors) or 64-bit memory (for Pentium processors). When memory is wider than one byte, it is still measured in MB. For example, a 1M 32-bit (4 bytes) SIMM would be 4MB (that is, the capacity of the device is 4MB), and a 4M 32-bit SIMM would be 16MB. So when you go shopping for an 8MB 72-pin SIMM, chances are that youre getting a 2M 32-bit memory module. Table 23-7 provides you with an index to help identify common 72-pin SIMMs. You can see the relationship between memory layout and overall capacity.

MEMORY ORGANIZATION

765

TABLE 23-7 72-PIN SIMM IDENTIFICATION GUIDELINES CONFIGURATION 36 chips: (36) 16 1 SOJs or 12 chips: (8) 16 4, (4) 16 1 SOJs 24 chips: (16) 4 4 SOJs, (8) 4 1 SOJs 12 chips: (8) 4 4 SOJs, (4) 4 1 SOJs 24 chips: (16) 1 4 SOJs, (8) 1 1 SOJs 12 chips: (8) 1 4 SOJs, (4) 1 1 SOJs 4 chips: (4) 256 18 SOJs or 24 chips: (16) 256 4 SOJs, & (8) 256 1 PLCC 12 chips: (8) 256 4 SOJs, & (4) 256 1 PLCC 32 chips: (32) 16 1 SOJs or 8 chips: (8) 16 4 SOJs 16 chips: (16) 4 4 SOJs 8 chips: (8) 4 4 SOJs 16 chips: (16) 1 4 SOJs or 4 chips: (4) 1 16 SOJs 8 chips: (8) 1 4 SOJs or 2 chips: (2) 1 16 SOJs 16 chips: (16) 256 4 SOJs 8 chips: (8) 256 4 SOJs DESCRIPTION Parity SIMM, usually double sided Parity SIMM, usually double sided Parity SIMM, double or single sided Parity SIMM, usually double sided Parity SIMM, double or single sided Parity SIMM, usually double sided CAPACITY 64MB 32MB 16MB 8MB 4MB 2MB TYPE 16 36 8 36 4 36 2 36 1 36 512 36

Parity SIMM Non-parity SIMM, usually double sided Non-parity SIMM, usually double sided Non-parity SIMM, usually single sided Non-parity SIMM, usually double sided Non-parity SIMM, usually single sided Non-parity SIMM, usually double sided Non-parity SIMM

1MB 64MB 32MB 16MB 8MB 4MB 2MB 1MB

256 36 16 32 8 32 4 32 2 32 1 32 512 32 256 32

2

SYSTEM DATA AND TROUBLESHOOTING

Memory Organization

The memory in your computer represents the result of evolution over several computer generations. Memory operation and handling is taken care of by your systems microprocessor. As CPUs improved, memory-handling capabilities have improved as well. Todays microprocessors, such as the Intel Pentium or Pentium Pro, are capable of addressing more than 4GB of system memorywell beyond the levels of contemporary software applications. Unfortunately, the early PCs were not nearly so powerful. Older PCs could only address 1MB of memory because of the limitations of the 8088 microprocessor. Because backward compatibility is so important to computer users, the drawbacks and limitations of older systems had to be carried forward into newer computers, instead of being eliminated. Newer systems overcome their inherent limitations by adding different types of memory, along with the hardware and software to access the memory. This part of the chapter describes the typical classifications of computer memory: conventional, extended, and expanded memory. This chapter also describes high memory concepts. Notice that these memory types have nothing to do with the actual ICs in your system, but the way in which software uses the memory.

CONVENTIONAL MEMORY

Conventional memory is the traditional 640KB assigned to the DOS Memory Area (10000h to 9FFFFh, as shown in Fig. 23-4). The original PCs used microprocessors that

766

MEMORY TROUBLESHOOTING

1024Kb System ROM

FFFFFh F0000h System ROM E0000h Optional/user ROM D0000h Optional/user ROM C0000h Video RAM Video RAM B0000h A0000h User area 90000h User area 70000h User area 50000h User area System/user area 10000h User area 00000h Conventional and upper memory in a typical PC. 30000h

640Kb

0Kb

FIGURE 23-4

could only address 1MB of memory (called real-mode memory or base memory). Out of that 1MB, portions of the memory must be set aside for basic system functions. BIOS code, video memory, interrupt vectors, and BIOS data are only some of the areas that require reserved memory. The remaining 640KB became available to load and run your application, which can be any combination of executable code and data. The original PC only provided 512KB for the DOS program area, but computer designers quickly learned that another 128KB could be added to the DOS area while still retaining enough memory for overhead functions, so 512KB became 640KB. Every IBM-compatible PC still provides a 640KB base memory range, and most DOS application programs continue to fit within that limit to ensure backward compatibility to older systems. However, the drawbacks to the 8088 CPU were soon apparent. More memory had to added to the computer for its evolution to continue. Yet, memory had to be added in a way that did not interfere with the conventional memory area. Table 23-8 illustrates a comprehensive memory map for a typical PC.

EXTENDED MEMORY

The 80286 introduced in IBMs PC/AT was envisioned to overcome the 640KB barrier by incorporating a protected mode of addressing. The 80286 can address up to 16MB of memory in protected mode, and its successors (the 80386 and later) can handle 4GB of protected-

MEMORY ORGANIZATION

767

TABLE 23-8 REAL-MODE MEMORY MAP OF A TYPICAL PC ADDRESS RANGE (H) 00000003FF 00000 00004 00008 0000C 00010 00014 00018 0001C 00020 00024 00028 0002C 00030 00034 00038 0003C 00040 00044 00048 0004C 00050 00054 00058 0005C 00060 00064 00068 0006C 00070 00074 00078 0007C 00080 00084 00088 0008C 00090 00094 00098 0009C 000A0

DESCRIPTION Interrupt Vector Table (256 double words): INT 00H Divide-by-zero interrupt handler INT 01H Single-step interrupt handler INT 02H Non-maskable interrupt (memory parity or I/O error) INT 03H Breakpoint INT 04H Arithmetic overflow interrupt handler INT 05H Print screen INT 06H Reserved INT 07H Reserved INT 08H Timer-interrupt routine (18.21590 /sec) IRQ0 INT 09H Keyboard service routine IRQ1 INT 0AH VGA retrace (and AT slave interrupts) IRQ2 INT 0BH Serial device 2 service routine IRQ3 INT 0CH Serial device 1 service routine IRQ4 INT 0DH Hard-disk interrupt routine IRQ5 INT 0EH Diskette interrupt routine IRQ6 INT 0FH Parallel-port service routine IRQ7 INT 10H Video services INT 11H Equipment check INT 12H Memory-size check INT 13H Diskette and hard disk I/O INT 14H RS-232 service call INT 15H System services calls INT 16H Keyboard call INT 17H Printer I/O call INT 18H Basic ROM entry (startup) INT 19H Boot loader: implement system (IPL) from disk INT 1AH Time-of-day call INT 1BH Keyboard break address INT 1CH User timer interrupt INT 1DH Monitor ROMfor 6845 video inititialization INT 1EH Disk-control table pointer INT 1FH Alphanumeric character pattern table pointer INT 20H DOS terminate program INT 21H Microsoft DOS function calls INT 22H DOS terminate address (not a callable function) INT 23H DOS Ctrl-break exit address (not a callable function) INT 24H DOS fatal-error exit address (not a callable function) INT 25H DOS absolute disk read INT 26H DOS absolute disk write INT 27H Terminate and stay resident (control passes to COMMAND.COM) INT 28H Idle loop, spooler waiting; issued by DOS when waiting

2

SYSTEM DATA AND TROUBLESHOOTING

768

MEMORY TROUBLESHOOTING

TABLE 23-8 REAL-MODE MEMORY MAP OF A TYPICAL PC (CONTINUED) ADDRESS RANGE (H) 000A4 000A8 000AC 000B8 000BC 000C0 000C8 000CC 000D0 000FC 00100 00104 00108 0010C 00100 00114 00118 0011C 00120 00124 00128 0012C 00140 00144 00168 0016C 00170 00174 00180 0019C 001A0 001B0 001B4 001C0 001C4 001C8 001CC 001D0 001D4 001D8 001DC 001E0

DESCRIPTION INT 29H CON device raw output handler INT 2AH 3.x Network communications INT 2BH-2DH reserved for DOS INT 2EH Execute DOS command (undocumented) INT 2FH Print spool control (Multiplex Interrupt) INT 30H-31H Internal use INT 32H Reserved for DOS INT 33H Microsoft mouse-driver calls INT 34H-3EH Reserved for DOS INT 3FH Used by LINK to manage overlay segments INT 40H Fixed-disk/floppy-disk handler INT 41H ROM pointer; fixed-disk parameters INT 42H EGA: video vector screen BIOS entry INT 43H EGA: Initialization parameters INT 44H EGA: Graphics-character patterns INT 45H Reserved INT 46H AT: Pointer to second fixed disk parameters INT 47H Reserved INT 48H PCjr cordless-keyboard Xlat routine INT 49H PCjr non-keyboard scan-code Xlat table INT 4AH AT, PS/2 user alarm routine INT 4BH-4FH Reserved INT 50H Periodic alarm interrupt from timer INT 51H-59H Reserved INT 5AH Cluster adapter BIOS-entry address INT 5BH Cluster boot INT 5CH NETBIOS entry point INT 5DH-5FH Reserved INT 60H-66H Reserved for user program interrupts INT 67H EMM: Expanded memory manager routines INT 68H-6BH Unused INT 6CH System-resume vector INT 6DH-6FH Unused INT 70H Real-time clock INT 71H LAN adapter INT 72H Reserved INT 73H Reserved INT 74H Mouse interrupt INT 75H 80287 NMI Error INT 76H Fixed disk controller INT 77H Reserved INT 78H-7FH Unused

IRQ8 IRQ9 IRQ10 IRQ11 IRQ12 IRQ13 IRQ14 IRQ15

MEMORY ORGANIZATION

769

TABLE 23-8 REAL-MODE MEMORY MAP OF A TYPICAL PC (CONTINUED) ADDRESS RANGE (H) 00200 00218 0021C 003C4 003FF 00400-004FF 00400 00408 0040E 00410

DESCRIPTION INT 80H-85H Reserved for BASIC INT 86H AT: NetBIOS relocated INT 18H INT 87H-F0H Reserved for BASIC interpreter INT F1H-FFH Reserved for user program interrupts Used for power-on and initial boot stack BIOS Data Area: COM1: to COM4: port addresses LPT1: to LPT3: port addresses LPT4: address except PS/2 reserved Equipment flag bits: 1514 Number of LPTs attached 13 Internal modem (CVT) or reserved 12 Joystick 119 Number of COMs 8 Unused (jr: DMS chip present) 76 Number of disk drives 5 1 = 80 25 0 = 40 25 screen 4 1 = color 0 = monochrome 32 00 = 64K chips; 11 = 256K chips (PC,XT,AT) 1 Math coprocessor installed 0 IPL disk installed Init. flag; reserved (CVT self-test status) Memory size in K bytes Reserved Reserved Keyboard monitor flag bytes 0 and 1: bit: 7 ins lock 7 ins pressed 6 caps lock 6 caps pressed 5 num lock 5 num lock pressed 4 scroll lock 4 scroll pressed 3 alt pressed 3 pause locked 2 crtl pressed 2 sysreq pressed 1 <shift press 1 <alt pressed 0 >shift press 0 >alt pressed Alternate keypad entry Keyboard buffer head pointer Keyboard buffer tail pointer Keyboard buffer Drive recalibration status bit: 7 Interrupt flag 64 Reserved 3 Recalibrate drive 3 2 Recalibrate drive 2 1 Recalibrate drive 1 0 Recalibrate drive 0

2

SYSTEM DATA AND TROUBLESHOOTING

00412 00413 00415 00416 00417

00419 0041A 0041C 0041E 0043E

770

MEMORY TROUBLESHOOTING

TABLE 23-8 REAL-MODE MEMORY MAP OF A TYPICAL PC (CONTINUED) ADDRESS RANGE (H) 0043F

DESCRIPTION Motor status bit: 7 Currently reading or writing 6 Reserved 54 00 Drive 0 Selected 01 Drive 1 Selected 10 Drive 2 Selected 11 Drive 3 Selected 3-0 Drive 3-0 motor on status Motor-control time-out counter Diskette Status Return Code 00H No error 01H Invalid diskette drive parameter 02H Address mark not found 03H Write-protect error 04H Requested sector not found 05H Reserved 06H Diskette change line active 07H Reserved 08H DMA overrun on operation 09H Attempt to DMA across a 64K boundary 0AH Reserved 0BH Reserved 0CH Media type not found 0DH Reserved 0EH Reserved 0FH Reserved 10H CRC error on diskette read 20H General controller failure 40H Seek operation failed 80H Diskette drive not ready Diskette drive controller status bytes (NEC) CRT_MODE bit: 7 Text 80 25 mono on mono card 6 Graphics 640 200 mono on color card 5 Graphics 320 200 mono on color card 4 Graphics 320 200 on color card 3 Text 80 25 color 2 Text 80 25 mono on color 1 Text 40 25 color 0 Text 40 25 mono on color card CRT_COLS Number of columns (80) CRT_LEN Length of regen buffer in bytes CRT_START Starting address in regen buffer Cursor position on each of eight pages CURSOR_MODE top-bottom line of cursor (cursor type) ACTIVE_PAGE index ADDR_6845 Base address for 6845 display chip 3B4H for monochrome 3D4H for color

00440 00441

00442 00449

0044A 0044C 0044E 00450 00460 00462 00463

MEMORY ORGANIZATION

771

TABLE 23-8 REAL-MODE MEMORY MAP OF A TYPICAL PC (CONTINUED) ADDRESS RANGE (H) 00465

DESCRIPTION CRT_MODE_SETTING for 3 x 8 register 3B8H for MDA 3D8H for CGA CRT_PALLETTE setting register (3D9H) on color card Temporary storage for SS:SP during shutdown Flag to indicate interrupt Timer counter (timer low, timer high words) Timer overflow (24-hour roll-over flag byte) Break key state (bit 7 = 1 if break key pressed) Reset flag word: 1234 bypass memory test 4321 preserve memory 5678 system suspend 9ABC manufacturing test ABCD system POST loop (CVT) Hard-disk status or reserved for ESDI Adapter/A 00H No error 01H Invalid function request 02H Address mark not found 03H Write protect error 04H Requested sector not found 05H Reset failed 06H Reserved 07H Drive parameter activity failed 08H DMA overrun on operation 09H Data boundary error 0AH Bad sector flag detected 0BH Bad track detected 0CH Reserved 0DH Invalid number of sectors on format 0EH Control data address mark detected 0FH DMA arbitration level out of range 10H Uncorrectable ECC or CRC error 20H General controller failure 40H Seek operation failed 80H Time out AAH Drive not ready BBH Undefined error occurred CCH Write fault on selected drive E0H Status error/error register 0 FFH Sense operation failed Number of hard-disk drives Fixed disk-drive control byte (PC XT) Fixed disk-drive controller port (PC XT) LPT1: to LPT4: time-out byte values (PS/2 has no LPT4:) COM1: to COM4: timeout byte values Keyboard buffer start pointer (word) Keyboard buffer end pointer (word)

00466 00467 0046B 0046C 00470 00471 00472

2

SYSTEM DATA AND TROUBLESHOOTING

00474

00475 00476 00477 00478 0047C 00480 00482

772

MEMORY TROUBLESHOOTING

TABLE 23-8 REAL-MODE MEMORY MAP OF A TYPICAL PC (CONTINUED) ADDRESS RANGE (H) 00484 00485 00487

DESCRIPTION ROWS video character Rows - 1 POINTS Height of character matrix-bytes per character INFO byte: bit: 7 Video mode number (of INT 10H funct.0) 65 Size of video RAM 0064K 10192K 01128K 11256K 4 reserved 3 (1) video subsystem is inactive 2 reserved 1 (1) video subsystem on monochrome 0 (1) alphanumeric cursor emulation enabled INFO_3 byte: bit: 7 Input FEAT1 (bit 6 of ISR0 (Input Status Reg.) 6 Input FEAT1 (bit 5 of ISR0) 5 Input FEAT0 (bit 6 of ISR0) 4 Input FEAT0 (bit 5 of ISR0) 3 EGA config. switch 4 (1=off) 2 EGA config. switch 3 1 EGA config. switch 2 0 EGA config. switch 1 Flags bit: 7 bit 4 Alphanumeric scan lines: 00 350-line mode 01 400 10 200 11 Reserved 6 (1) Display switching enabled 5 Reserved 3 (1) Default palett loading is disabled 2 (1) Using monochrome monitor 1 (1) Gray scale is enabled 0 (1) VGA is active DCC Display combination code table index (VGA) Media control bit: 76 Last diskette drive data rate selected 00500Kb per second 01300Kb per second 10250Kb per second 11reserved 54 Last diskette drive step rate selected 30 reserved Hard-disk status register Hard-disk error register Hard-disk interrupt control flag Combination hard disk/floppy card (bit 0=1) Drive-0 media-state byte Drive-1 media-state byte

00488

00489

0048A 0048B

0048C 0048D 0048E 0048F 00490 00491

MEMORY ORGANIZATION

773

TABLE 23-8 REAL-MODE MEMORY MAP OF A TYPICAL PC (CONTINUED) ADDRESS RANGE (H) 00492 00493

DESCRIPTION Drive 2 media state byte Drive 3 media state byte bit: 76 Diskette drive date rate 00500Kb per second 01300Kb per second 10250Kb per second 11Reserved 5 Double stepping required 4 Media established 3 Reserved 20 Drive/media state 000 360Kb diskette/360Kb drive not established 001 360Kb diskette/1.2Mb drive not established 010 1.2Mb diskette/1.2Mb drive not established 011 360Kb diskette/360Kb drive established 100 360Kb diskette/1.2Mb drive established 101 1.2Mb diskette/1.2Mb drive established 110 Reserved 111 None of the above Drive 0 track currently selected Drive 1 track currently selected Keyboard mode state and type flags bit: 7 Read ID in progress 6 Last character was first ID character 5 Force NumLock if read ID and KBX 4 101/102 keyboard installed 3 Right Alt key pressed 2 Right Ctrl key pressed 1 Last code was E0 hidden code 0 Last code was E1 hidden code Keyboard LED flags bit: 7 Keyboard transmit error flag 6 Mode-indicator update 5 Cancel receive flag 4 Acknowledgment received 3 = 0 reserved 2-0 Keyboard LED state bits Offset address to user wait complete flag Segment to user wait complete flag User wait count, microseconds low word User wait count, microseconds high word Wait active flag bit: 7 Wait-time elapse and post flag 61 Reserved LANA DMA channel flags LANA 0 status LANA 1 status Saved hardfile interrupt vector

2

SYSTEM DATA AND TROUBLESHOOTING

00494 00495 00496

00497

00498 0049A 0049C 0049E 004A0

004A1 004A2 004A3 004A4

774

MEMORY TROUBLESHOOTING

TABLE 23-8 REAL-MODE MEMORY MAP OF A TYPICAL PC (CONTINUED) ADDRESS RANGE (H) 004A8 004AC 004B4 004B5 004B9 004BA 004BB 004BC 004BD 004CE 004D0 004F0 00500005FF 00500

DESCRIPTION BIOS video save table and overrides Reserved Keyboard NMI control flags (CVT) Keyboard break-pending flags (CVT) Port-60 single-byte queue (CVT) Scan code of last key (CVT) Pointer-to-NMI buffer head (CVT) Pointer-to-NMI buffer tail (CVT) NMI scan-code buffer (CVT) Day counter (CVT and after) Reserved Application program communication area DOS Data Area: Print-screen status flag 1 = printer active 0FFH = printer fault Reserved for BASIC and POST work area Single-drive mode-status byte 0 = drive A 1 = drive B Reserved POST work area Reserved for BASIC BASIC Shell Flag = 2 if current shell BASIC segment address storage set with DEF SEG BASIC int 1Ch clock-interrupt vector BASIC int 23h ctrl-break interrupt vector BASIC int 24h disk-error interrupt vector BASIC dynamic storage DOS dynamic storage Used by DOS for diskette initialization Used by MODE command Reserved for DOS data Reserved for DOS I/O drivers from xIO.SYS xIO.SYS IRET for interrupts 1, 3, and 0FH during POST MS-DOS kernel from xDOS.SYS: Interrupt handlers and routines MS-DOS disk-buffer cache, FCBs and installable device drivers MCB (Memory control block, 16 bytes, paragraph aligned) Start of transient program

00501 00504

00505 00510 0050F 00510 00512 00516 0051A 0051B 00520 00522 00530 00534 00600 00700 008470FFFF

MEMORY ORGANIZATION

775

TABLE 23-8 REAL-MODE MEMORY MAP OF A TYPICAL PC (CONTINUED) ADDRESS RANGE (H) 100009FFFF A0000AFFFF B0000B3FFF B4000B7FFF B8000BBFFF BC000BFFFF C0000C3FFF C4000C5FFF C6000C63FF C6400C7FFF C8000CBFFF CC000CFFFF D0000D7FFF D8000DBFFF DC000DFFFF E0000EFFFF F0000F3FFF F4000F7FFF F8000FBFFF FC000FEFFF FF000FFFEF FFFF0FFFF3

DESCRIPTION User Data Area (programs and data) Start of EGA and VGA graphics-display RAM modes 0Dh and above Start of MDPA and Hercules graphics-display RAM Reserved for graphics-display RAM Start of CGA color graphics-display RAM Reserved for graphics-display RAM EGA BIOS ROM Video-adapter ROM space 256 bytes of PGA communication area Last 7Kb of video adapter ROM space 16K of hard-disk BIOS adapter ROM space 32K cluster-adapter BIOS ROM Last 16Kb of adapter ROM space 64K expansion ROM space (AT, PS/2) System-monitor ROM System-expansion ROMs BIOS ROM, BASIC, and simple BIOS System ROM Hardware boot far jump vector

2

SYSTEM DATA AND TROUBLESHOOTING

mode memory. Today, virtually all computer systems provide several MB of extended memory. Besides an advanced microprocessor, another key element for extended memory is software. Memory-management software must be loaded in advance for the computer to access its extended memory. Microsofts DOS 5.0 provides an extended memory manager utility (HIMEM.SYS), but other off-the-shelf utilities are available as well. Unfortunately, DOS itself cannot use extended memory. You might fill the extended memory with data, but the executable code comprising the program remains limited to the original 640KB of base memory. Some programs written with DOS extenders can overcome the 640KB limit, but the additional code needed for the extenders can make such programs a bit clunky. A DOS extender is basically a software module containing its own memory-management code, which is compiled into the final application program. The DOS extender loads a program in real-mode memory. After the program is loaded, it switches program control to the protected-mode memory. When the program in protected mode needs to execute a DOS (real mode) function, the DOS extender converts protectedmode addresses into real-mode addresses, copies any necessary program data from protected to real-mode locations, switches the CPU to real-mode addressing, and carries out the function. The DOS extender then copies any results (if necessary) back to protected-mode addresses, switches the system to protected-mode once again, and the program continues to

776

MEMORY TROUBLESHOOTING

run. This back-and-forth conversion overhead results in less-than-optimum performance, compared to strictly real-mode programs or true protected-mode programs. With multiple megabytes of extended memory typically available, it is possible (but unlikely) that any one program will utilize all of the extended memory. Multiple programs that use extended memory must not attempt to utilize the same memory locations. If conflicts occur, a catastrophic system crash is almost inevitable. To prevent conflicts in extended memory, memory-manager software can make use of three major industry standards: the Extended Memory Specification (XMS), the Virtual Control Program Interface (VCPI), or the DOS Protected-Mode Interface (DPMI). This chapter does not detail these standards, but you should know where they are used.

EXPANDED MEMORY

Expanded memory is another popular technique used to overcome the traditional 640KB limit of real-mode addressing. Expanded memory uses the same physical RAM chips, but differs from extended memory in the way that physical memory is used. Instead of trying to address physical memory locations outside of the conventional memory range, as extended memory does, expanded memory blocks are switched into the base memory range, where the CPU can access it in real mode. The original expanded memory specification (called the Lotus-Intel-Microsoft LIM or EMS specification) used 16KB banks of memory which were mapped into a 64KB range of real-mode memory existing just above the video memory range. Thus, four blocks of expanded memory could be dealt with simultaneously in the real mode. Early implementations of expanded memory utilized special expansion boards that switched blocks of memory, but later CPUs that support memory mapping allowed expanded memory managers (EMMs or LIMs) to supply software-only solutions for i386, i486, and Pentium-based machines. EMS/LIM 4.0 is the latest version of the expanded memory standard which handles up to 32MB of memory. An expanded memory manager (such as the DOS utility EMM386.EXE) allows the extended memory sitting in your computer to emulate expanded memory. For most practical purposes, expanded memory is more useful than extended memory because its ability to map directly to the real mode allows support for program multi-tasking. To use expanded memory, programs must be written specifically to take advantage of the function calls and subroutines needed to switch memory blocks. Functions are completely specified in the LIM/EMS 4.0 standard.

UPPER MEMORY AREA (UMA)

The upper 384KB of real-mode memory is not available to DOS because it is dedicated to handling memory requirements of the physical computer system. This is called the High DOS Memory Range or Upper Memory Area (UMA). However, even the most advanced PCs do not use the entire 384KB, so there is often a substantial amount of unused memory existing in your systems real-mode range. Late-model CPUs, such as the i386 and i486 can remap extended memory into the range unused by your system. Because this found memory space is not contiguous with your 640KB DOS space, DOS application programs cannot use the space, but small independent drivers and TSRs can be loaded and run from this UMA. The advantage to using high DOS memory is that more of the 640KB DOS range remains available for your application program. Memory-management programs (such as the utilities found with DOS 5.0 and higher) are needed to locate and remap these memory blocks.

MEMORY CONSIDERATIONS

777

HIGH MEMORY

A peculiar anomaly occurs with CPUs that support extended memorythey can access one segment (about 64KB) of extended memory beyond the real-mode area. This capability arises because of the address line layout on late-model CPUs. As a result, the realmode operation can access roughly 64KB above the 1MB limit. Like high DOS memory, this found 64KB is not contiguous with the normal 640KB DOS memory range, so DOS cannot use this high memory to load a DOS application, but device drivers and TSRs can be placed in high memory. DOS 5.0 is intentionally designed so that its 40 to 50KB of code can be easily moved into this high memory area. With DOS loaded into high memory, an extra 40 to 50KB or so will be available within the 640KB DOS range.

Memory Considerations

Memory has become far more important than just a place to store bits for the microprocessor. It has proliferated and specialized to the point where it is difficult to keep track of all the memory options and architectures that are available. This part of the chapter reviews established memory types, and explains some of the current memory architectures.

2

SYSTEM DATA AND TROUBLESHOOTING

MEMORY SPEED AND WAIT STATES

The PC industry is constantly struggling with the balance between price and performance. Higher prices usually bring higher performance, but low cost makes the PC appealing to more people. In terms of memory, cost-cutting typically involves using cheaper (slower) memory devices. Unfortunately, slow memory cannot deliver data to the CPU quickly enough, so the CPU must be made to wait until memory can catch up. All memory is rated in terms of speedspecifically, access time. Access time is the delay between the time data in memory is successfully addressed, to the point at which the data has been successfully delivered to the data bus. For PC memory, access time is measured in nanoseconds (ns), and current memory offers access times of 50 to 60 ns. 70-ns memory is extremely common. The question often arises: Can I use faster memory than the manufacturer recommends? The answer to this question is almost always Yes, but rarely does performance benefit. As you will see in the following sections, memory and architectures are typically tailored for specific performance. Using memory that is faster should not hurt the memory or impair system performance, but it costs more and will not produce a noticeable performance improvement. The only time such a tactic would be advised is when your current system is almost obsolete, and you would want the new memory to be useable on a new, faster motherboard if you choose to upgrade the motherboard later on. A wait state orders the CPU to pause for one clock cycle to give memory additional time to operate. Typical PCs use one wait state, although very old systems might require two or three. The latest PC designs with high-end memory or aggressive caching might be able to operate with no (zero) wait states. As you might imagine, a wait state is basically a waste of time, so more wait states result in lower system performance. Zero wait states allow optimum system performance. Table 23-9 illustrates the general relationship between CPUs, wait states, and memory speed. It is interesting to note that some of the fastest systems allow the most wait states. This flexibility lets the system support old, slow memory,

778

MEMORY TROUBLESHOOTING

TABLE 23-9 CPUS, WAIT STATES, AND MEMORY SPEED CPU 8088 8086 80286 80286 80286 80386SX 80386SX/DX 80386SX 80386DX 80386SX 80486DX 80486DX 80486SLC2 80486SLC3 80486SX 80486DX4 80486DX2 Pentium Pentium WAIT STATES 1 0 1 1 0 02 02 02 05 02 05 05 02 02 02 02 02 05 02 MEMORY ACCESS 200 ns 150 ns 150 ns 120 ns 85 ns 100 ns 85 ns 80 ns 80 ns 70 ns 80 ns 70 ns 70 ns 70 ns 70 ns 70 ns 70 ns 60 ns 50 ns

but the resulting system performance would be so poor that there would be little point in using the system in the first place. There are three classic means of selecting wait states. First, the number of wait states might be fixed (common in old XT systems). Wait states might be selected with one or more jumpers on the motherboard (typical of i286 and early i386 systems). Current systems, such as i486 and Pentium computers, place the wait state control in the CMOS setup routine. You might have to look in an advanced settings area to find the entry. When optimizing a computer, you should be sure to set the minimum number of wait states.

Setting too few wait states can cause the PC to behave erratically.

DETERMINING MEMORY SPEED

It is often necessary to check SIMMs or DIMMs for proper memory speed during troubleshooting, or when selecting replacement parts. Unfortunately, it can be very difficult to determine memory speed accurately based on part markings. Speeds are normally marked cryptically by adding a number to the end of the part number. For example, a part number ending in -6 often means 60 ns, a 7 is usually 70 ns, and a 8 can be 80 ns. Still, the only way to be absolutely certain of the memory speed is to cross reference the memory part number with a manufacturers catalog, and read the speed from the catalogs description (i.e., 4M 32 50 ns EDO).

MEMORY CONSIDERATIONS

779

PRESENCE DETECT (PD)

Another feature of modern memory devices is a series of signals known as the Presence Detect lines (youll see these as PDx signals in 72-pin pinouts, such as Table 23-2 and 233). By setting the appropriate conditions of the PD signals, it is possible for a computer to immediately recognize the characteristics of the installed memory devices, and configure itself accordingly. Presence detect lines typically specify three operating characteristics of memory: size (device layout) and speed. Table 23-10 highlights many of the most commonly used signal combinations.

UNDERSTANDING MEMORY REFRESH

The electrical signals placed in each DRAM storage cell must be replenished (or refreshed) periodically every few milliseconds. Without refresh, DRAM data will be lost. In principle, refresh requires that each storage cell be read and re-written to the memory array. This is typically accomplished by reading and re-writing an entire row of the array at one time. Each row of bits is sequentially read into a sense/refresh amplifier (part of the DRAM IC), which basically recharges the appropriate storage capacitors, then re-writes each row bit to the array. In actual operation, a row of bits is automatically refreshed whenever an array row is selected. Thus, the entire memory array can be refreshed by reading each row in the array every few milliseconds. The key to refresh is in the way DRAM is addressed. Unlike other memory ICs that supply all address signals to the IC simultaneously, a DRAM is addressed in a two-step sequence. The overall address is separated into a row (low) address and a column (high) address. Row

TABLE 23-10 INDEX OF PRESENCE DETECT (PD) SIGNALS PIN 67 (PD1) GND N/C GND N/C GND N/C GND N/C GND N/C GND N/C PIN 68 (PD2) N/C GND GND N/C N/C GND N/C GND GND N/C N/C GND PIN 69 (PD3) N/C GND N/C GND N/C PIN 70 (PD4) N/C N/C GND GND N/C PIN 71 (PD5) N/C N/C N/C N/C N/C N/C GND GND

2

SYSTEM DATA AND TROUBLESHOOTING

72-PIN SIMM Size (parity pinout) 256K 32/36 512K 32/36 1M 32/36 2M 32/36 4M 32/36 8M 32/36 256K 32/36 512K 32/36 1M 32/36 2M 32/36 4M 32/36 8M 32/36 60 ns 70 ns 80 ns 100 ns 120 ns

Size (ECC pinout)

Speed (parity/ECC pinout)

GND = Jumper installed N/C = No jumper installed

780

MEMORY TROUBLESHOOTING

address bits are placed on the DRAM address bus first, and the Row Address Select (RAS) line is pulsed logic 0 to multiplex the bits into the ICs address decoding circuitry. The low portion of the address activates an entire array row and causes each bit in the row to be sensed and refreshed. Logic 0s remain logic 0s and logic 1s are recharged to their full value. Column address bits are then placed on the DRAM address bus, and the Column Address Select (CAS) is pulsed to logic 0. The column portion of the address selects the appropriate bits within the chosen row. If a read operation is taking place, the selected bits pass through the data buffer to the data bus. During a Write operation, the Read/Write line must be logic 0, and valid data must be available to the IC before CAS is strobed. New data bits are then placed in their corresponding locations in the memory array. Even if the IC is not being accessed for reading or writing, the memory must still be refreshed to ensure data integrity. Fortunately, refresh can be accomplished by interrupting the microprocessor to run a refresh routine that simply steps through every row address in sequence (column addresses need not be selected for simple refresh). This row-only (or -RAS only) refresh technique speeds the refresh process. Although refreshing DRAM every few milliseconds might seem like a constant aggravation, the computer can execute quite a few instructions before being interrupted for refresh. Refresh operations are generally handled by the chipset on your motherboard. Often, memory problems (especially parity errors) that cannot be resolved by replacing a SIMM can be traced to a refresh fault on the motherboard.

MEMORY TYPES

For a computer to work, the CPU must take program instructions and exchange data directly with memory. As a consequence, memory must keep pace with the CPU (or make the CPU wait for it to catch up). Now that processors are so incredibly fast (and getting faster), traditional memory architectures are being replaced by specialized memory devices that have been tailored to serve specific functions in the PC. As you upgrade and repair various systems, you will undoubtedly encounter some of the following memory designations:

s DRAM (Dynamic Random-Access Memory) This remains the most recognized and

common form of computer memory. DRAM achieves a good mix of speed and density, while being relatively simple and inexpensive to produceonly a single transistor and capacitor is needed to hold a bit. Unfortunately, DRAM contents must be refreshed every few milliseconds or the contents of each bit location will decay. DRAM performance is also limited because of relatively long access times. Today, many video boards are using DRAM SIMMs to supply video memory. s SRAM (Static Random-Access Memory) The SRAM is also a classic memory design it is even older than DRAM. SRAM does not require regular refresh operations, and can be made to operate at access speeds that are much faster than DRAM. However, SRAM uses six transistors (or more) to hold a single bit. This reduces the density of SRAM and increases power demands (which is why SRAM was never adopted for general PC use in the first place). Still, the high speed of SRAM has earned it a place as the PCs L2 (or external) cache. Youll probably encounter three types of SRAM cache schemes: asynchronous, synchronous burst, and pipeline burst. s Asynchronous Static RAM (Async SRAM or ASRAM) This is the traditional form of L2 cache, introduced with i386 systems. Theres really nothing too special about ASRAM, except that its contents can be accessed much faster (20 ns, 15 ns, or 12 ns) than

MEMORY CONSIDERATIONS

781

DRAM. ASRAM does not have enough performance to be accessed synchronously, and has long since been replaced by better types of cache. s Synchronous-Burst Static RAM (Sync SRAM or SBSRAM) This is largely regarded as the best type of L2 cache for intermediate-speed motherboards (~60 to 66MHz). With access times of 8.5 ns and 12 ns, the SBSRAM can provide synchronous bursts of cache information in 2-1-1-1 cycles (i.e., 2 clock cycles for the first access, then 1 cycles per accessin time with the CPU clock). However, as motherboards pass 66MHz (i.e., 75 and 83MHz designs), SBSRAM loses its advantage to Pipelined Burst SRAM. s Pipelined-Burst Static RAM (PB SRAM) At 4.5 to 8 ns, this is the fastest form of highperformance cache now available for 75MHz+ motherboards. PBSRAM requires an extra clock cycle for lead off, but then can sync with the motherboard clock (with timing such as 3-1-1-1) across a wide range of motherboard frequencies. If youre interested in more technical details about PBSRAM, check out the ASUS site at: http://asustek.asus.com.tw/Products/TB/mem-0001.html.

s VRAM (Video Random-Access Memory) DRAM has been the traditional choice for video

2

SYSTEM DATA AND TROUBLESHOOTING

memory, but the ever-increasing demand for fast video information (i.e., high-resolution SVGA displays) requires a more efficient means of transferring data to and from video memory. Originally developed by Samsung Electronics, video RAM achieves speed improvements by using a dual data bus scheme. Ordinary RAM uses a single data bus data enters or leaves the RAM through a single set of signals. Video RAM provides an input data bus and an output data bus. This allows data to be read from video RAM at the same time new information is being written to it. You should realize that the advantages of VRAM will only be realized on high-end video systems, such as 1024 768 256 (or higher), where you can get up to 40% more performance than a DRAM video adapter. Below that, you will see no perceivable improvement with a VRAM video adapter. s FPM DRAM (Fast-Page Mode DRAM) This is a popular twist on conventional DRAM. Typical DRAM access is accomplished in a fashion similar to reading from a booka memory page is accessed first, then the contents of that page can be located. The problem is that every access requires the DRAM to re-locate the page. Fast-page mode operation overcomes this delay by allowing the CPU to access multiple pieces of data on the same page without having to re-locate the page every timeas long as the subsequent read or write cycle is on the previously located page, the FPDRAM can access the specific location on that page directly. s EDRAM (Enhanced DRAM) This is another, lesser-known variation of the classic DRAM developed by Ramtron International and United Memories. First demonstrated in August 1994, the EDRAM eliminates an external cache by placing a small amount of static RAM (cache) into each EDRAM device itself. In essence, the cache is distributed within the system RAM; as more memory is added to the PC, more cache is effectively added as well. The internal construction of an EDRAM allows it to act like page-mode memoryif a subsequent read requests data that is in the EDRAMs cache (known as a hit), the data is made available in about 15 nsroughly equal to the speed of a fair external cache. If the subsequent read requests data that is not in the cache (called a miss), the data is accessed from the DRAM portion of memory in about 35 ns, which is still much faster than ordinary DRAM. s EDO RAM (Extended Data Output RAM) EDO RAM is a relatively well-established variation to DRAM, which extends the time that output data is validthus the words

782

MEMORY TROUBLESHOOTING

presence on the data bus is extended. This is accomplished by modifying the DRAMs output buffer, which prolongs the time where read data is valid. The data will remain valid until a motherboard signal is received to release it. This eases timing constraints on the memory and allows a 15 to 30% improvement in memory performance with little real increase in cost. Because a new external signal is needed to operate EDO RAM, the motherboard must use a chipset designed to accommodate EDO. Intels Triton chipset was one of the first to support EDO, although now most chipsets (and most current motherboards) currently support EDO. EDO RAM can be used in non-EDO motherboards, but there will be no performance improvement. BEDO (Burst Extended Data Output RAM) This powerful variation of EDO RAM reads data in a burst, which means that after a valid address has been provided, the next three data addresses can be read in only one clock cycle each. The CPU can read BEDO data in a 5-1-1-1 pattern (5 clock cycles for the first address, then one clock cycle for the next three addresses. Although BEDO offers an advantage over EDO, it is only supported currently by the VIA chipsets: 580VP, 590VP, 680VP. Also, BEDO seems to have difficulty supporting motherboards over 66MHz. SDRAM (Synchronous or Synchronized DRAM) Typical memory can only transfer data during certain portions of a clock cycle. The SDRAM modifies memory operation so that outputs can be valid at any point in the clock cycle. By itself, this is not really significant, but SDRAM also provides a pipeline burst mode that allows a second access to begin before the current access is complete. This continuous memory access offers effective access speeds as fast as 10 ns, and can transfer data at up to 100MB/s. SDRAM is becoming quite popular on current motherboard designs, and is supported by the Intel VX chipset, and VIA 580VP, 590VP, and 680VP chipsets. Like BEDO, SDRAM can transfer data in a 5-1-1-1 pattern, but it can support motherboard speeds up to 100MHz, which is ideal for the 75MHz and 82MHz motherboards now becoming so vital for Pentium II systems. Check out the following references for more information on SDRAM: ~http://www.chips.ibm.com/products/memory/sdramart/sdramart.html ~http://www.fujitsu-ede.com/sdram/index.html ~http://www.ti.com/sc/docs/memory/brief.htm CDRAM (Cached DRAM) Like EDRAM, the CDRAM from Mitsubishi incorporates cache and DRAM on the same IC. This eliminates the need for an external (or L2) cache, and has the extra benefit of adding cache whenever RAM is added to the system. The difference is that CDRAM uses a set-associative cache approach that can be 15 to 20% more efficient than the EDRAM cache scheme. On the other hand, EDRAM appears to offer better overall performance. RDRAM (Rambus DRAM) Most of the memory alternatives so far have been variations of the same basic architecture. Rambus, Inc. (joint developers of EDRAM) has created a new memory architecture called the Rambus Channel. A CPU or specialized IC is used as the master device and the RDRAMs are used as slave devices. Data is then sent back and forth across the Rambus channel in 256-byte blocks. With a dual 250MHz clock, the Rambus Channel can transfer data based on the timing of both clocksthis results in data-transfer rates approaching 500MB/s (roughly equivalent to 2-ns access time). The problem with RDRAM is that a Rambus Channel would require an extensive re-design to the current PC memory architecturea move that most PC makers strenuously resist. As a result, you are most likely to see RDRAM in high-end,

MEMORY CONSIDERATIONS

783

specialized computing systems. Still, as memory struggles to match the microprocessor, PC makers might yet embrace the Rambus approach for commercial systems. s WRAM (Windows RAM) Samsung Electronics has recently introduced WRAM as a new video-specific memory device. WRAM uses multiple-bit arrays connected with an extensive internal bus and high-speed registers that can transfer data almost continuously. Other specialized registers support attributes, such as foreground color, background color, write-block control bits, and true-byte masking. Samsung claims data-transfer rates of up to 640MB/sabout 50% faster than VRAMyet WRAM devices are cheaper than their VRAM counterparts. It is likely that WRAM will receive some serious consideration in the next few years.

MEMORY TECHNIQUES

Rather than incur the added expense of specialized memory devices, PC makers often use inexpensive, well-established memory types in unique architectures designed to make the most of low-end memory. The three most-popular architectures are: paged memory, interleaved memory, and memory caching.

Paged memory This approach basically divides system RAM into small groups (or

2

SYSTEM DATA AND TROUBLESHOOTING

pages) from 512 bytes to several KB long. Memory-management circuitry on the motherboard allows subsequent memory accesses on the same page to be accomplished with zero wait states. If the subsequent access occurs outside of the current page, one or more wait states might be added while the new page is found. This is identical in principle to fast-page mode DRAM. You will find page-mode architectures implemented on high-end i286, PS/2 (model 70 and 80), and many i386 systems.

Interleaved memory This technique provides better performance than paged mem-

ory. Simply put, interleaved memory combines two banks of memory into one. The first portion is even, while the second portion is oddso memory contents are alternated between these two areas. This allows a memory access in the second portion to begin before the memory access in the first portion has finished. In effect, interleaving can double memory performance. The problem with interleaving is that you must provide twice the amount of memory as matched pairs. Most PCs that use interleaving will allow you to add memory one bank at a time, but interleaving will be disabled and system performance will suffer.

Memory caching This is perhaps the most recognized form of memory-enhancement

architecture (Fig. 23-5). Cache is a small amount (anywhere from 8KB to 1MB) of very fast SRAM, which forms an interface between the CPU and ordinary DRAM. The SRAM typically operates on the order of 5 to 15 ns, which is fast enough to keep pace with a CPU using zero wait states. A cache-controller IC on the motherboard keeps track of frequently accessed memory locations (as well as predicted memory locations), and copies those contents into cache. When a CPU reads from memory, it checks the cache first. If the needed contents are present in cache (called a cache hit), the data is read at zero wait states. If the needed contents are not present in the cache (known as a cache miss), the data must be read directly from DRAM at a penalty of one or more wait states. A small quantity of very fast

784

MEMORY TROUBLESHOOTING

Main system RAM CPU Tag RAM Cache logic Cache RAM

FIGURE 23-5

Major cache system components.