Escolar Documentos

Profissional Documentos

Cultura Documentos

6.111 Final Project Proposal: Venkat Chandar and Ben Gelb November 4, 2005

Enviado por

einu_1Descrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

6.111 Final Project Proposal: Venkat Chandar and Ben Gelb November 4, 2005

Enviado por

einu_1Direitos autorais:

Formatos disponíveis

6.

111 Final Project Proposal

Venkat Chandar and Ben Gelb November 4, 2005

Overview

Our project is a real-time video editing system. This system will be able to modify an input video stream in several ways. First, we will implement a zoom feature. This will enlarge a portion of image by a variable scale factor selected by the user. The second feature we will implement is overlay. The user will be able to type in text to overlay on the video. Finally, we will implement a trace function. This allows the user to draw an overlay object freehand using a mouse.

System Description

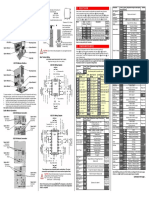

Figure 1 shows a block diagram for the design of our video processor system. Our system has keyboard and mouse inputs inputs, and a video input. The output is a modied video signal. From the block diagram, we see that that several intermediate modules are used to generate nal output. The video stream is rst processed by the video input module. This module interfaces with the video input hardware on the 6.111 labkit and produces horizontal and vertical sync signals, a eld signal, and a 24-bit pixel value encoded in YCrCb format. These outputs are fed to the zoom module. The 6.111 labkit includes sample code for the video input module. We plan to use this code with minimal, if any, modication.

Framegrab Module

The framegrab module takes in the horizontal and vertical sync signals from the input module, along with the frame and pixel signals. The motivation for the frame grab module is that the user could switch to an alternate video stream, load in a frame, and switch back to the original video stream. The stored frame can then be superimposed onto the video stream in dierent ways by the blue screen or overlay modules. The framegrab module will write one frame to the ZBT memory. The control module sends a trigger signal, which is asserted when the frame grab module should store the current frame. By storing a frame in the memory, the overlay module can read this frame, scale it to a smaller size, and superimpose it onto the video stream for a picture-in-picture eect. Also, the blue screen module can superimpose the stored frame into the background. The framegrab module will be responsible for making sure that the frame buer is never accessed simultaneously by the blue screen and overlay modules. To accomplish, this the overlay and blue screen modules send inputs to the framegrab module, and receive the data in the memory from the framegrab module. The address select input from the control module is used to determine whether to allow the blue screen 1

O_ADDRESS O_DATA

20

24

INPUT

H-SYNC V-SYNC FIELD

24

H-SYNC V-SYNC FIELD FRAMEGRAB PIXEL

24

H-SYNC V-SYNC BLUE SCREEN FIELD PIXEL

24

ZOOM

H-SYNC V-SYNC FIELD PIXEL

24

OVERLAY

H-SYNC V-SYNC FIELD PIXEL

24

OUTPUT

PIXEL

B_DATA

24

B_ADDRESS

20

CALIBRATE

ENABLE

TRIGGER ADDRESS_SELECT PS/2 KEY ASCII READY

2 8

ENABLE

20

21

SELECT

4

WE

FSM BUTTONS READY POS

20

DATA

MAG

POS

PS/2 MOUSE

H-SYNC GUI V-SYNC PIXEL

3

VGA OUT

CONTROL

Figure 1: Video Processor Block Diagram

or the overlay module to read the buer. This is not a huge limitation, since it does not really make sense to simultaneously superimpose the frame into the background and display a smaller version of the same frame in a single image.

Blue Screen Module

The blue screen module takes in the horizontal and vertical sync signals, the eld, and the pixel value from the framegrab module. When enable is asserted, this module will replace any blue background pixels with the contents in the frame buer.To calibrate the module so that we can determine what pixel values correspond to blue, the blue screen module takes in a calibrate input from the control module. When calibrate is asserted, the incoming video stream should just be the background. By examining this stream, the module should be able to determine appropriate thresholds to use in order to classify pixels as background or not.

Zoom Module

The zoom module takes in inputs from the control module and the blue screen module. The enable input indicates whether zoom should be used. The 20-bit position input gives the position on screen where we want to zoom in. The 2-bit magnication input tells us how much to enlarge the image around the point given by the position input. The zoom module produces horizontal and vertical sync output signals, a eld signal, and a 24-bit pixel output. The zoom module interacts with a ZBT memory. This is because we need a one frame buer to perform the necessary computation, and the on-chip BRAMs do not have enough memory to store a frame.

Overlay Module

After the zoom module comes the overlay module. This module is responsible for adding any overlay objects the user may have specied. In our design, any overlay objects will be rendered by the control module. The overlay module just needs to read the rendered overlay objects from BRAM modules instantiated within the overlay module. The overlay module takes in the outputs of the zoom module, as well as some signals from the control module. Table 1 describes the interactions with the control module that program the overlay modules BRAMs and registers. First, there is a write-enable input. If write-enable is asserted, the control module needs to write to the BRAM or some associated registers. In this case, a 21-bit data bus is used to tell the overlay module what needs to be written. The 4-bit select signal controls whether the BRAM or a register get written to. The high-order two bits of select are used to select between one of three possbile overlay objects: 2 text objects and the trace object. The low order 2 bits control which information is being written. If the low order bits are 00, we write to the BRAM associated with the right object. If the low order bits are 01, we write to the length register for the object. The length register for text objects stores how many characters of text are in this object. The trace does not need a length register. If the low order bits are 10, the overlay module writes to the position register, which stores the position where text overlay objects should appear on screen. Finally, if the low order bits are 11, the overlay module writes to the register, which indicates whether the object should actually be overlayed or not.

Table 1: Overlay Programming Specication Programming Function Select Bus Value Data Bus Format Text1 Video Buer 0000 Bits 19:0 for address, bit 20 for value Text1 Horizontal Length 0001 Bits 9:0 for value Text1 Position 0010 Bits 19:0 for value Text1 Enable 0011 Bit 20 for value Text2 Video Buer 0100 Bits 19:0 for address, bit 20 for value Text2 Horizontal Length 0101 Bits 9:0 for value Text2 Position 0110 Bits 19:0 for value Text2 Enable 0111 Bit 20 for value Frame Buer Position 1000 Bits 19:0 for value Frame Buer Enable 1011 Bit 20 for value Trace Video Buer 1100 Bits 19:0 for address, bit 20 for value Trace Enable 1111 Bit 20 for value

The overlay module also interacts with the framegrab module. By reading the ZBT frame buer, the overlay module can superimpose a downsampled version of the stored frame onto the video stream. The frame can be superimposed at a variable position supplied by the user. This position is sent to the overlay module by the control module. The control module also uses the enable signal to tell the overlay module if the stored frame should be superimposed ot not. Table 1 details how this works.

Output Module

The overlay module outputs horizontal and vertical sync signals, a eld signal, and a pixel output. This data is sent to the output module. The output module uses these signals to interface with the NTSC decoder on the 6.111 labkit. This produces the nal video image with all modications, which can be sent to a video monitor. We plan to use the code supplied with the 6.111 labkit for the output module, perhaps with minor modications.

Control Module

The control module allows the video processor to interface with a user. It receives keyboard and mouse input from the PS/2 keyboard and mouse submodules and renders a graphical user interface which is output to a VGA display submodule via pixel data, horizontal and vertical sync lines. A concept drawing of the graphical user interface is seen in Figure 2. The control module receives a ready signal from each of the PS/2 modules which indicates that a new piece of user input is ready to be processed. The control module will then read a new key press, mouse location, or mouse click. The combination of the keyboard/mouse input and VGA output allow the user to enter text to be stored for overlay, and then visually place the overlay text on top of the video using the mouse to select a position. This interface also allows the user to freehand draw on top of the video image using the trace functionality. Finally, the user interface will allow the user to control the zoom functionality by selecting a center point and magnication

1024x768

FRAMEGRABBER TRIGGER 525x720 DRAWING/PLACEMENT SURFACE

BLUESCREEN ENABLE CALIBRATE

ZOOM ENABLE 2X 4X 8X CHOOSE CENTER POINT

OVERLAY TEXT1 TEXT2 FRAMEGRAB TRACE ENABLE ENABLE ENABLE ENABLE SET POSITION SET POSITION SET POSITION CLEAR DRAW CLEAR CLEAR ENTER TEXT ENTER TEXT

Figure 2: GUI Concept Drawing

level. The users interactions with the control module are translated to output lines that control the framegrab, blue screen, zoom and overlay submodules. This is accomplished through the use of a nite state machine sub-part within the control module. Three of these lines go to the zoom module an enable line which switches the zoom module in and out of the video path, a position output, which denes the center point of the zoom, and a magnication output which species the magnication level of the zoom. The other three outputs go to the overlay submodule. These outputs are used to write to various video memories that are in the overlay submodule. The write enable line signies that a write should be performed on the next rising clock edge. The select output chooses what memory in the overlay module is being written, and the data bus carries the appropriate data and addressing necessary to carry out the type of write specied by the value of the select output. The use of these outputs is presented in detail in Table 1.

PS/2 Input Modules

The PS/2 keyboard module interfaces with the PS/2 hardware on the 6.111 labkit and has two outputs, an ASCII data output, which carries an 8-bit ASCII representation of a key press. The ready line goes high for one clock cycle after a keypress to indicate that there is a new characater. This module has been released as sample code for the labkit. We intend to use this sample module with minimal, if any, modication. The PS/2 mouse module is similar to the keyboard module. It outputs the mouses current position over a position output, and indicates a transition in the state of any of the buttons on the buttons output. An internal register keeps track of the mouses position on a grid the size of the VGA display.

VGA Output Module

The VGA output module takes as input horizontal and vertical sync as well as a pixel value and interfaces with the Triple DAC hardware on the labkit. This output module is implemented in the lab4 code. We plan to use this implementation with minimal, if any, modication.

Testing

We plan to test the system in several stages. First, we will test out the input and output modules by themselves. When these modules work, we should be able to take in a video input and see it on the video monitor at the output. After verifying this basic performance, we can start testing the processing modules. The overlay module can be tested easily by hardcoding data into the BRAM and registers. The overlay module can be added between the input and output modules, and when the module is working properly we should see overlay objects on top of the video at the output. While the overlay module is being tested, the PS/2 input modules can be tested separately. Using the logic analyzer, we should be able to check that these modules output the correct values. After the PS/2 input modules have been tested, part of the control module can be tested. Specically, we will check that the control module can generate the correct VGA output for a computer monitor. Note that all this testing can be done in parallel with the overlay testing described above, because all the tests so far do not require any interaction between the control module and the processing modules. 6

The next step of testing will be to verify the operation of the zoom module. To start, we will check that the zoom module interface with the ZBT memory is working properly. Then, in the same way we tested the overlay module, we can test the zoom module with a hardcoded position and magnication factor. When the module is working properly, we should see a magnied version of the image on the output video monitor. After the zoom module has been tested, the framebgrab and blue screen modules will be tested. Again, we can hardcode the control signals and check that these modules work. We can shift out the zoom and overlay modules for initial testing of the blue screen module, and then add the overlay module back in to test the picture-in-picture functionality. The last tests we need to perform are to verify that the control module produces the correct programming signals for the zoom and overlay modules. We should be able to check this easily using the Xilinx ISE simulator or the logic analyzer. Then, we can connect all the modules together, and the entire system should work properly.

Division of Labor

The division of labor reects the testing procedure described above. Ben will work on the PS/2 input modules, the control module, the framegrab module, and the VGA output module. Venkat will work on the blue screen, zoom, overlay, and output modules.

Você também pode gostar

- ConsoleswDocumento11 páginasConsoleswMuralidharan NRAinda não há avaliações

- Demo: Real-Time Video Focus Identification and Assessment: Page 1 of 1Documento10 páginasDemo: Real-Time Video Focus Identification and Assessment: Page 1 of 1Ãsïyá ZāfârAinda não há avaliações

- Cognex Designer and ProfinetDocumento4 páginasCognex Designer and ProfinetplpdspAinda não há avaliações

- Project 3Documento16 páginasProject 3gsjhgAinda não há avaliações

- Using Safe Frames: Chapter 2 Seeing It All - Working With The ViewportsDocumento11 páginasUsing Safe Frames: Chapter 2 Seeing It All - Working With The ViewportskeeyanAinda não há avaliações

- Artoolkit 3Documento7 páginasArtoolkit 3KARTHI46Ainda não há avaliações

- VGA Controller PDFDocumento6 páginasVGA Controller PDFAviPatelAinda não há avaliações

- Experiment #2 - Introduction To TI C2000 Microcontroller, Code Composer Studio (CCS) and Matlab Graphic User Interface (GUI)Documento18 páginasExperiment #2 - Introduction To TI C2000 Microcontroller, Code Composer Studio (CCS) and Matlab Graphic User Interface (GUI)lpestanaAinda não há avaliações

- Resumen de LeccionesDocumento158 páginasResumen de LeccionesClaudio GodoyAinda não há avaliações

- Defence University College ofDocumento5 páginasDefence University College ofmelese tsegaAinda não há avaliações

- Immersive Calibration PRO User GuideDocumento93 páginasImmersive Calibration PRO User GuideKarthik ReddyAinda não há avaliações

- Chapter 3Documento11 páginasChapter 3nikhilAinda não há avaliações

- 1 - Introduction To Proteus VSM (Part I) : LAB ObjectivesDocumento16 páginas1 - Introduction To Proteus VSM (Part I) : LAB ObjectivesNirmal Kumar Pandey100% (1)

- Manual of Configuration and Use of Picgoto Controller and Picgoto ServerDocumento12 páginasManual of Configuration and Use of Picgoto Controller and Picgoto Serverpcesar_souza100% (1)

- Home Automation XBEE ModulesDocumento32 páginasHome Automation XBEE ModulesFrancisco NatarenoAinda não há avaliações

- PS - 1.2 - Tutorial (BL) - Orthophoto, DeM (Without GCPS)Documento14 páginasPS - 1.2 - Tutorial (BL) - Orthophoto, DeM (Without GCPS)Dindin WahidinAinda não há avaliações

- Application of LabView Vision and Fuzzy Control For Controling A Gantry CraneDocumento4 páginasApplication of LabView Vision and Fuzzy Control For Controling A Gantry CraneJournalofICTAinda não há avaliações

- Final Exam Multimedia CommunicationsDocumento10 páginasFinal Exam Multimedia CommunicationsArif CupuAinda não há avaliações

- Cyclops 1.3 User's Guide: Changes in Version 1.3 (Mac OSX Only)Documento19 páginasCyclops 1.3 User's Guide: Changes in Version 1.3 (Mac OSX Only)meudicAinda não há avaliações

- Training For HMI V1.0 20150127Documento67 páginasTraining For HMI V1.0 20150127minhtutran1983Ainda não há avaliações

- Infineon-Component - Segment - LCD - (SegLCD) - V3.20-Software Module Datasheets-V03 - 04-ENDocumento35 páginasInfineon-Component - Segment - LCD - (SegLCD) - V3.20-Software Module Datasheets-V03 - 04-ENAlhassan Ahmed OmranAinda não há avaliações

- Simulink TutorialDocumento7 páginasSimulink TutorialAmylegesse01Ainda não há avaliações

- Heidelberg Primesetter: Plug-In ManualDocumento12 páginasHeidelberg Primesetter: Plug-In ManualGRABADOS EXPRESAinda não há avaliações

- 023 - Micronet & GAPDocumento36 páginas023 - Micronet & GAPLindo PatoAinda não há avaliações

- Vitsat-1 Payload Report.: DescriptionDocumento12 páginasVitsat-1 Payload Report.: DescriptionVarun ReddyAinda não há avaliações

- Manual CP600webDocumento24 páginasManual CP600webDaniel JimenezAinda não há avaliações

- NI Tutorial 52139 enDocumento16 páginasNI Tutorial 52139 enJack Eito NeoAinda não há avaliações

- 20 Sim Reference 43Documento1.064 páginas20 Sim Reference 43fercho72169Ainda não há avaliações

- Index: Product Part NumberDocumento27 páginasIndex: Product Part Numberalper sungurAinda não há avaliações

- ReleaseNote en V4.28 PDFDocumento10 páginasReleaseNote en V4.28 PDFQuang VienAinda não há avaliações

- COULOMB Quick Start GuideDocumento128 páginasCOULOMB Quick Start GuideJordan RileyAinda não há avaliações

- Sdh-2 Multi-Finger Gripper and Kuka Robot Animations For Real-Time Simulations of Robot-Hand-Control Strategies Using Open Source Software BlenderDocumento9 páginasSdh-2 Multi-Finger Gripper and Kuka Robot Animations For Real-Time Simulations of Robot-Hand-Control Strategies Using Open Source Software BlenderGkkAinda não há avaliações

- Creating A "Hello World" Application Using The MPLAB Harmony Configurator (MHC)Documento18 páginasCreating A "Hello World" Application Using The MPLAB Harmony Configurator (MHC)PratikAinda não há avaliações

- Codesys Visualization: Supplement To The User Manual For PLC Programming With Codesys 2.3Documento108 páginasCodesys Visualization: Supplement To The User Manual For PLC Programming With Codesys 2.3機車隆Ainda não há avaliações

- 4D Ship Simulator User Guide Rev1.0 (20130225)Documento51 páginas4D Ship Simulator User Guide Rev1.0 (20130225)hacker0206Ainda não há avaliações

- Assignment 2Documento7 páginasAssignment 2مرتضی اللهی دهقیAinda não há avaliações

- 04-BSC6900V900R011 GO Data Configuration ISSUE2.0-20100506-BDocumento61 páginas04-BSC6900V900R011 GO Data Configuration ISSUE2.0-20100506-Bsamiramahdavi100% (1)

- CX-Process Monitor Plus: WS02-LCMC1-EV2Documento7 páginasCX-Process Monitor Plus: WS02-LCMC1-EV2อเวจี ที่รักAinda não há avaliações

- 3.2.2.6 Frame For Rotor Temperature Alarm Value SetupDocumento51 páginas3.2.2.6 Frame For Rotor Temperature Alarm Value SetupClip nhungcaunoihayAinda não há avaliações

- UVCDocumento9 páginasUVCMarco E. MadrigalAinda não há avaliações

- IRace ManualDocumento10 páginasIRace Manualg4emlAinda não há avaliações

- CoDeSys Visu V23 EDocumento106 páginasCoDeSys Visu V23 Enhatanh2610Ainda não há avaliações

- Wa0028.Documento8 páginasWa0028.NaveenAinda não há avaliações

- User Manual XBEEDocumento21 páginasUser Manual XBEEGauravGupta100% (1)

- Color Detection Using FPGA Based Smart CameraDocumento19 páginasColor Detection Using FPGA Based Smart Cameratry199Ainda não há avaliações

- Xy Plotter v2.0 User Guide Mdraw Version 1.0 PDFDocumento38 páginasXy Plotter v2.0 User Guide Mdraw Version 1.0 PDFShubhamKuchhal100% (1)

- FPGA Robot Arm Assistant: Final Project ReportDocumento32 páginasFPGA Robot Arm Assistant: Final Project Reporthassan angularAinda não há avaliações

- Model Tuning in ICS Telecom PDFDocumento20 páginasModel Tuning in ICS Telecom PDFAndi Abdul AzisAinda não há avaliações

- HW Assignment 2Documento11 páginasHW Assignment 2Akshat JhaAinda não há avaliações

- 2080 qr001 - en PDocumento95 páginas2080 qr001 - en PfelltecAinda não há avaliações

- Manhinh KXDocumento49 páginasManhinh KXNguyễn Văn HuânAinda não há avaliações

- g4 Project ReportDocumento60 páginasg4 Project ReportDrake Moses KabbsAinda não há avaliações

- Infineon-Component - Segment - LCD - (SegLCD) - V2.10-Software Module Datasheets-V03 - 04-ENDocumento32 páginasInfineon-Component - Segment - LCD - (SegLCD) - V2.10-Software Module Datasheets-V03 - 04-ENCode-XAinda não há avaliações

- MBED With Nucleo F401REDocumento15 páginasMBED With Nucleo F401REZahidur Ovi RahmanAinda não há avaliações

- RobotStudio 2023-2-1 Release NotesDocumento21 páginasRobotStudio 2023-2-1 Release NotesbekappodatakaalkatelAinda não há avaliações

- Combining ModelSim and Simulink With SystemVision in An Integrated Simulation EnvironmentDocumento5 páginasCombining ModelSim and Simulink With SystemVision in An Integrated Simulation Environmentleo3001Ainda não há avaliações

- System Generator TutorialDocumento33 páginasSystem Generator TutorialAthul KsAinda não há avaliações

- Lect1 - Algorithms and FlowchartDocumento29 páginasLect1 - Algorithms and FlowchartMM Ayehsa Allian Schück67% (6)

- IBM360-Amdahl April64Documento15 páginasIBM360-Amdahl April64THIAGO LIMAAinda não há avaliações

- Eecs 4314 Assignment 2Documento15 páginasEecs 4314 Assignment 2api-723823461Ainda não há avaliações

- Bin 4X: Universal Interface With 4 Configurable Binary Inputs / LED Outputs Zio-Bin4X Technical Documentation FeaturesDocumento2 páginasBin 4X: Universal Interface With 4 Configurable Binary Inputs / LED Outputs Zio-Bin4X Technical Documentation FeaturesДимитър МирчевAinda não há avaliações

- Embedded System Module 1Documento28 páginasEmbedded System Module 1Yatish KAinda não há avaliações

- Esp32-Pico-V3-02 DatasheetDocumento33 páginasEsp32-Pico-V3-02 Datasheetuuu_raduAinda não há avaliações

- Evolution of Operating System I PDFDocumento4 páginasEvolution of Operating System I PDFAngel KaseraAinda não há avaliações

- ICT Syllabus Form 1 - 4Documento46 páginasICT Syllabus Form 1 - 4ALI MWALIMU0% (1)

- Networking With Linux: UPC Telematics DepartmentDocumento35 páginasNetworking With Linux: UPC Telematics DepartmentDiego BardalesAinda não há avaliações

- 6 - Block Architecture and The LAD-STL-FBD EditorDocumento27 páginas6 - Block Architecture and The LAD-STL-FBD EditorMichele BacocchiaAinda não há avaliações

- Label QR Code MUK111312007Documento2 páginasLabel QR Code MUK111312007Klayton MonteverdeAinda não há avaliações

- Tesys Motor Starters - Open Version: PresentationDocumento4 páginasTesys Motor Starters - Open Version: PresentationjoaoAinda não há avaliações

- Conversion Guide Rockwell To Siemens ControllersDocumento4 páginasConversion Guide Rockwell To Siemens ControllersNixiusAinda não há avaliações

- CAESAR II PIPING Tutorial A Pages 120 To 157 From C2APDocumento38 páginasCAESAR II PIPING Tutorial A Pages 120 To 157 From C2APLuis OrtizAinda não há avaliações

- 51 52 25 123 enDocumento2 páginas51 52 25 123 enManuelAinda não há avaliações

- Diagnose CCW09 CPU3425Documento5 páginasDiagnose CCW09 CPU3425Eswin RamosAinda não há avaliações

- Lecture-4 Features of MicroprocessorDocumento21 páginasLecture-4 Features of MicroprocessorMuhammad MusaddiqAinda não há avaliações

- Aggregate Etherchannel Quality of Service PDFDocumento12 páginasAggregate Etherchannel Quality of Service PDFmichaelsilvaAinda não há avaliações

- 07 RTL Optimization TechniquesDocumento20 páginas07 RTL Optimization Techniquesgideontargrave7Ainda não há avaliações

- Year9 Notes On Input Devices Part 1Documento13 páginasYear9 Notes On Input Devices Part 1NagarajAinda não há avaliações

- E-16D/-5D/-2D: Enterprise Environment Monitoring System Installation and Operation ManualDocumento207 páginasE-16D/-5D/-2D: Enterprise Environment Monitoring System Installation and Operation ManualComputer789Ainda não há avaliações

- CSC 203 Week 1-3Documento22 páginasCSC 203 Week 1-3seyiAinda não há avaliações

- Onvert EB Into Obile Apps Platform: Alveetech CO MDocumento18 páginasOnvert EB Into Obile Apps Platform: Alveetech CO Milias ahmedAinda não há avaliações

- Chapter One IntroductionDocumento7 páginasChapter One Introductionyohannes assefaAinda não há avaliações

- Intecont Satus ManualDocumento108 páginasIntecont Satus ManualMiladinm1100% (1)

- Digital Axle CounterDocumento51 páginasDigital Axle CounterUjjwal ChandraAinda não há avaliações

- MSDOS GuideDocumento19 páginasMSDOS Guidemaani.ssssAinda não há avaliações

- TwinCAT QuickStartDocumento11 páginasTwinCAT QuickStartpopipacAinda não há avaliações

- gfk1504k (VersaMax Completo)Documento505 páginasgfk1504k (VersaMax Completo)Elu RuizAinda não há avaliações

- 8255 Programmable Peripheral InterfaceDocumento27 páginas8255 Programmable Peripheral InterfaceumramanAinda não há avaliações

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsNo EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsAinda não há avaliações

- Chip War: The Quest to Dominate the World's Most Critical TechnologyNo EverandChip War: The Quest to Dominate the World's Most Critical TechnologyNota: 4.5 de 5 estrelas4.5/5 (227)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)No EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Nota: 5 de 5 estrelas5/5 (1)

- Chip War: The Fight for the World's Most Critical TechnologyNo EverandChip War: The Fight for the World's Most Critical TechnologyNota: 4.5 de 5 estrelas4.5/5 (82)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XNo EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XNota: 3 de 5 estrelas3/5 (2)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102No EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Nota: 5 de 5 estrelas5/5 (2)

- CompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102No EverandCompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Ainda não há avaliações

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesNo EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesAinda não há avaliações

- Amazon Web Services (AWS) Interview Questions and AnswersNo EverandAmazon Web Services (AWS) Interview Questions and AnswersNota: 4.5 de 5 estrelas4.5/5 (3)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFNo EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFAinda não há avaliações

- Programming with STM32: Getting Started with the Nucleo Board and C/C++No EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Nota: 3.5 de 5 estrelas3.5/5 (3)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxNo EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxAinda não há avaliações

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertNo EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertNota: 3.5 de 5 estrelas3.5/5 (6)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsNo EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsNota: 5 de 5 estrelas5/5 (2)

- Raspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesNo EverandRaspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesAinda não há avaliações

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideNo EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideNota: 1 de 5 estrelas1/5 (1)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002No EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Nota: 5 de 5 estrelas5/5 (1)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]No EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Nota: 5 de 5 estrelas5/5 (2)

- Real-Time UML Workshop for Embedded SystemsNo EverandReal-Time UML Workshop for Embedded SystemsNota: 3.5 de 5 estrelas3.5/5 (2)

- Raspberry Pi for Python Programmers Cookbook - Second EditionNo EverandRaspberry Pi for Python Programmers Cookbook - Second EditionAinda não há avaliações

- How To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsNo EverandHow To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsAinda não há avaliações

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XNo EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XNota: 5 de 5 estrelas5/5 (1)

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714829744?v=1)