Escolar Documentos

Profissional Documentos

Cultura Documentos

Diretivas Sintese Brazil IP 1.0.0

Enviado por

AbelGuilherminoDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Diretivas Sintese Brazil IP 1.0.0

Enviado por

AbelGuilherminoDireitos autorais:

Formatos disponíveis

Tutorial e Diretivas para Captura de Projeto, Validao e Prototipao de Mdulos de Hardware Descritos em SystemC

Projeto Fnix

BRAZIL IP

Verso 1.0.0 | 11/11/03 Alessandro Noriaki Ide, Ney Laert Vilar Calazans, Edson Ifarraguirre Moreno, Taciano Ares Rodolfo, Fernando Gehm Moraes (noriaki, calazans, edson, taciano, moraes@inf.pucrs.br)

Diretivas de Projeto SystemC

Projeto Fnix

Histrico de Alteraes

Data

Verso

Descrio

ltimo RF

ltimo RNF

Autor

11/11/03

1.0.0

Verso inicial do documento

Noriaki, Ney, Edson, Taciano, Moraes

Lista de Aprovadores

Nome Funo

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 2/49

Diretivas de Projeto SystemC

Projeto Fnix

Contedo

1. 2.

Introduo..............................................................................................................................4 Estudo de Caso - Controlador Serial Protocolo RS232 ..............................................................4 2.1 2.2 2.3 2.4 2.5 2.6 Formato de pacotes RS232 para a presente implementao................................................4 Estrutura geral da implementao....................................................................................5 Implementao em VHDL...............................................................................................6 Implementao em SystemC RTL....................................................................................7 Limites de operao do mdulo........................................................................................8 Estrutura de hardware para prototipao...........................................................................8 Tipos de dados sintetizveis .............................................................................................9

3.

Codificao para Sntese em SystemC......................................................................................9 3.1 3.2 Estilos de codificao....................................................................................................10 3.2.1 Codificao de processos em SystemC ....................................................................10 3.2.2 Codificao para inferncia de flip-flops, latches e registradores ...............................11 3.2.3 Codificao para inferncia de memria compartilhada ............................................12 3.2.4 Problemas utilizando a verso 2002.06 do CoCentric SystemC Compiler ..................15

4.

Tcnicas de Prototipao em FPGA .......................................................................................16 4.1 Traduo SystemC VHDL / Verilog ..........................................................................17 4.1.1 SystemC VHDL / Verilog independente da tecnologia de implementao.............17 4.1.2 SystemC VHDL / Verilog / EDIF usando bibliotecas de tecnologia ......................18 4.2 Snteses lgica e fsica...................................................................................................18 4.2.1 Fluxo HDL............................................................................................................19 4.2.2 Fluxo SystemC ......................................................................................................23 4.3 Ambientes para validao do prottipo em hardware.......................................................26 4.3.1 Software para comunicao entre o controlador de comunicao e o hospedeiro ........26

5.

Tcnicas de Validao Funcional...........................................................................................27 5.1 SystemC isoladamente...................................................................................................27 5.1.1 Visualizao do VCD.............................................................................................27 5.2 Simulao funcional com comparao de onda geradas em HDL e SystemC.....................29 5.2.1 Comparao de formas de onda: HDL versus SystemC traduzido para HDL..............29

6.

Referncias ..........................................................................................................................31

Anexo I - Verso VHDL do Controlador Serial RS-232..................................................................33 Anexo II - Verso SystemC do Controlador Serial RS-232 .............................................................37 Anexo III - Mdulos Adicionais para Prototipao em Hardware....................................................42 Anexo IV - Cdigo SystemC de Mdulos Adicionais para Simulao .............................................44

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 3/49

Diretivas de Projeto SystemC

Projeto Fnix

1. Introduo

O objetivo deste documento servir como guia de treinamento para a modelagem, a validao e a prototipao de mdulos de hardware a p artir de descries elaboradas mediante uso da linguagem SystemC. SystemC definida hoje como uma biblioteca de classes voltada para a modelagem de hardware, construda sobre a linguagem C/C++. Utiliza-se aqui a verso 2.0.1 da biblioteca de classes SystemC [1], conforme disponvel no stio da Open SystemC Initiative (OSCI). O documento baseado em um estudo de caso simples, uma interface de comunicao serial, baseada no padro RS232, descrito na Seo 2. SystemC pode ser usada para a modelagem de hardware em diversos nveis de abstrao. No presente j possvel empregar descries SystemC como descrio de entrada para fluxos automatizados de gerao de hardware, desde que restrinja -se as construes de SystemC empregadas a um subconjunto dito sintetizvel. Este subconjunto denominado aqui de SystemC no nvel de transferncia entre registradores ou SystemC RTL (do ingls, Register Transfer Level). A ferramenta principal para processar SystemC RTL usada neste documento o CoCentric SystemC Compiler da empresa Synopsys, que permite realizar a sntese lgica de SystemC RTL para formatos EDIF ou HDL, ou apenas traduzir SystemC RTL para cdigo HDL RTL (nas linguagens Verilog ou VHDL). Alguns critrios para codificao de estruturas de hardware RTL so apresentados e discutidos na Seo 3. Como algumas das tcnicas de produzir hardware a partir de SystemC propostas aqui envolvem a passagem por cdigo HDL intermedirio, alm do CoCentric SystemC Compiler emprega-se tambm ferramentas de sntese lgica como Leonardo Spectrum da Mentor Graphics e/ou XST da Xilinx. Para a prototipao de hardware a partir de cdigo SystemC RTL cita-se aqui o uso do ambiente ISE da Xilinx. O uso destas e outras ferramentas para produzir descries fsicas de hardware passveis de configurao em dispositivos de plataformas de prototipao baseadas em FPGAs Xilinx o assunto tratado na Seo 4. As tcnicas de prototipao cujo uso descrito na Seo 4 pressupe descries corretas. Para validar descries SystemC RTL antes da prototipao, tcnicas de validao funcional devem ser empregadas. Este o tema da Seo 5. Todo o trabalho descrito aqui diretamente utilizvel de forma tutorial. Para tanto, anexos ao final do texto provem o cdigo fonte de todos os arquivos necessrios para executar cada um dos fluxos de projeto, validao e prototipao discutidos aqui. Embora descreva-se aqui implementaes validadas em duas plataformas de prototipao especficas, a quantidade de trabalho para portar o material dos anexos para outras plataformas mnima, desde que a mesma possua uma interface serial que possa ser usada para conexo a um computador hospedeiro.

2. Estudo de Caso - Controlador Serial Protocolo RS232

Como estudo de caso neste documento utiliza-se um controlador de comunicao serial cujo protocolo compatvel com o padro RS232. Trata-se de uma implementao mnima, pois o padro RS232 possui uma srie de parmetros de implementao opcional ou varivel, tais como a funcionalidade dos sinais CD, DSR, CTS, RTS, RI e DTR, o bit de paridade e a durao do STOPBIT [8].

2.1

Formato de pacotes RS232 para a presente implementao

Em primeiro lugar, apenas os sinais fundamentais transmisso so usados, quais sejam TXD e RXD, so usados aqui. Pacotes transmitidos no padro RS232 so de formato fixo e possuem exatamente 10 ou 11 bits. O formato geral de um pacote ilustrado na Figura 1. O estado de repouso de uma linha serial consiste em um valor lgico fixo 1. A transmisso inicia -se quando h uma transio deste estado de repouso para um valor lgico 0. Este valor o primeiro dos bits transmitido, e denominaDiretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 4/49

Diretivas de Projeto SystemC

Projeto Fnix

se STARTBIT. Seguem-se 8 bits, que constituem a parte til do pacote. Uma observao de grande importncia notar que os 8 bits de um byte so enviados a partir do bit menos significativo. Por exemplo, supor que se queira enviar o valor 96 em hexadecimal (doravante representado usando o prefixo H, 96H) pela serial. Isto corresponde a 10010110 em binrio. A seqncia enviada pela serial invertida em relao representao original, ou s eja, 01101001. O dcimo bit enviado numa comunicao serial pode ser o bit de PARIDADE. Este bit opcional e pode empregar paridade par ou paridade mpar A presente implementao no utiliza este bit, transmitindo pacotes de 10 bits. Por fim, segue o STOPBIT, que indica o fim da transmisso, e sempre um valor lgico 1 com durao de 1, 1,5 ou 2 bits. Aps o STOPBIT, a transmisso de um novo pacote pode ocorrer, ou a linha pode permanecer um tempo arbitrrio em repouso. Todos os bits do pacote, com a possvel exceo do STOPBIT, possuem tempo de durao idntico. O inverso do tempo de transmisso de um bit em segundos define a taxa de transmisso, tambm chamada de baud rate, em bits por segundo ou bps.

Figura 1 - Estrutura de um pacote transmitido usando o protocolo serial RS232. Antes do STARTBIT e aps o STOPBIT linha est em repouso (1 lgico). O STOPBIT pode ter sua durao de transmisso estabelecida como sendo a durao de 1, 1,5 ou 2 bits.

2.2

Estrutura geral da impleme ntao

A partir da especificao da Seo 2.1, implementou-se um mdulo de hardware, denominado controlador de comunicao serial, ou simplesmente serial, para prover comunicao entre um dispositivo externo, denominado hospedeiro, e outros mdulos internos a um circuito integrado (CI) dedicado que conter tambm o mdulo serial. A Figura 2 ilustra a interface externa do mdulo implementado e o contexto tpico de sua utilizao. Os mdulos do CI em acrscimo ao mdulo serial so coletivamente denominados hardware do usurio .

clock reset

TX_DATA TXD TRANSMISSO TX_AV

HOSPEDEIRO

(COMPUTADOR) RX_DATA RXD RECEPO RX_START TX_BUSY

HARDWARE DO USURIO

Figura 2 - Exemplo de contexto de utilizao tpico para o controlador de comunicao serial. O CI tipicamente um dispositivo reconfigurvel do tipo FPGA em uma plataforma de prototipao de hardware. O hospedeiro tipicamente um computador que se conecta via um cabo serial

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 5/49

Diretivas de Projeto SystemC

Projeto Fnix

plataforma de prototipao. Foi tambm desenvolvido no contexto deste trabalho um software que permite estabelecer a comunicao entre o hospedeiro e o mdulo serial. Este software est livremente disponvel e pode ser obtido a partir da Internet em http://www.inf.pucrs.br/~gaph/. Todos os sinais de interface do mdulo serial so fios simples, exceo de TX_DATA e RX_DATA, que so barramentos de 8 bits. Todos os sinais de controle so ativos no valor 1 lgico, exceto o sinal reset, que ativo em 0. O mdulo serial dividido em dois mdulos: controle de transmisso e controle de recepo. O controle de transmisso responsvel por receber os dados provenientes do hospedeiro pela porta de entrada TXD, montar o byte de carga til do pacote e envi lo ao hardware do usurio atravs da porta de sada TX_DATA, notificando ao mesmo a existncia de um dado disponvel atravs do sinal TX_AV. O mdulo de recepo responsvel por receber os dados provenientes do hardware do usurio atravs da porta de entrada RX_DATA, serializ-los e envi-los ao hospedeiro atravs da porta de sada RXD. Atravs de RX_START notificado serial que se deseja enviar um dado ao hospedeiro, enquanto atravs de RX_BUSY recebida a notificao que o dado est sendo enviado ao mesmo. reset e clock possuem as funes cl ssicas em circuitos sncronos.

2.3

Implementao em VHDL

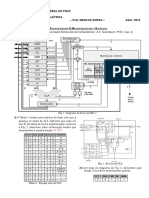

A Figura 3 ilustra a implementao do mdulo serial em VHDL. Os dois mdulos conceituais, transmisso e recepo, foram descritos em VHDL com cinco processos: Autobaud, Clockgenerate, ShiftReg, Data_TX e Data_RX. Estes processos se comunicam atravs do compartilhamento de sinais conforme pode ser observado na Figura 3.

TXD clock reset

8

autobaud

ck_cycles

14

TX_DATA

transmisso

TX_AV

ck_cycles 14

resync 10 regin

regDeslocamento

geraclock

serial_clk 8

RX_DATA

recepo

RXD

RX_START RX_BUSY

Figura 3 Diagrama de blocos da implementao VHDL do mdulo serial. O processo Autobaud responsvel pela sincronizao da comunicao entre o mdulo serial e o hospedeiro, tornando desnecessria a configurao manual da taxa de transmisso (baud rate). Este processo uma mquina de estados finita de 5 estados, cujo grafo de transio de estados encontra-se descrito na Figura 4. Est mquina apenas usada no incio da operao do mdulo serial, ou aps cada reinicializao da serial via reset. Sua funcionalidade consiste em encontrar a relao entre as freqncias de operao do clock do mdulo serial e de transmisso de dados escolhida pelo hospedeiro. Pressupe-se assim que o primeiro dado enviado pelo hospedeiro sempre um padro de 0s e 1s alternados, obrigatoriamente o valor 55H, ou seja, 01010101 em binrio. Assim o primeiro

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 6/49

Diretivas de Projeto SystemC

Projeto Fnix

pacote composto pela seqncia de 10 bits 0101010101, onde o primeiro o STARTBIT, o ltimo o STOPBIT e os demais so 55H A partir deste padro, o processo Autobaud conta quantos perodos do sinal clock nos 4 primeiros bits 0 do pacote inicial (o STARTBIT e os trs primeiros 0s de 55H) e grava este total no sinal ctr0. O que se deseja obter o nmero total de ciclos de clock que cabem em um semi-perodo de relgio de transmisso serial, valor usado para estabelecer a taxa de comunicao do mdulo serial. Para tanto o mdulo Autobaud termina seu processamento em um estado que gera o valor ctr0 dividido por 8, valor armazenado e informado atravs do sinal ck_cycles. O processo Clockgenerate produz o sinal serial_clk , que comanda a FSM de recepo dos dados enviados pelo hospedeiro ao controlador serial, bem como a FSM de transmisso de dados do controlador serial ao hospedeiro. Para isso, a cada borda de descida de clock, um contador interno incrementado at o valor total contido no sinal ck_cycles. O sinal serial_clk gerado assim pela diviso de clock por serial_clk . De tempos em tempos interessante ressincronizar sinal serial_clk , para corrigir eventuais diferenas cumulativas de desvios de perodo causados pela diviso inteira. Isto feito atravs do sinal resync, gerado externamente a este processo.

reset=0 TXD=0 / ctr0<=0 TXD=1 / bit_cnt++

S1

TXD=0 TXD=1

S2

ctr0++ bit_cnt != 0 & TXD=0

S3

TXD=1

TXD=0

bit_cnt = 0 & TXD=0

S6

ck_cycles<=ctr0 div 8 TXD=1

S4

Figura 4 Mquina de estados do processo Autobaud. bit_cnt um contador de 2 bits. O processo Shift_Reg simplesmente um registrador de deslocamento que monta os dados vindos do computador, atravs do sinal TXD, no sinal regin a cada borda de subida do sinal serial_clk. Este processo tambm afetado pela ressincronizao. O processo Data_TX responsvel por gerar a ressincronizao, bem como pela deteco do STARTBIT dos pacotes provenientes da porta de entrada TXD, e pelo envio dos dados contidos em regin para a porta de sada TX_DATA aps a deteco do STOPBIT e pela notif icao de dado disponvel atravs da porta de sada TX_AV. O processo Data_RX responsvel pela montagem do pacote a ser enviado pela porta de sada RXD. Um registrador de deslocamento recebe os dados provenientes da porta de entrada RX_DATA e aps acrescer a estes STARTBIT e STOPBIT armazena-os no sinal word. Pela porta TX_BUSY notifica-se que um dado est sendo transmitido atravs de RXD. No necessrio processo para enviar dados serialmente para a porta de sada RXD. Isto feito utilizando uma lgic a combinacional que envia a posio 0 do sinal word porta RXD. A codificao completa dos processos descritos acima em VHDL encontra-se no Apndice I.

2.4

Implementao em SystemC RTL

Os dois mdulos Data_TX e Data_RX representados na Figura 2, foram descritos em SystemC RTL a partir da descrio em VHDL. Alm dos processos Autobaud, Clockgenerate , Shift_Reg, Data_TX e Data_RX, foi necessrio acrescentar o processo Update_RXD para enviar o bit da posio 0 do sinal word porta de sada RXD, como ilustrado no diagrama de blocos da Figura 5. Isto ocorreu porque em SystemC no possvel implementar lgica combinacional fora de processos. As duas descries do controlador de comunicao serial, em VHDL e em SystemC RTL, diferem apenas no fato de que necessrio respeitar as regras de sintaxe e de semntica de SystemC.

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 7/49

Diretivas de Projeto SystemC

Projeto Fnix

TXD clock reset

8

autobaud

ck_cycles

14

TX_DATA

transmisso

TX_AV

ck_cycles 14

resync 10 regin

regDeslocamento

geraclock

serial_clk 8

RX_DATA

recepo

RXD update_rxd

word [0]

RX_START RX_BUSY

Figura 5 - Processo Update_RXD adicionado ao diagrama de blocos da serial para permitir a implementao desta em SystemC.

2.5

Limites de operao do mdulo

A documentao disponvel sobre o padro de transmisso serial RS232 estabelece com o taxa de transmisso mxima um baud rate de 115.200bps [8]. Contudo, nenhum limite inferior descrito nesta ou em outra referncia disponvel. Para o mdulo discutido neste documento, entretanto, existe uma freqncia mnima de operao. Esta determinada pela dimenso do registrador usado para contar o nmero de ciclos do relgio principal do mdulo que cabem em um perodo de transmisso de 1 bit pelo ou para o mdulo serial. Este registrador, identificado pelo sinal ctr0 da implementao de 17 bits. Assim pode-se calcular que o baud rate mnimo de transmisso de dados de ou para o mdulo dado pela seguinte equao: baud rate mnimo = clock utilizado pelo mdulo / 131072. O nmero 131072 corresponde ao valor de contagem mximo do sinal ctr0, responsvel por contar quantos pulsos do clock ocorrem em um nico pulso do sinal TXD. Na Seo 8 discute-se a implementao do mdulo serial, mencionado duas implementaes, uma usando relgio de 25MHz e outra usando relgio de 24MHz. Para estas freqncias de operao, os baud rates correspondentes so os seguintes: baud rate mnimo a 25MHz = 25.000.000 / 131072 190 bps. baud rate mnimo a 24MHz = 24.000.000 / 131072 184 bps. A taxa mxima obviamente no problemtica de se obter com estas freqncias de operao. A diviso da freqncia de relgio pelas taxas de transmisso padro usadas (e. g. 2400bps, 9600bps, 57600bps e 115200bps) normalmente no gera valores inteiros. Por questes de eficincia, o processo de diviso destes valores no hardware trabalha com valores estritamente inteiros. O erro resultante corrigido pelo uso do processo de ressincronizao, executado a cada dado transmitido.

2.6

Estrutura de hardware para prototipao

Para efetuar a prototipao do controlador, encapsulou-se o mesmo em um hardware que efetua uma conexo em lao. Neste, as portas de sada TX_DATA e TX_AV so conectadas s portas de entrada

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 8/49

Diretivas de Projeto SystemC

Projeto Fnix

RX_DATA e RX_START respectivamente, como observvel na Figura 6. Desta forma, todos os dados enviados pelo computador pela porta de entrada TXD devero retornar inalterados pela porta de sada RXD. O sinal rx_busy ignorado nesta montagem de teste, pois a temporizao de transmisso ser sempre trivialmente respeitada, visto que pacotes consecutivos sero enviados do hardware do usurio para o hospedeiro com atrasos longos, correspondentes ao tempo de espera pela recepo serial dos dados. O cdigo fonte VHDL do arquivo que descreve este hardware encontra-se no Anexo III.

top.vhd

TX_DATA TXD TRANSMISSO

TX_AV

serialinterface.vhd

HOSPEDEIRO

(COMPUTADOR) RXD RECEPO

RX_START

RX_DATA

Figura 6 Diagrama de blocos do hardware usado para testar a implementao da serial.

3. Codificao para Sntese em SystemC

O objetivo desta Seo introduzir de maneira informal e discutir algumas diretivas de codificao para SystemC no nvel RTL, visando obter descries passveis de sntese automatizada. Como dito antes, o presente documento tem natureza tutorial. Existem referncias mais amplas e completas objetivando a gerao de SystemC RTL sintetizvel tal como o guia para a gerao de SystemC RTL sintetizvel da Synopsys [2] e o guia de modelagem RTL da ferramenta CoCentric SystemC Compiler, igualmente da empresa Synopsys [3]. As diretivas mencionadas aqui, junto com estes documentos prov um conjunto de recursos vasto para habilitar a captura de projeto de mdulos de hardware sintetizveis em SystemC. Os resultados experimentais e indicaes de uso de construes e tcnicas de projeto especficas citados neste documento no esto discutidos na referncias [2] e [3], pois so fruto do trabalho prtico dos autores no assunto, e constituem uma contribuio adicional em relao aos manuais. Outra referncia que contm informaes sobre estilos de codificao para sntese o livro de Thorsten e outros [4]. Um trabalho paralelo, empreendido para a familiarizao e avaliao d tcnicas de codificao e e sntese de hardware a partir de SystemC pode ser encontrado em [5]. Neste artigo, descreve-se um estudo de caso de implementao de hardware usando SystemC, resultados de comparao da velocidade de simulao e quantidade de rea ocupada quando partindo de descries em VHDL e/ou SystemC. As Sees a seguir apresentam algumas diretivas de codificao SystemC RTL referentes ao tipo de dados sintetizveis, na Seo 3.1. A seguir, discute-se alguns estilos de codificao para obter bons resultados de sntese, na Seo 3.2. Os documentos [2] e [3] expem tipos de dados sintetizveis bsicos, assim como algumas prticas interessantes de codificao. Este material foi utilizado como base para a descrio dos projetos usados abaixo como exemplos.

3.1

Tipos de dados sintetizveis

Existe um subconjunto de SystemC definido como um padro de facto para viabilizar a sntese automtica de hardware. O documento que define este subconjunto a referncia [2]. No Captulo 3 desta encontra-se a lista de construes no sintetizveis junto com diretivas de correo de cdigo

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 9/49

Diretivas de Projeto SystemC

Projeto Fnix

contendo estas para torn-los sintetizveis. No mesmo Captulo, h a lista completa de tipos de dados sintetizveis. Emprega-se aqui uma boa parte dos tipos sintetizveis em exemplos. Por exemplo, recomenda-se em [2] o uso do tipo C++ nativo bool para modelar valores e sinais transportando exatamente um (1) bit de informao. O tipo sc_bit suportado mas no recomendado. O Tipo sc_logic serve para modelar 1 fio que suporta quatros estados (0, 1, X e Z), o que permite modelar conflitos de valores e fios em estado de alta impedncia, um subconjunto dos estados suportados pelos tipos std_logic e std_logic_vector em VHDL. Os tipos sc_bv e sc_lv modelam vetores de comprimento arbitrrio de sc_bit e sc_logic , respectivamente. O tipo sc_uint deve usado sempre que possvel no lugar de sc_bv. Outros tipos C++/SystemC suportados [2] servem para modelar representaes sintetizveis de: nmeros naturais de preciso fixa; nmeros inteiros de preciso fixa; caracteres; tipos enumerados, para uso, por exemplo em codificao simblica de estados em mquinas de estados finitas; agregados de tipos sintetizve is.

Alm do subconjunto de construes e dos tipos sintetizveis, a referncia [2] define o conjunto de operadores a usar com estes para produzir cdigo sintetizvel.

3.2

Estilos de codificao

H alguns pontos bsic os importantes que podem ser levados em conta para a descrio de hardware mais complexo em SystemC. Talvez um dos principais aspectos de hardware complexo seja a correta modelagem do comportamento seqencial. Para tanto se discute abaixo a descrio de processos sensveis ao nvel e borda de sinais de controle como relgio (clock) e inicializao (reset). Segue-se a discusso da codificao eficiente de registradores codificao de latches e como evitar estes, bem como a discusso de conceitos relacionados inferncia automtica de blocos de memria por ferramentas de sntese que aceitem como entrada SystemC. 3.2.1 Codificao de processos em SystemC

Processos que modelem hardware em SystemC so tipicamente implementados usando a construo SC_METHOD. Um processo criado com SC_METHOD reage a um conjunto de sinais, que compe a sua lista de sensitividade. Pode-se declarar sensibilidade ao nvel de sinais, usando a funo sensitive() ou borda de sinais de controle, usando sensitive_pos() ou sensitive_neg(). Construes usando o formato stream de C++ so alternativas para declarar a sensitividade de um processo (eg: sensitive_pos << clock << reset;). No vivel contudo, declarar sensitividade simultnea ao nvel e borda de sinais em um mesmo processo. Notese que VHDL por exemplo, permite este tipo de definio de sensitividade mista. Processos sensveis ao nvel so aconselhados para modelar lgica combinacional [2]. A lista de sensitividade neste caso deve conter exatamente todas as entradas do mdulo combinacional modelado. O processo avaliado cada vez que ocorrer uma mudana no valor lgico de pelo menos um dos sinais da lista de sensitividade. Sempre que uma das variveis declaradas na lista de sensitividade sofre alterao, o processo avaliado. Os tipos usados na lista de sensitividade podem ser quaisquer dos tipos sintetizveis mencionados na Seo 3.1. Processos sensveis borda so avaliados sempre que um elemento da sua lista de sensitividade troca de valor no sentido da declarao da sensitividade para aquele sinal. Processos sensveis borda de sinais esto relacionados seja a bordas positivas ( sensitive_pos) e/ou negativas (sensitive_neg). O nico tipo usado em listas de sensitividade destes processos o tipo sc_in<bool>.

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 10/49

Diretivas de Projeto SystemC

Projeto Fnix

3.2.2

Codificao para inferncia de flip-flops, latches e registradores

A codificao de registradores e latches tem relao com a forma como a lista de sensitividade de um processo definida. Processos sensveis borda le vam inferncia de registradores durante a sntese lgica automatizada. J processos sensveis ao nvel levam inferncia de latches. Na Figura 7 apresentada a codificao de um registrador e a Figura 8 apresenta o relatrio gerado aps a sntese lgica desta descrio.

#ifndef _reg_h #define _reg_h #include <systemc.h> SC_MODULE(reg) { sc_in< bool > clock, reset; sc_in< sc_uint<16> > D; sc_out< sc_uint<16> > Q; void mainProcess(); SC_CTOR(reg) { SC_METHOD(mainProcess); sensitive_pos << reset; sensitive_neg << clock; } }; #endif if (reset.read()) Q = 0; else Q = D; } #include "reg.h" void reg::mainProcess() {

Figura 7 Codificao de um registrador em SystemC. Processo sensvel borda positiva do reset e borda negativa do clock. Observa-se na Figura 7 que a lista de sensitividade do processo mainProcess foi definida para ser executada na borda de subida (sensitive_pos) do reset e na borda de descida(sensitive_neg) do clock. Este processo somente ser executado quando uma das duas condies for atendida e ambas foram resolvidas no processo.

Inferred memory devices in process in routine reg__17 line 13 in file '/home3/gaph/emoreno/temp/teste/registrador/ff/scc_cache/reg.v'. =============================================================================== | Register Name | Type | Width | Bus | MB | AR | AS | SR | SS | ST | =============================================================================== | Q_reg | Flip-flop | 16 | Y | N | Y | N | N | N | N | ===============================================================================

Figura 8 Resultado da sntese lgica do registrador. A Figura 8 mostra o resultado obtido pela sntese lgica. Foi utilizado o CoCentric SystemC Compiler como ferramenta de converso de SystemC RTL para o formato interno do CoCentric Design Compiler. Este ltimo foi utilizado como ferramenta de sntese lgica. O resultado um componente do tipo flip-flop com reset assncrono (campo AR do relatrio). A codificao de um latch pode ser feita definindo um processo sensvel ao nvel. A diferena bsica est em definir o processo como sensvel aos sinais clock, reset e D, conforme a Figura 9 e no atender a todas as possibilidades de sensitividade. Por exemplo, na Figura 9 h 2 possibilidades para o reset, 2 para o clock e 216 possibilidades para D disparar o processo. O mesmo processo de sntese foi realizado para esta descrio, ou seja, CoCentric SystemC Compiler usado como ferramenta de gerao de arquivo de formato interno, seguido do CoCentric Design Compiler, usado como ferramenta de sntese lgica. O resultado parcial pode ser visto na Figura 10, confirmando a inferncia de latch.

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 11/49

Diretivas de Projeto SystemC

Projeto Fnix

#ifndef _reg_h #define _reg_h #include <systemc.h> SC_MODULE(reg) { sc_in< bool > clock, reset; sc_in< sc_uint<16> > D; } sc_out< sc_uint<16> > Q; void mainProcess(); SC_CTOR(reg) { SC_METHOD(mainProcess); sensitive << reset << clock << D; } }; #endif if (reset.read()) Q.write(0); else if (!clock.read()) Q.write(D.read()); #include "reg.h" void reg::mainProcess() {

Figura 9 Codificao de latch em SystemC. Processo sensvel ao nvel de reset, clock e D.

Inferred memory devices in process in routine reg__17 line 11 in file '/home3/gaph/emoreno/temp/teste/registrador/latch/scc_cache/reg.v'. =========================================================================== | Register Name | Type | Width | Bus | MB | AR | AS | SR | SS | ST | =========================================================================== | Q_reg | Latch | 16 | Y | N | N | N | - | - | - | ===========================================================================

Figura 10 - Resultado da sntese lgica do latch. 3.2.3 Codificao para inferncia de memria compartilhada

Um ponto comum na grande maioria dos projetos de hardware complexo o emprego de grandes blocos de memria compartilhada entre processos de um mesmo mdulo. Abaixo apresenta-se um mdulo simples que descreve dois processos, uma para leitura e um para escrita de uma estrutura de memria compartilhada. No primeiro caso, descreve-se esta memria utilizando o canal primitivo sc_signal, conforme mostrado na Figura 11. A construo sc_signal, permite a diferentes mdulos (declarados usando a construo SystemC SC_MODULE) se comunicar. Isto anlogo comunicao entre processos em VHDL, habilitada pelo uso da declarao signal daquela linguagem.

#ifndef _mem #define _mem #include "systemc.h" SC_MODULE(mem){ sc_in<bool> clock,ce,rw; sc_in<sc_lv<16> > dataIn; sc_in<sc_lv<3> > addIn; sc_out<sc_lv<16> > dataOut; sc_signal<sc_lv<16> > memio[8]; void readMem(); void writeMem(); SC_CTOR(mem){ SC_METHOD(readMem); sensitive << clock << ce; sensitive << rw; #include "mem.h" void mem::readMem(){ if((clock.read()) && (ce.read()) && ( !rw.read())){ memio[addIn.read().to_uint()].write(dataIn.read()); } } void mem::writeMem(){ if((clock.read()) && (ce.read()) && (rw.read())){ dataOut.write(memio[addIn.read().to_uint()].read()); } }

Figura 11 Descrio de um mdulo com memria compartilhada utilizando sc_signal. O resultado da traduo da descrio SystemC RTL do mdulo da Figura 11 pode ser visto nas figuras a seguir. A Figura 12, a Figura 13 e a Figura 14 apresentam a traduo para VHDL.

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 12/49

Diretivas de Projeto SystemC

Projeto Fnix

LIBRARY IEEE, SYNOPSYS; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_MISC.ALL; USE SYNOPSYS.ATTRIBUTES.ALL;

entity mem is port( clock: in STD_LOGIC; ce: in STD_LOGIC; rw: in STD_LOGIC; dataIn: in UNSIGNED (15 DOWNTO 0); addIn: in UNSIGNED (2 DOWNTO 0); dataOut: out UNSIGNED (15 DOWNTO 0)); end mem; architecture mem of type VHDL_TYPE_1 is type VHDL_TYPE_2 is signal memio_7: signal memio_6: signal memio_5: signal memio_4: signal memio_3: signal me mio_2: signal memio_1: signal memio_0: begin mem is array (0 array (0 UNSIGNED UNSIGNED UNSIGNED UNSIGNED UNSIGNED UNSIGNED UNSIGNED UNSIGNED

to 7) of UNSIGNED (15 DOWNTO 0); to 7) of UNSIGNED (15 DOWNTO 0); (15 DOWNTO 0); (15 DOWNTO 0); (15 DOWNTO 0); (15 DOWNTO 0); (15 DOWNTO 0); (15 DOWNTO 0); (15 DOWNTO 0); (15 DOWNTO 0);

Figura 12 Entidade e arquitetura resultantes da traduo do mdulo mem para VHDL. A utilizao de sc_signal para definir uma memria compartilhada um problema para o CoCentric SystemC Compiler na verso usada, 2002.11. O resultado da traduo a criao de n sinais onde n igual ao tamanho da memria, neste caso 8, como pode ser observado na Figura 12. O problema no ocorre se a dimenso do vetor unitria.

readMem : process (clock, ce, rw, memio_0, memio_1, memio_2, memio_3, memio_4, memio_5, memio_6, memio_7) variable memio_next: VHDL_TYPE_1; begin memio_next(7) := memio_7; memio_next(6) := memio_6; memio_next(5) := memio_5; memio_next(4) := memio_4; memio_next(3) := memio_3; memio_next(2) := memio_2; memio_next(1) := memio_1; memio_next(0) := memio_0; if (clock /= '0' and ce /= '0' and rw = '0') then memio_next(CONV_INTEGER(addIn)) := dataIn; end if; memio_0 <= memio_next(0); memio_1 <= memio_next(1); memio_2 <= memio_next(2); memio_3 <= memio_next(3); memio_4 <= memio_next(4); memio_5 <= memio_next(5); memio_6 <= memio_next(6); memio_7 <= memio_next(7); end process;

Figura 13 Processo de leitura do mdulo mem traduzido para VHDL. O tradutor CoCentric SystemC Compiler cria internamente para cada processo uma varivel local com o tamanho de toda a memria. Inicialmente, a memria carregada com os sinais correspondentes cada posio. A partir da condio de leitura, conforme Figura 13, uma das posies da varivel local alterada e finalmente a varivel descarregada nos sinais.

writeMem : process (clock, ce, rw, memio_0, memio_1, memio_2, memio_3, memio_4, memio_5, memio_6, memio_7) variable memio_curr: VHDL_TYPE_2; begin memio_curr(7) := memio_7; memio_curr(6) := memio_6; memio_curr(5) := memio_5; memio_curr(4) := memio_4; memio_curr(3) := memio_3; memio_curr(2) := memio_2; memio_curr(1) := memio_1; memio_curr(0) := memio_0; if (clock /= '0' and ce /= '0' and rw /= '0') then dataOut <= memio_curr(CONV_INTEGER(addIn)); end if; end process;

Figura 14 - Processo de escrita do mdulo mem traduzido para VHDL. Assim como no processo de leitura, o processo de escrita carrega o contedo em uma varivel local e no final este ser descarregado na porta dataOut, conforme Figura 14. Esta traduo no otimizada, pois cria muito espao intermedirio de armazenamento. Inicialmente, foi descrita em SystemC apenas

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 13/49

Diretivas de Projeto SystemC

Projeto Fnix

uma memria de 8 posies, mas o resultado foi a gerao de 8 sinais e duas memrias locais de 8 posies, o que resulta em uma rea 3 vezes maior que a original. O mesmo processo de traduo foi repetido, mas desta vez selecionando como HDL de sada Verilog. O resultado foi o mesmo. O segundo estudo de caso foi definido utilizando uma memria compartilhada no mais empregando sc_signal, mas apenas o tipo sintetizvel, conforme Figura 15.

#ifndef _mem #define _mem #include "systemc.h" SC_MODULE(mem){ sc_in<bool> clock,ce,rw; sc_in<sc_lv<16> > dataIn; sc_in<sc_lv<3> > addIn; sc_out<sc_lv<16> > dataOut; sc_lv<16> memio[8]; void readMem(); void writeMem(); SC_CTOR(mem){ SC_METHOD(readMem); sensitive << clock << ce; sensitive << rw; #include "mem.h" void mem::readMem(){ if((clock.read()) && (ce.read()) && (!rw.read())){ memio[addIn.read().to_uint()]=dataIn.read(); } } void mem::writeMem(){ if((clock.read()) && (ce.read()) && (rw.read())){ dataOut.write(memio[addIn.read().to_uint()]); } }

Figura 15 - Descrio de um mdulo com memria compartilhada sem utilizar sc_signal. O novo mdulo foi traduzido para VHDL e Verilog e o resultado obtido foi o mesmo quanto ao grau de otimizao, porm divergente quanto funcionalidade. A Figura 16 apresenta a traduo realizada para VHDL e a Figura 17 a traduo para Verilog. Utilizando apenas o tipo sintetizvel no qualificado como sc_signal, o resultado em Verilog foi aceitvel, tanto em termos de otimizao quanto comportamento. O mesmo no se pode dizer da verso VHDL. A traduo para VHDL no foi coerente com a descrio e simulao em SystemC RTL, pois foram geradas duas reas de armazenamento, locais para cada processo, o que no representa uma memria compartilhada, como se pode notar na Figura 16.

entity mem is port( clock: in STD_LOGIC; ce: in STD_LOGIC; rw: in STD_LOGIC; dataIn: in UNSIGNED (15 DOWNTO 0); addIn: in UNSIGNED (2 DOWNTO 0); dataOut: out UNSIGNED (15 DOWNTO 0)); end mem; architecture me m of mem is type VHDL_TYPE_1 is array (0 to 7) of UNSIGNED (15 DOWNTO 0); begin readMem : process (clock, ce, rw) variable memio: VHDL_TYPE_1; begin if (clock /= '0' and ce /= '0' and rw = '0') then memio(CONV_INTEGER(addIn)) := dataIn; end if; end process; writeMem : process (clock, ce, rw) variable memio: VHDL_TYPE_1; begin if (clock /= '0' and ce /= '0' and rw /= '0') then dataOut <= memio(CONV_INTEGER(addIn)); end if; end process; end mem;

Figura 16 Resultado da traduo para VHDL do mdulo mem SystemC sem utilizar sc_signal. O melhor resultado quanto funcionalidade e tamanho de hardware foi obtido com a traduo para Verilog, conforme pode ser visto na Figura 17, para o caso de memria compartilhada.

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 14/49

Diretivas de Projeto SystemC

Projeto Fnix

module mem(clock, ce, rw, dataIn, addIn, dataOut); input clock; wire clock; input ce; wire ce; input rw; wire rw; input [15:0] dataIn; wire [15:0] dataIn; input [2:0] addIn; wire [2:0] addIn; output [15:0] dataOut; reg [15:0] dataOut; reg [15:0] memio [7:0]; always @(clock or ce or rw) begin : readMem if (clock && ce && !rw) memio[addIn] = dataIn; end

always @(clock or ce or rw) begin : writeMem if (clock && ce && rw) dataOut <= memio[addIn]; end endmodule

Figura 17 - Resultado da traduo para Verilog do mdulo mem SystemC sem utilizar sc_signal. 3.2.4 Problemas utilizando a verso 2002.06 do CoCentric SystemC Compiler

O emprego da verso 2002.06 do CoCentric SystemC Compiler apresentou alguns problemas quanto coerncia e otimizao do cdigo HDL gerado. A questo de coerncia est relacionada utilizao de sinais ou portas do tipo bool e a questo de otimizao est relacionada descrio dos processos de um mdulo. A Figura 18 ilustra um cdigo SystemC RTL vlido que ao ser submetida verso 2002.06 do CoCentric SystemC Compiler gera uma descrio VHDL sintaticamente incorreta.

#ifndef _reg_h #define _reg_h #include <systemc.h> SC_MODULE(reg) { sc_in< bool > clock, reset; sc_in< sc_uint<16> > D; } sc_out< sc_uint<16> > Q; void mainProcess(); SC_CTOR(reg) { SC_METHOD(mainProcess); sensitive << reset << clock << D; } }; #endif if (reset.read()) Q.write(0); else if (!clock.read()) Q.write(D.read()); #include "reg.h" void reg::mainProcess() {

Figura 18 - Processo utilizando sinais do tipo bool com comparao implcita. Observando a linha em destaque na Figura 18, direita, v-se uma clusula de reset onde porta Q atribudo o valor 0 sempre que o valor de reset for verdadeiro. A simulao do mdulo em SystemC correta, porm quando traduzido para VHDL com a verso 2002.11 do SystemC Compiler, o resultado da traduo deste processo uma descrio VHDL incorreta, como pode ser visto nas linhas em destaque na Figura 19. A porta de entrada reset uma porta do tipo std_logic em VHDL e pode assumir mais de 5 valores diferentes o que invalida a clusula if reset then. Por ser um conjunto de classes, os tipos de dados especficos de SystemC possuem mtodos prprios. Assim, quando utiliza-se um sinal do tipo sc_lv<N>, pode-se fazer a converso deste para um valor inteiro sem sinal ou inteiro com sinal apenas incluindo a chamada de mtodo to_uint() ou to_int(), respectivamente. O problema que quando o compilador resolve esta chamada de mtodos, associada uma varivel local ao processo a cada converso, o que resulta em ocupao de rea adicional em hardware.

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 15/49

Diretivas de Projeto SystemC

Projeto Fnix

LIBRARY IEEE, SYNOPSYS; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_MISC.ALL; USE SYNOPSYS.ATTRIBUTES.ALL;

entity reg port( clock: reset: ce: D: Q: end reg;

is in STD_LOGIC; in STD_LOGIC; in STD_LOGIC; in UNSIGNED (15 DOWNTO 0); out UNSIGNED (15 DOWNTO 0));

architecture reg of reg is begin mainProcess : process (reset, clock) begin if reset then Q <= CONV_UNSIGNED(0, 16); elsif clock then Q <= D; end if; end process; end reg;

Figura 19 Traduo do processo mainProcess descrito em SystemC. A soluo encontrada para estes erros foi a utilizao de uma verso mais atualizada do CoCentric SystemC Compiler. A verso utilizada a 2003.06, disponvel para download dos parceiros Synopsys Inc. no endereo ftp://ftp.synopsys.com.

4. Tcnicas de Prototipao em FPGA

Aborda-se aqui o processo de validao em hardware do controlador serial. A prototipao em FPGAs de hardware pode ser realizada por diferentes processos. Visando ilustrar o uso de SystemC como linguagem de partida para a prototipao de hardware, mostram-se aqui vrios fluxos possveis. Primeiro, pode-se partir de SystemC e realizar a sntese lgica usando ferramentas Synopsys, seguido de sntese fsica com ferramentas especficas do vendedor de FPGAs. Pode-se tambm empregar ferramentas Synopsys para a sntese fsica, desde que dispondo das bibliotecas especficas do vendedor de FPGAs instaladas no ambiente Synopsys. Outra possibilidade usar ferramentas Synopsys apenas para traduzir o cdigo SystemC para HDL independente de dispositivo, entrando a partir da com o HDL gerado em um ambiente de CAD especfico, tal como ISE da Xilinx ou Quartus da Altera. A Figura 20 ilustra um conjunto de fluxos possveis, com exemplos de ferramentas empregadas em cada passo. Entre cada dois passos consecutivos, o formato de comunicao de informaes via uma linguagem textual, seja de alto nvel como HDLs e/ou SystemC, seja de baixo nvel como EDIF. As Sees a seguir discutem a sntese a partir de SystemC. Na Seo 4.1, discutem-se fluxos baseados em uma traduo prvia de SystemC para uma HDL. A seguir, a Seo 4.2 apresenta solues para as questes que aparecem durante as snteses lgica e fsica do hardware em um fluxo baseado em ferramentas Synopsys e em um fluxo baseado em ferramentas Xilinx. Finalmente, a Seo 8 apresenta os ambientes usados na validao do prottipo em hardware para o estudo de caso serial.

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 16/49

Diretivas de Projeto SystemC

Projeto Fnix

Captura de Projeto em SystemC Captura de Projeto em HDL SC DC_Shell HDL SC/HDL

Sntese Lgica (Leonardo Spectrum)

EDIF

Sntese Fsica (Xilinx ISE)

EDIF

FPGA Compiler II

binrio Configurao do FPGA

Figura 20 Possibilidades de composio de fluxos de projeto para prototipao.

4.1

Traduo SystemC VHDL / Verilog

A traduo automtica de um cdigo em SystemC RTL para VHDL pode ser realizada utilizando a ferramenta CoCentric SystemC Compiler da Synopsys. Esta ferramenta faz parte do ambiente do Design Compiler. Para iniciar o processo de traduo, digita-se:

> dc_shell

4.1.1

SystemC VHDL / Verilog independente da tecnologia de implementao

> compile_systemc format [vhdl ou verilog] <nome_arq.cpp>

A compilao do cdigo em SystemC para VHDL feita pelo seguinte comando:

Observao: Projetos compostos por mais de um mdulo devem ter respeitada uma ordem de compilao especfica. Assim, deve ser executado o comando acima para cada sub-mdulo do sistema. Como exemplo cita-se um projeto composto por um registrador (reg.cpp), um banco de registradores (bcRegs.cpp), conforme mostrado na Figura 21.

bcRegs REG 1 REG 3 REG 2 REG 4

Figura 21 Exemplo de estrutura hierrquica de mdulos SystemC para um dado projeto.

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 17/49

Diretivas de Projeto SystemC

Projeto Fnix

O projeto deve ser compilado da seguinte forma:

> compile_systemc format vhdl/verilog <reg1.cpp> > compile_systemc format vhdl/verilog <reg2.cpp> > compile_systemc format vhdl/verilog <reg3.cpp> > compile_systemc format vhdl/verilog <reg4.cpp> > compile_systemc format vhdl/verilog <bcRegs.cpp>

4.1.2

SystemC VHDL / Verilog / EDIF usando bibliotecas de tecnologia

Nesta Seo apresentam-se alguns passos a serem executados para viabilizar a gerao automtica de cdigo HDL dependente de tecnologia. Considera-se neste caso, o uso de um FPGA da famlia Virtex2 da Xilinx. Define-se as seguintes variveis no dc_shell:

> search_path = search_path + <local_onde_esto_bibliotecas>

Um exemplo prtico para o estudo de caso em questo seria:

> search_path = search_path + /soft/xilinx/synopsys/libraries/syn > target_library = xdc_virtex2-4.db > synthetic_library = {"/soft/xilinx/synopsys/libraries/syn/ xdw_virtex.sldb"} + {"standard.sldb"} > symbol_library = /soft/xilinx/synopsys/libraries/syn/virtex.sdb > link_library = { * } + target_library + synthetic_library

Aps isto, deve-se digitar os seguintes comandos:

> read target_library > read synthetic_library > compile_systemc rtl <nome_do_arquivo_cpp> -rtl_format db > link > compile > write f vhdl o <nome_do_arquivo_vhdl>

Se o projeto for hierrquico, pode-se acrescentar -h ao ltimo comando acima. Note-se a escolha de VHDL como alvo da traduo. Poder-se-ia utilizar no lugar desta o texto verilog, com significado bvio. Obs 1: As bibliotecas target_library e link_library especificam a tecnologia do fabricante que ser utilizada para a gerao do hardware final desejado. Obs 2: A biblioteca symbol_library especifica os smbolos utilizados, conforme o fabricante, para a gerao de esquemtico para posterior avaliao em ferramentas grficas de visualizao de circuitos. Obs 3: A biblioteca synthetic_library contm componentes lgicos independentes de tecnologia que podem gerar um hardware mais otimizado. O compilador mapeia as operaes do projeto para os componentes desta biblioteca.

4.2

Snteses lgica e fsica

A seguir descreve-se dois tipos de fluxos para prototipao de projetos de hardware, possveis segundo a Figura 20. O primeiro fluxo parte de uma descrio SystemC e utiliza ferramental da Synopsys.. O

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 18/49

Diretivas de Projeto SystemC

Projeto Fnix

segundo fluxo parte de uma descrio HDL, utiliza a ferramenta Leonardo Spectrum da Mentor Graphics para realizar a sntese lgica e o sistema de CAD ISE de sntese fsica para gerao de um arquivo de configurao final Obs : A ferramenta Leonardo Spectrum no estritamente necessria, j que pode-se realizar a sntese lgica de dentro do sistema ISE, atravs da ferramenta integrada XST de sntese lgica. Contudo, o software Leonardo Spectrum possui uma caracterstica importante ausente no XST, qual seja, a gerao de estimativas de rea, atraso e freqncia de operao antes da sntese fsica. 4.2.1 Fluxo HDL

Os exemplos desta Seo podem ser usados tanto para a sntese a partir de descries HDL geradas manualmente ou a partir de SystemC que foi automaticamente traduzido para uma HDL. Abaixo usase VHDL como HDL de entrada. O emprego de Verilog ao invs de VHDL i plica modificaes m nfimas no fluxo de prototipao. 4.2.1.1 Sntese Lgica

Supondo que se utiliza a Ferramenta Leonardo Spectrum, da Mentor Graphics, para realizao da sntese lgica, deve-se seguir os seguintes passos, cujo efeito na janela grfica da ferramenta pode ser acompanhado na Figura 22.

Figura 22 Interface grfica do software Leonardo Spectrum da Mentor Graphics, ilustrando os passos relevantes da sntese lgica. 1. Definir a tecnologia a ser usada (Virtex); 2. Definir o tipo do dispositivo (XCV800hq240); 3. Definir a velocidade do dispositivo (-4);

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 19/49

Diretivas de Projeto SystemC

Projeto Fnix

4. Inserir os arquivos .VHD (serialinterface.vhd e top.vhd); Obs : Os mdulos devem ser inseridos respeitando os critrios de hierarquia, de forma ascendente (bottom-up). 5. Definir o diretrio de trabalho (e.g. /home/gaph/taciano); 6. Definir o nome do arquivo de sada (top.edf); 7. Clicar no boto Run Flow; 8. Aps concluso, deve surgir mensagem indicando que o EDIF foi gerado com sucesso. 4.2.1.2 Sntese Fs ica 1. Gerao de um arquivo .EDIF atravs da ferramenta Leonardo Spectrum e posterior uso da ferramenta Xilinx ISE; 2. Usar como entrada arquivos HDL direto na ferramenta Xilinx ISE. A seguir descreve-se os passos para o uso da ferramenta de sntese fsica disponvel no ambiente ISE da Xilinx na sua verso 5.2. 1. Clicar em File-> New Project, para criar um novo projeto. Acompanhar pela Figura 23;

Passada a etapa de sntese lgica, a prxima etapa a sntese fsica. H duas formas de realizar esta:

Figura 23 Criao de um projeto para hardware a ser prototipado em FPGAs Xilinx mediante emprego do ambiente ISE V5.2 da Xilinx. Os passos a seguir correspondem parametrizao bsica do projeto, e o resultados de escolhas relacionadas ao presente estudo de caso encontram-se ilustrados na Figura 24. 2. Colocar o nome do projeto (serial); 3. Definir o diretrio de trabalho C:\Xilinx\bin\serial; 4. Definir as propriedades do dispositivo Device Family: Virtex; Device: xcv800; Package: hq240; Speed Grade: -4; Design Flow: EDIF ou XST VHDL Obs : Escolhe-se a opo EDIF se a sntese lgica j foi realizada, gerando o arquivo EDIF. Caso contrrio, escolhe-se a opo XST VHDL. 5. Pressionar o boto OK.

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 20/49

Diretivas de Projeto SystemC

Projeto Fnix

Figura 24 Parametrizao bsica do projeto de hardware para sntese fsica usando o ambiente ISE V5.2 da Xilinx. 6. A seguir, conforme ilustrado na Figura 25, clica-se com o boto direto do mouse sobre a opo xcv800-4hq-240 e escolhe-se a opo Add a Copy of Source, para inserir os arquivos. Se no item 4 foi escolhida a opo Design Flow: EDIF, ento se insere os seguintes arquivos: top.edf; serial02.ucf; Caso contrrio, insere-se: serial.vhd; top.vhd; serial02.ucf.

Figura 25 Seleo dos arquivos fonte para a sntese fsica usando o ambiente ISE V5.2 da Xilinx. 7. A seguir, conforme ilustrado na Figura 26, na janela de processos deve-se clicar com o boto direito do mouse sobre a opo Implement Design, escolhendo-se em seguida a opo Run;

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 21/49

Diretivas de Projeto SystemC

Projeto Fnix

Figura 26 Disparo da execuo da sntese fsica usando o ambiente ISE V5.2 da Xilinx. Depois de concluda a sntese fsica deve-se proceder gerao do arquivo de configurao binrio do FPGA, tambm denominado de bitstream. Para tanto, necessrio parametrizar a gerao, conforme exemplificado nos passos a seguir e ilustrado na Figura 27, passando aps gerao do bitstream em si, mostrada na Figura 28. 8. Clicar com o boto direito sobre a opo Generate Programming File e selecionar Properties; 9. Clicar sobre General Options e confirmar se a opo Create Bit File est selecionada; 10. Clicar sobre Startup options e selecionar a opo JTAG Clock. Pressupe-se aqui que a configurao do FPGA ser feita usando o protocolo e cabo JTAG. Outras opes existem e sua utilizao est descrita e documentada nos manuais do ambiente ISE;

Figura 27 Parametrizao do processo de gerao de bitstreams usando o ambiente ISE V5.2 da Xilinx. 11. Clicar com o boto direito sobre a opo Generate Programming File e selecionar Run, para gerar o arquivo de configurao do FPGA (top.bit).

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 22/49

Diretivas de Projeto SystemC

Projeto Fnix

Figura 28 Criao do bitstream de configurao usando o ambiente ISE V5.2 da Xilinx. 4.2.2 Fluxo SystemC

Este fluxo voltado para a prototipao em FPGAs Xilinx ou Altera. A seguir descrito o fluxo

utilizando as ferramentas SystemC Compiler e FPGA Compiler II, da Synopsys. Como a ferramenta FPGA Compiler ainda no suporta SystemC diretamente, a traduo inicial fundamental. Os passos so os seguintes: 1. Executar o seguinte comando, para abrir o DC_Shell (ilustrado na Figura 29);

> dc_shell

Figura 29 Chamada do Design Compiler Shell da Synopsys. 2. Gerar o arquivo HDL a partir de entrada SystemC (ilustrado na Figura 30);

> compile_systemc format vhdl <nome_arq.cpp>

Figura 30 Gerao do arquivo HDL a partir do DC Shell. Usa-se como exemplo VHDL. A verso do comando para gerar Verilog trivialmente obtida. 3. Ver o resultado na Figura 31;

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 23/49

Diretivas de Projeto SystemC

Projeto Fnix

Figura 31 Resultado do processo de traduo de SystemC para HDL. Usa-se como exemplo VHDL. 4. A seguir, necessrio entrar na ferramenta FPGA Compiler para proceder sntese fsica, seguida da gerao do bitstream de configurao. Executar o comando fc2 para abrir o FPGA Compiler II conforme mostrado na Figura 32;

Figura 32 Chamada da ferramenta FPGA Compiler II da Synopsys. 5. Criar um novo projeto e apertar o boto OK, conforme mostrado na Figura 33;

Figura 33 Criao de um novo projeto usando a ferramenta FPGA Compiler II da Synopsys.

Uma vez criado o projeto, necessrio estabelecer as bibliotecas a usar e escolher a entidade de nvel de abstrao mais alto da implementao, conforme ilustrado na Figura 34. Os trs passos seguintes a estes so ilustrados na Figura 35 :

6. Selecionar as bibliotecas (ccsc.vhd/attributes.vhd) e os arquivos HDL (serialinterface.vhd/ top.vhd); 7. Selecionar a entidade TOP (top) e selecionar o boto Next;

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 24/49

Diretivas de Projeto SystemC

Projeto Fnix

Figura 34 Seleo de bibliotecas de sntese e do arquivo HDL topo da hierarquia de projeto usando a ferramenta FPGA Compiler II da Synopsys.

Figura 35 Seleo de dispositivo e opes de sntese usando a ferramenta FPGA Compiler II da Synopsys. 8. Selecionar o dispositivo alvo: Vendor: Xilinx Family: VIRTEX Device: V800HQ240

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 25/49

Diretivas de Projeto SystemC

Projeto Fnix

Speed Grade: -4 9. Selecionar Optimization, Optimize for Area, Effort High e aceitar escolher via boto OK; 10. Clicar em RUN para gerar o arquivo EDIF. Este passo e os dois anteriores esto ilustrados na Figura 35; 11. Finalmente, deve-se gerar o arquivo de configurao ( bitstream) do FPGA atravs da Ferramenta Xilinx ISE V5.2, conforme j apresentado nas partes finais da Seo 4.2.1.2.

4.3

Ambientes para validao do prottipo em hardware

Para validar o hardware do controlador de comunicao serial, utilizou-se a plataforma de prototipao XSV800 da empresa XESS Inc.. Esta utiliza um FPGA Virtex XCV800 da Xilinx de 800.000 portas lgicas equivalentes. Adicionalmente, foi tambm utilizada para validar o mdulo a plataforma V2MB1000 da empresa Memec-Insight, contendo um FPGA Virtex2 XC2V1000 da Xilinx de 1.000.000 de portas lgicas equivalentes. Para efetuar a configurao do FPGA a partir de um computador hospedeiro nestas plataformas utilizou-se o software GXSload da XESS e o software Impact da Xilinx, respectivamente. Para enviar dados do computador hospedeiro para o hardware utilizou-se o programa SerialSoftware, desenvolvido pelo grupo GAPH da PUCRS e disponvel na homepage deste. O funcionamento deste software descrito em mais detalhe na Seo 4.3.1. A freqncia mxima de operao estimada pelo software de sntese fsica diferente para cada execuo da sntese, bem como para cada dispositivo alvo empregado. No caso do experimento conduzido, utilizou-se o sistema de CAD ISE Verso 5.2 da empresa Xilinx. A estimativa de freqncia mxima de operao do hardware contendo a serial foi em torno de 50 MHz. A freqncia de operao utilizada para validar o mdulo serial na plataforma XSV800 foi de 25 MHz, obtida pela configurao de um gerador de sinal de relgio da plataforma. Na plataforma V2MB1000 utilizou-se um relgio de 24MHz. 4.3.1 Software para comunicao entre o controlador de comunicao e o hospedeiro

O programa utilizado para enviar e receber dados foi o SerialSoftware, desenvolvido pelo grupo de pesquisa GAPH. Este programa foi escrito em Java e encontra-se disponvel na homepage do GAPH (www.inf.pucrs.br/~gaph). A tela principal do programa aparece na Figura 36. Atravs do SerialSoftware possvel transmitir dados entre o hospedeiro e o mdulo serial executando em uma das plataformas de prototipao citadas. Como mencionado na Seo 2, primeiramente, deve-se enviar o dado sincronizador 55H para estabelecer a taxa de transmisso entre o computador e o controlador de comunicao serial. Aps, pode-se transmitir dados. No caso do estudo de caso presente, todo dado enviado recebido e devolvido intacto pelo hardware ao SerialSoftware. As janelas Transmitter e Receiver mostram os dados digitados pelo usurio do SerialSoftware e a resposta do hardware, respectivamente. O primeiro valor enviado aps inicializao do hardware (55H) consumido pelo processo Autobaud (descrito na Seo 2). Na Figura 36 pode-se perceber esta funcionalidade notando que este valor no devolvido na janela Receiver. Observao Importante: em algumas situaes, o envio do primeiro valor de sincronizao 55H pode no ser suficie nte para estabelecer o sincronismo do hardware. Isto ocorre por motivos ainda no totalmente claros aos implementadores. Uma forma de contornar o problema providenciar sempre o envio de uma seqncia de valores 55H antes de qualquer operao de transferncia de dados usando o mdulo serial. Costuma-se usar 5 a 10 envios deste valor, o que sempre garante atingir o sincronismo. Com isto, um protocolo de inicializao de clientes do mdulo serial deve ser usado. Costuma-se fazer o cliente aguardar que o primeiro dado diferente de 55H chegue pela serial, a partir do qual consideram-se vlidos todos os dados recebidos aps este. Assim, todos os valores 55H iniciais so ignorados pelo cliente, bem com o primeiro valor diferente deste.

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 26/49

Diretivas de Projeto SystemC

Projeto Fnix

Figura 36 - SerialSoftware: utilizado para enviar e receber dados do hospedeiro para o hardware via controlador serial.

5. Tcnicas de Validao Funcional

Nesta Seo descreve -se duas formas de validao funcional para mdulos de propriedade intelectual (IPs) descritos em SystemC RTL. A primeira abordagem, na Seo 5.1, discute a validao de descries SystemC RTL isoladamente. A segunda abordagem trata da validao por comparao entre os resultados gerados com uma descrio originalmente gerada em VHDL e outra originalmente gerada em SystemC RTL.

5.1

SystemC isoladamente

IPs descritos em SystemC podem ser validados atravs da gerao de formas de onda que simulam seu comportamento, seguido da anlise dos resultados obtidos. Os passos tpicos deste processo de validao compreendem: Codificar a funcionalidade do IP em SystemC RTL (conforme Seo 2); Compilar o cdigo utilizando um compilador tal como o GNU gcc ou o compilador Microsoft Visual C++ Compiler (msvc6), e vincular ao projeto o objeto SystemC sc_trace que permite a gerao de um arquivo do tipo VCD para visualizao de formas de onda; Visualizar as formas de onda utilizando uma ferramenta como Gtkwave (ferramenta gratuita).

5.1.1

Visualizao do VCD copiar o arquivo VCD para o diretrio do Gtkwave. abrir uma janela de prompt do DOS. entrar no diretrio do Gtkwave e digitar winwave <arquivo.vcd>.

Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 27/49

Para visualizar o VCD o procedimento o seguinte:

Diretivas de Projeto SystemC

Diretivas de Projeto SystemC

Projeto Fnix

Os cdigos fonte necessrios para gerar o arquivo VCD com o resultado da simulao do controlador serial implementado em SystemC encontram-se no Anexo IV. A tela de abertura do Gtkwave encontra-se na Figura 37.

Figura 37 Tela de abertura do Gtkwave. Deve-se ento adicionar os sinais a serem observados. Para tanto, clica-se em Search e aps em Signal Search Tree, conforme mostrado na Figura 38.

Figura 38 - Adicionando sinais ao grfico de formas de onda da ferramenta Gtkwave. Com os sinais adicionados, pode-se ordenar as formas de ondas atravs dos botes de ZOOM. Na Figura 39 pode-se observar os sinais adicionados e tambm est indicada a regio dos botes de ZOOM.

Figura 39 - Sinais adicionados e botes de ZOOM. Na Figura 40 observa-se as formas de onda correspondentes a uma trecho de uma das simulaes do controlador serial, usada para validar funcionalmente o projeto.

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 28/49

Diretivas de Projeto SystemC

Projeto Fnix

Figura 40 Forma de onda mostrando no Gtkwave uma parte de uma das simulaes usadas para validar o controlador serial implementado em SystemC.

5.2

Simulao funcional com comparao de onda geradas em HDL e SystemC

Outra forma de validao funcional de hardware descrito em SystemC aquela em que o cdigo SystemC gerado a partir da adaptao manual ou traduo automatizada de um cdigo HDL (tipicamente VHDL ou Verilog). Neste caso, comum se dispor de resultados de validao funcional obtidos em um simulador HDL tal como Modelsim ou Active-HDL. Assim, pode-se fazer a validao do cdigo SystemC usando estes simuladores, via comparao das formas de onda obtidas a partir do cdigo HDL e a partir do cdigo SystemC. Os passos a executar para isto so: Simular o mdulo, descrito em VHDL, utilizando ferramentas como ModelSim da Mentor Graphics ou Active-HDL, da Aldec; Adaptar ou traduzir o mdulo de hardware para uma descrio SystemC RTL vlida (conforme mencionado na Seo 2); Traduzir o cdigo SystemC automaticamente para uma HDL (VHDL ou Verilog), utilizando o CoCentric SystemC Compiler;

Observao: Cdigo HDL gerado atravs da ferramenta CoCentric SystemC Compiler da Synopsys utiliza bibliotecas da Synopsys. Para simular o HDL gerado necessrio adicionar alguns arquivos de bibliotecas Synopsys no projeto. Para o caso da linguagem VHDL estes arquivos so ccsc.vhd e attributes.vhd disponveis nos diretrios <%synopsysInstallDir>/package/ccsc/src e <%synopsysInstallDir>/package/synopsys/src, respectivamente. 5.2.1 Comparar as funcionalidades utilizando um simulador de HDL.

Comparao de formas de onda: HDL versus SystemC traduzido para HDL

A ttulo de exemplo, mostra-se aqui a comparao entre implementaes VHDL e SystemC utilizando a ferramenta ActiveHDL da Aldec. Para isto, deve-se ter em mos as formas de onda das duas implementaes, VHDL e SystemC traduzido para VHDL, onde ambos possuam o mesmo nmero de sinais e mesmos nomes para que a comparao possa ser feita diretamente 1 . No ActiveHDL, deve-se clicar no cone Compare waveforms... conforme ilustra a Figura 41.

possvel estabelecer uma correspondncia entre sinais de nomes diferentes para realizar a comparao, mas o processo tedioso. Como assume-se aqui que a implementao SystemC uma traduo manual de cdigo HDL, simples garantir durante a traduo que nomes iguais sero empregados para sinais correspondentes.

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 29/49

Diretivas de Projeto SystemC

Projeto Fnix

Figura 41 - Para efetuar comparaes entre duas formas de onda, escolhe -se a opo Compare waveforms... Na janela Open, mostrada na Figura 42, deve-se ento selecionar a forma de onda que ser comparada com a forma de onda atualmente mostrada na janela de simulao corrente.

Figura 42 - Seleo da forma de onda para comparao. Na Figura 43 pode-se observar o resultado desta ao para o caso de simulaes absolutamente idnticas demonstrando a equivalncia funcional das duas simulaes. A ferramenta ActiveHDL informa quantos sinais foram comparados, quantas diferenas foram encontradas entre as formas de onda e salienta as regies onde se encontram estas diferenas. Existe tambm a possibilidade de se comparar diretamente as formas de onda gerada no ActiveHDL com formas de onda no padro VCD, geradas via o comando SystemC sc_trace. Para que isto seja possvel, quando se seleciona os sinais da descrio em VHDL para visualizar na forma de onda, devese selecionar os que se encontram no mdulo de mais alta hierarquia. Se isto no for respeitado o ActiveHDL no conseguir realizar a comparao. Em ambas as formas de onda, os sinais devero estar no mesmo nvel hierrquico. De resto, a comparao segue o mesmo fluxo citado anteriormente. Porm na janela de Open (Figura 42) no item Files of Type deve-se selecionar Extended Value Change Dump file que o padro VCD, e selecionar o arquivo.VCD desejado. Na Figura 44 mostrase uma comparao entre uma forma de onda gerada no ActiveHDL e uma forma de onda no padro VCD. Nesta comparao visualizam-se algumas diferenas encontradas entre as duas formas de onda, bem como a conveno para salientar estas diferenas.

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 30/49

Diretivas de Projeto SystemC

Projeto Fnix

Figura 43 - Comparao entre duas formas de ondas idnticas.

Figura 44 - Comparao entre duas formas de onda diferentes, uma gerada no ActiveHDL e a forma de onda padro VCD gerada pelo gcc.

6. Referncias

[1] Open SystemC Initiative. Functional Specification for SystemC 2.0. Update for SystemC 2.0.1, Version 2.0-Q April 2002. Disponvel em: http://www.systemc.org/.

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 31/49

Diretivas de Projeto SystemC

Projeto Fnix

[2] Synopsys Inc. Describing Synthesizable RTL in SystemC. Version 1.2. November 2002. Disponvel em: http://www.synopsys.com/products/sld/rtl_systemc.pdf [3] Synopsys Inc. CoCentric SystemC Compiler RTL User and Modeling Guide . Version U2003.06. June 2003. Disponvel na Synopsys SolvNet: http://solvnet.synopsys.com/login/ designsphere. [4] Thorsten, G. et al. System Design with SystemC. Kluwer Academic Publishers, Boston, 217 pages, 2002. [5] Ney Calazans, Edson Moreno, Fabiano Hessel, Vitor Rosa, Fernando Moraes, Everton Carara. From VHDL Register Transfer Level to SystemC Transaction Level Modeling: a Comparative Case Study. In: 16th Symposyum on Integrated Circuits and Systems, SBCCI2003. So Paulo, Brazil, 8 -11 September, 2003. pp. 355-360. Disponvel em http://www.brazilip.org/ fenix/publications/2003_SBCCI_R8_to_publish.pdf. [6] OCP Internationa l Partnership. Open Core Protocol Specification. Release 1.0, Document Revision 002, 2001. [7] OCP International Partnership. Open Core Protocol Specification. Release 2.0, Document Revision 1.1, 2003. [8] Tischer, M. & Jennrich, B. PC Intern The Encyclopedia of System Programming. Chapter 7: Serial Ports. Abacus, Grand Rapids, Sixth Edition, 985 pages, 1996.

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 32/49

Diretivas de Projeto SystemC

Projeto Fnix

Anexo I - Verso VHDL do Controlador Serial RS-232

--######################################################################### --Serial Core with autobaud feature --- clock -- input synchronism signal -- reset -- active high hardware reset signal -- rx_data -- byte to be transmitted from the hardware to the host -- rx_start -- control signal. Indicates data byte available in rx_data -- rx_busy -- hardware-to-host transmit status busy signal -- rxd -- line containing data to the host serial interface -- txd -- line from which to receive data from the host interface -- tx_data -- byte received from the host computer -- tx_av -- control signal - there is data available in tx_data --+------------------+ -| SERIAL | -| +--------+ | -TXD | | | | ---------->| | |=========> tx_data (8 bits) -| | TRANS. | | -| | |---------> tx_av -| | | | -| +--------+ | -| | -| +--------+ | -RXD | | | | -<---------| | |<========== rx_data (8 bits) -clock | | REC. |<---------- rx_start ---------->| | |----------> rx_busy -reset | | | | ---------->| +--------+ | -+------------------+ --- Reviewed by Fernando Moraes 20/05/2002 -- Comments revised by Ney Calazans in 04/11/2003 ---######################################################################### --******************************************************************* -- Serial Core --******************************************************************* library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity serialinterface is port( clock: in std_logic; reset: in std_logic; rx_data: in std_logic_vector (7 downto 0); rx_start: in std_logic; rx_busy: out std_logic; rxd: out std_logic; txd: in std_logic; tx_data: out std_logic_vector (7 downto 0); tx_av: out std_logic );

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 33/49

Diretivas de Projeto SystemC

Projeto Fnix

end serialinterface; architecture serialinterface of serialinterface is -- auto baud related signals type Sreg0_type is (S1, S2, S3, S4, S6); signal Sreg0: Sreg0_type; signal ctr0 : STD_LOGIC_VECTOR(16 downto 0); signal Bit_Cnt: STD_LOGIC_VECTOR (1 downto 0); -- serial clock generation related signals signal CK_CYCLES : STD_LOGIC_VECTOR(13 downto 0); signal contador : STD_LOGIC_VECTOR(13 downto 0); signal serial_clk : STD_LOGIC; -- receiver related signals signal word, busy : STD_LOGIC_VECTOR (8 downto 0); signal go : STD_LOGIC; -- transmitter related signals signal regin : STD_LOGIC_VECTOR(9 downto 0); -- 10 bits: signal resync, r : STD_LOGIC; begin

start/byte/stop

--######################################################################### -- Autobaud process: this process is executed only once after -- each activation of the serial IP reset signal. It determines the rate of -- serial transmission between the hardware and the host processor to the -- hardware side. Each time the baud rate of the host processor is changed, -- the serial interface must be reset so that the autobaud process is run -- to synchronize the hardware to the host software transmission speed. --- Functioning: the host computer must start by sending the control value -- 55H (in binary 0101 0101). The process counts the number of clock cycles -- that fit' in four 0 bits in this control word, for the start bit and the -- first three 0 bits of the payload. To get the target clock period -- divided by 2, the obtained count value is divided by 8. --######################################################################### autobaud: process (reset, clock) begin if Reset = '1' then Sreg0 <= S1; Bit_Cnt <= "00"; ck_cycles <= (OTHERS=>'0'); ctr0 <=(OTHERS=>'0'); elsif clock'event and clock = '1' then case Sreg0 is when S1 => if txd = '0' then -- autobaud starts in the start bit Sreg0 <= S2; ctr0 <= (OTHERS=>'0'); end if; when S2 => ctr0 <= ctr0 + 1; -- count the number of clock cycles if txd = '1' then -- while the received data is '0' Sreg0 <= S3; Bit_cnt <= Bit_Cnt + '1'; end if; when S3 => if Bit_cnt /= "00" and txd = '0' then Sreg0 <= S2; elsif Bit_cnt = "00" and txd = '0' then Sreg0 <= S4; end if; when S4 => if txd = '1' then Sreg0 <= S6; end if; when S6 => Sreg0 <= S6; -- store the number of cycles

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 34/49

Diretivas de Projeto SystemC

Projeto Fnix

ck_cycles <= ctr0(16 downto 3); -- divided by 8

end case; end if; end process; --######################################################################### -- Clockgenerate process: Serial interface clock generation. From time -- to time the clock is resynchronized to adjust to the data reception -- speed of the PC. Resync is controlled externally to this process. --######################################################################### Clockgenerate: process(resync, clock) begin if resync='1' then contador <= (0=>'1', others=>'0'); serial_clk <='0'; elsif clock'event and clock='0' then if contador = ck_cycles then serial_clk <= not serial_clk; contador <= (0=>'1', others=>'0'); else contador <= contador + 1; end if; end if; end process; --######################################################################### -- Shift_Reg process: This process implements a shift register that reads -- data coming from the host serial interface line (TXD). All bits are put -- to 1 after resync detection, which is performed for each start bit -- found. Resync is produced by the Data_TX process. --######################################################################### Shift_Reg: process (resync, serial_clk) begin if resync = '1' then regin <= (others=>'1'); elsif serial_clk'event and serial_clk='1' then regin <= txd & regin(9 downto 1); end if; end process; --######################################################################### -- Data_TX process: This process implements data transmission to the user -- hardware, after the payload byte is received and mounted by the -- Shift_Reg process. This process also produces a resync signal after each -- detecting each start bit. -- Target: User hardware. External Signals: tx_data and tx_av. --######################################################################### Data_TX: process (clock, ck_cycles) begin if ck_cycles=0 then - while ck_cycles is 0, keep TX FSM reset r <= '0'; -- R is na indicator of start bit arrival resync <= '1'; -- keep resync active tx_data <= (others=>'0'); tx_av <= '0'; -- keep telling there is no available data elsif clock'event and clock='1' then if r='0' and txd='0' then -- start bit detected r <= '1'; resync <= '1'; tx_av <= '0'; elsif r='1' and regin(0)='0' then -- full byte received, tell r <= '0'; -- there is data available

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 35/49

Diretivas de Projeto SystemC

Projeto Fnix

tx_data <= regin(8 downto 1); tx_av <= '1'; else -- this is executed for each bit different resync <= '0'; -- from the start bit tx_av <= '0'; end if; end if; end process; --######################################################################### -- Data_RX process: This process implements data transmission to the host -- from the user hardware. The 8-bit word is read from the user hardware -- and stored together with the start bit. Then, this word is shifted to -- produce the serial transmission to host. Vector busy is filled with 1s -- and then 0s are shifted into it. Rx_busy is output to the user hardware. -- When last bit of busy becomes 0, transmission has finished. -- Target: host. External Signals: rxd and rxd_busy --######################################################################### Data_RX: process(rx_start, reset, serial_clk) begin if rx_start='1' or reset='1' then go <= rx_start ; rx_busy <= rx_start ; word <= (others=>'1'); busy <= (others=>'0'); elsif serial_clk'event and serial_clk ='1' then go <= '0'; -- go is made 0 exactly 1 cycle after reset/rx_start if go='1' then word <= rx_data & '0'; -- read/store byte to be sent to host busy <= (8=>'0', others=>'1'); else word <= '1' & word(8 downto 1); -- shift left word busy <= '0' & busy(8 downto 1); -- and busy vectors rx_busy <= busy(0); -- set rx_busy to bit 0 in busy vector end if; end if; end process; rxd <= word(0); -- bit sent to the host computer is always bit 0 in word end serialinterface;

Diretivas de Projeto SystemC

Diretivas_Sintese_Brazil_IP_1.0.0.doc

Pg 36/49

Diretivas de Projeto SystemC

Projeto Fnix

Anexo II - Verso SystemC do Controlador Serial RS-232 Arquivo serial.h

#ifndef __serialinterface_h #define __serialinterface_h SC_MODULE(serialinterface) { sc_in sc_in < bool > clock; < bool > reset;

sc_in < bool > rx_start; sc_out < bool > tx_av; sc_out < bool > rx_busy; sc_in < bool > TXD; sc_out < bool > RXD; sc_in < sc_lv<8> > rx_data; sc_out < sc_lv<8> > tx_data; sc_out < bool > tx_av_out; //AUTO BAUD-----------------------sc_signal < sc_uint<3> > Sreg0; //ESTADOS 001=S1, 010=S2, 011=S3, 100=S4, 110=S6 sc_signal < sc_uint<17> > Ctr0; sc_signal < sc_uint<2> > Bit_Cnt; //--------------------------------//Geracao do clock da serial------sc_signal < sc_uint<14> > ck_cycles; sc_signal < sc_uint<14> > contador; sc_signal < bool > serial_clk; //--------------------------------//RECEPCAO------------------------sc_signal < sc_uint<9> > word; sc_signal < sc_uint<9> > busy; sc_signal < bool > go; //--------------------------------//TRANSMISSAO---------------------sc_signal < sc_uint<10> > regin; sc_signal < bool > resync; sc_signal < bool > r; //--------------------------------void void void void void void proc_autobaud(); proc_geraclock(); proc_transRdesl(); proc_transmissao(); proc_recepcao(); update_rxd();

SC_CTOR(serialinterface) {

Diretivas de Projeto SystemC Diretivas_Sintese_Brazil_IP_1.0.0.doc Pg 37/49

Diretivas de Projeto SystemC

Projeto Fnix

SC_METHOD(proc_autobaud); sensitive_pos << clock; sensitive_neg << reset; SC_METHOD(proc_geraclock); sensitive_pos << resync; sensitive_neg << clock; SC_METHOD(proc_transRdesl); sensitive_pos << serial_clk; sensitive_pos << resync; SC_METHOD(proc_transmissao); sensitive << ck_cycles; sensitive << clock; SC_METHOD(proc_recepcao); sensitive_neg << reset; sensitive_pos << rx_start << serial_clk; SC_METHOD(update_rxd); sensitive << word; } }; #endif

Arquivo serial.cpp