Escolar Documentos

Profissional Documentos

Cultura Documentos

74193

Enviado por

Dyalma PerezDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

74193

Enviado por

Dyalma PerezDireitos autorais:

Formatos disponíveis

CONTADORES Son circuitos digitales lgicos secuenciales de salida binaria o cuenta binaria, caracteristica de temporizacion y de memoria, por lo cual

estn constituidos a base de flip-flops.

CARACTERISTICAS IMPORTANTES 1. 2. 3. 4. Un nmero mximo de cuentas (mdulo del contador) Cuenta ascendente o descendente. Operacin sncrona o asncrona. Autnomos o de autodetencin.

UTILIDAD Se Ejemplos: 1. 2. 3. 4. utilizan para contar eventos.

nmero de pulsos de reloj. medir frecuencias. Se utilizan como divisores de frecuencia y para almacenar datos. Ejemplo: en un reloj digital. Se utilizan para direccionamiento secuencial y algunos circuitos aritmticos.

CONTADORES DE RIZADO. Son dispositivos contadores que tienen conectados los flip-flops en forma asincrona, es decir, que no,tienen conectadas las entradas de reloj (CLK) en paralelo, sino que tiene que esperar que el primer flip-flop, al activarse por el pulso conmute generando una salida, la cual active o coloque en modo de conmutacion al siguiente flip-flop, el cual con el siguiente pulso conmuta activando al siguiente y asi sucesivamente. El modo de conmutacion en los flip-flop se consigue colocando las entradas J y K en ALTA (1 logico). El mdulo de un contador est determinado por la cuenta mxima a la que es diseado, es decir, si el contador es diseado para que cuente de 0 a 15 su mdulo es el 16 (contador mdulo 16) y simplificado se denomina contador mod-16, si es diseado para contar de 0 a 9 ser un contador mdulo 10 o mod-10, etc.

CONTADOR DE RIZADO MODULO- 16. Este contador se encuentra constituido por flip-flop JK en modo de conmutacin al mantener presente en las entradas J y K un 1 lgico y conectados entre si de forma asncrona, es decir, que la salida del flip-flop 1 (FF1) est conectada de forma directa a la entrada de reloj del siguiente flip-flop 2 (FF2). Los indicadores de salida dan una seal binaria, donde el indicador A (QA) es el LSB (Bit Menos Significativo), el indicador D (QD) es el MSB (Bit Ms Significativo).

Figura 1: Contador de rizado mod-16 El circulito en la entrada de reloj (CLK) de los fip-flops, nos indica que trabajan o conmutan con lgica negativa, es decir, que se activan en la transicin de ALTA a BAJA (flanco posterior) del pulso de reloj y la salida del FF1 (QA) va del nivel BAJO al ALTO dando como resultado la cuenta binaria 0001. En el pulso 2, en la transcicion del nivel ALTO a BAJO, FF1 se desactiva pasando su salida del nivel ALTO a BAJO, activando el FF2, conmutando la salida del nivel BAJO a ALTO generando la cuenta 0010, en el pulso 3 del reloj se activa FF1 generando la salida 0011, porque FF2 se encuentra en mantenimiento teniendo su salida (QB) activada, en el siguiente pulso se incrementa la cuenta a 0100, segn se observa en el diagrama de tiempo de la figura 2.

Cuenta decimal 0 1 2 3 4 5 6 7 Tabla 1:

Cuenta binaria 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1

Cuenta decimal 8 9 10 11 12 13 14 15 de

Cuenta binaria 1 1 1 1 1 1 1 1 un 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 contador mod-16

Secuencia

Figura 2: Diagrama de tiempos de un contador mod-16 CONTADORES PARALELOS

Con este tipo de contadores se elimina o se atenua el retardo que se presenta en los contadores asncronos, donde se tiene que esperar que un flip-flop active al otro. Este efecto se consigue conectando el reloj directamente a las entradas de reloj (CLK) de los flip-flops, es decir, conectando los pulsos de reloj en paralelo (sncronamente) y las salidas de los flip-flops a las entradas J y K de los mismos.

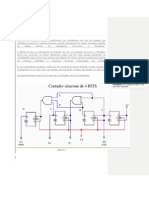

CONTADOR

PARALELO

DE

BITS

MOD-8.

Figura 3: Contador paralelo mod-8

Tambin est construido a base de flip-flops JK, los cuales tienen conectadas sus entradas de reloj en paralelo y sus salidas QA, va conectada a las entradas J y K del siguiente flip-flop (FF2) y asi sucesivamente por lo que estara en modo de mantenimiento hasta que la salida del FF1 les de un 1 logico lo que los colocara en modo de conmutacion a FF2, al estar las entradas del reloj en paralelo, la transicin del primer pulso del nivel ALTO a BAJO, FF1 se activa mientras que FF2 se coloca en modo de conmutacin y FF3 sigue en mantenimiento generando la cuenta 001. En el segundo pulso FF1 se desactiva y FF2 conmuta generando la salida 010, si en el tercer pulso estuviera la salida FF2 conectada directamente a las entradas J y K del FF3 se generara la cuenta mxima 111, por que el FF2 se encuentra en estado de mantenimiento en este caso activado por el pulso anterior, teniendo en modo de conmutacion a FF3 el cual, junto con FF1 se activara en el pulso 3. Para evitar este inconveniente se conecta la salida del FF1 y del FF2 a las entradas de una puerta AND y las salidas de la puerta AND a las entradas J y K de FF3, colocandolo en modo de conmutacin solamente cuando FF1 y FF2 estn activados, es decir, en el pulso 3. Generando en el pulso 4 de reloj que se desactiven FF1 y FF2 y se active FF3 generando la cuenta 100 y en los siguientes pulsos se generarn. El resto de cuenta como se muestra en el diagrama de tiempo de la figura 4.

Cuenta Binaria 0 0 0 0 1 1 0 0 1 1 0 0 0 1 0 1 0 1

Cuenta decimal 0 1 2 3 4 5

1 1 Tabla 2:

1 1 Secuencia

0 1

6 7 de un contador mod-8

Figura 4: Diagrama de tiempos de un contador mod-8 OTROS CONTADORES. Estos contadores no llegan a su cuenta mxima, por que se interrumpe su cuenta segn el diseo o la necesidad que se tenga, por ejemplo, un contador MOD-6 o MOD-10. CONTADOR DE RIZADO MOD-6. Para conseguir este tipo de contador de bits, se utiliza una entrada de reset o borrado la cual se activa inmediatamente despus de la cuenta ms alta que se necesite, en este caso en la cuenta 110, colocando los flip-flops en 0 lgico. En la figura 5 se muestra el esquema de un contador mod-6.

Figura 5: Esquema lgico de un contador de rizado mod-6

Este trabajo de activar las entradas de reset de cada flip-flop lo realiza una puerta NAND la cual da un 0 lgico a las entradas de reset. Al recibir en las entradas de la NAND los 1 lgicos de las salidas del FF2 y del FF3 colocndo en 0 lgico todos los flip-flops y as el contador comienza de nuevo a contar desde 000 hasta 101 o inversamente si es de cuenta descendente.

C 0

B 0

A 0

Cuenta decimal 0

0 0 0 1 1 1 1 Tabla 3:

0 1 1 0 0 1 1

1 0 1 0 1 0

1 2 3 4 5 RESET

1 de un contador mod-6

Secuencia

Figura 6: Diagrama de tiempos del contador mod-6

El retardo que es causado en el pulso 6 cuando va del nivel ALTO a BAJO hasta que FF2 y FF3 son puestos a 0 en el punto B del diagrama de tiempo, se le denomina tiempo de propagacin y ste depende del retardo de propagacin del flip-flop y de la puerta que se est utilizando, este retardo de propagacin en la familia TTL es del orden de unos 30ns (nanosegundos). En las otras familias son mayores. CONTADOR DECADA (CUENTA DECENAS) Es uno de los ms utilizados, esta construido a base de 4 flip-flops JK y una puerta NAND la cual pone en 0 los flip-flops al llegar la cuenta mxima (1010). Como se sabe un contador de 4 bits, llega a una cuenta mxima binaria de 1111 que equivale a 16 en decimal, por lo que la puerta NAND debe activarse inmediatamente despus de la cuenta 1001 0 9 en decimal para que el contador sea mod-10.

Figura 7: Diagrama lgico de un contador dcada rizado

Entonces, como la cuenta inmediatamente despus de 1001 es 1010, entonces se conectan las entradas de la puerta NAND a las salidas de FF2 (QB) y FF4 (QD) que al mandar los unos a las entradas de la NAND, la activan enviando un pulso a las entradas de reset (borrado o CLR) de los flip-flops colocndolos en cero y reinicializando la cuenta.

Figura 8: Smbolo lgico simplificado de un contador dcada

CONTADORES DESCENDENTES Son los contadores en los cuales su cuenta va en sentido inverso a la normal, es decir, de 16 a 0 o en binario de 1111 a 0000. (si es de mod-16) CONTADOR DE RIZADO DESCENDENTE DE 3 BITS Esta diseado similarmente a los dems contadores, con la diferencia que este trae en los flip-flops una salida negada (1), la cual da el pulso contrario a la salida normal (Q), es decir, cuando Q es positivo, 1 es negativo. Esta salida 1 es la que va a ir conectada a la entrada de reloj (CLR) de los otros flip-flops, de resto todas las conexiones son iguales como se muestra en la figura 9.

Figura 9: Contador de rizado descendente de 3 bits

El funcionamiento es el siguiente: al tener los 3 flip-flops sus entradas J y K en estado de conmutacin (ambas entradas en ALTO) y sus salidas Q activadas o en estado de SET en los flip-flops, al llegar el primer pulso en la transicin de ALTO a BAJO, el FF1 conmuta, con lo cual Q va del nivel ALTO a BAJO y 1 va del nivel BAJO al ALTO y la cuenta pasa de 111 a 110 (de 7 a 6 en decimal), en el pulso 2 en la transicin de ALTO a BAJO,

FF1 comuta con lo cual la salida Q va del nivel BAJO al ALTO y la salida 1 va del nivel BAJO al ALTO y se genera la cuenta 101 (5 en decimal) y as hasta llegar a la cuenta mxima, que en este caso es 0000 como se muestra en el diagrama de tiempo,

Figura 10: Diagrama de tiempos de un contador descendente de 3 bits

CONTADORES CON CI TTL Son circuitos integrados donde vienen incluidos los flip-flops conectados segn el tipo de contador y las puertas. Estos contadores se pueden llamar de propsito general. El CI 74192 es un contador reversible BCD sncrono TTL, es decir, mdulo-10. Tiene doble entrada de reloj, una para cuenta ascendente y una para cuenta descendente que conmutan en la transicin del nivel BAJO al nivel ALTO del pulso. La entrada de borrado sncrono se activa en nivel ALTO colocndo las salidas en nivel BAJO (0000) y se inicializa en cualquier nmero que se cargue en las entradas de datos en forma binaria y se transfieren asncronamente a la salida BCD (A=QA, B=QB, C=QC, D=QD). La salida de arrastre se utiliza para conectar en cascada serie varios contadores.

Figura

11:

Smbolo

del

contador

74192

Figura 12: Conexin en cascada de dos contadores de 0 a 99

CONTADOR BINARIO DE 4 BITS TTL 7493. El contador 7493 utilizan 4 flip-flops JK en modo de conmutacin, con entradas de reloj P0 y P1 en donde P1 es la entrada de reloj del segundo flip-flop por lo que para formar un contador de 4 bits mod-16 hay que conectar la salida del primer flip-flop de manera externa (puente) con la entrada P1, quedando P0 como la entrada de reloj del contador. Tambin tiene dos entradas de reset (MR1 y MR2) las cuales no se deben dejar desconectadas (flotando) porque, como estas se activan en ALTA, al estar flotando toman un nivel ALTO lo que mantendra en reset al contador.

Figura 13: Contador 7493 CONTADORES CON CI CMOS. CONTADOR CMOS 74HC393 El CI 74HC393 es un doble contador binario de 4 bits. Esta construido a base del flip-flop T. Las entradas de reloj (1P y 2P) son activadas por flanco posterior, o sea, en la transicion de ALTO a BAJO del pulso de reloj. Las entradas de reset (1MR y 2 MR) del maestro en el contador se activan en nivel ALTO, las salidas se etiquetan desde Q0 a Q3, siendo Q0 el LSB y, Q3 el MSB del numero binario de 4 bits. Requiere una fuente de alimentacion de 5V DC y viene en un CI DIP de14 patillas.

Figura 14: Diagrama lgico del contador CMOS 74HC393

CONTADOR CMOS CI 74HC193

El CI 74HC193 es un contador reversible sncrono de 4 bits preinicializable como lo muestra la hoja de datos.

Figura 16: Contador CMOS 74HC193

Tiene 2 entradas de reloj (CPU y CPD), que se activan en la transicin del nivel BAJO al ALTO del pulso de reloj, la entrada CPU es para la cuenta ascendente (UP) y la entrada CPD es para la cuenta descendente (D), por lo que dependiendo si el contador que se necesite se conecta al nivel alto o +5V. Los modos de operacion del contador CMOS 74HC193 se muestran en la tabla de verdad 5. El modo de reset borra asncronamente las salidas (Q0 a Q3) al binario 0000 activndose en ALTO el cual puede ser un pulso de corta duracin. Las entradas de carga de datos en paralelo (D0 a D3) se utilizan para programar un nmero en binario desde donde se quiere que empieze a contar de nuevo al activar la entrada de carga en paralelo (P)) con un nivel BAJO y los datos son transferidos asncronamente a las salidas (Q0 a Q3). Las salidas de arrastre T5 y T generan un pulso negativo, para la conexin en cascada de contadores, ya sea en forma ascendente o en forma descendente la cuenta de estos. El contador 74HC193 viene en un DIP de 16 patillas y opera con una tensin de alimentacion de +5V DC. DIVISION DE FRECUENCIA: EL RELOJ DIGITAL. En un contador digital de salida binaria el retraso que se forma al activarse cada flip-flop a determinado pulso de reloj, en realidad es una division de frecuencia, por ejemplo, en un contador de 4 bits la salida QA divide la frecuencia en 2 porque necesita un pulso para activarse y otro para desactivarse, la salida QB divide en 4 la frecuencia del reloj de entrada porque tiene que esperar que pasen los 2 pulsos en la salida QA para poder activarse y otros 2 pulsos para desactivarse, la salida QC es una salida que divide por 8 y la salida QD divide por 16.

Figura 20: Diagrama de bloques de un reloj digital.

El reloj digital utiliza los contadores como divisores de frecuencia y acomuladores de cuenta. La funcin del contador como acumulador de cuentas es contar los pulsos de entrada y sirve como memoria temporalmente mientras muestra la hora actual que es decodificada y pasada a los visualizadores de hora. Los contadores como divisores de frecuencia tienen en su entrada una onda cuadrada de 60 Hz, el bloque divisor por 60, es construido por un contador divisor por 6, conectado a un contador divisor por 10.

Figura 21: Contador divisor por 60 El contador divisor por 6 transforma los 60 Hz en 10 hz y el contador divisor por 10 transforma los 10Hz en 1Hz o 1 pulso por segundo. El contador divisor por 10 es construido con un CI 7493 por lo que la primera conexion que se debe hacer es un puente entre Q0 y P1 para convertirlo en un contador de 4 bits, en segundo lugar el CI debe convertirse en un contador decadal (mod-10) como se explico anteriormente, conectando Q3 y Q1 a las 2 entradas de reset. El contador divisor por 6 es hecho con un CI 7493 conectando la entrada de reloj a P1, es decir, que el primer flip-flop (entrada P0) no se utiliza. Los acumuladores de cuenta de 0 a 59 son 2 contadores en donde uno es un contador mod-10 para acumular las unidades (0 al 9) de los segundos y el otro es un contador mod-6 que recibe el pulso de arrastre del mod-10 para contar las decenas de los segundos. Los decodificadores/excitadores sirven para decodificar la salida BCD al visualizador de 7 segmentos.

Você também pode gostar

- CONTADORESDocumento14 páginasCONTADORESalexanderRuizSAinda não há avaliações

- Contadores AsincronosDocumento17 páginasContadores AsincronosRonald Reyes100% (1)

- Contadores asíncronos, paralelos y TTLDocumento4 páginasContadores asíncronos, paralelos y TTLYousei Ruki Uruha Teikoku IshtarAinda não há avaliações

- El Contador en AnilloDocumento14 páginasEl Contador en AnilloJosé GuachoAinda não há avaliações

- Contadores Asincronos y SincronosDocumento30 páginasContadores Asincronos y SincronosYamil Solis Diaz100% (3)

- Practica Contador Binario NuevoDocumento9 páginasPractica Contador Binario NuevoRominAgAinda não há avaliações

- Contador asíncrono binario de 2 y 3 bitsDocumento10 páginasContador asíncrono binario de 2 y 3 bitsUlisesAinda não há avaliações

- Practicas 50Documento8 páginasPracticas 50Eduardo RomeroAinda não há avaliações

- Contadores y MemoriasDocumento26 páginasContadores y MemoriasHector ValdiviaAinda não há avaliações

- Sistemas I 8Documento12 páginasSistemas I 8Sergio Escobar MendozaAinda não há avaliações

- Diseño de ContadoresDocumento20 páginasDiseño de ContadoresDereck LeivaAinda não há avaliações

- Tabla de Verdad de Pic Contador BinarioDocumento14 páginasTabla de Verdad de Pic Contador BinariojaviertdzoAinda não há avaliações

- Práctica 2Documento11 páginasPráctica 2Aguilar Alvarez Fabian EduardoAinda não há avaliações

- Sistemas Digitales 2Documento38 páginasSistemas Digitales 2Maom OsorioAinda não há avaliações

- Registro DesplazamientosDocumento6 páginasRegistro DesplazamientosElvis Paucar SocasiAinda não há avaliações

- Exposicion CircuitosDocumento24 páginasExposicion CircuitosYamil Solis DiazAinda não há avaliações

- Contando Con CircuitosDocumento12 páginasContando Con CircuitosPablo Mamani SuycoAinda não há avaliações

- TD Apunte7Documento23 páginasTD Apunte7JOSE LUIS SEGUNDO MANAYAYAinda não há avaliações

- ElctronicaDocumento12 páginasElctronicaPaulo Barrios RodriguezAinda não há avaliações

- Comparador DigitalDocumento6 páginasComparador DigitalRommel GalminAinda não há avaliações

- Contadores Binarios - Introduc y PrácticasDocumento6 páginasContadores Binarios - Introduc y PrácticasPaola torresAinda não há avaliações

- Capitulo 5 - Circuitos SecuencialesDocumento14 páginasCapitulo 5 - Circuitos Secuencialesgeorge_rivera_26Ainda não há avaliações

- ContadoresDocumento11 páginasContadoresDan GoldmannAinda não há avaliações

- Técnicas Digitales Apunte 7 - ContadoresDocumento23 páginasTécnicas Digitales Apunte 7 - ContadoresProf Matias GarciaAinda não há avaliações

- Contadores y Registros InformeDocumento22 páginasContadores y Registros Informecristhianarevalo2001Ainda não há avaliações

- Pre Informe Lab - 5 Sistemas DigitalesDocumento10 páginasPre Informe Lab - 5 Sistemas DigitalesJosue Mendoza RuedaAinda não há avaliações

- DIseño de COntadoresDocumento17 páginasDIseño de COntadoresCristinaAinda não há avaliações

- Practica 7 Contadores BinariosDocumento9 páginasPractica 7 Contadores BinariosTorrealba GerardoAinda não há avaliações

- Inicio de ContadoresDocumento3 páginasInicio de ContadoresErick BarretoAinda não há avaliações

- Contadores y registros digitalesDocumento18 páginasContadores y registros digitalesLucia Barrera GastañaduiAinda não há avaliações

- Contador AsincronoDocumento5 páginasContador AsincronoromarioAinda não há avaliações

- Introducción a los contadores digitales síncronos y asíncronosDocumento14 páginasIntroducción a los contadores digitales síncronos y asíncronosAlee AlejandroAinda não há avaliações

- Informe de Circuitos Logicos (Contadores) 4Documento18 páginasInforme de Circuitos Logicos (Contadores) 4Louis Charles86% (7)

- Trabajo de ContadoresDocumento24 páginasTrabajo de ContadoresAbraham VergaraAinda não há avaliações

- Previo 4 CONTADORES. 1Documento12 páginasPrevio 4 CONTADORES. 1Jose ArrazolaAinda não há avaliações

- Contador 60 eventos Flip FlopsDocumento8 páginasContador 60 eventos Flip FlopsGerardo MartínezAinda não há avaliações

- Clase Registros Cuarta Parte 2020Documento45 páginasClase Registros Cuarta Parte 2020Unknowia MadnessAinda não há avaliações

- Pre Informe de ContadoresDocumento33 páginasPre Informe de ContadoresHenrySolórzanoMartelAinda não há avaliações

- CONTADORESDocumento7 páginasCONTADORESChristian IzarraAinda não há avaliações

- C2 ContadoresDocumento6 páginasC2 Contadoresbuonarroti17Ainda não há avaliações

- Curso de Inglés BBC English 01Documento8 páginasCurso de Inglés BBC English 01Luis Fernando LizarazoAinda não há avaliações

- Trabajo Practico Flip-Flops y Circuitos Secuenciales PDFDocumento10 páginasTrabajo Practico Flip-Flops y Circuitos Secuenciales PDFDonaldo Leonel Vargas AnguloAinda não há avaliações

- Contador Ascendente y Descendente Utilizando FlipflopsDocumento9 páginasContador Ascendente y Descendente Utilizando FlipflopsEmilio XiaAinda não há avaliações

- Pre Informe 4Documento8 páginasPre Informe 4Quicaño PradoAinda não há avaliações

- U6 Diseño LógicoDocumento31 páginasU6 Diseño LógicoluisAinda não há avaliações

- Sid Ard Sem10Documento11 páginasSid Ard Sem10Arturo ReyesAinda não há avaliações

- Ejemplos Practicos de L CapDocumento8 páginasEjemplos Practicos de L Capmiguel ramosAinda não há avaliações

- Contadores síncronos (paralelosDocumento11 páginasContadores síncronos (paralelosWilliams Molina EspirituAinda não há avaliações

- Contador 0 A 7Documento6 páginasContador 0 A 7JUAN PABLO VARGASAinda não há avaliações

- Clase 10 - Tema 4 - Dispositivos Secuenciales y Contadores 2021-2Documento6 páginasClase 10 - Tema 4 - Dispositivos Secuenciales y Contadores 2021-2PlutonioAinda não há avaliações

- Contadores asíncronos MODDocumento6 páginasContadores asíncronos MODEdwin GonzalezAinda não há avaliações

- Contadores SíncronosDocumento7 páginasContadores SíncronosCristian Ochoa AriasAinda não há avaliações

- Practica 10Documento8 páginasPractica 10Arturo Palacios CalderonAinda não há avaliações

- ContadorLaboratorio7Documento7 páginasContadorLaboratorio7luis smallAinda não há avaliações

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiNo EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiNota: 5 de 5 estrelas5/5 (1)

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208No EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208Ainda não há avaliações

- Stock DiciembreDocumento45 páginasStock DiciembreDyalma PerezAinda não há avaliações

- Lider de BloqueoDocumento3 páginasLider de BloqueoDyalma PerezAinda não há avaliações

- Programación de Actividades 24.10.22Documento8 páginasProgramación de Actividades 24.10.22Dyalma Perez100% (1)

- Programación de Actividades 01.01.23Documento8 páginasProgramación de Actividades 01.01.23Dyalma PerezAinda não há avaliações

- Jueves 30 de Setiembre - Ficha de TrabajoDocumento1 páginaJueves 30 de Setiembre - Ficha de TrabajoDyalma PerezAinda não há avaliações

- Topología implementación antenasDocumento37 páginasTopología implementación antenasDyalma PerezAinda não há avaliações

- Caligrafía semanal con reflexionesDocumento2 páginasCaligrafía semanal con reflexionesDyalma PerezAinda não há avaliações

- Ingenieria de Las TelecomunicacionesDocumento14 páginasIngenieria de Las TelecomunicacionesDyalma PerezAinda não há avaliações

- Programación de Actividades 23.12.22Documento8 páginasProgramación de Actividades 23.12.22Dyalma PerezAinda não há avaliações

- Programación diaria de actividades en plantaDocumento8 páginasProgramación diaria de actividades en plantaDyalma PerezAinda não há avaliações

- Formato para Presentación de Tesis y Trabajos de InvestigaciónDocumento34 páginasFormato para Presentación de Tesis y Trabajos de InvestigaciónDyalma PerezAinda não há avaliações

- Status Iperc y PETSDocumento1 páginaStatus Iperc y PETSDyalma PerezAinda não há avaliações

- Selcom Fibra y OtrosDocumento1 páginaSelcom Fibra y OtrosDyalma PerezAinda não há avaliações

- TP10 - 6-Arranque de Los ServiciosDocumento1 páginaTP10 - 6-Arranque de Los ServiciosDyalma PerezAinda não há avaliações

- Plano de Evacuación Fase 01 Norte - 3540 - 011Documento1 páginaPlano de Evacuación Fase 01 Norte - 3540 - 011Dyalma PerezAinda não há avaliações

- Redes y Comunicacion Datos 20162 PDFDocumento1 páginaRedes y Comunicacion Datos 20162 PDFDyalma PerezAinda não há avaliações

- Prueba Unidad 9 y 10Documento3 páginasPrueba Unidad 9 y 10Dyalma PerezAinda não há avaliações

- FOR-PERGEN-COT-008 V°01 Análisis de Trabajo SeguroDocumento4 páginasFOR-PERGEN-COT-008 V°01 Análisis de Trabajo SeguroDyalma PerezAinda não há avaliações

- Modelo Carta de Renuncia ChileDocumento1 páginaModelo Carta de Renuncia ChileMiguel Ramirez Medina0% (2)

- ACTA DE VISITA TIPO TSS LADO CLIENTEv2Documento1 páginaACTA DE VISITA TIPO TSS LADO CLIENTEv2Dyalma PerezAinda não há avaliações

- Draka Guia Tecnica Cables Datos ESDocumento4 páginasDraka Guia Tecnica Cables Datos ESDyalma PerezAinda não há avaliações

- DJ Telefonica - Telsius Setiembre 2021Documento3 páginasDJ Telefonica - Telsius Setiembre 2021Dyalma PerezAinda não há avaliações

- Ilo Sama 22.05.2021Documento14 páginasIlo Sama 22.05.2021Dyalma PerezAinda não há avaliações

- Alarma 16 Ac VALEREDocumento7 páginasAlarma 16 Ac VALEREDyalma PerezAinda não há avaliações

- 03 BB03 41753 PDFDocumento1 página03 BB03 41753 PDFElder Lima GalindoAinda não há avaliações

- Sillon BiomedicoDocumento2 páginasSillon BiomedicoDyalma PerezAinda não há avaliações

- PFC Eloy Gonzalez Hernandez PDFDocumento112 páginasPFC Eloy Gonzalez Hernandez PDFChristian JuniorAinda não há avaliações

- Lenguajes de Programacion de PLCDocumento6 páginasLenguajes de Programacion de PLCMarco Antonio Gil RománAinda não há avaliações

- El Diseño de Un Sistema de ControlDocumento17 páginasEl Diseño de Un Sistema de ControlDyalma PerezAinda não há avaliações

- INTRODUCCIÓN - ProyectoDocumento5 páginasINTRODUCCIÓN - ProyectoDyalma PerezAinda não há avaliações

- Guía 5 de Discusión 2021 (d10, d11) .TemperaturaDocumento10 páginasGuía 5 de Discusión 2021 (d10, d11) .TemperaturaOswaldo CardozaAinda não há avaliações

- Florence NightingaleDocumento4 páginasFlorence NightingaleCarmen CerónAinda não há avaliações

- Factura VerticalDocumento1 páginaFactura VerticalCarlos Oswaldo PerezAinda não há avaliações

- ZDB & Z2DB - Rexroth PDFDocumento20 páginasZDB & Z2DB - Rexroth PDFGabrielAinda não há avaliações

- Calidad de La InvestigaciónDocumento21 páginasCalidad de La InvestigaciónPaola injanteAinda não há avaliações

- Factores de Riesgo de IncendioDocumento19 páginasFactores de Riesgo de IncendioJosé Manuel Chávez SagardíaAinda não há avaliações

- Formaciones Mesozoicas en GuatemalaDocumento13 páginasFormaciones Mesozoicas en GuatemalaDulce María GonzálezAinda não há avaliações

- 180 Ae85 PDFDocumento8 páginas180 Ae85 PDFDao TuanAinda não há avaliações

- 120 - Nyy-J - Nyy-O DiferenciasDocumento2 páginas120 - Nyy-J - Nyy-O DiferenciasRudolph AzzAinda não há avaliações

- 1.lang Et Al-2018-Journal of PeriodontologyDocumento8 páginas1.lang Et Al-2018-Journal of PeriodontologyKarla RuizAinda não há avaliações

- Autenticación con tarjetas inteligentesDocumento193 páginasAutenticación con tarjetas inteligentescarlos arocaAinda não há avaliações

- Declaración Impacto Ambiental Zona CamalDocumento32 páginasDeclaración Impacto Ambiental Zona Camalal jazari cueva vasquezAinda não há avaliações

- Cognición Social y Habilidad de Mentalización en DocentesDocumento9 páginasCognición Social y Habilidad de Mentalización en DocentesNesmy ChanAinda não há avaliações

- Ultrasonido Chattanooga MANUAL USUARIODocumento31 páginasUltrasonido Chattanooga MANUAL USUARIOcristinaAinda não há avaliações

- Actividad #1. Elementos de La Toma de DecisionesDocumento7 páginasActividad #1. Elementos de La Toma de DecisionesFlor Maria GomezAinda não há avaliações

- Tema 1 Calibración de PasosDocumento4 páginasTema 1 Calibración de PasosJoseJavierMarinAinda não há avaliações

- Acherontia Styx (Polilla de La Muerte)Documento12 páginasAcherontia Styx (Polilla de La Muerte)Gustavo LimachiAinda não há avaliações

- Modelos y Compor. Org. en El Sistema Policial. Parametros de Estandarizacion de La Gestion PolicialDocumento4 páginasModelos y Compor. Org. en El Sistema Policial. Parametros de Estandarizacion de La Gestion PolicialHumberto Miguel TorresAinda não há avaliações

- Resumen Completo de Jhon Murra de Diego Araya AcuñaDocumento41 páginasResumen Completo de Jhon Murra de Diego Araya AcuñaDiego Andrés Araya Acuña100% (1)

- Arreglos UnidimensionalesDocumento7 páginasArreglos UnidimensionalesAldo Olta100% (1)

- 2018 AnalesIngMec-21.1NormasFabricacionAditiva PPPMASEGGDocumento15 páginas2018 AnalesIngMec-21.1NormasFabricacionAditiva PPPMASEGGraicogonzalezAinda não há avaliações

- Portafolio PsicopatologíaDocumento9 páginasPortafolio PsicopatologíaClarisol Peña PerezAinda não há avaliações

- Catalogo 2022Documento33 páginasCatalogo 2022Zayuri EliasAinda não há avaliações

- Rol de Ejercicios de Replicación, Trasnscripción Del ADNDocumento1 páginaRol de Ejercicios de Replicación, Trasnscripción Del ADNCésar Ulises Loarte Rubio67% (3)

- 1-Identificacion y Evaluacion Peligro MecanicoDocumento44 páginas1-Identificacion y Evaluacion Peligro MecanicoSteban MuñozAinda não há avaliações

- Preguntas de Examen de Álgebra LinealDocumento5 páginasPreguntas de Examen de Álgebra LinealJean Franco Santos LazaroAinda não há avaliações

- TallerNo 1Documento1 páginaTallerNo 1Camilo Moncayo MoncayoAinda não há avaliações

- Semana N°9 Grupo 8Documento63 páginasSemana N°9 Grupo 8Jenifer NausinAinda não há avaliações

- Niños calle y proyecto saludDocumento5 páginasNiños calle y proyecto saludDavid DávalosAinda não há avaliações

- MinutasDocumento9 páginasMinutasMaria Lorean CasasolaAinda não há avaliações