Escolar Documentos

Profissional Documentos

Cultura Documentos

Memoria Cache

Enviado por

EddieDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Memoria Cache

Enviado por

EddieDireitos autorais:

Formatos disponíveis

ORGANIZACIN Y ARQUITECTURA DEL COMPUTADOR II

MEMORIA INTERNA.

Memoria Interna

Programa

1. Jerarqua de Memoria 2. Memoria Cach

Definicin y Funcionamiento Elementos de diseo de la cach Ejemplo de funcionamiento

3. Memoria Virtual.

Memoria Segmentada Memoria Paginada Memoria Virtual

4. Conclusiones

Memoria Interna

Caractersticas de los sistemas de memoria Ubicacin:

Procesador. Interna (Principal). Externa (Secundaria). Capacidad: Tamao de la Palabra. (8, 16, 32 y 64bits). Numero de palabras. Unidad de Transferencia: (64, 128 y 256 bits) Palabra. Bloque. Mtodo de Acceso: Acceso Secuencial. Acceso Directo. Acceso Aleatorio. Acceso Asociativo. Dispositivo Fsico: Semiconductor. Soporte Magntico. Caractersticas Fsicas: Voltil / No Voltil. Borrable / No Borrable. Organizacin.

Prestaciones: (Tn = Ta + N/R) Tiempo de Acceso. Tiempo de Ciclo. Velocidad de Transferencia.

Memoria Interna

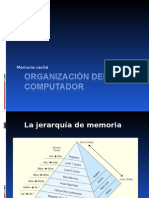

1. Jerarqua de Memoria.

Los programas y datos se almacenan en memoria. La jerarqua de memoria surge para optimizar la relacin que existe entre el coste, tiempo de acceso y tamao de la memoria. Localidad de las referencias Existe una alta probabilidad de que dos referencias consecutivas en el tiempo se encuentren alojadas en posiciones relativamente prximas en memoria. Adems, una referencia reciente tiene cierta probabilidad de ser referenciada de nuevo.

Memoria Interna

1. Jerarqua de Memoria.

Esquema de la jerarqua de memoria. La informacin sube y baja por la pirmide segn las necesidades. El vrtice de la pirmide tiene menos capacidad pero ms velocidad y contiene los datos que estn siendo utilizados.

Memoria Interna

2. Memoria cach

El objetivo de la memoria cach es lograr que la velocidad de la memoria sea la mas rpida posible, consiguiendo al mismo tiempo un tamao ms grande al precio de memorias semiconductoras menos costosas.

La memoria cach es una memoria muy rpida pero de pequeo tamao entre la CPU y la memoria principal. Entre Cach y Memoria Principal la transferencia de informacin se realiza en unidades mayores que la palabra, es decir, en bloques.

Memoria Interna

Estructura de un sistema de memoria cach/principal

Direccin De Memoria

0

1 Nmero de lnea

0

Etiqueta

Bloque

Bloque (K palabras)

1

2

C-1

Longitud de bloque (K palabras)

Cach

2n - 1 Longitud de palabra

Bloque

M=

2n/K

Bloques

Memoria Principal

2. Memoria cach (Operacin de Lectura de la Cach)

Memoria Interna

Memoria Interna

2. Memoria cach (Organizacin)

Memoria Interna

2. Elementos de diseo de la cach

Los elementos a tener en cuenta son: Funcin de correspondencia: Es el mecanismo que asigna una lnea de cach a un bloque de memoria. Algoritmo de sustitucin: Una vez llena la cach, ante una nueva peticin debe decidir cual de las lneas es eliminada. Poltica de escritura. Si se modifica un dato en la cach debemos decidir cuando se modifica tambin en memoria principal. Mecanismo de coherencia de cach: Si hay una memoria principal y varias CPUs cada una con su cach, debemos mantener una relacin lgica entre los datos en las cachs y la memoria principal. Otros elementos de diseo:

10

Memoria Interna

2. Memoria cach.

La cach va a ser una memoria asociativa (se accede por medio de una etiqueta). Las direcciones ahora se pueden dividir en dos partes: nmero de bloque y desplazamiento (para la direccin fsica de la memoria principal). La direccin para obtener un dato de la cach se puede descomponer de varias formas.

11

Memoria Interna

2. Correspondencia directa

Un bloque de memoria principal slo puede ir a una lnea. Cada bloque de memoria principal ya tiene su lnea asignada: Bloque 0-> Lnea 0 Bloque 1 -> Lnea 1 etc.. Bloque M -> Lnea 0 (Si hay M lneas) Bloque M+1 -> Lnea 1,

La direccin se descompone en

Etiqueta Lnea Palabra

12

Memoria Interna

2. Correspondencia directa

Un bloque de memoria principal slo puede ir a una lnea.

13

Memoria Interna

2. Correspondencia directa

Longitud de las direcciones = (s + w) bits Numero de unidades direccionables = 2s+w palabras o bytes Tamao de bloque = Tamao de lnea = 2w palabras o bytes Numero de bloques en memoria principal = 2s+w/2w = 2s Numero de lneas en cache = m = 2r Tamao de la etiqueta = (s-r)bits

14

Memoria Interna

2. Ejercicio 2

Supongamos una memoria cach con correspondencia directa que almacena 64KB, cada bloque es de 512 Bytes. La Memoria Principal es de 16MB. Calcular la direccin virtual para la cach. (Palabra = Byte). Solucin: La cach tiene 64* 1024 / 512 = 128 lneas, es decir necesitamos 7 bits para codificar la lnea. Cada lnea tiene 512 palabras, es decir necesitamos 9 bits para codificar la palabra dentro de la lnea. La memoria principal necesita 24 bits en el bus de direcciones para codificar los 16 MB. Es decir, las direcciones son de 24 bits. Por lo tanto: Direccin virtual: 8 bits para etiqueta (= 24 -7-9) 7 bits para la lnea 9 bits para la palabra

15

Memoria Interna

Un Computador dispone de una memoria RAM de 256 MB y una Memoria Cache por correspondencia directa de 512KB. Cada bloque contiene 8 palabras. Cuntos bloques hay en memoria principal Cuntas lneas tiene la memoria Cache Disea el formato de direcciones de memoria principal. Dnde se hace corresponder , dentro de la Cache, la palabra de la posicin de memoria 3ABC8F8

16

Memoria Interna

Considere un computador con las siguientes caractersticas: un total de 1 MB de memoria principal, el tamao de palabra es de un Byte; el tamao del bloque es de 16 Bytes, en un tamao de cache de 64 KB. 3P Las direcciones de memoria principal: F0010, 01234 Y CABEE, indique los valores de las etiquetas, direccin de lnea de cache y desplazamientos de palabras con una cache con correspondencia directa. Indique dos direcciones cualesquiera de memoria principal con etiquetas diferentes que se correspondan con la misma lnea para una cache con correspondencia directa.

17

Memoria Interna

2. Correspondencia asociativa.

Correspondencia asociativa. Cada bloque de memoria puede ir a cualquier lnea de la cach.

Las direcciones estn formadas por:

Etiqueta Palabra

18

Memoria Interna

2. Correspondencia asociativa.

Correspondencia asociativa.

19

Memoria Interna

2. Correspondencia asociativa.

Longitud de las direcciones = (s + w) bits Numero de unidades direccionables = 2s+w palabras o bytes Tamao de bloque = Tamao de lnea = 2w palabras o bytes Numero de bloques en memoria principal = 2s+w/2w = 2s Numero de lneas en cache = indeterminado Tamao de la etiqueta = s bits

20

Memoria Interna

2. Correspondencia asociativa por conjuntos.

Correspondencia asociativa por conjuntos. La cach se divide en n conjuntos, cada uno de k lneas. Un bloque de memoria principal va al conjunto que le corresponde (en cualquiera de sus lneas). Las direcciones estn formadas por Etiqueta Conjunto Palabra

21

Memoria Interna

2. Correspondencia asociativa por conjuntos.

Correspondencia asociativa por conjuntos.

22

Memoria Interna

2. Correspondencia asociativa por conjuntos.

Longitud de las direcciones = (s + w) bits Numero de unidades direccionables = 2s+w palabras o bytes Tamao de bloque = Tamao de lnea = 2w palabras o bytes Numero de bloques en memoria principal = 2s+w/2w = 2s Numero de lneas en el conjunto = k Numero de conjuntos = v = 2d Numero de lneas en cache = kv = k x 2d Tamao de la etiqueta = (s-d)bits

23

Memoria Interna

2. Algoritmos de sustitucin.

Algoritmos de sustitucin: Nos indica la lnea que debe ser reemplazada. En el caso de correspondencia directa no hay problemas (slo puede ir a una lnea).

LRU (Least Recentlly Used: Menos Recientemente Utilizado). Se reemplaza la lnea que se us hace ms tiempo FIFO (First Input First Output: El primero en entrar es el primero en salir). Se reemplaza la lnea que se carg en memoria hace ms tiempo. LFU (Least Frecuently Used: Menos Frecuentemente Utilizada). Se reemplaza la lnea que se usa con menos frecuencia.

24

Memoria Interna

2. Poltica de escritura.

Poltica de Escritura Es el mecanismo que nos indica cuando se actualizan los datos en memoria principal.

Escritura inmediata: Cuando se modifica un dato en la cach, se modifica en Memoria Principal. Inconveniente: Muchos accesos a memoria. Post escritura: Slo se escribe en memoria principal cuando el bloque ha sido modificado en cach y debe ser reemplazado. Inconveniente: cach y memoria principal pueden tener datos distintos.

25

Memoria Interna

2. Coherencia de cach.

Mecanismo de coherencia de cach. Si hay una memoria principal y varias CPUs cada una con su cach, debemos mantener una relacin lgica entre los datos en las cachs y la memoria principal.

Vigilancia del bus en escritura inmediata: Si una cach escribe en memoria, las dems activan un indicador sealando que esa lnea ya no es valida. Transparencia Hardware: Se utiliza Hardware adicional para modificar todas las cachs. Memoria excluida de la cach: Los datos que se pueden compartir entre procesadores se excluyen de la cach, slo pueden estar en memoria principal.

26

Memoria Interna

2. Otros elementos.

Otros elementos del diseo de una cach.

Cach de dos niveles: Puedo definir dos niveles de cach. Cach unificada frente a partida: Puedo definir una cach para datos y otra para instrucciones o bien una nica cach dnde se almacena todo. Longitud de la lnea. Cuanto mayor longitud tenga la lnea, menos fallos tendremos, pero un fallo supone un coste muy alto (hay que trasvasar muchos datos de la memoria principal a la cach).

27

Você também pode gostar

- Memoria caché funcionamientoDocumento16 páginasMemoria caché funcionamientoArik SamudioAinda não há avaliações

- Simulador CacheDocumento11 páginasSimulador CacheJonathan Herrera50% (2)

- Trabajo Memoria CachéDocumento18 páginasTrabajo Memoria CachéSandra Jaquel Timoteo GuerreroAinda não há avaliações

- Memoria JerarquíaDocumento42 páginasMemoria JerarquíalzAinda não há avaliações

- Practica 8 Simulador CacheDocumento8 páginasPractica 8 Simulador CacheSthewen MoralesAinda não há avaliações

- Actividad T1-03-Serie de Ejercicios 1Documento21 páginasActividad T1-03-Serie de Ejercicios 1Hecsali SalinasAinda não há avaliações

- 06a Arquitecturas y Memorias 2a ParteDocumento32 páginas06a Arquitecturas y Memorias 2a ParteEidenAinda não há avaliações

- Memoria CA HeDocumento6 páginasMemoria CA HedaniAinda não há avaliações

- Ejercicios Tema6Documento4 páginasEjercicios Tema6Xavier DaviasAinda não há avaliações

- Tema3 4 5 6 Memoria ProblemasDocumento4 páginasTema3 4 5 6 Memoria ProblemasKelly EchevarriaAinda não há avaliações

- Clase - 4-5 Memoria CacheDocumento30 páginasClase - 4-5 Memoria CacheMARIA ACHICUEAinda não há avaliações

- Teoria de La Memoria CacheDocumento46 páginasTeoria de La Memoria CacheRoberthoCastillaAinda não há avaliações

- P Tema3 Cache Resueltos PDFDocumento16 páginasP Tema3 Cache Resueltos PDFasturiasbrotherAinda não há avaliações

- Clase 3 Arquitectura de Computadores PDFDocumento42 páginasClase 3 Arquitectura de Computadores PDFIsra VivancoAinda não há avaliações

- Exercises Unit 9 Memory HierarchyDocumento10 páginasExercises Unit 9 Memory HierarchymaiacteAinda não há avaliações

- Almacenamiento de datos en sistemas de cómputoDocumento122 páginasAlmacenamiento de datos en sistemas de cómputoCelia GRAinda não há avaliações

- 5 - 8 - 1 - Memoria CacheDocumento24 páginas5 - 8 - 1 - Memoria CacheDavid SalazarAinda não há avaliações

- Tema MemoriaDocumento16 páginasTema MemoriaRFID DemarkaAinda não há avaliações

- Practico 4 2021Documento8 páginasPractico 4 2021Matias BeneitezAinda não há avaliações

- Tema 3 - Memoria PrincipalDocumento32 páginasTema 3 - Memoria PrincipalMiguel LopézAinda não há avaliações

- Memoria CacheDocumento23 páginasMemoria CachedionisionietoAinda não há avaliações

- Ejercicios Tema 5-12-13Documento5 páginasEjercicios Tema 5-12-13Zarate BismkAinda não há avaliações

- Ejercicios Propuestos Tema 7 Jerarquía de Memoria - CachéDocumento11 páginasEjercicios Propuestos Tema 7 Jerarquía de Memoria - CachéRaúl BaceteAinda não há avaliações

- Memoria CachéDocumento12 páginasMemoria Cachécarmen diazAinda não há avaliações

- UTP - Capítulo 9 Subsistema de MemoriasDocumento42 páginasUTP - Capítulo 9 Subsistema de MemoriasMichel AndersonAinda não há avaliações

- Ejercicios Resueltos Tema 5Documento16 páginasEjercicios Resueltos Tema 5Leandro López100% (1)

- Ejercicios Resueltos Tema 7 Jerarquía de Memoria - CachéDocumento8 páginasEjercicios Resueltos Tema 7 Jerarquía de Memoria - CachéRaúl BaceteAinda não há avaliações

- Práctica 5 - Boletín (Enunciado)Documento4 páginasPráctica 5 - Boletín (Enunciado)Xiaomi mi8Ainda não há avaliações

- Tarea - 5A y 5BDocumento12 páginasTarea - 5A y 5BCrisAinda não há avaliações

- Memorias CacheDocumento18 páginasMemorias CacheEzequiel GonzalezAinda não há avaliações

- Memoria CacheDocumento9 páginasMemoria CacheFlor AfonzoAinda não há avaliações

- Conceptos y Tipos de MemoriaDocumento5 páginasConceptos y Tipos de MemoriaManuelAinda não há avaliações

- Practicas Unidad 4Documento66 páginasPracticas Unidad 4Carlos MoralesAinda não há avaliações

- Practica3 ARQ2020 Jerarquias de MemoriaDocumento2 páginasPractica3 ARQ2020 Jerarquias de MemoriaFrancisco Tomas MauriAinda não há avaliações

- Memoria Compartida Distribuida PDFDocumento19 páginasMemoria Compartida Distribuida PDFbaghead8Ainda não há avaliações

- PreguntasDocumento26 páginasPreguntasDaeed GarciaAinda não há avaliações

- RESUMEN CAPITULO 4 Y5Documento17 páginasRESUMEN CAPITULO 4 Y5HEctorWilsonnAinda não há avaliações

- 2840 PreguntasDocumento11 páginas2840 PreguntasAlex SotoAinda não há avaliações

- Ejercicios de Arquitectura de ComputadorasDocumento2 páginasEjercicios de Arquitectura de ComputadorasHector ChecasovichAinda não há avaliações

- Introducción a las memorias semiconductorasDocumento45 páginasIntroducción a las memorias semiconductorasHenry M CondoriAinda não há avaliações

- 2017 II Trabajo Final de Arquitectura de ComputadorasDocumento2 páginas2017 II Trabajo Final de Arquitectura de Computadorasjoel0% (1)

- AC CuestionarioMemoriaInternaDocumento4 páginasAC CuestionarioMemoriaInternaDarwinPatricioAlvaradoArceAinda não há avaliações

- Ejercicios_CacheDocumento6 páginasEjercicios_CacheCarolina Zúñiga BlancoAinda não há avaliações

- CUESTIONARIO LIBRO Introduccion A La InformaticaDocumento6 páginasCUESTIONARIO LIBRO Introduccion A La InformaticaLuis Arturo Alvarez Sanchez100% (1)

- CacheDocumento2 páginasCacheEric AlmendrasAinda não há avaliações

- Taller de Arquitectura de ComputadoresDocumento6 páginasTaller de Arquitectura de ComputadoresJuan Pablo Ramirez GutierrezAinda não há avaliações

- Preguntas para Final de Arquitectura de ComputadoresDocumento3 páginasPreguntas para Final de Arquitectura de ComputadoresAndro Erick Valero MedinaAinda não há avaliações

- Arquitectura del procesador y la memoria: estructura lógica y funcionalDocumento39 páginasArquitectura del procesador y la memoria: estructura lógica y funcionalMariana LozanoAinda não há avaliações

- Tema III Memoria PDFDocumento25 páginasTema III Memoria PDFMaría Luisa BacaAinda não há avaliações

- CapacidadDocumento14 páginasCapacidadAlíanLeltSwnMAinda não há avaliações

- Practica Calificada ResueltoDocumento4 páginasPractica Calificada ResueltoGinoAinda não há avaliações

- Memoria CachéDocumento17 páginasMemoria CachéFlavio Vargas100% (2)

- Memorias: SegmentaciónDocumento59 páginasMemorias: SegmentaciónLautaro OlivastriAinda não há avaliações

- UNIDAD VI-LENGUAJE MIPS (Parte1)Documento37 páginasUNIDAD VI-LENGUAJE MIPS (Parte1)César Adrian Guevara SalcedoAinda não há avaliações

- Antología de MemoriasDocumento9 páginasAntología de MemoriasJMoisés ElizaldeAinda não há avaliações

- Memoria caché: definición, tipos, niveles y aplicaciónDocumento2 páginasMemoria caché: definición, tipos, niveles y aplicaciónWendyAinda não há avaliações

- Ej T5Ftos EnunciadosDocumento14 páginasEj T5Ftos EnunciadosNek VastianAinda não há avaliações

- UF1275 - Selección, instalación, configuración y administración de los servidores de transferencia de archivosNo EverandUF1275 - Selección, instalación, configuración y administración de los servidores de transferencia de archivosAinda não há avaliações

- UF1468 - Almacenamiento de la información e introducción a SGBDNo EverandUF1468 - Almacenamiento de la información e introducción a SGBDAinda não há avaliações

- Iniciación al diseño de circuitos impresos con Altium DesignerNo EverandIniciación al diseño de circuitos impresos con Altium DesignerAinda não há avaliações

- Niv Mat s7Documento5 páginasNiv Mat s7Lucas TapiaAinda não há avaliações

- Manual de Usuario Sistema SIGESP Modulo APRDocumento18 páginasManual de Usuario Sistema SIGESP Modulo APRignacio ferrerAinda não há avaliações

- Guía de Comunicación y Lenguaje de 3° Básico: 7 tipos de lecturaDocumento2 páginasGuía de Comunicación y Lenguaje de 3° Básico: 7 tipos de lecturaJoaquín VanegasAinda não há avaliações

- La revelación del Hijo AmadoDocumento1 páginaLa revelación del Hijo AmadoRODRIGO AAinda não há avaliações

- Área: Comunicación: Sesión de Aprendizaje N°2Documento5 páginasÁrea: Comunicación: Sesión de Aprendizaje N°2Elizabeth Salazar TelloAinda não há avaliações

- Tropos, Secuencias y Drama LiturgicosDocumento5 páginasTropos, Secuencias y Drama LiturgicosGuille O Luna G100% (2)

- 1021 ViaCrucis-1Documento6 páginas1021 ViaCrucis-1Rafael BahamonteAinda não há avaliações

- 2.3.1.2 Packet Tracer - Sensors and The PT Microcontroller - ILMDocumento4 páginas2.3.1.2 Packet Tracer - Sensors and The PT Microcontroller - ILMFelipe PoloAinda não há avaliações

- Para Una Erotica LatinoamericanaDocumento146 páginasPara Una Erotica Latinoamericanavelvetmorning100% (1)

- Andriller ForensicDocumento11 páginasAndriller Forensicm mAinda não há avaliações

- 00 Programa Analitico - Lenguajes - Ingles - Segundo GradoDocumento16 páginas00 Programa Analitico - Lenguajes - Ingles - Segundo GradoElsa Patricia Parra Vázquez100% (3)

- Metafísica - Tomás AlviraDocumento8 páginasMetafísica - Tomás AlviraAlejandro Rocha Pérez100% (1)

- NORMAS Y TIPOS DE DOCUMENTOS ADMINISTRATIVOS (Tarea 5)Documento4 páginasNORMAS Y TIPOS DE DOCUMENTOS ADMINISTRATIVOS (Tarea 5)Evelin MacasAinda não há avaliações

- Guía de meditaciones cabalísticasDocumento5 páginasGuía de meditaciones cabalísticasYuli Mariela CortesAinda não há avaliações

- Neoclasicismo, Romanticismo y ModernismoDocumento30 páginasNeoclasicismo, Romanticismo y ModernismoJulio César Martínez Castillo0% (1)

- Grupo 3 La AcotacionDocumento7 páginasGrupo 3 La AcotacionValeria AguirreAinda não há avaliações

- GPS South Galaxy G3Documento4 páginasGPS South Galaxy G3joseAinda não há avaliações

- Origen Divino de Las Sagradas EscriturasDocumento20 páginasOrigen Divino de Las Sagradas Escriturasrafaelvillalobos100% (1)

- Dpo3 U2 A2 RucfDocumento7 páginasDpo3 U2 A2 RucfElizaa CallejithaasAinda não há avaliações

- Citas para Operativo de Documentos de Beca Pilares 2023Documento164 páginasCitas para Operativo de Documentos de Beca Pilares 2023ANAHI LISSETE SALVADOR DELGADOAinda não há avaliações

- Larrosa Pedagogia ProfanaDocumento13 páginasLarrosa Pedagogia ProfanaWanderson Vilton83% (6)

- La Profecia PDF Jacob Cristo (Título)Documento1 páginaLa Profecia PDF Jacob Cristo (Título)Gladys BravoAinda não há avaliações

- Adaptación Curricular ModeloDocumento5 páginasAdaptación Curricular Modeloramiro condoriAinda não há avaliações

- Plantilla Seminario 2022 PDFDocumento26 páginasPlantilla Seminario 2022 PDFAurelio Ollachica SullaAinda não há avaliações

- Las Respuestas Literarias A Álbumes Ilustrados en Contextos MulticulturalesDocumento18 páginasLas Respuestas Literarias A Álbumes Ilustrados en Contextos MulticulturalesHikikomori MaryAinda não há avaliações

- Guía El Informe Escrito 8°Documento3 páginasGuía El Informe Escrito 8°Adriana Uribe50% (2)

- La ReseñaDocumento6 páginasLa ReseñaEmilia Guzman100% (1)

- Bosquejo JeremiasDocumento3 páginasBosquejo JeremiasKlever CuzcoAinda não há avaliações

- Informe Ordenamiento Por SeleccionDocumento17 páginasInforme Ordenamiento Por SeleccionGurbhen100% (1)

- Guia Nivel Avanzado Trabajo PrácticoDocumento7 páginasGuia Nivel Avanzado Trabajo PrácticoROCIO LEONAinda não há avaliações