Escolar Documentos

Profissional Documentos

Cultura Documentos

Stick-Diagrams (2) VLSI

Enviado por

mayankfirstTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Stick-Diagrams (2) VLSI

Enviado por

mayankfirstDireitos autorais:

Formatos disponíveis

VLSI

BiCMOS Inverter

Two bipolar transistors (T3 and T4

One nMOS and one pMOS

transistor (both enhancement-type

devices, OFF at Vin=0V)

Inverter has high input

impedance, i.e., MOS gate input

Inverter has low output impedance

Inverter has high drive capability

but occupies a relatively small

area

However, this is not a good

arrangement to implement since

no discharge path exists for

current from the base of either

bipolar transistor when it is being

turned off which results into slow

down of the circuit transistion.

Conventional BiCMOS

Inverter

Two additional enhancement-type

nMOS devices have been added

(T5 and T6).

These transistors provide

discharge paths for transistor

base currents during turn-off.

Without T5, the output low voltage

cannot fall below the base to

emitter voltage VBE of T3.

When Vin = 0 :

T1 is off. Therefore T3 is non-

conducting

T2 ON - supplies current to base of

T4

T4 base voltage set to Vdd.

T5 is turned on & clamps base of T3

to GND. T3 is turned off.

T4 conducts & acts as current

source to charge load CL towards

Vdd.

Vout rises to Vdd - Vbe (of T4)

When Vin = Vd :

T2 is off

T1 is on and supplies current to

the base of T3

T6 is turned on and clamps the

base of T4 to GND. T4 is turned

off.

T3 conducts & acts as a current

sink to discharge load

CL towards 0V

Vout falls to 0V+ VCEsat (of T3)

Again, this BiCMOS gate does

not swing rail to rail. Hence some

finite power is dissipated when

driving another CMOS or

BiCMOS gate. The leakage

component of power dissipation

can be reduced by varying the

BiCMOS device parameters

LATCHUP

Latchup is defined as the

generation of a low

impedance path in CMOS

chips between power

supply rail and

the ground rail due to the

interaction of parasitic

pnp and npn bipolar

transistors.

These BJTs form a (SCR)

with positive feedback

and virtually short circuit

the power rail to ground,

thus causing excessive

current flows and

even permanent device

damage

CMOS Latchup

n+

p-type substrate

n+

p+

p+

V (5 V)

DD

n+ p+

V (0 V)

SS

B S D D S B

n-well

R

sub

R

well

v

O

pnp transistor

npn transistor

If V

Rwell

is

0.7V

If V

Rsub

is

0.7V

Formation of SCR from BJT

Latch up triggering

For latch up to occur the parasitic npn-pnp circuit

has to be triggered and the holding state has to

be maintained.

Latchup can be triggered by transient current or

voltages that may occur internally to a chip

during power-up or externally due to voltages or

currents beyond normal operating ranges.

Two possible triggering mechanisms are

1)lateral triggering

2)vertical triggering

Lateral and vertical triggering

Current has to be injected into either the

npn- or pnp- emitter to initiate latch up.

Lateral triggering occurs when a current

flows in the emitter of the lateral npn-

transistor .

Vertical triggering occurs when a sufficient

current is injected into the emitter of the

vertical- pnp transistor.

Necessary conditions for latch up

Both PNP and NPN bi polars must be

biased into the active state.

The product of the parasitic bipolar

transistor current gains (npn*pnp) is

greater than or equal to one

The terminal network must be capable of

supplying a current greater than the

holding current required by the PNPN path

12

Latchup prevention techniques

Reducing the value of resistors and

reducing the gain of the parasitic

transistors are the basis for eliminating

latch up Reduce the BJT gains by lowering

the minority carrier lifetime through Gold

doping of the substrate (solution might

cause excessive leakage currents).

Substrate resistance : It can be reduced

by the use of silicon starting- material with

a thin epitaxial layer on top of highly doped

substrate .

Well resistance:

It can be reduced by

having retrograde well structure is also

used. This well has a highly doped area at

the bottom of the well, whereas the top of

the well is more lightly doped.

I/O latch up prevention

Reducing the gain of parasitic transistors

is achieved through the use of guard rings.

Guard rings are that p+ diffusions in the p

substrate and n+ diffusions in the n-well to

collect injected minority carriers

p+ guard ring

Use p

+

guardband rings connected to ground around nMOS transistors and

n

+

guard rings connected to V

DD

around pMOS transistors to reduce R

w

and

R

sub

and to capture injected minority carriers before they reach the base of

the parasitic BJT.

N+ Guard ring

Latchup Prevention summary

Use p+ guard rings to ground around nMOS transistors and n+ guard rings connected to

VDD around pMOS transistors to reduce Rwell and Rsub and to capture injected minority

carriers before they reach the base of the parasitic BJTs

Place substrate and well contacts as close as possible to the source connections

Use minimum area p-wells (in case of twin-tub technology or n-type substrate) so that the

p-well photocurrent can be minimized during transient pulses

Source diffusion regions of pMOS transistors should be placed so that they lie along

equipotential lines when currents flow between VDD and p-wells. In some n-well I/O

circuits, wells are eliminated by using only nMOS transistors.

Avoid the forward biasing of source/drain junctions so as not to inject high currents; the

use of a lightly doped epitaxial layer on top of a heavily doped substrate has the effect of

shunting lateral currents from the vertical transistor through the low-resistance substrate.

Layout n- and p-channel transistors such that all nMOS transistors are placed close to

GND and pMOS transistors are placed close to VDD rails. Also maintain sufficient

spacings between pMOS and nMOS transistors.

Stick Diagrams

Cartoon of a layout.

Shows all components.

Does not show exact placement, transistor sizes,

wire lengths, wire widths, boundaries, or any

other form of compliance with layout or design rules.

Useful for interconnect visualization, preliminary layout

layout compaction, power/ground routing, etc.

Stick Diagrams

Metal

poly

ndiff

pdiff

Can also draw

in shades of

gray/line style.

Buried Contact

Contact Cut

Stick Diagrams Some rules

Rule 1.

When two or more sticks of the same

type cross or touch each other that

represents electrical contact.

Stick Diagrams Some rules

Rule 2.

When two or more sticks of different type

cross or touch each other there is no

electrical contact.

(If electrical contact is needed we have to show the connection

explicitly).

Stick Diagrams Some rules

Rule 3.

When a poly crosses diffusion it

represents a transistor.

Note: If a contact is shown then it is not a transistor.

Stick Diagrams Some rules

Rule 4.

In CMOS a demarcation line is drawn to

avoid touching of p-diff with n-diff. All pMOS

must lie on one side of the line and all

nMOS will have to be on the other side.

5 V

Dep

V

out

Enh

0V

V

in

5 v

0 V

V

in

5 v

Alternate Layout Strategy

Mask Layout Encoding

A B

x

y

X X

X X

x

A B

y

Parallel Connected MOS

Patterning

x

y

A B

X

X X

A B

x

y

General Layout Geometry

Individual

Transistors

Shared Gates

Shared drain/

source

Vp

Gnd

Designing MOS Arrays

A

B C

y

x

y

x

A

B C

CMOS STICK DIAGRAMS

Layer Types

p-substrate

n-well

n+

p+

Gate oxide (thin oxide)

Gate (polycilicon)

Field Oxide

Insulated glass

Provide electrical isolation

Demarcation line

Only metal and polysilicon can cross the demarcation line

Top view of the FET pattern

n+ n+ n+ n+ p+ p+ p+ p+

NMOS NMOS

PMOS

PMOS

n-well

The CMOS NOT Gate

X

X

X

X

Vp

Gnd

x

Gnd

n-well

Vp

x

x

x

Contact

Cut

Alternate Layout of NOT Gate

Gnd

Vp

x

x

X

x

Vp

Gnd

X

x

X

X

Example - Stick Diagrams (1/2)

Circuit Diagram. Pull-Down Network

(The easy part!)

Alternatives - Pull-up Network

Complete Stick Diagram

Stick Diagram - Example

NOR Gate

OUT

B

A

Stick Diagram - Example

Power

Ground

B

C

Out

A

NAND Layout

Gnd

Vp

b a.

a

b

X

Vp

Gnd

X

X

X

X

a

b

b a.

NOR Layout

Gnd

Vp

b a +

a

b

X

Vp

Gnd

X

X

X

X

a

b

b a +

Stick Diagram XOR Gate

Examples

Why Design Rules???????

Acts as an interface or

communication link between the

circuit designer and the process

engineer during the

manufacturing phase

Manufacturing problems

Photo resist shrinkage tearing.

Variations in material deposition.

Temperature and oxide thickness.

Impurities.

Variations across a wafer.

Difference between Via and metal

Contact is connection to source, drain or

poly. While Vias is used to make

connection between two metal layers.

Both vias and contact are formed using

metals.

Vias are generally made of tungsten while

contact is made using aluminium.

Transistor problems:

Variations in threshold voltage: This may

occur due to variations in oxide thickness,

ion-implantation and poly layer.

Changes in source/drain diffusion overlap.

Variations in substrate.

Wiring problems:

Diffusion: There is variation in doping which

results in variations in

resistance, capacitance.

Poly, metal: Variations in height, width

resulting in variations in resistance,capacitance.

Shorts and opens.

Oxide problems

Variations in height.

Lack of planarity.

Via problems:

Via may not be cut all the way through.

Undersize via has too much resistance.

Via may be too large and create short.

Types of Design Rules

The design rules primary address two

issues:

1. The geometrical reproduction of features

that can be reproduced by the mask-

making and lithographical process ,and

2. The interaction between different layers.

Two approaches in describing

the design rules

Scalable Design Rules (e.g.

SCMOS, -based design rules)

In this approach, all rules are

defined in terms of a single

parameter . The rules are so

chosen that a design can be

easily ported over a cross

section of industrial process

,making the layout portable

.Scaling can be easily done by

simply changing the value of .

Absolute Design Rules (e.g. -

based design rules ) :

In this approach, the design rules

are expressed in absolute

dimensions (e.g. 0.75m) and

therefore can exploit the features

of a given process to a maximum

degree. Here, scaling and porting

is more demanding, and has to be

performed either manually or using

CAD tools .Also, these rules tend

to be more complex especially for

deep submicron.

-based design rules

The fundamental unity in the definition of a

set of design rules is the minimum line

width .It stands for the minimum mask

dimension that can be safely transferred to

the semiconductor material .Even for the

same minimum dimension, design rules

tend to differ from company to company,

and from process to process. Now, CAD

tools allow designs to migrate between

compatible processes.

Lambda rules

Feature Size: minimum distance between source and

drain of transistor

Feature size = 2 (@ 90nm feature size =45)

According to Moores Law, how much does the feature

size scale by every ~2 years?

Design rules specify line widths,

separations and extensions in

terms of .

Lambda-based

Rules

One lambda

()= one half of the

minimummask

dimension, typically

the length of a

transistor channel.

This can be used to

derive design rules

and to estimate

minimum

dimensions of a

junction area and

perimeter before a

transistor has to be

laid out.

Lambda-based Rules(Cont)

Design rules based on single parameter,

Most foundry allows submission of designs using simpler

set of design rules that can be easily scaled to different

processes.

These are called lambda design rules that has units

of m.

All distance and widths and spacing are written as value

= m where m is scaling multiplier.for ex.: w =3 , s = 4

If the factory will use technology =0.15 m

w =0.45 m, s = 0.6 m

Guidelines for using -based

Design Rules:

Minimum line width of

poly is 2 & Minimum line

width of diffusion is 2

Minimum distance between

two diffusion layers 3

Design Rules Classified into

four main types

Min. width to avoid breaks

Min. spacing to avoid shorts

Min. surround

Min. extension

Minimum extension to ensure

complete overlaps

dpo= min.

extension of

poly beyond

Active

Design Rule

for Active

Areas

Silicon devices are

built on active areas of

the substrate

Wa= min width of active

feature

Sa-a= min. edge-to-edge

spacing of active mask

polygon

Design Rule for

Doped silicon

(n+)

Wa = min width of

an active area

Sa-n = min.

active-to-nSelect

spacing

Design Rule

for Doped

silicon (p+)

Wa = min width of

an active area

sa-p = min.

active-to-nSelect

spacing

Sp-nw= min.

p+ to nWell

spacing

Design

Rule

MOSFET structure exists

every time a poly gate

line completely crosses

an n+ or p+ region

Design Rule for poly

features are

Wp= min. poly width of

a poly line

dpo= min. extension of

poly beyond Active

Design rule for

Active contact

Active contact is a

cut in the oxide that

allows the first layer

of metal to contact

as active n+ or p+

region.

Sa-ac= min.

spacing between

active and active

contact

dac,v = vertical

size of the contact

dac,h = horizontal

size of the contact

C

o

n

t

a

c

t

c

u

t

s

Poly to Metal

Metal to Diffusion

(buried contact)

Poly to Diffusion

(butting contact)

Design rule for Metal1

Metal1 is applied to the wafer after oxide. It is used as interconnect

for signals and also for power supply distribution.

Wm1= min. width of Metal1 line

Sm1-ac= min. spacing from Metal1 to Active Contact

Metal Contact

Two metal wires have 3 distance

between them to overcome capacitance

coupling and high frequency coupling.

Metal wires width can be as large as

possible to decrease resistance.

Butting Contact

Buttering contact is

used to make poly

and silicon contact.

Window's original

width is 4, but on

overlapping width

is 2.

So actual contact

area is 6 by 4.

Vias is a cut in the oxide layers to contact

between two metals.

Distance between two wells depends on the

well potentials as shown above. The reason

for 8 is that if both wells are at same high

potential then the depletion region between

them may touch each other causing punch-

through. The reason for 6 is that if both wells

are at different potentials then depletion region

of one well will be smaller, so both depletion

region will not touch each other so 6 will be

good enough.

Active region has length 10 which is

distributed over the followings

2 for source diffusion

2 for drain diffusion

2 for channel length

2 for source side encroachment

2 for drain side encroachment

Layout Design Rules summary

SCMOS Design Rule Summary

Line size and spacing:

metal1: Minimum width=3, Minimum Spacing=3

metal2: Minimum width=3, Minimum Spacing=4

poly: Minimum width= 2, Minimum Spacing=2

ndiff/pdiff: Minimum width= 3, Minimum

Spacing=3, minimum ndiff/pdiff seperation=10

wells: minimum width=10,

min distance form well edge to source/drain=5

Transistors:

Min width=3

Min length=2

Min poly overhang=2

SCMOS Design Rule Summary

Contacts (Vias)

Cut size: exactly 2 X 2

Cut separation: minimum 2

Overlap: min 1 in all directions

Magic approach: Symbolic contact layer min. size 4 X

4

Contacts cannot stack (i.e., metal2/metal1/poly)

Other rules

cut to poly must be 3 from other poly

cut to diff must be 3 from other diff

metal2/metal1 contact cannot be directly over poly

negative features must be at least 2 in size

CMP Density rules (AMI/HP subm): 15% Poly, 30% Metal

Spacings

Diffusion/diffusion: 3

Poly/poly: 2

Poly/diffusion: 1

Via/via: 2

Metal1/metal1: 3

Metal2/metal2: 4

Metal3/metal3: 4

Disadvantages of Lambda rules

1. Linear scaling is possible only over a

limited range of dimensions.

2. Scalable design rules are conservative

This results in over dimensioned and less

dense design.

3. This rule is not used in real life.

CMOS R and C

Gate

Capacitance

Interconnect

Capacitance

and Resistance

Channel

On-Resistance

Source/Drain

Capacitance

Sources of Resistance

Wiring resistance

MOS structure resistance - R

on

Source and drain resistance

Contact (via) resistance

Top view

Drain n+ Source n+

W

L

Poly Gate

Wire Resistance

L

W

H

R =

L

H W

Sheet Resistance R

R

1

R

2

=

=

L

A

=

Material (O-m)

Silver (Ag) 1.6 x 10

-8

Copper (Cu) 1.7 x 10

-8

Gold (Au) 2.2 x 10

-8

Aluminum (Al) 2.7 x 10

-8

Tungsten (W) 5.5 x 10

-8

Material Sheet Res. (O/ )

n, p well diffusion 1000 to 1500

n+, p+ diffusion 50 to 150

n+, p+ diffusion

with silicide

3 to 5

polysilicon 150 to 200

polysilicon with

silicide

4 to 5

Aluminum 0.05 to 0.1

Sheet Resistance

Sheet resistance is a measure

of resistance of thin films that are

nominally uniform in thickness. It is

commonly used to characterize materials

made by semiconductor doping, metal

deposition, resistive paste printing,

and glass coating

MOS Structure Resistance

The simplest model assumes the transistor

is a switch with an infinite off resistance

and a finite on resistance R

on

S

D

R

on

V

GS

> V

T

Source and Drain Resistance

More pronounced with scaling since

junctions are shallower

With silicidation R is reduced to the

range 1 to 4 O/

R

S

R

D

S

G

D

R

S,D

= (L

S,D

/W)R

where L

S,D

is the length of the source or drain diffusion

R

is the sheet resistance of the source or drain

diffusion (20 to 100 O/ )

Contact Resistance

Transitions between routing layers (contacts through

vias) add extra resistance to a wire

keep signals wires on a single layer whenever

possible

avoid excess contacts

reduce contact resistance by making vias larger

(beware of current crowding that puts a practical

limit on the size of vias) or by using multiple

minimum-size vias to make the contact

Typical contact resistances, R

C

,(minimum-size)

5 to 20 O for metal or poly to n+, p+ diffusion and

metal to poly

1 to 5 O for metal to metal contacts

More pronounced with scaling since contact openings

are smaller

Capacitance Estimation

Gate Capacitance

Diffusion capacitance

Routing capacitance(O/p--------- I/p)

MOS Capacitor characteristics

MOS Capacitor characteristics

Sources of Capacitance

C

w

C

DB2

C

DB1

C

GD12

C

G4

C

G3

wiring (interconnect) capacitance

intrinsic MOS transistor capacitances

V

out2

V

in

extrinsic MOS transistor (fanout) capacitances

V

out

V

out

V

in

M

2

M

1

M

4

M

3

V

out2

C

L

MOS Intrinsic Capacitances

Structure capacitances

Channel capacitances

Depletion regions of the reverse-

biased pn-junctions of the drain and

source

Intrinsic MOS Capacitances

Structure capacitances

Channel capacitances

Diffusion capacitances from the depletion

regions of the reverse-biased pn-junctions

C

GS

C

SB

C

DB

C

GD

C

GB

S

G

B

D

C

GS

= C

GCS

+ C

GSO C

GD

= C

GCD

+ C

GDO

C

GB

= C

GCB

C

SB

= C

Sdiff

C

DB

= C

Ddiff

MOS Structure Capacitances

x

d

Source

n+

Drain

n+

W

L

drawn

x

d

Poly Gate

n+ n+

t

ox

L

eff

Top view

lateral diffusion

C

GSO

= C

GDO

= C

ox

x

d

W = C

o

W

Where Cox (gate capacitance per unit area)

Overlap capacitance (linear)

MOS Channel Capacitances

S

D

p substrate

B

G

V

GS

+

-

n+ n+

depletion

region

n channel

C

GS

= C

GCS

+ C

GSO

C

GD

= C

GCD

+ C

GDO

C

GB

= C

GCB

The gate-to-channel capacitance depends upon

the operating region and the terminal voltages

MOS Diffusion Capacitances

S

D

p substrate

B

G

V

GS

+

-

n+ n+

depletion

region

n channel

C

SB

= C

Sdiff

C

DB

= C

Ddiff

The junction (or diffusion) capacitance is from the

reverse-biased source-body and drain-body pn-junctions.

Review: Reverse Bias Diode

All diodes in MOS digital circuits are reverse biased; the

dynamic response of the diode is determined by

depletion-region charge or junction capacitance

C

j

= C

j0

/((1 V

D

)/|

0

)

m

where C

j0

is the capacitance under zero-bias conditions

(a function of physical parameters), |

0

is the built-in

potential (a function of physical parameters and

temperature)and m is the grading coefficient

m = for an abrupt junction (transition from n to p-

material is instantaneous)

m = 1/3 for a linear (or graded) junction (transition is

gradual)

Nonlinear dependence (that decreases with increasing

reverse bias)

+

-

V

D

Junction Capacitance

Extrinsic (Fan-Out) Capacitance

The extrinsic, or fan-out, capacitance is the

total gate capacitance of the loading gates M3

and M4.

C

fan-out

= C

gate

(NMOS) + C

gate

(PMOS)

= (C

GSOn

+ C

GDOn

+ W

n

L

n

C

ox

) +

(C

GSOp

+ C

GDOp

+ W

p

L

p

C

ox

)

Simplification of the actual situation

Assumes all the components of C

gate

are between

V

out

and GND (or V

DD

)

Assumes the channel capacitances of the loading

gates are constant

Wiring Capacitance

The wiring capacitance depends upon

the length and width of the connecting

wires and is a function of the fan-out from

the driving gate and the number of fan-

out gates.

Wiring capacitance is growing in

importance with the scaling of

technology.

Parallel Plate Wiring

Capacitance

C

pp

= (c

di

/t

di

) WL

permittivity

constant

(SiO

2

= 3.9)

Dielectric

Substrat e

L

W

H

t

di

Electrical-field lines

Current flow

Sources of Interwire Capacitance

interwire

fringe

pp

C

wire

= C

pp

+C

fringe

+C

interwire

= (c

di

/t

di

)WL + (2tc

di

)/log(t

di

/H) + (c

di

/t

di

)HL

W - H/2 H

+

(a)

(b)

Fringing Capacitance

Interconnect

Insights

For W/H < 1.5, the fringe component dominates the

parallel-plate component. Fringing capacitance can

increase the overall capacitance by a factor of 10 or

more.

When W < 1.75H interwire capacitance starts to

dominate

Interwire capacitance is more pronounced for wires in the

higher interconnect layers (further from the substrate)

Rules of thumb

Never run wires in diffusion

Use poly only for short runs

Shorter wires lower R and C

Thinner wires lower C but higher R

Gate-level Delay Estimation

Three common measurements of gate

performance:

Delay time (td or tpd) -- Delay between

when the input signal to a gate reaches

the 50% point and when the output signal

reaches the 50% point.

Rise time (tr) -- time it takes for a signal to

go from 10% to 90% of its output range

Fall time (tf) -- time it takes for a signal to

go from 90% to 10% of its output range

Rise/fall times matter for a number

of reasons

They are a component of total gate delay

While the inputs to a gate are rising or falling, a

conductive path exists between power and ground

1) Power dissipation

2)Can potentially harm the chip if too much

current flows

For signals that have high inductance, overly short

rise/fall times can lead to di/dt-induced swings

Mostly relevant on chip I/O pins

Estimating Delay

Gate delays are determined by how quickly the driving gate can

charge/discharge its load capacitance

Gate delay may vary depending on which inputs

are changing -- generally use the worst case

Fall Time Analysis

During the fall time one or more nMOS

transistors discharge the energy stored in

the output capacitance

During the fall time, the nMOS transistor starts in

the saturated region and passes into the linear

region

Divide fall time into two components: tf,sat and tf,linear.

In saturation, current through the transistor is constant

This becomes

Define t1, t2 such that Vo(t1) = 0.9Vdd and

Vo(t2) = Vdd - Vt. Then

And tf,sat is:

Integrating, we get tf,linear

For many processes, Vt ~= 0.2Vdd,

allowing us to approximate

Rise Time

Redoing the same analysis for the pMOS

transistor in pullup gives

Note that beta for pMOS tends to be about

1/2 beta for nMOS given equivalent size

devices, so typically want pMOS about

twice as wide as nMOS to get equivalent

rise and fall times

For equally sized N and P transistors

where n= 2p

Hence,

Gate Delay Estimation

Depends on rise and fall times of the input

signals.

Assuming (unrealistically) that the input

rises or falls in zero time, then the gate

delay can be approximated as half of the

rise or fall time for the gate, and averaged

to

Circuit Delay Estimation

1. Divide circuit into DC-connected blocks

2. Compute a simple delay model for each block

3. Add the delays for each block to get overall

delay.

In CMOS, a DC-connected block (stage) will be

either:

1. A single logic gate

2. A transmission-gate network and the

gates driving it

General Approach- Divide circuit into DC-connected

components, solve for each component

Scaling of MOS Circuits

VLSI technology is

constantly evolving

towards smaller line

widths

Reduced feature size

generally leads to

better / faster

performance

More gate / chip

MOSFET performance

improves as size is

decreased: shorter switching

time, lower power

consumption.

Scaling Factors

In our discussions we will consider 2 scaling

factors, and

1/ is the scaling factor for VDD and oxide

thickness D

1/ is scaling factor for all other linear

dimensions

We will assume electric field is kept constant

Simple derivations showing the effects of scaling

are derived in Pucknell and Eshraghian pages

125 - 129

To accommodate this change, the size of the

silicon wafers on which the integrated circuits

are fabricated have also increased by a very

significant factor from the 2 and 3 in diameter

wafers to the 8 in (200 mm) and 12 in (300 mm)

diameter wafers

The latest catch phrase in semiconductor

technology (as well as in other material science)

is nanotechnology usually referring to GaAs

devices based on quantum mechanical

phenomena

These devices have feature size (such as film

thickness, line width etc) measured in

nanometres or 10

-9

metres

Recurring Costs

cost of die + cost of die test + cost of packaging

variable cost = ----------------------------------------------------------------

final test yield

cost of wafer

cost of die = -----------------------------------

dies per wafer die yield

t (wafer diameter/2)

2

t wafer diameter

dies per wafer = ---------------------------------- ---------------------------

die area \ 2 die area

die yield = (1 + (defects per unit area die area)/o)

-o

Yield Example

Example

l wafer size of 12 inches, die size of 2.5 cm

2

, 1 defects/cm

2

,

o = 3 (measure of manufacturing process complexity)

l 252 dies/wafer (remember, wafers round & dies square)

l die yield of 16%

l 252 x 16% = only 40 dies/wafer die yield !

Die cost is strong function of die area

proportional to the third or fourth power of the die area

Transistor Scaling Issues

High gate leakage :static power dissipation

Poly depletion in gate electrode increased effective Tox,

reduced Ion

Need for enhanced channel mobility

Will Moores Law run out of steam?

Cant build transistors smaller than an atom

Many reasons have been predicted for end of scaling

Dynamic power

Subthreshold leakage, tunneling

Short channel effects

Fabrication costs

Interconnect delay

Limitations of Scaling

Substrate Doping scaling factors

Depletion width

Interconnect and contact resistances

Subthreshold currents

Logic levels and supply voltage due to

noise

Current density

Short Channel Effects

Hot Electron Effects

Time Dependent Dielectric Breakdown

CMOS and NMOS nand Gates

CMOS and NMOS NOR Gates

Você também pode gostar

- Euler S Path and Stick DiagramDocumento12 páginasEuler S Path and Stick Diagramdsweetalker50% (2)

- Unit2 - 2 - MOS Layers & Stick Diagrams For NMOS - CMOS - BiCMOSDocumento60 páginasUnit2 - 2 - MOS Layers & Stick Diagrams For NMOS - CMOS - BiCMOSneha yarrapothuAinda não há avaliações

- Pass Transistor Logic PDFDocumento25 páginasPass Transistor Logic PDFTejas KumbarAinda não há avaliações

- FUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFDocumento190 páginasFUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFVarunKaradesaiAinda não há avaliações

- Lightening ArresterDocumento13 páginasLightening Arresterrohanlagad10Ainda não há avaliações

- Stick Diagram BasicsDocumento26 páginasStick Diagram Basicssanju012100% (1)

- CMOS Process FlowDocumento35 páginasCMOS Process Flowag21937570Ainda não há avaliações

- Cmos Design Rules Layout PDFDocumento33 páginasCmos Design Rules Layout PDFkrishnaavAinda não há avaliações

- Design and Development of Arduino Based Automatic Fan Control System Using PIR and LM 35 SensorDocumento12 páginasDesign and Development of Arduino Based Automatic Fan Control System Using PIR and LM 35 SensorEzekiel Dela Pena0% (1)

- Stick Diagrams and TutorialDocumento38 páginasStick Diagrams and TutorialSangya Shrivastava0% (3)

- MOS Layers: Four Basic Layers N-Diffusion P-Diffusion Polysilicon MetalDocumento12 páginasMOS Layers: Four Basic Layers N-Diffusion P-Diffusion Polysilicon MetalNivedita Shettar100% (1)

- Transistor: Universiti Teknologi MalaysiaDocumento36 páginasTransistor: Universiti Teknologi MalaysiamaxwhereAinda não há avaliações

- BiCMOS TechnologyDocumento17 páginasBiCMOS TechnologyJacob ChakoAinda não há avaliações

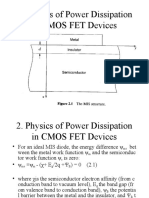

- Physics of Power Dissipation in CMOS FET DevicesDocumento70 páginasPhysics of Power Dissipation in CMOS FET DevicesPunith Gowda M BAinda não há avaliações

- Shallow Junctions SlidesDocumento29 páginasShallow Junctions SlidesGyanaranjan NayakAinda não há avaliações

- Different Types of DiodesDocumento8 páginasDifferent Types of DiodesAllelie UgotAinda não há avaliações

- Ec8353electronicdevicesandcircuitsunit2 180711152109Documento126 páginasEc8353electronicdevicesandcircuitsunit2 180711152109dhivyaAinda não há avaliações

- De Practical FileDocumento140 páginasDe Practical FileSahil BharalAinda não há avaliações

- Resistor Definition and Symbol: o o o o o o o oDocumento7 páginasResistor Definition and Symbol: o o o o o o o oGio Lagadia100% (1)

- A1429 VlsiDocumento8 páginasA1429 VlsiratnamsAinda não há avaliações

- Stick Diagram & Lambda Based Design RulesDocumento21 páginasStick Diagram & Lambda Based Design Rulesbaraniinst6875100% (1)

- E3-327 (3) - M SOI MOSFET Oct 2013Documento56 páginasE3-327 (3) - M SOI MOSFET Oct 2013Tara VishinAinda não há avaliações

- IC Logic Families 1Documento27 páginasIC Logic Families 1Shahin ShuvoAinda não há avaliações

- Optocoupler or Optoisolator PDFDocumento10 páginasOptocoupler or Optoisolator PDFpiyushpandeyAinda não há avaliações

- Lecture 5Documento43 páginasLecture 5Mjj VegaAinda não há avaliações

- AM Generation and Detection MethodsDocumento26 páginasAM Generation and Detection MethodsKalpana KoppoluAinda não há avaliações

- Bipolar TransistorDocumento3 páginasBipolar TransistorAndrei Josef NizaAinda não há avaliações

- Ee 435 2Documento43 páginasEe 435 2EdamEdamAinda não há avaliações

- 1-Introduction To Semiconductor MaterialsDocumento43 páginas1-Introduction To Semiconductor MaterialsStevie AdrielAinda não há avaliações

- Why VLSI? - Moore's Law. - The VLSI Design ProcessDocumento28 páginasWhy VLSI? - Moore's Law. - The VLSI Design Processlim hyAinda não há avaliações

- Ece-V-fundamentals of Cmos Vlsi (10ec56) - SolutionDocumento41 páginasEce-V-fundamentals of Cmos Vlsi (10ec56) - SolutionSanthosh Chandu C100% (2)

- VLSI Design Question BankDocumento10 páginasVLSI Design Question Bankbooks babuAinda não há avaliações

- Optical Fibers: Fiber Is TIR (Total Internal Reflection)Documento12 páginasOptical Fibers: Fiber Is TIR (Total Internal Reflection)Ńovitatis ĎineshAinda não há avaliações

- CMOS CM & Biasing CircuitsDocumento50 páginasCMOS CM & Biasing Circuitsabhi_jAinda não há avaliações

- English (Transistor) : Jurusan Teknik Elektro Program Studi D-Iv Teknik Elektronika Politeknik Negeri Malang 2019Documento5 páginasEnglish (Transistor) : Jurusan Teknik Elektro Program Studi D-Iv Teknik Elektronika Politeknik Negeri Malang 2019Zulfikar Iannur AwwalAinda não há avaliações

- Universal GatesDocumento15 páginasUniversal GatesGirish AcharyaAinda não há avaliações

- Bi CMOSDocumento6 páginasBi CMOSlachuns123Ainda não há avaliações

- Review of Semiconductor Physics, PN Junction Diodes and ResistorsDocumento26 páginasReview of Semiconductor Physics, PN Junction Diodes and ResistorsShraddha JamdarAinda não há avaliações

- Lab 6 Combinational Logic and Boolean SimplificationDocumento4 páginasLab 6 Combinational Logic and Boolean SimplificationRabah AmidiAinda não há avaliações

- Gummen PoolDocumento29 páginasGummen PoolvanithapremkumarAinda não há avaliações

- Optical NetworksDocumento46 páginasOptical NetworksJaviAinda não há avaliações

- CMOS Amplifiers - Problems PDFDocumento20 páginasCMOS Amplifiers - Problems PDFAnurag AnandAinda não há avaliações

- Presentation: Thin Film TransistorDocumento9 páginasPresentation: Thin Film TransistorMayankSharma100% (1)

- PT3 - 13 - FSK Modulator PDFDocumento20 páginasPT3 - 13 - FSK Modulator PDFTempaAinda não há avaliações

- Final Ic & PDC ManualDocumento128 páginasFinal Ic & PDC Manualsree_rajen1388100% (2)

- Chapter 1 IC FabricationDocumento35 páginasChapter 1 IC FabricationAiman NamakuAinda não há avaliações

- DC Motor Simulation Using LTSpiceDocumento7 páginasDC Motor Simulation Using LTSpiceMizael AlvesAinda não há avaliações

- EEN-324 Power ElectronicsDocumento53 páginasEEN-324 Power ElectronicsRameshBabuAinda não há avaliações

- DiodesDocumento91 páginasDiodesMohammad Gulam AhamadAinda não há avaliações

- CapacitorsDocumento4 páginasCapacitorsJohn David YermoAinda não há avaliações

- Unit3 OFCDocumento36 páginasUnit3 OFCrajithaAinda não há avaliações

- Conductor: Isolated Copper AtomDocumento23 páginasConductor: Isolated Copper AtomMuhammad SirajAinda não há avaliações

- Diode Resistance & Diode Equivalent CircuitsDocumento42 páginasDiode Resistance & Diode Equivalent Circuitsgirishkumardarisi254Ainda não há avaliações

- CHPTR 5 Designing Cmos Circuits For Low PowerDocumento27 páginasCHPTR 5 Designing Cmos Circuits For Low Powerharikirthika100% (1)

- Counter Circuits: ObjectivesDocumento9 páginasCounter Circuits: ObjectivesRuhul Amin Khalil100% (1)

- Latch UpDocumento4 páginasLatch UpCherry AbhiAinda não há avaliações

- Latch-Up and Its PreventionDocumento4 páginasLatch-Up and Its PreventionCuong LaidangAinda não há avaliações

- Latch UpDocumento4 páginasLatch UpSaurabh MishraAinda não há avaliações

- Lecture 1. CMOS Logic: Dr. Zhaohui WangDocumento39 páginasLecture 1. CMOS Logic: Dr. Zhaohui WangRajendraAinda não há avaliações

- LATCH UP CMOS InverterDocumento19 páginasLATCH UP CMOS InverterGIRISH GIDAYEAinda não há avaliações

- Exercises On LabviewDocumento4 páginasExercises On LabviewmayankfirstAinda não há avaliações

- Physics-Based Pulse Distortion For Ultra-Wideband SignalsDocumento10 páginasPhysics-Based Pulse Distortion For Ultra-Wideband SignalsmayankfirstAinda não há avaliações

- APARs 280313Documento6 páginasAPARs 280313mayankfirstAinda não há avaliações

- Force and Compliance Controls: 9.1 Hybrid Position/Force ControlDocumento10 páginasForce and Compliance Controls: 9.1 Hybrid Position/Force ControlmayankfirstAinda não há avaliações

- Table of Fourier Transform PairsDocumento8 páginasTable of Fourier Transform PairsmayankfirstAinda não há avaliações

- Broadband Millimeter WaveDocumento10 páginasBroadband Millimeter WavemayankfirstAinda não há avaliações

- Classification of Radio WavesDocumento4 páginasClassification of Radio WavesmayankfirstAinda não há avaliações

- Endfire AntennasDocumento5 páginasEndfire AntennasmayankfirstAinda não há avaliações

- Aim:To Implement The Shur Algorithm Using MatlabDocumento1 páginaAim:To Implement The Shur Algorithm Using MatlabmayankfirstAinda não há avaliações

- Signals and Systems With MATLAB Computing and Simulink Modeling - Steven T. KarrisDocumento651 páginasSignals and Systems With MATLAB Computing and Simulink Modeling - Steven T. KarrisvalstavAinda não há avaliações

- Design RulesDocumento14 páginasDesign RulesmayankfirstAinda não há avaliações

- Lecture 5 Scaling II 28Documento29 páginasLecture 5 Scaling II 28mayankfirstAinda não há avaliações

- What Is TRP? How Is It Calculated? Which Site Provide Regular TRP Rating of News Channels?Documento3 páginasWhat Is TRP? How Is It Calculated? Which Site Provide Regular TRP Rating of News Channels?mayankfirstAinda não há avaliações

- Practical Cs Xii Mysql 2022-23 FinalDocumento9 páginasPractical Cs Xii Mysql 2022-23 FinalHimanshu GuptaAinda não há avaliações

- HemoptysisDocumento30 páginasHemoptysisMarshall ThompsonAinda não há avaliações

- Jurnal Ekologi TerestrialDocumento6 páginasJurnal Ekologi TerestrialFARIS VERLIANSYAHAinda não há avaliações

- Session4 Automotive Front End DesignDocumento76 páginasSession4 Automotive Front End DesignShivprasad SavadattiAinda não há avaliações

- LKG Math Question Paper: 1. Count and Write The Number in The BoxDocumento6 páginasLKG Math Question Paper: 1. Count and Write The Number in The BoxKunal Naidu60% (5)

- Metalcor - 1.4507 - Alloy - F255 - Uranus 52N - S32520Documento1 páginaMetalcor - 1.4507 - Alloy - F255 - Uranus 52N - S32520NitinAinda não há avaliações

- DIFFERENTIATING PERFORMANCE TASK FOR DIVERSE LEARNERS (Script)Documento2 páginasDIFFERENTIATING PERFORMANCE TASK FOR DIVERSE LEARNERS (Script)Laurice Carmel AgsoyAinda não há avaliações

- Bài Tập Từ Loại Ta10Documento52 páginasBài Tập Từ Loại Ta10Trinh TrầnAinda não há avaliações

- Planning EngineerDocumento1 páginaPlanning EngineerChijioke ObiAinda não há avaliações

- Technion - Computer Science Department - Technical Report CS0055 - 1975Documento25 páginasTechnion - Computer Science Department - Technical Report CS0055 - 1975MoltKeeAinda não há avaliações

- The BetterPhoto Guide To Creative Digital Photography by Jim Miotke and Kerry Drager - ExcerptDocumento19 páginasThe BetterPhoto Guide To Creative Digital Photography by Jim Miotke and Kerry Drager - ExcerptCrown Publishing GroupAinda não há avaliações

- F5 Chem Rusting ExperimentDocumento9 páginasF5 Chem Rusting ExperimentPrashanthini JanardananAinda não há avaliações

- Grade 9 WorkbookDocumento44 páginasGrade 9 WorkbookMaria Russeneth Joy NaloAinda não há avaliações

- Why File A Ucc1Documento10 páginasWhy File A Ucc1kbarn389100% (4)

- Digital SLR AstrophotographyDocumento366 páginasDigital SLR AstrophotographyPier Paolo GiacomoniAinda não há avaliações

- Technical Data Sheet TR24-3-T USDocumento2 páginasTechnical Data Sheet TR24-3-T USDiogo CAinda não há avaliações

- Uneb U.C.E Mathematics Paper 1 2018Documento4 páginasUneb U.C.E Mathematics Paper 1 2018shafickimera281Ainda não há avaliações

- A Review of Stories Untold in Modular Distance Learning: A PhenomenologyDocumento8 páginasA Review of Stories Untold in Modular Distance Learning: A PhenomenologyPsychology and Education: A Multidisciplinary JournalAinda não há avaliações

- Catálogo MK 2011/2013Documento243 páginasCatálogo MK 2011/2013Grupo PriluxAinda não há avaliações

- Specialty Coffee Association of Indonesia Cupping Form (ARABICA)Documento1 páginaSpecialty Coffee Association of Indonesia Cupping Form (ARABICA)Saiffullah RaisAinda não há avaliações

- Sistine Chapel Ceiling Lesson PlanDocumento28 páginasSistine Chapel Ceiling Lesson PlannivamAinda não há avaliações

- Buss40004 - Balance of PowerDocumento3 páginasBuss40004 - Balance of PowerVishwa NirmalaAinda não há avaliações

- Discovery and Integration Content Guide - General ReferenceDocumento37 páginasDiscovery and Integration Content Guide - General ReferencerhocuttAinda não há avaliações

- ULANGAN HARIAN Mapel Bahasa InggrisDocumento14 páginasULANGAN HARIAN Mapel Bahasa Inggrisfatima zahraAinda não há avaliações

- CEN and CENELEC Position Paper On The Proposal For CPR RevisionDocumento15 páginasCEN and CENELEC Position Paper On The Proposal For CPR Revisionhalexing5957Ainda não há avaliações

- Morse Potential CurveDocumento9 páginasMorse Potential Curvejagabandhu_patraAinda não há avaliações

- Baxter - Heraeus Megafuge 1,2 - User ManualDocumento13 páginasBaxter - Heraeus Megafuge 1,2 - User ManualMarcos ZanelliAinda não há avaliações

- HAYAT - CLINIC BrandbookDocumento32 páginasHAYAT - CLINIC BrandbookBlankPointAinda não há avaliações

- BRAND AWARENESS Proposal DocumentDocumento11 páginasBRAND AWARENESS Proposal DocumentBuchi MadukaAinda não há avaliações

- ThaneDocumento2 páginasThaneAkansha KhaitanAinda não há avaliações