Escolar Documentos

Profissional Documentos

Cultura Documentos

Verilog

Enviado por

gannoju423Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Verilog

Enviado por

gannoju423Direitos autorais:

Formatos disponíveis

Lexical Conventions Data Types

Very similar to C

Verilog is case-sensitive All keywords are in lowercase

Whitespace Comments Numbers Strings Identifiers Keywords

Whitespace

Whitespace is ignored in Verilog except

In strings When separating tokens

Blank space (\b) Tab (\t) Newline (\n)

Comments

// single line comment /* multi-line comment */ /* Nested comments /* like this */ may not be acceptable (depends on Verilog compiler) */

Used for readability and documentation Just like C:

Arithmetic Logical Relational Equality Bitwise Reduction // Not available in software languages Shift Concatenation Replication Conditional

Number Specification

Sized numbers Unsized numbers Unknown and high-impedance values Negative numbers

X or Z values

Unknown value: lowercase x

High-impedance value: lowercase z Examples

12h13x 6hx 32bz

4 bits in hex, 3 bits in octal, 1 bit in binary 4 bits in hex, 3 bits in octal, 1 bit in binary

Extending the most-significant part

Filled with x if the specified MSB is x Filled with z if the specified MSB is z Zero-extended otherwise 6hx

Applied when <size> is bigger than the specified value

Examples:

Negative numbers

-6d3 4d-2 // illegal

Put the sign before the <size> Examples:

Twos complement is used to store the value Use _ to improve readability

Underscore character and question marks

? is the same as z (only regarding numbers)

4b10?? // the same as 4b10zz 12b1111_0000_1010 Not allowed as the first character

Strings

As in C, use double-quotes Examples:

Hello world! a / b text\tcolumn1\bcolumn2\n

Identifiers and keywords

identifiers: alphanumeric characters, _, and $

Keywords: identifiers reserved by Verilog Examples:

reg value; input clk;

Should start with an alphabetic character or _ Only system tasks can start with $

Value set and strengths Nets and Registers Vectors Integer, Real, and Time Register Data Types Arrays Memories Parameters Strings

Verilog concepts to model hardware circuits

Value level Value strength

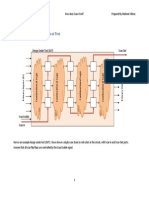

Used to represent connections between HW elements Keyword: wire

Default value: z Examples Values continuously driven on nets Fig. 3-1 Default: One-bit values

unless declared as vectors

For trireg, default is x wire a; wire b, c; wire d=1b0;

Registers represent data storage elements

Retain value until next assignment NOTE: this is not a hardware register or flipflop Keyword: reg Default value: x Example:

reg reset; initial begin reset = 1b1; #100 reset=1b0; end

Net and register data types can be declared as vectors (multiple bit widths) Syntax: Example

wire/reg [msb_index : lsb_index] data_id; wire a; wire [7:0] bus; wire [31:0] busA, busB, busC; reg clock; reg [0:40] virtual_addr;

Integer

Keyword: integer Very similar to a vector of reg

Bit width: implementation-dependent (at least 32bits)

Designer can also specify a width:

integer [7:0] tmp;

integer variables are signed numbers reg vectors are unsigned numbers

Examples:

integer counter; initial counter = -1;

Real

Keyword: real Values:

Cannot have range declaration Example:

Default value: 0 Decimal notation: 12.24 Scientific notation: 3e6 (=3x106)

real delta; initial begin delta=4e10; delta=2.13; end integer i; initial i = delta; // i gets the value 2 (rounded value of 2.13)

Time

Used to store values of simulation time Keyword: time Bit width: implementation-dependent (at least 64) $time system function gives current simulation time Example:

time save_sim_time; initial save_sim_time = $time;

Only one-dimensional arrays supported Allowed for reg, integer, time Syntax:

Not allowed for real data type

<data_type> <var_name>[start_idx : end_idx];

Examples:

integer count[0:7]; reg bool[31:0]; time chk_point[1:100]; reg [4:0] port_id[0:7]; integer matrix[4:0][4:0]; // illegal count[5] chk_point[100] port_id[3]

Note the difference between vectors and arrays

RAM, ROM, and register-files used many times in digital systems Memory = array of registers in Verilog Word = an element of the array Examples:

Can be one or more bits

Note the difference (as in arrays):

reg membit[0:127]; reg [0:127] register;

reg membit[0:1023]; reg [7:0] membyte[0:1023]; membyte[511]

Similar to const in C Syntax:

But can be overridden for each module at compiletime

parameter <const_id>=<value>;

Gives flexibility

Example:

Allows to customize the module

parameter port_id=5; parameter cache_line_width=256; parameter bus_width=8; wire [bus_width-1:0] bus;

Strings are stored in reg variables. 8-bits required per character The string is stored from the least-significant part to the most-significant part of the reg variable Example:

reg [8*18:1] string_value; initial string_value = Hello World!; \n: newline %%: % \: \t: tab \\: \ \ooo: character number in octal

Escaped characters

Basic structure of a Verilog module:

module mymod(output1, output2, input1, input2); output output1; Verilog convention lists output [3:0] output2; outputs first input input1; input [2:0] input2; endmodule

Instances of

module mymod(y, a, b);

look like

mymod mm1(y1, a1, b1); // Connect-byposition mymod (y2, a1, b1), (y3, a2, b2); // Instance names omitted mymod mm2(.a(a2), .b(b2), .y(c2)); // Connect-byname

Você também pode gostar

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- Beginners Python Cheat Sheet PCC All PDFDocumento26 páginasBeginners Python Cheat Sheet PCC All PDFName100% (1)

- Protec SPD BrochureDocumento4 páginasProtec SPD BrochureCrestAinda não há avaliações

- 8085 microprocessor interview questionsDocumento1 página8085 microprocessor interview questionsgannoju423Ainda não há avaliações

- Selecting our Project TitleDocumento1 páginaSelecting our Project Titlegannoju423Ainda não há avaliações

- AZ-400 exam skills measuredDocumento14 páginasAZ-400 exam skills measuredgannoju423Ainda não há avaliações

- 24 C 64Documento24 páginas24 C 64Dau Le Doan BacAinda não há avaliações

- Unix Signal - Wikipedia, The Free Encyclopedia PDFDocumento8 páginasUnix Signal - Wikipedia, The Free Encyclopedia PDFgannoju423Ainda não há avaliações

- Biggest Countries: GermanyDocumento2 páginasBiggest Countries: Germanygannoju423Ainda não há avaliações

- Awesome Countries: AustraliaDocumento2 páginasAwesome Countries: Australiagannoju423Ainda não há avaliações

- C Library Function - Memmove : DescriptionDocumento1 páginaC Library Function - Memmove : Descriptiongannoju423Ainda não há avaliações

- DS1307 Real Time ClockDocumento14 páginasDS1307 Real Time Clockpraveen_kodgirwarAinda não há avaliações

- 89s51 DatasheetDocumento27 páginas89s51 DatasheetazizboysAinda não há avaliações

- 89s51 DatasheetDocumento27 páginas89s51 DatasheetazizboysAinda não há avaliações

- C Lecture NotesDocumento188 páginasC Lecture Notessurendraaalla0% (1)

- Gecassets - Co.in - 8085 Microprocessor - Ramesh GaonkarDocumento330 páginasGecassets - Co.in - 8085 Microprocessor - Ramesh Gaonkargannoju423Ainda não há avaliações

- Functions in CDocumento14 páginasFunctions in CPS RadhikaAinda não há avaliações

- C PointersDocumento7 páginasC PointersPrem AnanthAinda não há avaliações

- May 4, 2007 9:12 World Scientific Book - 9in X 6in Book-MainDocumento19 páginasMay 4, 2007 9:12 World Scientific Book - 9in X 6in Book-Maingannoju423Ainda não há avaliações

- Secrets of PrintfDocumento6 páginasSecrets of PrintfguzskaAinda não há avaliações

- Refer NceDocumento63 páginasRefer Ncegannoju423Ainda não há avaliações

- DFT 123Documento15 páginasDFT 123gannoju423Ainda não há avaliações

- LDPC EgDocumento21 páginasLDPC Eggannoju423Ainda não há avaliações

- Verilog ADocumento170 páginasVerilog Aaminkhan83Ainda não há avaliações

- OVM 2.0 Golden Reference Guide - 0Documento212 páginasOVM 2.0 Golden Reference Guide - 0rjohn1Ainda não há avaliações

- Array Mul 16bitDocumento6 páginasArray Mul 16bitgannoju423Ainda não há avaliações

- Viterbi FPGA implementation for UWB receiversDocumento19 páginasViterbi FPGA implementation for UWB receiversgannoju423Ainda não há avaliações

- VLSI, VLSI System & VLSI System DesignDocumento26 páginasVLSI, VLSI System & VLSI System Designrohit_sreerama4040Ainda não há avaliações

- Thesis On Fir FilterDocumento88 páginasThesis On Fir Filtergannoju42333% (3)

- Part I Multiple Choice QuestionsDocumento15 páginasPart I Multiple Choice Questionsgannoju423100% (1)

- Understanding DRAM Operation: Figure 1: IBM Trench Capacitor Memory CellDocumento10 páginasUnderstanding DRAM Operation: Figure 1: IBM Trench Capacitor Memory Cellgannoju423Ainda não há avaliações

- Comp Arch CH 03 L06 Array MultDocumento23 páginasComp Arch CH 03 L06 Array MultpreetamnAinda não há avaliações

- F5 TcpdumpDocumento14 páginasF5 TcpdumpNETRICH IT SolutionsAinda não há avaliações

- Army C-sUAS Systems AssessmentDocumento4 páginasArmy C-sUAS Systems AssessmentArthur WongAinda não há avaliações

- Calculation of Induction Motor Starting Parameters Using MatlabDocumento6 páginasCalculation of Induction Motor Starting Parameters Using MatlabДејан ПејовскиAinda não há avaliações

- Chasis+5Y18+-+FSCQ1265RT LA76933 LA78041 LA42352 BSC23-N0120+Hitachi+CDH-29GFS12 PDFDocumento45 páginasChasis+5Y18+-+FSCQ1265RT LA76933 LA78041 LA42352 BSC23-N0120+Hitachi+CDH-29GFS12 PDFdardoAinda não há avaliações

- Data Extraction From Planning Area To Backup Info CubeDocumento10 páginasData Extraction From Planning Area To Backup Info CubeHari KrishnaAinda não há avaliações

- Market Plan On Vodafone vs. Pakistani OperatorsDocumento47 páginasMarket Plan On Vodafone vs. Pakistani OperatorswebscanzAinda não há avaliações

- PRISM Proof Cloud Email ServicesDocumento11 páginasPRISM Proof Cloud Email ServiceshughpearseAinda não há avaliações

- Essays On AerodynamicsDocumento423 páginasEssays On AerodynamicsVyssion100% (1)

- EE331 Lab 1 v2Documento13 páginasEE331 Lab 1 v2Áo ĐenAinda não há avaliações

- Alejandrino, Michael S. Bsee-3ADocumento14 páginasAlejandrino, Michael S. Bsee-3AMichelle AlejandrinoAinda não há avaliações

- Kawasaki 4 Cylinder Hyperpack Installation ManualDocumento8 páginasKawasaki 4 Cylinder Hyperpack Installation ManualJuan Carlos RojasAinda não há avaliações

- Side Sealing Machine Operation GuideDocumento30 páginasSide Sealing Machine Operation GuideRocio GimenezAinda não há avaliações

- Rock Mechanics ASSGN 2Documento7 páginasRock Mechanics ASSGN 2ankeshAinda não há avaliações

- MMP - Intro To ElectronicDocumento12 páginasMMP - Intro To ElectronicAye Chan OoAinda não há avaliações

- PSR 640Documento188 páginasPSR 640fer_12_328307Ainda não há avaliações

- CatDocumento27 páginasCatGovarthanan GopalanAinda não há avaliações

- Group 6 - Chapter 1 RevisedDocumento15 páginasGroup 6 - Chapter 1 RevisedJAMES ELIJAH BALDERRAMAAinda não há avaliações

- Apps Associates - Introductory Profile GENDocumento15 páginasApps Associates - Introductory Profile GENRodrigo MarquesAinda não há avaliações

- Alert Operators Transmission - Aot: Customer Services DirectorateDocumento8 páginasAlert Operators Transmission - Aot: Customer Services DirectorateIbrahim KhalilAinda não há avaliações

- Rilem TC 162-TDF PDFDocumento17 páginasRilem TC 162-TDF PDFAref AbadelAinda não há avaliações

- 120FF51A Installation Guide For SAP Solutions PDFDocumento234 páginas120FF51A Installation Guide For SAP Solutions PDFNaqib Hassan100% (1)

- Hi Tech ApplicatorDocumento13 páginasHi Tech ApplicatorSantosh JayasavalAinda não há avaliações

- C# Abstract Classes and Interfaces ExplainedDocumento20 páginasC# Abstract Classes and Interfaces ExplainedshubhamAinda não há avaliações

- Process Control Valves TrainingDocumento12 páginasProcess Control Valves TrainingpptmnltAinda não há avaliações

- Dell Wireless Card Guide AddendumDocumento6 páginasDell Wireless Card Guide AddendumwazupecAinda não há avaliações

- OSCA Individual AssignmentDocumento33 páginasOSCA Individual AssignmentVincent LimAinda não há avaliações

- Aligning HR Interventions With Business StrategiesDocumento14 páginasAligning HR Interventions With Business StrategiesSunielAinda não há avaliações

- 6248 User Manual Sailor VHF DDocumento66 páginas6248 User Manual Sailor VHF DChristiano Engelbert SilvaAinda não há avaliações

- Steam Condensate Pot SizingDocumento1 páginaSteam Condensate Pot SizingSaeid Rahimi MofradAinda não há avaliações