Escolar Documentos

Profissional Documentos

Cultura Documentos

Eee 416 Lecture One Vlsi

Enviado por

Shafquat RahmanDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Eee 416 Lecture One Vlsi

Enviado por

Shafquat RahmanDireitos autorais:

Formatos disponíveis

Introduction to VLSI Design

EEE 416

Dr. Mohammad Al Hakim

Module Aims

Introduction to VLSI Technology

Process Design

Trends

Chip Fabrication

Real Circuit Parameters

Circuit Design

Electrical Characteristics

Configuration Building Blocks

Switching Circuitry

Translation onto Silicon

CAD

Practical Experience in Layout Design

Learning Outcomes

Understand the principles of the design and

implementation of standard MOS

integrated circuits and be able to assess

their performance taking into account the

effects of real circuit parameters

Laboratory

Microwind layout and simulation package

DSCH logic level simulator

Dedicated to training in sub-micron CMOS

VLSI design

Layout editor and electrical circuit extractor

Why VLSI?

Integration improves the design

Lower parasitics = higher speed

Lower power consumption

Physically smaller

Integration reduces manufacturing cost -

(almost) no manual assembly

Moores Law

Gordon Moore: co-founder of Intel

Predicted that the number of transistors

per chip would grow exponentially (double

every 18 months)

Exponential improvement in technology is a

natural trend:

e.g. Steam Engines - Dynamo - Automobile

What is a Silicon Chip?

A pattern of interconnected switches and gates on the surface of a

crystal of semiconductor (typically Si)

These switches and gates are made of

areas of n-type silicon

areas of p-type silicon

areas of insulator

lines of conductor (interconnects) joining areas together

Aluminium, Copper, Titanium, Molybdenum, polysilicon, tungsten

The geometryof these areas is known as the layout of the chip

Connections from the chip to the outside world are made around the

edge of the chip to facilitate connections to other devices

Semiconductors and Doping

Adding trace amounts of certain materials to semiconductors

alters the crystal structure and can change their electrical

properties

in particular it can change the number of free electrons or holes

N-Type

semiconductor has free electrons

dopant is (typically) phosphorus, arsenic, antimony

P-Type

semiconductor has free holes

dopant is (typically) boron, indium, gallium

Dopants are usually implanted into the semiconductor using

Implant Technology, followed by thermal process to diffuse the

dopants

Metal-oxide-semiconductor (MOS)

and related VLSI technology

pMOS

nMOS

CMOS

Basic MOS Transistors

Minimum line width

Transistor cross section

Charge inversion channel

Source connected to substrate

Enhancement vs Depletion mode devices

pMOS are 2.5 time slower than nMOS due

to electron and hole mobilities

Fabrication Technology

Silicon of extremely high purity

chemically purified then grown into large crystals

Wafers

crystals are sliced into wafers

wafer diameter is currently 150mm, 200mm, 300mm

wafer thickness <1mm

surface is polished to optical smoothness

Wafer is then ready for processing

Each wafer will yield many chips

chip die size varies from about 5mmx5mm to 15mmx15mm

A whole wafer is processed at a time

Fabrication Technology

Different parts of each die will be made P-

type or N-type (small amount of other

atoms intentionally introduced - doping -

implant)

Interconnections are made with metal

Insulation used is typically SiO2. SiN is also

used. New materials being investigated

(low-k dielectrics)

Typical fabrication centre

Different MOS architectures

Você também pode gostar

- Introduction To VLSI Design EEE 416: Dr. Mohammad Al HakimDocumento19 páginasIntroduction To VLSI Design EEE 416: Dr. Mohammad Al HakimFaisal HossainAinda não há avaliações

- Introduction To VLSI Design EEE 416: Dr. Mohammad Al HakimDocumento23 páginasIntroduction To VLSI Design EEE 416: Dr. Mohammad Al HakimMizanur Rahman SujanAinda não há avaliações

- Fabrikasi ICDocumento47 páginasFabrikasi ICNanamaliamAinda não há avaliações

- VLSI IntroductionDocumento23 páginasVLSI IntroductionSreenivasulu MamillaAinda não há avaliações

- Unit 1 MOS Fabrication TechnologyDocumento86 páginasUnit 1 MOS Fabrication TechnologyChinna ChowdaryAinda não há avaliações

- Introduction To MOS TechnologiesDocumento15 páginasIntroduction To MOS TechnologieslokeshwarrvrjcAinda não há avaliações

- Introduction To VLSI TechnologyDocumento19 páginasIntroduction To VLSI TechnologyVikas KumarAinda não há avaliações

- Strained Silicon TechnologyDocumento35 páginasStrained Silicon TechnologyTanzeem IqbalAinda não há avaliações

- Chapter 1 - Introduction To IC DesignDocumento40 páginasChapter 1 - Introduction To IC DesignnaztrexAinda não há avaliações

- Course Coordinator Module CoordinatorDocumento166 páginasCourse Coordinator Module CoordinatorBituAinda não há avaliações

- Class IDocumento12 páginasClass IChandru BadachiAinda não há avaliações

- Fundamentals of Modern VLSI Devices and FabricationDocumento12 páginasFundamentals of Modern VLSI Devices and FabricationChandru BadachiAinda não há avaliações

- Analog VLSI Design: Nguyen Cao QuiDocumento72 páginasAnalog VLSI Design: Nguyen Cao QuiKhuong LamborghiniAinda não há avaliações

- M1-01 CMOS Fabrication - LayoutDocumento27 páginasM1-01 CMOS Fabrication - LayoutAhmed ShafeekAinda não há avaliações

- VLSI Tech Intro 2024Documento89 páginasVLSI Tech Intro 2024Jossan EleazarEDENAinda não há avaliações

- IC Fabrication - An IntroductionDocumento37 páginasIC Fabrication - An IntroductionramkumarrajaAinda não há avaliações

- VLSI Design Interview QuestionsDocumento11 páginasVLSI Design Interview QuestionsRohit SomkuwarAinda não há avaliações

- VLSI Unit-1Documento49 páginasVLSI Unit-1sherkad dhanushAinda não há avaliações

- Dr. Öğr. Üyesi Itır KöymenDocumento8 páginasDr. Öğr. Üyesi Itır KöymengörkemAinda não há avaliações

- EE313 MOS Digital Integrated Circuit DesignDocumento30 páginasEE313 MOS Digital Integrated Circuit DesignFernando Sánchez HernándezAinda não há avaliações

- Ec3352 Vlsi and Chip DesignDocumento15 páginasEc3352 Vlsi and Chip DesignParanthaman GAinda não há avaliações

- Vlsi System DesignDocumento29 páginasVlsi System DesignAmar KumarAinda não há avaliações

- ICDocumento39 páginasICsetup.1430% (1)

- Lect 1Documento19 páginasLect 1nnehasinghAinda não há avaliações

- M1-01 CMOS Fabrication & LayoutDocumento26 páginasM1-01 CMOS Fabrication & LayoutMina WafikAinda não há avaliações

- Vlsi Lab Viva Questions and AnswersDocumento11 páginasVlsi Lab Viva Questions and AnswersNiranjan Mamadapur Assistant Professor - ECEAinda não há avaliações

- WINSEM2017-18 - ECE5023 - TH - TT531A - VL2017185001741 - Reference Material I - Radiation Effects On Semiconductor MemoriesDocumento72 páginasWINSEM2017-18 - ECE5023 - TH - TT531A - VL2017185001741 - Reference Material I - Radiation Effects On Semiconductor MemoriesAashishAinda não há avaliações

- Digital Systems and VLSI: Chapter # 01 Tahniyat AslamDocumento37 páginasDigital Systems and VLSI: Chapter # 01 Tahniyat AslamLal ChandAinda não há avaliações

- CMOS BasicsDocumento41 páginasCMOS BasicsYeshoda MallikarjunaAinda não há avaliações

- Microwave & MM Wave Planar Transmission Lines-III PDFDocumento125 páginasMicrowave & MM Wave Planar Transmission Lines-III PDFGhfrt JhuyAinda não há avaliações

- Lecture01 Ee474 IntroDocumento26 páginasLecture01 Ee474 Introaritrabhattacharyya52Ainda não há avaliações

- Silicon ManufacturingDocumento132 páginasSilicon ManufacturingAndrea SottocornolaAinda não há avaliações

- ASIC Back-End Design: by Bipeen Kiran KulkarniDocumento74 páginasASIC Back-End Design: by Bipeen Kiran KulkarniSuresh BharathAinda não há avaliações

- IC FabricationDocumento76 páginasIC FabricationRoshdy AbdelRassoulAinda não há avaliações

- VLSI Unit 2 Technology - SDocumento52 páginasVLSI Unit 2 Technology - SIndrajeet GautamAinda não há avaliações

- Topics in (Nano) Biotechnology: Microfabrication TechniquesDocumento111 páginasTopics in (Nano) Biotechnology: Microfabrication TechniquestprakashtceAinda não há avaliações

- Vlsi ch1Documento64 páginasVlsi ch1Nihar ranjan AditAinda não há avaliações

- UNIT-2 Stick Diagrams and LayoutDocumento54 páginasUNIT-2 Stick Diagrams and LayoutVenkateswara ReddyAinda não há avaliações

- The Nanofab Group: EE 4345 - Semiconductor Electronics Design Project - Spring 2002Documento24 páginasThe Nanofab Group: EE 4345 - Semiconductor Electronics Design Project - Spring 2002ShwethAinda não há avaliações

- Vlsi Design 17EC63: Chetan S, Dept of ECE, SJMIT, ChtradurgaDocumento226 páginasVlsi Design 17EC63: Chetan S, Dept of ECE, SJMIT, ChtradurgaShivaprasad B KAinda não há avaliações

- CMOS Process Flow: Institute of Radio Physics & Electronics University of CalcuttaDocumento28 páginasCMOS Process Flow: Institute of Radio Physics & Electronics University of CalcuttaSoumi RoyAinda não há avaliações

- VLSI Design For ManufacturabilityDocumento27 páginasVLSI Design For ManufacturabilityYing Huang100% (1)

- Mems, Piezoelectric Sensing & ActuationDocumento36 páginasMems, Piezoelectric Sensing & ActuationNagabhushanaAinda não há avaliações

- Lect 1 Intro - 2020Documento63 páginasLect 1 Intro - 2020ramchanduriAinda não há avaliações

- Unit 3Documento45 páginasUnit 3maha88eceAinda não há avaliações

- Advanced VLSI Design: Dr. Premananda B.SDocumento339 páginasAdvanced VLSI Design: Dr. Premananda B.SSmriti RaiAinda não há avaliações

- Integrated Circuit Fabrication Process Study Notes For ECEDocumento9 páginasIntegrated Circuit Fabrication Process Study Notes For ECEkrishnaav100% (1)

- Introduction To Integrated Circuit Fabrication (Baru)Documento49 páginasIntroduction To Integrated Circuit Fabrication (Baru)Stevie AdrielAinda não há avaliações

- ECE467: Introduction To VLSI: Physical Structure and Fabrication Process of Integrated CircuitsDocumento38 páginasECE467: Introduction To VLSI: Physical Structure and Fabrication Process of Integrated Circuitssnagaraj.cool7813Ainda não há avaliações

- Backend (Physical Design) Interview Questions and AnswersDocumento11 páginasBackend (Physical Design) Interview Questions and AnswersJanarthanan DevarajuluAinda não há avaliações

- Group 5Documento32 páginasGroup 5Gian BanaresAinda não há avaliações

- A Brief Introduction To MEMSDocumento21 páginasA Brief Introduction To MEMSM.S.SureshAinda não há avaliações

- Lect1 Chap1 2 IntroductionDocumento25 páginasLect1 Chap1 2 IntroductionVijay KanthAinda não há avaliações

- VLSI Lab Viva Questions and Answers 1Documento21 páginasVLSI Lab Viva Questions and Answers 1anand_duraiswamyAinda não há avaliações

- CSCE 613: Fundamentals of VLSI Chip Design: Instructor: Jason D. BakosDocumento26 páginasCSCE 613: Fundamentals of VLSI Chip Design: Instructor: Jason D. BakosbhawnaAinda não há avaliações

- M1-01 CMOS Fabrication & LayoutDocumento14 páginasM1-01 CMOS Fabrication & LayoutCyrille MagdiAinda não há avaliações

- EcmDocumento22 páginasEcmCarlos WilliamsonAinda não há avaliações

- L11a 4345 Sp02Documento24 páginasL11a 4345 Sp02Sanjay GargAinda não há avaliações

- Free DMAIC Checklist Template Excel DownloadDocumento5 páginasFree DMAIC Checklist Template Excel DownloadErik Leonel LucianoAinda não há avaliações

- Linic - by SlidesgoDocumento84 páginasLinic - by SlidesgoKhansa MutiaraHasnaAinda não há avaliações

- Eps 400 New Notes Dec 15-1Documento47 páginasEps 400 New Notes Dec 15-1BRIAN MWANGIAinda não há avaliações

- 27 Technip Energies - JD (PWD Students Only)Documento1 página27 Technip Energies - JD (PWD Students Only)0901EE201067 KUNAL JOLLY SAXENAAinda não há avaliações

- Intercostal Drainage and Its ManagementDocumento36 páginasIntercostal Drainage and Its ManagementAnusha Verghese67% (3)

- Myplan Assessment Skills Profiler Report Summary AnalysisDocumento5 páginasMyplan Assessment Skills Profiler Report Summary Analysisapi-338283524Ainda não há avaliações

- Rastriya Swayamsewak SanghDocumento60 páginasRastriya Swayamsewak SanghRangam Trivedi100% (3)

- YeastDocumento16 páginasYeastpippo pappi100% (1)

- Introduction To Hydraulic System in The Construction Machinery - Copy ALIDocumento2 páginasIntroduction To Hydraulic System in The Construction Machinery - Copy ALImahadAinda não há avaliações

- ADP ObservationDocumento15 páginasADP ObservationSanjay SAinda não há avaliações

- Infoblatt Skischulen Trends Port eDocumento18 páginasInfoblatt Skischulen Trends Port eAustrian National Tourism BoardAinda não há avaliações

- PE 12 Q3 WK1-2 Understanding On Health Related FitnessDocumento8 páginasPE 12 Q3 WK1-2 Understanding On Health Related FitnessEmarkzkie Mosra OrecrebAinda não há avaliações

- Instrumentation Design BasicsDocumento28 páginasInstrumentation Design BasicsCharles ChettiarAinda não há avaliações

- Moodle2Word Word Template: Startup Menu: Supported Question TypesDocumento6 páginasMoodle2Word Word Template: Startup Menu: Supported Question TypesinamAinda não há avaliações

- Industrial Marketing Module 2Documento32 páginasIndustrial Marketing Module 2Raj Prixit RathoreAinda não há avaliações

- GEODynamics CONNEX Brochure 2008.10 - Rev2 Final PDFDocumento12 páginasGEODynamics CONNEX Brochure 2008.10 - Rev2 Final PDFSusin LimAinda não há avaliações

- An1914 PDFDocumento56 páginasAn1914 PDFUpama Das100% (1)

- Minglana-Mitch-T-Answers in Long QuizDocumento9 páginasMinglana-Mitch-T-Answers in Long QuizMitch MinglanaAinda não há avaliações

- Vallen AE AccesoriesDocumento11 páginasVallen AE AccesoriesSebastian RozoAinda não há avaliações

- ICCM2014Documento28 páginasICCM2014chenlei07Ainda não há avaliações

- Clay & Shale Industries in OntarioDocumento193 páginasClay & Shale Industries in OntarioJohn JohnsonAinda não há avaliações

- Interdisciplinary Project 1Documento11 páginasInterdisciplinary Project 1api-424250570Ainda não há avaliações

- Annex A2 - CS Form 100 - Revised 2023 - CSESP - A1 - Edited - A1Documento2 páginasAnnex A2 - CS Form 100 - Revised 2023 - CSESP - A1 - Edited - A1obs.obando2022Ainda não há avaliações

- Light Design by Anil ValiaDocumento10 páginasLight Design by Anil ValiaMili Jain0% (1)

- Neoclassical CounterrevolutionDocumento1 páginaNeoclassical CounterrevolutionGraziella ValerioAinda não há avaliações

- Memo For Completed RubricDocumento3 páginasMemo For Completed Rubricnisev2003Ainda não há avaliações

- Umihara Et Al-2017-Chemistry - A European JournalDocumento3 páginasUmihara Et Al-2017-Chemistry - A European JournalNathalia MojicaAinda não há avaliações

- EtchDocumento2 páginasEtchlex bactolAinda não há avaliações

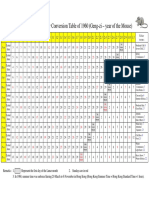

- Gregorian-Lunar Calendar Conversion Table of 1960 (Geng-Zi - Year of The Mouse)Documento1 páginaGregorian-Lunar Calendar Conversion Table of 1960 (Geng-Zi - Year of The Mouse)Anomali SahamAinda não há avaliações

- Good Data Won't Guarantee Good DecisionsDocumento3 páginasGood Data Won't Guarantee Good DecisionsAditya SharmaAinda não há avaliações