Escolar Documentos

Profissional Documentos

Cultura Documentos

Organizao e Arquiteturas de Computadores 2009 Cap 1 1234975555354535 1

Enviado por

luisgaunaDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Organizao e Arquiteturas de Computadores 2009 Cap 1 1234975555354535 1

Enviado por

luisgaunaDireitos autorais:

Formatos disponíveis

Janeiro de 2005

A MELHOR FACULDADE TECNOLGICA DE FORTALEZA.

Prof. Aristides

Janeiro de 2005

HARDWARE

(O Computador)

DADOS

(Informaes)

SOFTWARE

(Programas)

PESSOAS

(Usurios)

Evoluo dos Computadores;

Linguagem de Mquina;

Organizao Interna, Anlise de

Desempenho;

Organizao de Memria e Dispositivos de

Entrada e Sada.

Janeiro de 2008

BROOKSHEAR, J. Glenn. Cincia da Computao - Uma

Viso Abrangente. Porto Alegre: Bookman, 2000.

Organizao e Projeto de Computadores - A I nterface

Hardware/Software, J L Hennessy, D A Patterson;

Arquitetura e Organizao de Computadores, W Stallings,

trad da 5a. Ed, Pearson-Prentice Hall, 2002.

Bibliografia Complementar:

Bibliografia Bsica:

Capitulo 1:

Componentes do Computador.

1.1

Computador e o Processamento

da Informao.

A Informao

Estamos vivendo a Era da Informao.

Mas, afinal, o que INFORMAO?

Claude Shannon (autor de "The Mathematical Theory of

Communication") define que informao est presente sempre que

um sinal transmitido de um ponto a outro.

So informaes:

palavras,

um quadro (sinais visuais na forma de ondas de luz),

os impulsos eltricos atravs dos quais nossos olhos transmitem

imagens ao crebro, msica, etc.

Alm de transmitidas e recebidas, informaes podem ser

armazenadas e depois reproduzidas: em livros, em discos, em

fotografias, e na memria humana. Desta forma, uma informao

original pode ser reproduzida (transmitida muitas vezes).

Processamento da informao - refere-se ao armazenamento,

transmisso, combinao e comparao da informao.

Alguns agentes contriburam de forma expressiva para estarmos

hoje vivendo a Era da Informao.

A escrita iniciou este processo, a imprensa foi um passo muito

importante, e recentemente as telecomunicaes difundem

informao instantnea por todo o planeta.

O mais recente dos agentes fundamentais que propiciaram esta

onda de informaes tambm o mesmo agente da tecnologia

que mais nos auxilia a lidar com ela, um agente que nos permite

armazenar, classificar, comparar, combinar e exibir informaes

acuradamente e com velocidade: este agente tecnolgico o

COMPUTADOR.

1.1.1 Sistema Binrio e Hexadecimais

Reviso.

Nmero

Coisa banal que usamos no nosso dia-a-dia.

O que nmero?

Bem, pode ser dito que um smbolo que

representa uma coleo de objetos iguais.

Seja, por exemplo, o objeto representado por .

Assim a coleo seria representada por 3

, a coleo por 5 , etc.

Simples no?

Existem duas maneiras de representar uma informao:

analogicamente

digitalmente.

1 1 1 1 0 0

Os smbolos elementares so os dgitos ou algarismos e

a quantidade deles a base do sistema de numerao.

Portanto, um sistema de numerao permite

representar qualquer coleo com uma quantidade

finita de smbolos elementares.

E o nosso sistema de uso corrente o decimal por ter a

base 10.

Mas podemos ter sistemas de qualquer base, desde que

maior que 1.

Janeiro de 2005

A - COLEO B - DECIMAL C - OCTAL D - HEXADECIMAL E - BINRIO

0 0 0 0

* 1 1 1 1

** 2 2 2 10

*** 3 3 3 11

**** 4 4 4 100

***** 5 5 5 101

****** 6 6 6 110

******* 7 7 7 111

******** 8 10 8 1000

********* 9 11 9 1001

********** 10 12 A 1010

*********** 11 13 B 1011

************ 12 14 C 1100

************* 13 15 D 1101

************** 14 16 E 1110

*************** 15 17 F 1111

**************** 16 20 10 10000

***************** 17 21 11 10001

****************** 18 22 12 10010

A designao de decimal para este sistema numrico,

advm de usar a base 10 e usa os algarismos:

0, 1, 2, 3, 4, 5, 6, 7, 8, 9.

4631

1 x 10

0

=

1

3 x 10

1

=

30

6 x 10

2

= 600

4 x 10

3

=

4000

Resultado = 4631

Sistema numrico decimal

Como o prprio nome diz, um sistema binrio

contm apenas dois elementos ou estados.

Num sistema numrico isto expresso como uma

base dois, usando os dgitos 0 e 1.

Esses dois dgitos tm o mesmo valor bsico de 0 e 1

do sistema numrico decimal.

Sistema numrico binrio:

Devido a sua simplicidade, microprocessadores usam o

sistema binrio de numerao para manipular dados;

Dados binrios so representados por dgitos binrios

chamados "bits;

O termo "bit" derivado da contrao de "binary

digit". Microprocessadores operam com grupos de

"bits" os quais so chamados de palavras;

O nmero binrio 1 1 1 0 1 1 0 1 contm oito "bits".

10011011

1 x 2

0

= 1

1 x 2

1

= 2

0 x 2

2

= 0

1 x 2

3

= 8

1 x 2

4

= 16

0 x 2

5

= 0

0 x 2

6

= 0

1 x 2

7

= 128

Resultado = 155

10111 = 1 x 2

4

+ 0 x 2

3

+ 1 x 2

2

+ 1 x 2

1

+ 1 x 2

0

= 23

Palavras binrias recebem nomes especiais conforme a

quantidade de bits utilizada pelas mesmas:

Nibble = 4 bits (2

4

= 16 variaes);

Byte = 8 bits (2

8

= 256 variaes);

Word = 16 bits (2

16

= 65.536 variaes);

Double Word = 32 bits (2

32

= 4.294.967.296 variaes);

Quad Word = 64 bits (2

64

= 18.446.744.073.709.600.000

variaes).

Janeiro de 2005

Sufixo Quantidade

Kilo (K) 2

10

= 1.024

Mega (M) 2

20

= 1.048.576

Giga (G) 2

30

= 1.073.741.824

Tera (T) 2

40

= 1.099.511.627.776

Peta (P) 2

50

= 1.125.899.906.843.624

Exa (E) 2

60

= 1.152.921.504.607.870.976

Zeta (Z) 2

70

= 1.180.591.620.718.458.879.424

Yotta (Y) 2

80

= 1.208.925.819.615.701.892.530.176

O sufixo K (kilo), que, em decimal, representa 1.000 vezes como

em Km e Kg), em binrio representa 2

10

vezes (1.024). Logo, 1

Kbyte representa 1.024 bytes, 2 Kbytes = 2.048 bytes.

Sistema numrico hexadecimal

Desde os primeiros microprocessadores, as palavras

binrias de dados manipuladas por eles eram mltiplos

de nibble. Com isso uma outra base numrica passou a

ser amplamente utilizada, a base 16 (hexadecimal).

0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F.

As letras A, B, C, D, E e F correspondem respectivamente

aos decimais 10, 11, 12, 13, 14 e 15.

Geralmente, os nmeros hexadecimais so escritos com

um prefixo $ ou 0x, ou com o sufixo h, para

realar o sistema numrico que estamos a utilizar.

Assim, o nmero hexadecimal A37E, pode ainda ser mais

corretamente escrito como $A37E, 0xA37E ou A37Eh.

0000 = 0

0001 = 1

0010 = 2

0011 = 3

0100 = 4

0101 = 5

0110 = 6

0111 = 7

1000 = 8

1001 = 9

1010 = A

1011 = B

1100 = C

1101 = D

1110 = E

1111 = F

$A37E = 1010001101111110

A 3 7 E

14 x 16

0

= 14

10 x 16

3

= 40960

3 x 16

2

= 768

7 x 16

1

= 112

Resultado = 41854

Binrio 1 1 1 1 1 0 1 0 1 0 1

Operao 1x2

10

+1x2

9

+1x2

8

+1x2

7

+1x2

6

+0x2

5

+1x2

4

+0x2

3

+1x2

2

+0x2

1

+1x2

0

Decimal 1024 +512 + 256 +128 + 64 + 0 + 16 + 0 + 4 + 0 + 1 = 2005

Octal 3 7 2 5

Operao 3x8

3

+ 7x8

2

+ 2x8

1

+ 5x8

0

Decimal 1536 + 448 + 16 + 5 = 2005

Decimal 2 0 0 5

Operao 2x10

3

+ 0x10

2

+ 0x10

1

+ 5x10

0

Decimal 2000 + 0 + 0 + 5 = 2005

Hexadecimal 7 D 5

Operao 7x16

2

+ 13x16

1

+ 5x16

0

Decimal 1792 + 208 + 5 = 2005

O Nmero 2005 em:

Binrio

Octal

Hexadecimal

1.2

A Evoluo dos Computadores

baco

A primeira calculadora que se tem

notcias o baco, de origem chinesa, do

sculo V a.C. capaz de efetuar operaes

algbricas elementares.

Calculadoras mecnicas

Anteriormente dcada de 40 j

existiam calculadoras mecnicas,

dentre elas, pode se destacar: a

calculadora de Charles Babbage

Atribui-se a Blaise Pascal (1623-1662) a

construo da primeira calculadora

mecnica capaz de fazer somas e

subtraes.

A primeira mquina de verdade foi construda

por Wilhelm Schickard (1592-1635);

somar, subtrair, multiplicar e dividir;

perdida durante a guerra dos trinta anos;

Durante muitos anos nada se soube sobre essa

mquina, por isso, atribua-se a Blaise Pascal

(1623-1662) a construo da primeira mquina

calculadora, que fazia apenas somas e

subtraes.

Em 1801, Joseph Marie Jacquard inventou um

tear mecnico dotado de uma leitora de cartes

perfurados, os quais representavam os desenhos

do tecido;

portanto um processador das informaes

relativas padronagem do tecido;

o tear funcionava to bem que este o primeiro

exemplo prtico de desemprego provocado pela

automao.

TEAR PROGRAMVEL

Charles Babbage (1792-1871) concebeu um

Computador Analtico dotado de um dispositivo

a que chamou de MOINHO (uma mquina de

somar com preciso de at 50 casas decimais), e

um dispositivo de entrada (inspirado no tear de

Jacquard) que leria cartes perfurados contendo

no somente nmeros (os dados) mas tambm

INSTRUES (o que fazer com os dados).

Imaginou ainda um dispositivo de memria que

chamou de ARMAZM para guardar os

nmeros, um banco com 1000 "registradores"

cada qual capaz de armazenar um nmero de 50

dgitos.

Finalmente, incluiu um dispositivo impressor

para dar sada aos resultados.

As instrues (gravadas em cartes) possveis de ser

implementadas pelo moinho eram:

entrar com um nmero no armazm

entrar com um nmero no moinho

mover um nmero do moinho para o armazm

mover um nmero do armazm para o moinho

comandar o moinho para executar uma operao

sair com um resultado.

Para construir um dispositivo a partir destas idias, Babbage

contou com a colaborao inestimvel da matemtica Ada Augusta

Byron, Lady Lovelace, filha do poeta Lord Byron. Ada

desenvolveu sries de instrues para o calculador analtico,

criando conceitos tais como sub-rotinas, loops e saltos

condicionais.

Babbage considerado o precursor do computador. Ada

considerada a precursora do software.

Herman Hollerith (1860-1929) tambm

inspirou-se nos cartes de Jacquard para criar

uma mquina para acumular e classificar

informaes - a Tabuladora de Censo.

Aplicao: processamento dos dados do censo.

1941- Konrad Zuse (Alemanha)

Primeiro computador digital,

automtico, programvel, de

propsito geral, completamente

funcional (eletromecnico).

John V. Atanasoff / Clifford Berry (EUA)

Primeiro prottipo de calculador eletrnico que funcionou nos

EUA.

Construdo entre 1937 e 1942 na Univ. do Estado de at Iowa.

John V. Atanasoff Clifford Berry

ABC Computer

(Atanasoff-Berry Computer)

Colossus, desenvolvido na Inglaterra no perodo de

1939 a 1943 com a inteno de quebrar o cdigo da

mquina de criptografia alem denominada

Enigma, que gerava seqncias aleatrias com

perodo de 1019 caracteres.

Deste projeto, tomou parte Alan Turing. Aps a

guerra, esse projeto foi descontinuado, mas

permaneceu secreto at 1973.

1944 - Howard Aiken (Universidade de Harvard - EUA)

Primeiro computador eletromecnico automtico de grande

porte.

Howard Hathaway Aiken

Na dcada de 40 surgiram

as primeiras vlvulas

eletrnicas;

Cada vlvula era capaz de

representar um bit de

informao;

Os bytes eram compostos

por oito vlvulas.

Primeira gerao ENIAC (Eletronic Numerical Integrator

and Computer), projetado durante a Segunda Grande Guerra

com a finalidade de calcular tiros de artilharia. Quando ele ficou

pronto, em 1946, a guerra j havia acabado. Seu peso era de 30 t,

consumia 140 kW e tinha 19.000 vlvulas.

Primeiro computador eletrnico digital de grande porte.

John Mauchly e J. Presper Eckert.

Mauchley e Eckert - ENIAC 1946:

18mil vlvulas, 1500 rels e 6mil chaves;

Marco da histria do computador moderno;

Fundaram uma empresa (hoje, Unisys).

Para 2 KB de memria seriam necessrias 16.384 vlvulas

e para trs circuitos 16.384 x 3 = 49.152 vlvulas.

Como no se tinha muita

confiana nos resultados,

devido constante queima

de vlvulas, cada clculo era

efetuado por trs circuitos

diferentes e os resultados

comparados.

Comemora-se na Universidade

da Pensylvania os cinqenta

anos do ENIAC, e para tal foi

montado o ENIAC num chip,

com as mesmas funes do

original.

CHIP ENIAC desenvolvido para as comemoraes dos 50

anos do ENIAC

Surgem os grandes computadores e, por detrs deles, as

grandes empresas: IBM, Bourroughs, NCR, etc..

a era de mquinas grandes, acessadas por uma

multido de terminais burros.

Chegou-se a prever que no mundo haveria cinco

grandes computadores, um para cada continente.

Era a viso de homens simples perante mquinas

maravilhosas e as vezes fatais, como conta Arthur Clark

em "2001.

A seguir veremos quatro marcos interessantes sobre esse

passado.

O termo bug, que sempre foi usado pelos engenheiros para

indicar pequenas falhas em suas mquinas. Em 1947, os

engenheiros que trabalhavam com o Harvard Mark I encontraram

uma traa entre seus circuitos, prenderam-na no livro de registro e

rotularam-na como o primeiro bug encontrado.

O primeiro "bug",

1947

O computador IAS, de 1952, que foi construdo segundo orientao

de von Newmann e muito influenciou o projeto do IBM 701, o

primeiro computador eletrnico comercializado pela IBM.

Computador IAS,

1952.

Janeiro de 2005

O UNIVAC, projetado pelos idealizadores do ENIAC.

Modelo do UNIVAC, 1954

PDP-8, primeiro computador com preo acessvel, tendo sido uma

mquina da srie PDP onde Ken Thompson e Dennis Ritchie

desenvolveram o UNIX.

Incio do domnio da IBM

Minicomputador PDP-8, 1965

Barramento nico

Surgimento dos minicomputadores

Segunda Gerao

Foi em 1947 que surgiu o primeiro transistor,

produzido pela Bell Telephone Laboratories;

Os transistores eram e so muito mais confiveis que as

vlvulas;

So feitos de cristal de silcio, o elemento mais

abundante na Terra;

Em 1954 a Texas I nstruments iniciou a produo

comercial de transistores;

Da mesma forma os transistores, nos

circuitos digitais foram utilizados para

representar os dois estados:

ligado/desligado, ou seja, zero/um;

Nos anos 60 e 70 devido ao emprego do

transistor nos circuitos, se deu a

exploso, o boom do uso de

computadores. Ocupavam menos

espao e tinham um custo satisfatrio.

Primeiro projeto de

transistor

Em 1968 chegou o primeiro computador da

UNICAMP, um IBM 1130, com 16KB de memria e

um disco de 1 MB, foi um acontecimento, ele

trabalhava com cartes perfurados. Rodava programas

em ASSEMBLER, Fortran, e PL1;

Para dar partida, se utilizava da console e cartes

perfurados especialmente codificados, denominados

cold start , funes executadas hoje pela ROM e o

BIOS.

Terceira gerao

Nos anos 60, iniciou-se o

encapsulamento de mais de um

transistor num mesmo receptculo,

surgiu assim o Circuito Integrado -

CI, os primeiros contavam com

cerca de 8 a 10 transistores por

capsula ( chip ).

Em novembro de 1971, a Intel introduziu o primeiro

microprocessador comercial, o 4004, inventado por trs

engenheiros da Intel. Primitivo aos padres de hoje, ele

continha somente 2.300 transistores e executava cerca de

60.000 clculos por segundo. Nos dias de hoje, vinte e sete

anos depois, um microprocessador o produto mais

complexo produzido em massa, com mais de 5.5 milhes

de transistores, executando centenas de milhes de

clculos por segundo.

Quarta gerao

J na rea dos microcomputadores, perguntamo-nos: qual foi o

primeiro ? Em 1975 a Revista Popular Electronics apresentou o

projeto e anunciou a venda do kit do primeiro microcomputador.

Era o Altair 8800, baseado no microprocessador 8008 da Intel. Foi

para esse microcomputador que a dupla Paul Allen e Bill Gates

vendeu um de seus primeiros produtos: um interpretador Basic.

O Altair 8800 aberto.

Integrao de Circuitos em Escala muito Alta (1980 - ?)

Circuitos integrados VLSI;

Milhes de transistores em um nico chip;

Surgimento dos microcomputadores;

Apple e Apple II Machintosh;

IBM PC;

Incio da computao pessoal.

Quinta Gerao

Ainda em estudo, poder utilizar Biochips.

Os computadores sero ento capazes de entender a linguagem

natural do homem, e a Inteligncia Artificial ser a fonte de

diversos avanos.

Janeiro de 2005

Quadro Comparativo de Caractersticas de microprocessadores

Microprocessador Data de

Lanamento

Palavra de

Dados

Endereamento Mximo

de MP

Intel 4004 1971 4 1 K Bytes

Intel 8080 1973 8 64 K Bytes

Intel 8088 1980 16 1 K Bytes

Intel 80286 1982 16 16 M Bytes

Intel 80386 1985 32 4 G Bytes

Intel 80486 1989 32 4 G Bytes

Intel Pentium 1993 32 4 G Bytes

Motorola MC 6800 1974 8 64K Bytes

MC 68000 1979 32 16 M bytes

MC 68010 1983 32 16 M Bytes

MC 68020 1984 32 4 G Bytes

MC 60030 1987 32 4G bytes

MC 68040 1989 32 4 G bytes

Zilog Z80 1974 8 64 K bytes

Zilog Z80 1979 16 1M Bytes

Leitura Recomendada:

Tanembaum Captulo 1;

Stallings Captulo 1 e 2;

Henessy e Patterson Captulo 1.

1.3

Modelo Hipottico de um

Computador.

MODELO HIPOTTICO DE UM COMPUTADOR

Operador - s faz o que for ordenado, no toma

decises;

Conjunto de escaninhos - com capacidade para um

carto cada;

Mquina de calcular - executa as operaes;

Caixa de entrada - para receber cartes de fora;

Mquina de escrever - para dar sada s informaes

/ resultados.

Para que este modelo funcione, deve existir em cada carto

uma INSTRUO. O operador segue de escaninho em

escaninho, fazendo exatamente o que est escrito em cada

carto, at encontrar um carto contendo uma instruo

que manda que ele PARE.

Conjunto de escaninhos

Caixa de entrada

Mquina de calcular

Mquina de escrever

EXERCCIO 1:

Obs.: Utilizaremos a notao (E10) significando "o contedo do escaninho

E10", isto , o valor que est agora armazenado no escaninho E10 (ou, mais

formalmente, o valor corrente daquela posio de memria).

E1 : armazene o valor 1 no E10

E2 : leia o contedo de E11 (externo - a caixa de entrada)

E3 : multiplique E10 com E11 (usando a mquina de calcular) e armazene o

resultado em E10

E4 : subtraia o valor 1 de E11

E5 : se o valor de E11 > 0, volte para E3, seno continue

E6 : imprima o contedo de E10 (usando a mquina de escrever)

E7 : PARE

E8 :

E9:

A partir de um sinal externo do tipo COMECE, este modelo inicia do E1 da

por diante prossegue at E8 (o final).

Resolva o exerccio; o que faz este algortmo?

ALGORITMO E10 E11 AO

E1- armazene o valor 1 no E10 1 - -

E2 - leia (E11) (caixa de entrada - p.ex: 4) - 4 -

E3 - (E10) x (E11); armazene resultado em E10 4 - -

E4 : subtraia o valor 1 de (E11) - 3 -

E5 : se (E11) > 0, volte para E3, seno continue - - Volta p/E3

E3 12 - -

E4 - 2 -

E5 - - Volta p/E3

E3 24 - -

E4 - 1 -

E5 - - Volta p/E3

E3 24 - -

E4 - 0 -

E5 - - Segue p/E6

E6 : imprima o contedo de E10 - - Imprime 24

E7 : PARE - - PARA

Este programa calcula o FATORIAL de um nmero.

EXERCCIO 2:

No mesmo algoritmo acima, avalie as conseqncias das seguintes

alteraes:

a) E5 : se o valor de E11 > 0, volte para E3,

b) E5 : se o valor de E11 >= 0, volte para E3; seno continue,

c) E7 : XXX

-----------------------------------------------------------------------------------

Num modelo real - o COMPUTADOR- s faz aquilo que ele

recebe instruo para realizar.

Um computador funciona a partir de um programa que o instrui

sobre o que deve fazer.

"O problema dos computadores que eles fazem exatamente

aquilo que voc os instruiu a fazer e no aquilo que voc

realmente queria que eles fizessem."

Um programador frustrado.

Resposta - Exerccio 2:

a) E5 : se o valor de E11 > 0, volte para E3, (eliminar "seno continue"), o

modelo no saberia o que fazer quando o valor de E11 chegasse a zero.

b) E5 : se o valor de E11 >= 0, volte para E3,

Haveria mais um passo no loop, multiplicando o contedo de E10 por 0 (zero) e o

resultado do processamento do algortmo seria SEMPRE ZERO.

c) E7 : XXX

Quando o modelo chegasse at E7, poderia encontrar qualquer coisa. No caso de

encontrar cdigo vlido (por exemplo, o "lixo" deixado por um programa

anterior) com algum significado, ele executaria a instruo (fosse esta o que quer

que fosse), chegando a um resultado imprevisvel (poderia dar um resultado

errado, poderia travar, poderia entrar em um loop, etc.).

Caso o contedo de E8 fosse um valor sem significado (por exemplo, um dado), o

modelo no saberia o que fazer e pararia.

Portanto, num modelo real - o COMPUTADOR- s faz aquilo que ele recebe

instruo para realizar. Um computador funciona a partir de um programa que

o instrui sobre o que deve fazer.

PROGRAMA uma seqncia de instrues (no modelo

hipottico, os cartes);

O programa deve ser escrito numa LINGUAGEM DE

PROGRAMAO - as linguagens naturais tm ambigidades e

podem dar margem a diferentes interpretaes;

HARDWARE (significa originalmente "ferragens, em ingls -

hardware store significa originalmente "loja de ferragens") o

conjunto de dispositivos fsicos do computador, o equipamento;

SOFTWARE (em analogia a hardware, a parte "soft", macia, so os

programas que permitem que o equipamento saiba o que realizar,

que ele funcione;

Depois surgiram outros termos, aproveitando as mesmas analogias,

tais como firmware (indicando programao gravada em

dispositivos fsicos e no modificvel pelo usurio);

PROCESSAMENTO AUTOMTICO DE DADOS:

Um computador capaz de executar um programa sozinho, desde

que o programa seja previamente armazenado nele, de forma que

ele tenha as indicaes de onde procurar as instrues.

MEMRIA (os escaninhos) - Dispositivo fsico para armazenar

programas e dados;

PROCESSADOR (operador e mquina de calcular) - Dispositivo

que realiza o processamento;

DISPOSITIVOS DE ENTRADA E SADA (caixa de entrada,

caixa de sada, mquina de escrever) - Formas de comunicao

entre o usurio e o computador;

SISTEMA - Um conjunto interligado de programas (e,

eventualmente, tambm de equipamentos);

LINGUAGEM DE MQUINA - a linguagem que o computador

entende, cujo "alfabeto" composto apenas de "1's" e "0's"

(linguagem binria);

LINGUAGEM DE PROGRAMAO - uma linguagem formal,

utilizando termos que se aproximam da linguagem humana, que

pode ser traduzida por programas especiais em linguagem de

mquina.

1.4.

Componentes do Computador

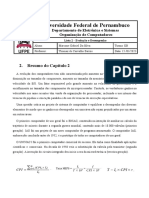

A arquitetura bsica de um computador moderno segue ainda de

forma geral os conceitos estabelecidos pelo Professor da

Universidade de Princeton, John Von Neumann (1903-1957), um

dos construtores do EDVAC.

Von Neumann props construir computadores que:

1. Codificassem instrues que pudessem ser armazenadas na

memria e sugeriu que usassem cadeias de uns e zeros (binrio)

para codific-los;

2. Armazenassem na memria as instrues e todas as

informaes que fossem necessrias para a execuo da tarefa

desejada;

3. Ao processarem o programa, as instrues fossem buscadas

diretamente na memria.

Este o conceito de PROGRAMA ARMAZENADO.

MEMORIA

PRINCIPAL

DISPOSITIVOS

DE ENTRADA

E SAIDA

UC

DMA deixa a UCP disponvel para

outro processamento em paralelo.

UCP

ULA

Troca de informaes (dados ou instrues) fluxo bidirecional.

Sinais de controle fluxo unidirecional.

Diagrama em bloco de um computador

Toda a lgica dos computadores construda a partir de chaves

liga / desliga.

Inicialmente foram usados chaves mecnicas, depois rels

eletro-mecnicos - o Z-1 construdo por Konrad Zuse em 1941 e

o MARK 1 de Howard Aiken em 1944 (capazes de executar at

5 chaveamentos por segundo).

Posteriormente, foram substitudos pelas vlvulas no ENIAC

em 1946 (capazes de 100.000 de chaveamentos por segundo), e

finalmente pelos transistores (semicondutores) inventados em

Stanford em 1947.

Os circuitos integrados (ou CI's) so encapsulamentos

compactos (LSI - Large Scale I ntegration e VLSI - Very Large

Scale I ntegration) de circuitos constitudos de minsculos

transistores.

Comentario:

UNIDADE CENTRAL DE PROCESSAMENTO (UCP):

A Unidade Central de Processamento a responsvel pelo

processamento e execuo de programas armazenados na MP.

Funes:

Executar instrues - realizar aquilo que a instruo determina.

Realizar o controle das operaes no computador.

Formada de duas unidades:

Unidade Lgica e Aritmtica (ULA) - responsvel pela realizao

das operaes lgicas (E, OU, etc) e aritmticas (somar, etc);

Unidade de Controle (UC) - envia sinais de controle para toda a

mquina, de forma que todos os circuitos e dispositivos

funcionem adequada e sincronizadamente.

Representao grfica da UCP com seus quatro componentes

principais destacados. A unidade de entrada e sada formada, nesta

representao, pelos registradores REM e RDM e por suas ligaes

com os demais elementos (logo veremos as funes de cada um

deles).

MEMRIA PRINCIPAL (MP):

A Memria Principal tem por finalidade armazenar toda

a informao que manipulada pelo computador -

programas e dados.

Para que um programa possa ser manipulado pela

mquina, ele primeiro precisa estar armazenado na

memria principal.

OBS.: os circuitos da Memria Principal no so

combinatoriais, eles tem capacidade de armazenar bits.

Os circuitos usados so do tipo "flip-flop", conforme

veremos em Circuitos Lgicos.

DISPOSITIVOS DE ENTRADA E SADA (E/S):

Tem por finalidade permitir a comunicao entre o

usurio e o computador.

OBS.: Para executar um programa, bastaria UCP e MP;

no entanto, sem os dispositivos de E/S no haveria a

comunicao entre o usurio e o computador.

PROCESSAMENTO AUTOMTICO DE DADOS:

O programas so armazenados na MP e a UCP capaz

de executar um processamento inteiro sem a interveno

do usurio, mesmo que haja vrios desvios no programa.

PASSOS:

armazenar o programa na MP;

indicar UCP onde o programa est armazenado.

Estas operaes so realizadas pelo

SISTEMA OPERACIONAL:

Aplicativo A Aplicativo B Aplicativo C

Drivers de Dispositivos

HARDWARE

Gerenciamento

de Processos

E/S

Arquivos

Gerenciamento

de Memoria

E/S

Dispositivos

Sistema Operacional d suporte aos aplicativos.

(Sustenta o ambiente no qual os aplicativos so executados).

1.5

Memria

Memria

Local onde os dados e os programas so armazenados (na forma

de bits) para imediata execuo (memria Principal - MP) ou

para uso posterior (memria secundria - MS);

A memria dividida em pequenas reas, chamadas endereos;

Armazenar consiste em guardar uma informao (ou um

conjunto de informaes) na memria e a operao

denominada escrita ou gravao ( write);

Recuperar uma informao (ou um conjunto de informaes) da

memria copi-la para uma outra posio na memria ou para

outro componente do sistema. Esta operao denominada

leitura (read).

No sistema de computador existe uma variedade grande de tipos de

memria, cada uma com sua finalidade e caracterstica especificas,

mas que interligam e se integram para o funcionamento do sistema.

Registradores

Cache

Principal

Secundria

Custo alto

Velocidade alta

Baixa capacidade

Custo baixo

Velocidade baixa

Alta capacidade

Pirmide Hierrquica de tipos de memria

Discos

Fitas

Os registradores so unidades de memria que

armazenam, temporariamente, na UCP, os dados a

serem manipulados por uma instruo ou seus

resultados parciais ou finais de um processamento;

Sendo um resultado parcial, armazenado em um

registrador, este ser transferido para a memria

principal (externa UCP).

Registradores

voltil - perde o contedo armazenado quando no energizada.

(RAM Random Access Memory).

Tipos de RAM

a) Esttica - a gravao estvel, s se alterando atravs de

operaes de escrita (consome mais energia);

b) Dinmica - a gravao do bit "1" se descarrega com o tempo,

precisando ser "refrescada" periodicamente (ciclo de refresh).

Memria Principal

A memria principal formada por dois tipos:

RAM (Randomic Acess Memory)

ROM (Read Only Memory)

Tipos de Memria

FPM x EDO x SDRAM

no voltil - no perde o contedo armazenado. (ROM, PROM,

EPROM, EEPROM)

c) ROM - Read Only Memory (gravada de fbrica - permanente);

d) PROM - Programable ROM (pode ser gravada uma nica vez

pelo usurio, atravs de equipamentos especiais);

e) EPROM - Erasable PROM (pode ser apagada atravs de raios

ultravioletas);

f) EEPROM - Electrical EPROM (pode ser apagada atravs de

sinais eltricos);

g) Memria Flash - uma memria que pode ser utilizada como

apenas de leitura ou como de leitura e gravao, dependendo do

driver utilizado. Geralmente utilizada como um disco em

pastilhas (chips), SSD - Solid State Disk.

ROM - Read Only Memory

Quando ligamos um microcomputador, podemos ver que sempre

executado o teste e a contagem de memria;

Este programa pode ser armazenado em ROM, que uma

memria de apenas leitura onde os dados no so apagados

quando desligamos a alimentao;

O programa armazenado em ROM, recebe o nome de firmware

que um programa inaltervel e que ser sempre executado.

Na ROM do microcomputador h basicamente trs

firmwares:

1. BIOS (Basic I nput/Output System) ensina o processador a

trabalhar com os perifricos mais bsicos do sistema, como ckt

de apoio, unidade de disquete e o vdeo em modo texto;

2. POST (Power-On Self-Test Autoteste ao Ligar) sempre que o

micro ligado o POST executa as seguintes rotinas:

Identifica a configurao instalada;

Inicializa os chipset da placa me;

Inicializa o vdeo;

Testa a memria;

Testa o teclado;

Carrega o sistema operacional para a memria;

Entrega o controle do microprocessador ao sistema

operacional.

3. Setup programa de configurao de hardware do

microcomputador.

Atualmente h duas tecnologias bsicas para construo

de circuitos de memria ROM:

Mask ROM programada de fbrica e no h

como reprograma-la, a no ser trocando o chip.

usada at o lanamento das primeiras placa-me

soquete 7;

Flash ROM tecnologia mais moderna que permite

reprogramao atravs de firmware. upgrade de

BIOS.

A memria secundria , tambm chamada

de auxiliar ou memria de massa, tem a

finalidade de armazenar de forma

permanente as informaes (dados e

programas) necessrios ao processamento.

A memria secundria eletromecnica e

por esta razo, seu tempo de acesso

relativamente alto, se comparado com outros

tipos de memria.

Memria Secundria

Uso da Memria.

O 8088 s podia enxergar 1 MB de memria que

dividida em reas menores de 64KB. 64KB x 16 =

1 MB.

Por motivos de compatibilidade, os micros atuais

mantm a mesma estrutura dos micros antigos no

primeiro megabyte de memria. Essa rea

dividida da seguinte forma:

rea de Memria Endereos Contedo

0 a 640 KB

00000h a 9FFFFh

Banco 0 ao banco 9

Memria convencional

640 a 704 KB A0000h a AFFFFh Banco 10: Mem. De vdeo

704 a 768 KB B0000h a BFFFFh Banco 11: Mem. De vdeo

768 a 832 KB C0000h a CFFFFh Banco 12: ROM da interface de

vdeo

832 a 896 KB D0000h a DFFFFh Banco 13: Firmware de interfaces

896 a 960 KB E0000h a EFFFFh Banco 14: Firmware de interfaces

960 a 1.024 KB F0000h a FFFFFh Banco 15: BIOS (e Basic residente,

caso haja)

Durante a execuo de uma instruo, a UCP realiza

um ou mais acessos memria principal, para

buscar a instruo e transferi-la a um dos

registradores, a fim de transferir os dados para a

ULA (Unidade Lgica e Aritmtica) ou para

armazenar o resultado de operao que se encontra

em um registrador;

A CACHE uma memria construda com

tecnologia similar da UCP, consequentemente, com

velocidade de transferncia compatvel, reduzindo

consideravelmente o tempo de espera da UCP por

instrues e dados.

Memria Cache

Tecnologia de Memria para Vdeo

O controlador de vdeo l o contedo da memria de vdeo

(presente na placa de vdeo), convertendo os dados armazenados

em sinais que sejam compreensveis pelo monitor.

Novas tecnologias relacionadas a memria de vdeo, surgiram afim

de aumentar o desempenho de interface de vdeo.

Para armazenar a imagem a ser exibida no vdeo, a placa utiliza-se

de um tipo especial de memria, chamada de memria de vdeo.

O contedo desta memria constantemente atualizado pela placa

de vdeo, seguindo as ordens transmitidas pelo processador.

Barramento PCI

Controlador

de vdeo

Memria

de vdeo

Funcionamento da placa de vdeo

Arquitetura Unificada de Memria (UMA Unified Memory

Architeture)

A interface de vdeo utiliza parte da memria RAM do micro, com

a finalidade de baratear o micro e aumentar o desempenho do

vdeo.

Depende do chipset da placa-me e geralmente onboard.

Em alguns casos o controlador de vdeo est dentro do processador

diminui custos. Ex.: Cyrix MediaGX;

Em outros, o processador de vdeo est integrado no chipset. SIS

5598 (TX PRO II).

Tipos de memrias de vdeo

As placas de vdeo utilizam memria RAM para

armazenar as imagens que sero mostradas no monitor.

Apesar de poderem usar memrias FPM, EDO ou

SDRAM comuns, o uso de memrias otimizadas para

vdeo, aumenta bastante sua performance.

Os principais tipos de memria de vdeo usados

atualmente so o VRAM, SGRAM e WRAM.

VRAM (Vdeo RAM)

A VRAM um tipo de memria especialmente desenvolvido para

o uso em placas de vdeo. Sua principal vantagem que pode ser

acessada simultaneamente por dois componentes. Isso permite

que a placa de vdeo use os dados contidos na VRAM para

atualizar a exibio das imagens, ao mesmo tempo que o

processador inclui novos dados.

O uso de memrias VRAM aumenta perceptivelmente o

desempenho da placa, o problema que este tipo de memria

bem mais caro que as memrias convencionais, fazendo com que

muitos fabricantes optem por utilizar memrias EDO comuns em

seus modelos de placas de vdeo mais baratas.

Barramento PCI

Controlador

de vdeo

Memria VRAM

Funcionamento de uma placa de vdeo com VRAM

WRAM (Windows RAM)

Como o nome sugere, a Windows RAM um tipo de

memria de vdeo otimizada para sistemas grficos como

o Windows.

Aperfeioamento sobre a VRAM criado pela Samsung,

que possui um desempenho cerca de 50% superior

(segundo a Samsung).

Apesar da melhora no desempenho, a WRAM mais

barata que as memrias VRAM comuns, tendo obtido

uma enorme aceitao no mercado.

Memria Rambus (RDRAM)

Criada pela empresa Rambus;

A memria conectada ao controlador de vdeo atravs de um

barramento estreito, porm rpido (Rambus);

Este barramento de 8 bits, consegue transmitir dois bytes por

pulso de clock: um na ativao do clock e outro na desativao;

O clock totalmente independente do barramento PCI e tem

freqncia de 250 MHz;

Segundo a empresa, essa tecnologia dez vezes mais rpida que as

memrias tradicionais de vdeo e de trs a cinco vezes mais rpida

que a VRAM.

Barramento PCI

Barramento RAMBUS

Controlador

de vdeo

Memria

de vdeo

Funcionamento de uma placa de vdeo Rambus.

SGRAM (Synchronous Graphic Ramdom Access Memory)

A SGRAM um tipo de memria SDRAM otimizada para o uso

em placas de vdeo, que apesar de possuir apenas uma entrada de

dados, pode ser dividida em duas pginas de memria. Como

ambas as pginas podem ser acessadas ao mesmo tempo,

simulamos uma dupla entrada de dados.

Atualmente as memrias SGRAM vm sendo cada vez mais usadas

em placas de vdeo de baixo e mdio desempenho, pois apesar do

desempenho levemente inferior s memrias VRAM so muito

mais baratas, sendo substitutas ideais para as memrias EDO.

1.5.1

Memria Principal

Memria Principal a parte do computador onde programas e

dados so armazenados para processamento;

A informao permanece na memria principal apenas

enquanto for necessrio para seu emprego pela UCP, sendo

ento a rea de MP ocupada pela informao pode ser liberada

para ser posteriormente sobregravada por outra informao;

Quem controla a utilizao da memria principal o Sistema

Operacional.

Estrutura da Memria Principal - CLULAS E ENDEREOS

A memria precisa ter uma organizao que permita ao

computador guardar e recuperar informaes quando necessrio.

Portanto, no basta transferir informaes para a memria.

preciso ter como encontrar essa informao mais tarde, quando

ela for necessria, e para isso preciso haver um mecanismo que

registre exatamente onde a informao foi.

Clula a unidade de armazenamento do computador. A memria

principal organizada em clulas. Clula a menor unidade da

memria que pode ser endereada e tem um tamanho fixo (para

cada mquina). As memrias so compostas de um determinado

nmero de clulas ou posies. Cada clula composta de um

determinado nmero de bits. Todas as clulas de um dado

computador tem o mesmo tamanho, isto , todas as clulas daquele

computador tero o mesmo nmero de bits.

Cada clula identificada por um endereo nico.

As clulas so numeradas seqencialmente, uma a uma, de 0 a

(N-1), chamado o endereo da clula.

Endereo o localizador da clula, que permite identificar

univocamente uma clula. Assim, cada clula pode ser

identificada pelo seu endereo.

Unidade de transferncia a quantidade de bits que

transferida da memria em uma nica operao de leitura ou

transferida para a memria em uma nica operao de escrita.

O tamanho da clula poderia ser igual ao da palavra, e tambm

unidade de transferncia, porm por razes tcnicas e de custo,

so freqentemente diferentes.

Palavra a unidade de processamento da UCP. Uma palavra

deve representar um dado ou uma instruo, que poderia ser

processada, armazenada ou transferida em uma nica operao.

Janeiro de 2005

Acesso - ao de armazenar ou recuperar uma

informao em uma memria;

No end. 5h temos o armazenamento

de um dado de 8 bits

Numa memria de 1 MB, tem

1 M endereos que armazenam

1 byte cada.

Como 1 M = 1.048.576 teremos

essa quantidade de endereos

Para armazenarmos um dado

De 8 bits em cada um.

Nmero de bits para representar um

endereo:

Expresso geral MP com endereos de

0 a (N-1):

N = 2

x

logo:

x = log

2

N

0

1

2

3

N-1

N

d

e

e

n

d

e

r

e

o

s

Estrutura da MP

sendo x = n de bits para representar um

endereo e N o nmero de endereos.

CAPACIDADE DA MEMRIA PRINCIPAL

A capacidade da MP em bits igual ao produto

do n de clulas pelo total de bits por clula.

T = N x M

T = capacidade da memria em bits

N = n de endereos (N=2x sendo x = n de bits do endereo)

M = n de bits de cada clula

10111101

10110101

10110001

10110111

1.6

Unidade Central de Processamento

A Unidade Central de Processamento - UCP (em ingls, Central

Processing Unity - CPU) a responsvel pelo processamento e

execuo dos programas armazenados na MP.

As funes da UCP so: executar as instrues e controlar as

operaes no computador.

A UCP composta de duas partes:

UAL - Unidade Aritmtica e Lgica - tem por funo a efetiva

execuo das instrues

ACC

REGs

Unidade de

Controle

ULA

Barramento Interno

Diagrama Esquemtico da ULA

Barramento de Controle

UC - Unidade de Controle - tem por funes a busca, interpretao e

controle de execuo das instrues, e o controle dos demais

componentes do computador

ACC

REGs

UC

ULA

CLOCK

RDM

REM

CI

RI

DECODER

INST.

Memria

Principal

Unidade Lgica e Aritmtica

Diagrama Funcional da UCP

Unidade de Controle

Barramento de Dados

Barramento de Endereos

B

a

r

r

a

m

e

n

t

o

I

n

t

e

r

n

o

Registradores Importantes na UCP

Na UC - CI - Contador de Instrues (em ingls: PC - Program

Counter) - armazena o endereo da prxima instruo a ser

executada - tem sempre o mesmo tamanho do REM.

Na UC - RI - Registrador de Instruo (em ingls: IR -

I nstruction Register) - armazena a instruo a ser executada.

Na ULA - ACC Acumulador (em ingls:ACC - Accumulator) -

armazena os dados (de entrada e resultados) para as operaes

na ULA; o acumulador um dos principais elementos que

definem o tamanho da palavra do computador - o tamanho da

palavra igual ao tamanho do acumulador.

Instrues

Para que um programa possa ser executado por um computador,

ele precisa ser constitudo de uma srie de instrues de mquina e

estar armazenado em clulas sucessivas na memria principal;

A UCP responsvel pela execuo das instrues que esto na

memria;

Quem executa um programa o hardware;

Programa em linguagem de mquina (uma seqncia de

instrues de mquina em cdigo binrio);

A linguagem de mquina composta de cdigos binrios,

representando instrues, endereos e dados e est totalmente

vinculada ao conjunto ("set") de instrues da mquina.

O programa elaborado pelo programador (o cdigo-fonte,

composto de instrues complexas) precisa ser "traduzido" em

pequenas operaes elementares executveis pelo hardware.

Cada uma das instrues tem um cdigo binrio associado, que o

cdigo da operao.

Formato geral de uma Instruo

Cdigo de operao (OPCODE) Operando (s) (OP)

OPCODE - identifica a operao a ser realizada pelo processador.

o campo da instruo cuja valor binrio identifica a operao a ser

realizada. Este cdigo a entrada no decodificador de instrues na

unidade de controle.

OP - ou so o(s) campo(s) da instruo cujo valor binrio sinaliza a

localizao do dado (ou o prprio dado) que ser manipulado

(processado) pela instruo durante a operao. Em geral, um

operando identifica o endereo de memria onde est contido o dado

que ser manipulado, ou pode conter o endereo onde o resultado da

operao ser armazenado. Finalmente, um operando pode tambm

indicar um Registrador (que conter o dado propriamente dito ou

um endereo de memria onde est armazenado o dado). Os

operandos fornecem os dados da instruo.

Obs: Existem instrues que no tem operando. Ex.: Instruo

HALT (PARE).

Conjunto de Instrues

Quando se projeta um hardware, define-se o seu conjunto ("set") de

instrues - o conjunto de instrues elementares que o hardware

capaz de executar. O projeto de um processador centrado no seu

conjunto ("set") de instrues. Quanto menor e mais simples for este

conjunto de instrues, mais rpido pode ser o ciclo de tempo do

processador.

Um processador precisa possuir instrues para:

operaes matemticas:

1. aritmticas: +, - , , ...;

2. lgicas: and, or, xor, ...;

3. de complemento;

4. de deslocamento.

operaes de movimentao de dados:

(memria <--> UCP, reg <--> reg);

operaes de entrada e sada (R/W em dispositivos de E/S);

operaes de controle (desvio de seqncia de execuo, parada).

As estratgias de implementao de processadores so:

CISC - Complex I nstruction Set Computer

Exemplo: PC, Macintosh; um conjunto de instrues maior e mais

complexo, implicando num processador mais complexo, com ciclo

de processamento mais lento; ou

RISC - Reduced I nstruction Set Computer

Exemplo: Power PC, Alpha, Sparc; um conjunto de instrues

menor e mais simples, implicando num processador mais simples,

com ciclo de processamento rpido.

Obs.: adotaremos o termo instruo para as instrues de mquina

ou em linguagem Assembly e comando para linguagens de alto nvel.

O projeto de um processador poderia ser resumido em:

a) Definir o conjunto de instrues (todas as possveis instrues que

o processador poder executar):

definir formato e tamanho das instrues;

definir as operaes elementares.

b) Projetar os componentes do processador (UAL, UC, registradores,

barramentos, ...)

Duas estratgias so possveis na construo do decodificador de

instrues da UC:

wired logic - as instrues so todas implementadas em

circuito);

Microcdigo - apenas um grupo bsico de instrues so

implementadas em circuitos; as demais so montadas atravs

de microprogramas que usam as instrues bsicas.

Ciclo de Instrues

As instrues so executadas

sequencialmente uma a uma. (a no ser

pela ocorrncia de um desvio).

O CI indica a seqncia de execuo, isto ,

o CI controla o fluxo de execuo das

instrues.

Descrio do processamento de uma

instruo na UCP:

a UC l o endereo da prxima instruo

no CI;

a UC transfere o endereo da prxima

instruo, atravs do barramento

interno, para o REM.

INICIO

TRMIO

Buscar prxima

Instruo

Interpretar a

Instruo

Buscar os Dados

Executar a

Instruo

Ciclo de Instrues

COMUNICAO ENTRE MEMRIA PRINCIPAL E UCP

BARRAMENTOS

Os componentes dos computadores se comunicam atravs de

barramentos;

Barramento um conjunto de condutores eltricos que

interligam os componentes do computador e de circuitos

eletrnicos que controlam o fluxo dos bits;

Para um dado ser transportado de um componente a outro,

preciso emitir os sinais de controle necessrios para o

componente-origem colocar o dado no barramento e para o

componente-destino ler o dado do barramento. Como um dado

composto por bits (geralmente um ou mais bytes) o

barramento dever ter tantas linhas condutoras quanto forem

os bits a serem transportados de cada vez.

REGISTRADORES UTILIZADOS

A comunicao entre MP e UCP usa dois registradores da UCP:

Registrador de Endereos de Memria - REM ou, em ingls,

Memory Address Register (MAR);

Registrador de Dados da Memria - RDM ou, em ingls, Memory

Buffer Register (MBR).

Barramentos UCP / MP:

Barramento de endereos unidirecional (s a UCP envia dados

- write - ou l dados - read - da MP);

Barramento de dados bidirecional;

Barramento de controle bidirecional:

UCP ---> MP (controles ... - r/w)

MP -----> UCP (wait ... )

PALAVRA (UNIDADE DE INFORMAO)

Palavra a unidade de informao do sistema UCP / MP.

A conceituao mais usada (IBM, Digital) define palavra como

sendo a capacidade de manipulao de bits do ncleo do

computador (UCP e MP).

Pressupe-se aqui que todos os elementos do ncleo do computador

(o que inclui o tamanho da UAL, do acumulador e registradores

gerais da UCP e o barramento de dados) tenham a mesma largura

(processem simultaneamente o mesmo nmero de bits), o que nem

sempre acontece. Muitas vezes encontram-se computadores em que

o tamanho da UAL e do acumulador (e registradores gerais) no o

mesmo tamanho dos barramentos. Desta forma, encontram-se

especificaes de "computadores de 64 bits" mesmo quando seu

barramento de dados de 32 bits, nesse caso referindo-se

exclusivamente capacidade de manipulao da UCP de 64 bits

(isto , sua UAL e acumulador tem 64 bits).

TEMPO DE ACESSO

Tempo de acesso - tempo decorrido entre uma requisio de leitura

de uma posio de memria e o instante em que a informao

requerida est disponvel para utilizao pela UCP.

As memrias DRAM (Dynamic RAM ) - tempo de acesso - 60 ns.

Tempo de ciclo - tempo decorrido entre dois ciclos sucessivos de

acesso memria. As memrias dinmicas perdem seu contedo em

alguns instantes e dependem de ser periodicamente atualizadas

(refresh). No caso das SRAM (Static RAM ou memrias estticas),

que no dependem de "refresh", o tempo de ciclo igual ao tempo de

acesso. As memrias dinmicas, no entanto, requerem ciclos

peridicos de "refresh", o que faz com que a memria fique

indisponvel para novas transferncias, a intervalos regulares

necessrios para os ciclos de "refresh". Assim, as memrias DRAM

tem ciclo de memria maior que o tempo de acesso.

ACESSO MEMRIA PRINCIPAL

O acesso MP ALEATRIO, portanto qualquer que seja o

endereo (a posio) de memria que se queira acessar, o tempo de

acesso o mesmo (constante).

A MP pode ser acessada atravs de duas operaes:

1 - LEITURA: LER da MEMRIA

Significa requisitar MP o contedo de uma determinada clula

(recuperar uma informao). Esta operao de recuperao da

informao armazenada na MP consiste na transferncia de um

conjunto de bits (cpia) da MP para a UCP e no destrutiva,

isto , o contedo da clula no alterado.

SENTIDO: da MP para a UCP

PASSOS EXECUTADOS PELO HARDWARE:

1. a UCP armazena no REM o endereo onde a informao

requerida est armazenada;

2. a UCP comanda uma leitura;

3. o contedo da posio identificada pelo endereo contido no

REM transferido para o RDM e fica disponvel para a UCP.

2 - ESCRITA: ESCREVER na MEMRIA

Significa escrever uma informao em uma clula da MP

(armazenar uma informao). Esta operao de

armazenamento da informao na MP consiste na transferncia

de um conjunto de bits da UCP para a MP e destrutiva (isto

significa que qualquer informao que estiver gravada naquela

clula ser sobregravada).

SENTIDO: da UCP para a MP

PASSOS EXECUTADOS PELO HARDWARE:

1. a UCP armazena no REM o endereo de memria da

informao a ser gravada e no RDM a prpria informao;

2. a UCP comanda uma operao de escrita;

3. a informao armazenada no RDM transferida para a posio

de memria cujo endereo est contido no REM.

SINCRONIZAO DE OPERAO DO SISTEMA

Imagine um barco a remo em uma competio, em que

a plena velocidade e direo somente atingida porque

todos os remadores fazem seus movimentos de forma

coordenada, regidos por um "patro" - geralmente o

timoneiro que indica o ritmo das remadas.

As diversas partes de um computador comportam-se

aproximadamente desta forma: instrues e dados,

aps sofrerem algum processamento em um

determinado componente, devem trafegar para o

prximo estgio de processamento (atravs de

condutores - um barramento ou um cabo), de forma a

estarem l a tempo de serem processados.

SINCRONIZAO DE OPERAO DO SISTEMA

O computador envia a todos os seus componentes um

sinal eltrico regular - o pulso de "clock" que

fornece uma referncia de tempo para todas as

atividades e permite o sincronismo das operaes

internas.

O pulso de clock indica que um ciclo (um "estado")

terminou, significando que o processamento deste

ciclo est terminado e um outro ciclo se inicia,

determinando a alguns circuitos que iniciem a

transferncia dos dados nele contidos (abrindo a porta

lgica para os prximos estgios) e a outros que

recebam os dados e executem seu processamento.

Clock

O clock um pulso alternado de sinais de tenso alta

("high") e baixa ("low"), gerado pelos circuitos de relgio

(composto de um cristal oscilador e circuitos auxiliares).

O clock o sinal de controle no barramento, mais

importante, pois um sinal de sincronismo.

o clock que determina o momento exato para troca de

informaes entre os circuitos.

Todos os processadores a partir do 486DX2 possuem

multiplicao de clock.

Perodo

1 0

Conforme vimos ao analisar a comunicao entre UCP e

memria, as instrues, os dados e os endereos

"trafegam" no computador atravs dos barramentos (de

dados, de endereos e de controle), sob a forma de bits

representados por sinais eltricos.

Periodicamente, uma nova configurao de bits

colocada nos circuitos, e tudo isso s faz sentido se

pudermos de alguma forma organizar e sincronizar essas

variaes, de forma a que, num dado instante, os diversos

circuitos do computador possam "congelar" uma

configurao de bits e process-las.

Para isso, preciso que exista um outro elemento, que

fornece uma base de tempo para que os circuitos e os

sinais se sincronizem. Este circuito chamado clock - o

relgio interno do computador. Cada um dos estados

diferentes que os circuitos assumem, limitados pelo sinal

do clock, chamado um ciclo de operao.

O clock um pulso alternado de sinais de tenso, gerado

pelos circuitos de relgio (composto de um cristal

oscilador e circuitos auxiliares).

Ciclo de Operao

Cada um do intervalos regulares de tempo delimitado pelo incio

da descida do sinal, equivalendo um ciclo excurso do sinal por

um "low"e um "high" do pulso.

O tempo do ciclo equivale ao perodo da oscilao.

Perodo o inverso da freqncia. Ou seja,

P = 1 / f.

A freqncia f do clock medida em hertz. Inversamente, a durao

de cada ciclo chamada de perodo, definido por P=1/f (o perodo

o inverso da freqncia).

Por exemplo:

se f = 10 hz logo P = 1/10 = 0,1 s.

1 Mhz (1 megahertz) equivale a um milho de ciclos por segundo.

Sendo a freqncia de um processador medida em megahertz, o

perodo ser ento medido em nanosegundos, como vemos no

exemplo abaixo:

f = 10 Mhz = 10 x 10

6

hz

P = 1 / 10

6

= 0,000001s = 100 nanosegundos.

Quando se diz que um processador de 200 Mhz, est-se definindo

a freqncia de operao de seu processador (seu clock),

significando que o processador pode alternar seus estados internos

166 milhes de vezes por segundo.

Isto acarreta que cada ciclo de operao dura:

1 / 200.000.000 s = 0,000000005s = 5 x 10-9 s

ou seja,

5 nanosegundos.

Como podemos ver pelo exemplo a seguir, o processador

com o clock ilustrado em (B) teria um tempo de ciclo

cinco vezes menor que o (A) e portanto teria

(teoricamente) condies de fazer cinco vezes mais

operaes no mesmo tempo.

http://venus.rdc.puc-rio.br/rmano/comp0clk.html.

Bibliografia:

Você também pode gostar

- Como Fazer Uma BainhaDocumento28 páginasComo Fazer Uma BainhaluisgaunaAinda não há avaliações

- Tipos de telhas e suas especificações para coberturasDocumento3 páginasTipos de telhas e suas especificações para coberturasluisgaunaAinda não há avaliações

- Arquitetura de ComputadoresDocumento29 páginasArquitetura de Computadorescabral feraAinda não há avaliações

- Apostila Conceitos Básicos de InformáticaDocumento21 páginasApostila Conceitos Básicos de InformáticaExcelly100% (14)

- N$C3$B3s Podemos$2C Sim$21Documento89 páginasN$C3$B3s Podemos$2C Sim$21luisgaunaAinda não há avaliações

- Apostila Sistema OperacionalDocumento61 páginasApostila Sistema OperacionalluisgaunaAinda não há avaliações

- Apostila Do Curso de Elaboração de ProjetosDocumento31 páginasApostila Do Curso de Elaboração de ProjetosIvan MasafretAinda não há avaliações

- Apostila de Administracao de Banco de DadosDocumento103 páginasApostila de Administracao de Banco de Dadosnana2103Ainda não há avaliações

- 32-Lesoes Trau - Col.CervDocumento9 páginas32-Lesoes Trau - Col.CervHeline CoelhoAinda não há avaliações

- Leitura Cronologica Da BibliaDocumento3 páginasLeitura Cronologica Da BiblialuisgaunaAinda não há avaliações

- Estudo 197Documento2 páginasEstudo 197luisgaunaAinda não há avaliações

- 01 Doutrina Crista de Deus CPDocumento44 páginas01 Doutrina Crista de Deus CPRonaldo TamaniniAinda não há avaliações

- Lab Aoc PC1Documento20 páginasLab Aoc PC1Lucas Prado de OliveiraAinda não há avaliações

- Arquitetura e Organização de ComputadoresDocumento16 páginasArquitetura e Organização de ComputadoresJoveniAlvesAinda não há avaliações

- Arquitetura ComputadoresDocumento27 páginasArquitetura ComputadoresFilipe HiluyAinda não há avaliações

- Apol 1 Logica de Programação-UninterDocumento7 páginasApol 1 Logica de Programação-UninterLeandro LopesAinda não há avaliações

- Microprocessadores e Computadores PessoaisDocumento3 páginasMicroprocessadores e Computadores PessoaisAntonio milton MugabeAinda não há avaliações

- Questionário Unidade Ii - ..Documento6 páginasQuestionário Unidade Ii - ..Abílio José Gomes FerreiraAinda não há avaliações

- Lista 2 - Marcone Gabriel Da SilvaDocumento5 páginasLista 2 - Marcone Gabriel Da SilvaMARCONE GABRIEL DA SILVAAinda não há avaliações

- SAP 1 (Final)Documento23 páginasSAP 1 (Final)Rafael OliveiraAinda não há avaliações

- Capitulos 567Documento24 páginasCapitulos 567thiagojapurAinda não há avaliações

- História do Computador emDocumento119 páginasHistória do Computador emMarcos De Campos MaiaAinda não há avaliações

- Analista de Sistema OperacionalDocumento276 páginasAnalista de Sistema Operacionalcavaco511Ainda não há avaliações

- Av1 - Arquitetura - Computadores - Ara0039 - 3001 - SoluçãoDocumento2 páginasAv1 - Arquitetura - Computadores - Ara0039 - 3001 - SoluçãoCê Tá DoidoAinda não há avaliações

- Códigos de Falha para Diagnóstico PDFDocumento137 páginasCódigos de Falha para Diagnóstico PDFScribdTranslations100% (1)

- 12 HardwareDocumento31 páginas12 Hardwarenoisdigital00Ainda não há avaliações

- Unidade 1 - Aula 5 e 6Documento8 páginasUnidade 1 - Aula 5 e 6Lee Marcos Cruz de SouzaAinda não há avaliações

- Prova Discursiva Arquiterura de Computadores UninterDocumento3 páginasProva Discursiva Arquiterura de Computadores UninterDimas GuerreiroAinda não há avaliações

- AE2 - Atividade de Estudo 2Documento3 páginasAE2 - Atividade de Estudo 2Bruno AlexAinda não há avaliações

- Modelo de Von Neumann PDFDocumento9 páginasModelo de Von Neumann PDFPetronio PadilhaAinda não há avaliações

- Exercicio Arquitetura de ComputadoresDocumento3 páginasExercicio Arquitetura de Computadorestbsss100% (1)

- Manual Automatismo 1 Folha e Contralador 14 04 14 PDFDocumento61 páginasManual Automatismo 1 Folha e Contralador 14 04 14 PDFPaulo Roberto de Souza100% (3)

- Simulado 1Documento5 páginasSimulado 1kin013Ainda não há avaliações

- Bloco2 Analise e Desenvolvimento de Sistemas - Completo - Av1, Av2, Av4 PDFDocumento35 páginasBloco2 Analise e Desenvolvimento de Sistemas - Completo - Av1, Av2, Av4 PDFJonathan DominguesAinda não há avaliações

- Aula 2 Organizac3a7c3a3o de ComputadoresDocumento29 páginasAula 2 Organizac3a7c3a3o de ComputadoresLuís GonçalvesAinda não há avaliações

- Organização de computadoresDocumento31 páginasOrganização de computadorescorreiogutaAinda não há avaliações

- Trena DigitalDocumento5 páginasTrena DigitalAlex SouzaAinda não há avaliações

- Informatica Basica - ResumoDocumento50 páginasInformatica Basica - ResumoJosefo SadiaAinda não há avaliações

- AOC - Parte 04 - Processadores - Marcos MendesDocumento60 páginasAOC - Parte 04 - Processadores - Marcos MendesFlexin 333Ainda não há avaliações

- Algoritmos e ProgramaçãoDocumento149 páginasAlgoritmos e ProgramaçãoBruno Alonso PachecoAinda não há avaliações

- Organização de Computadores - Simulado - Aula7Documento4 páginasOrganização de Computadores - Simulado - Aula7ddrum21100% (1)

- Organização de HardwareDocumento31 páginasOrganização de HardwareNayara HiranoAinda não há avaliações