Escolar Documentos

Profissional Documentos

Cultura Documentos

CS 06 (Conversores 2)

Enviado por

someone that you used to know0%(1)0% acharam este documento útil (1 voto)

37 visualizações22 páginasTítulo original

CS 06(Conversores 2).ppt

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

PPT, PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PPT, PDF, TXT ou leia online no Scribd

0%(1)0% acharam este documento útil (1 voto)

37 visualizações22 páginasCS 06 (Conversores 2)

Enviado por

someone that you used to knowDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PPT, PDF, TXT ou leia online no Scribd

Você está na página 1de 22

Convertidor digital/analgico en Escalera R- 2R

El convertidor utiliza resistores de 2 valores solamente

R y 2R, el sistema se puede ampliar para acomodar un

nmero arbitrario de bits. El nmero de resistores es el

doble para el mismo nmero de bits de entrada, que el

sistema de resistores ponderados. El Convertidor de re

sistores ponderados asigna pesos a los bits de entrada

utilizando resistores apropiadamente ponderados.

En el convert. D/A, R-2R, los bits estn ponderados

mediante la provisin de caminos para la divisin de

Corriente con las correspondientes atenuaciones suce

sivas para los bits menos significativos. Si las resis-

tncias son idnticas, la salida es independiente de

de valores. a

3

es el dgito de mayor peso

R R R R

2R 2R 2R 2R 2R

2R

V

0

V

ref

a

3

a

2

a

1

a

0

-

+

Ejercicio: Determinar la salida del DAC anterior, si

se el Vref= (-5v) y la R=12.5 k y los switchs apli-

lican una secuencia de 4 bits como se aprecia en los

diagramas siguientes:

0 1 2 3 4 6 5 7 8 9 10 11 12 13 14 15

a

0

a

1

a

2

a

3

Anlisis del circuito anterior:

I

T

=(-Vref/2R)=(-5v/25k)= -0.2mA,I

3

= (-I

T

/2)= -0.1 mA

I

2

= -0.1mA/2)= -0.05mA, I

1

=(- 0.05/2)= - 0.025 mA,

I

0

=(-0.025/2)= - 0,0125 mA, y hallando el voltaje de salida

para cada caso particular, tenemos:

V

00

= - (- 0.0125 x 25k) = 0.3125 v

V

01

= -(-0.025 x 25k)= 0.625 v

V

02

= -(-0.05 x 25k)= 1.25 v

V

03

= - (-0.1 x 2R)= 0.1 x 25k =2.5 v

Grfica de Vo(conversin de digital a

analgico)

.

V

fs

=4.6875. v

1LSB= (1/2

n

)= (1/16)=0.0625

N de pasos =2

n

-1

0.3125

0.6250

0.9375

1.2500

1.5625

1.8750

2.1875

2.5000

2.8125

3.1250

3.4375

3.7500

4.0625

4.3750

4.6875

0

0

0

0

0

0

0

1

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

0

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

1

precisin = 3.125%=(1LSB/2)

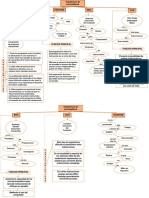

Conversor analgico a digital (ADC)

Un convertidor analgico digital tiene por finalidad

convertir un conjunto de niveles analgicos a un

conjunto de cdigos binarios correspondientes.

Tipos de convertidores analgicos Digitales

El convertidor paralelo o flash, es el mas rpido de

los diversos tipos de ADC; funciona mediante un

comparador para cada posible nivel de entrada codifi

cando la salida adecuadamente en binario.

Cuando la seal de entrada es menor que la seal de

referencia, la salida del comparador est en 0 logi

co. Cuando la seal de entrada es mas grande que la

de referencia, la salida est en 1 lgico. Un ADC

tipo paralelo de n bits de salida requiere de 2n-1

comparadores; por lo tanto si se tiene la ventaja de

su mayor velocidad, tiene el inconveniente que al

aumentar el nmero de bits se aumenta tambin el

nmero de comparadores.

El tiempo de conversin es fijo, los nicos retardos

Son las producidas por los comparadores y puertas.

El tiempo de conversin es del orden de los 10nseg.

El ADC (flash converter)

.

7

6

5

4

3

2

1

0

+

-

+

-

+

-

+

-

+

-

+

-

+

-

R

R

R R

R

R

R

R

EN

Do

D1

D2

salida

binaria

parlela

Codificador

de prioridad

Impulsos de

muestreo

Comparadores

+ V

REF

Entrada

analgica

ADC DE ESCALERA O RAMPA (COUNTER

RAMP)

El mtodo de rampa digital para la conversin A/D

se conoce tambin como mtodo de rampa en escale

ra o mtodo contador, se emplea un DAC y un conta-

dor binario para generar el valor digital de una entra-

da analgica. En la prxima diapositiva se presenta

El diagrama de un ADC de rampa digital.

Supongamos que el contador se inicializa en el esta-

do de reset y la salida del DAC es 0, a continua

cin suponemos que se aplica a la entrada una ten-

sion analgica, cuando se sobrepasa la tensin de

referencia(salida del DAC), el comparador conmuta

su salida a nivel alto y activa la puerta AND. Los im

pulsos de reloj hacen que el contador avance a tra-

.

CONTADOR MOD 255

Q

7

Q

6

Q

5

Q

4

Q

3

Q

2

Q

1

Q

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

Entrada

analgica

Comparador

+

-

EN

D A C

Latches

Circuito

de control

clear

Tensin de referencia en escalera

CLK

y

O

y

7

vs de sus estados binarios, produciendo una tensin de refe-

rencia en escalera a partir del DAC, el contador contina pa-

sando de un estado al siguiente, dando lugar sucesivamente a

escalones mas altos en la tensin de referencia; cuando la ten-

sin de referencia en escalera alcanza la tensin de entrada

analgica, la salida del comparador pasa a nivel bajo y la

puerta AND se desactiva, lo que hace que cesen los impulsos

de reloj y el contador se para. El estado binario del contador

en este momento es igual al nmero de escalones requeridos

de la tensin de referencia, para hacer la referencia igual o ma

yor que la entrada analgica, desde luego este nmero binario

representa el valor de la entrada analgica. La lgica del con-

tador carga la cuenta binaria en los latches y pone a 0 el con

tador,inicindose despus otra secuencia de cuenta, para mues

trear al valor de entrada.

El mtodo de rampa digital es ms lento que el mtodo flash

porque en el peor caso para entrada mxima, el contador debe

pasar a travs del nmero mximo de estados antes de realizar

la conversin. Para una conversin de 8 bits esto significa un

mximo de 256 estados. A continuacin se ilustra una secuen-

cia de conversin de 4 bits. Observar que para cada muestra

el contador debe contar desde cero hasta el escaln de la ten-

sin de referencia que alcanza a la tensin de entrada analgi-

ca. El tiempo de conversin es variable en funcin de la ten

sin analgica.

Seal analgica digitalizada a travs de un

convertidor de escalera o Rampa

se ve en la grfica que el tiempo de conversin es di

ferente entre una conversin y otra.

0111

1010

1101

1010

0110

0101

1000

1001

0100

14

13

12

11

10

09

07

08

05

06

04

03

02

01

00

Tiempo de conversin mximo

para estos valores concretos

Tiempo de conversin mnimo

para estos valores concretos

V

Convertidor Analgico digital por aproximaciones

sucesivas

Es el mtodo mas ampliamente conocido, tiene un tiempo de

conversin mucho menor que los otros mtodos a excepcin

del mtodo flash. El tiempo de conversin es fijo para cual-

quier valor de la entrada analgica. Este convertidor est for-

mado por un DAC, un registro de aproximaciones sucesivas

(SAR) y un Comparador. Su funcionamiento bsico es el si-

guiente : Los bits de entrada al DAC se habilitan (se ponen a

1 ) uno por vez, comenzando por el MSB; cada vez que se ha-

bilita, el comparador produce una salida que indica si la ten-

sin analgica de entrada es mayor o menor que la salida del

DAC.Si la salida del DAC es mayor que la entrada a-

nalgica, la salida del comparador est a nivel bajo,

haciendo que el bit en el registro pase a cero. Si la sa

lida es menor que la entrada analgica, el bit 1 se

mantiene en el registro. El sistema realiza esta opera-

cin con el MSB primero, luego con el siguiente bit

mas significativo, despus con el siguiente y as su-

cesivamente.

Despus que todos los bits del DAC hayan sido apli-

cados, el ciclo de conversin est completo

Para comprender mejor el funcionamiento del ADC

en referencia, haremos un ejemplo, como se muestra

en la prxima diapositiva.

Representacin esquemtica de un Convertidor Analgico-

Digital por aproximaciones sucesivas

Como ya se mencion el conversor analgico Digital por

aproximaciones sucesivas, esta compuesto por un

DAC(conversor Digital-Analgico), un SAR(Registro de

aproximaciones sucesivas), un comparador para la entrada

analgica y la salida, tal como se ve a continuacin.

D A C

S A R

D

-

+

entrada

analgica

c l k

salida binaria

serie

salida binaria

paralelo

V

(o u t)

D

0

D

1

D

2

D

3

M S B

L S B

Ejemplo

Se tiene un conversor de aproximaciones sucesivas de 4 bits,

realizar paso a paso la conversin de una tensin DC de 5v.

D A C

D A C

D A C

D

D A C

D

2

3

2

2

2

1

2

0

2

3

2

2

2

1

2

0

2

3

2

2

2

1

2

0

2

3

2

2

2

1

2

0

1 0 0 0

0 1 0 0

0 1 1 0 0 1 0 1

D

D

puesto a cero, porque (V-)

es mayor que (V+)

+ 8v

+ 4v

+ 6v + 5v

+ 5v

+ 5v

+ 5v

+ 5v

se mantiene, porque (V+)

es mayor que (V-)

puesto a cero, porque (V-)

es mayor que (V+)

se mantiene, porque (V+)

es igual que (V-)

1

2

3

4

BAJO ALTO

BAJO

ALTO

Cractersticas del Convertidor Analgico/Digital, del ejemplo

que se esta considerando.

Suponemos que el DAC tiene una salida de 8v para el bit

2

3

(MSB), Vout= 4v para 2

2

, Vout= 2v para 2

1

y Vout=1 para

2

0

(LSB).

La figura para el primer clock, muestra el primer paso del ciclo

de conversin con el MSB=1, en la que la salida del DAC es 8v,

la que al ser mayor que la entrada analgica de 5v,har que la

salida del comparador sea baja, lo que origina que el MSB del

SAR se ponga en 0.

El segundo clock muestra, el segundo paso del ciclo de

conversin con el bit 2

2

igual a 1 para el SAR; en este caso la

salida del DAC es de 4v, como este voltaje es menor que la

entrada analgica de 5v, la salida del comparador conmuta a

nivel alto, lo que hace que este bit se mantenga en el SAR

La figura del clock 3, muestra el tercer paso del ciclo de

conversin con el bit 2

1

=1 para el SAR, ahora la salida del

DAC es 6v(4+2), como este voltaje es mayor que la entrada

analgica de 5v, la salida del comparador conmuta a nivel

bajo, lo que implica que el bit 2

1

del SAR se ponga en 0

La figura del clock 4, muestra el cuarto y ltimo paso del ciclo

de conversin, con el bit 2

0

=1 para el SAR, la salida del DAC es

ahora 5v(4+1) y como la entrada es tambin 5v, el comparador

conmuta de bajo a alto, lo que hace que el LSB del SAR se

mantenga en 1. Se han probado los 4 bits y el ciclo de

conversin ha sido completado. En este momento el cdigo

binario almacenado en el registro(SAR) es 0101, que es el valor

binario de la entrada analgica de 5v. A continuacin se inicia

un nuevo ciclo de conversin y el proceso se repite. El SAR se

borra al comienzo de cada nuevo ciclo.

Aplicaciones:

Supongamos que un DAC, tiene las caractersticas siguientes:

Frecuencia de reloj 1MHz, salida del conversor a escala completa

10.23v y una entrada de 10bits

Determinar:

a) El equivalente digital obtenido para una entrada de 3.728 v

b) El tiempo de conversin para el caso anterior

c) La resolucin porcentual.

Solucin

Nmero de pasos posibles = 2

10

-1 =1023

Tamao del paso = (10.23 v/1023) = 10 mV

N de pasos para alcanzar la tensin pedida = (3.728 v/10 mV) =

373 aproximadamente y 373

(10)

= 0101110101

(2)

Tiempo de conversin para obtener 3.728 v (0101110101)

Como el clock es de 1MHZ entonces el perodo es de 1seg por lo tanto 1

seg 373 = 373 seg.

Ejemplo 2.-

Dos conversores A/D de 10 bits c/u de escalera y el otro de aproximaciones

sucesivas trabajan con un mismo tipo de reloj(500 kHZ). Calcular los

tiempos de conversin para escala completa.

Solucin

Sabemos que en el conversor A/D en escalera cada clock es un paso y en el de

aproximaciones sucesivas cada clock es un bit por lo que es importante

saber el perodo del reloj as :

T =(1/f) = (1/500kHZ) = 2seg. En consecuencia:

a) Para el conversor en escalera el tiempo de conversin es:

(2n-1) x 2seg = 2046 seg

a) Para el conversor de aproximaciones sucesivas el tiempo de conversin

es 10 bits x 2seg = 20seg

Ejercicio 3.-

Un conversor D/A, de 8 bits tiene una salida a escala completa

de 2ma. con un error tambin de escala completa de 0.5%Cul

es el rango de posibles salidas para una entrada 10000000

(2)

Solucin:

2ma = 2000A 0.5% de 2000A = 10A

Tamao del paso= [2000/(2

8

-1)] = (2000/255) = 7.84

10000000

(2)

= 80

(H)

=128

Salida de corriente para el binario 10000000

(2)

= 7.84 x128 =

1004A

Por lo tanto la salida pedida en A est:

994< salida para(10000000

(2)

)<1014

Você também pode gostar

- Manual para La Creacion de Idocs by MundosapDocumento47 páginasManual para La Creacion de Idocs by MundosapAlfredo100% (6)

- Investigacion Sobre Extenciones de ArchivosDocumento24 páginasInvestigacion Sobre Extenciones de Archivosemma100% (1)

- Programaciones Curriculares de Los Cursos de Computacion CetproDocumento22 páginasProgramaciones Curriculares de Los Cursos de Computacion CetproROSAAinda não há avaliações

- CS 04 (Memorias)Documento20 páginasCS 04 (Memorias)someone that you used to knowAinda não há avaliações

- Introduccion Finanzas Perossa PreviewDocumento34 páginasIntroduccion Finanzas Perossa Previewsomeone that you used to knowAinda não há avaliações

- MurciaDocumento130 páginasMurciabibliocacaAinda não há avaliações

- Informe EquiposDocumento4 páginasInforme EquiposYhonny CuffaroAinda não há avaliações

- RichardoleDocumento4 páginasRichardoleSantamaria JamesAinda não há avaliações

- Redes Xpon y FTTX PDFDocumento6 páginasRedes Xpon y FTTX PDFAriel MeroAinda não há avaliações

- Formato Guia Actividades Pedagogicas Happy World Grado 7a y 7B Informatica Segundo PeriodoDocumento3 páginasFormato Guia Actividades Pedagogicas Happy World Grado 7a y 7B Informatica Segundo PeriodoDavid MendozaAinda não há avaliações

- Procedimiento de RequisicionesDocumento18 páginasProcedimiento de Requisicionesjorge emerson cuellar javierAinda não há avaliações

- Mapa ConceptualDocumento2 páginasMapa ConceptualJose LuisAinda não há avaliações

- Programación Analitica Teléfonos en El Aula VeraguasDocumento12 páginasProgramación Analitica Teléfonos en El Aula VeraguasozelperroAinda não há avaliações

- OTT Resumen Como FuncionaDocumento3 páginasOTT Resumen Como Funcionatapiacusimarcoantoniogmail.com Tapia Cusi Marco AntonioAinda não há avaliações

- ManualPrecios PreciosActual Contrato PDFDocumento329 páginasManualPrecios PreciosActual Contrato PDFantoniotohotAinda não há avaliações

- Procesadores-VLIW - Grupo 5! PDFDocumento150 páginasProcesadores-VLIW - Grupo 5! PDFKaryna Cusacani MamaniAinda não há avaliações

- Userguide - Es - ES KOBO GLO HDDocumento70 páginasUserguide - Es - ES KOBO GLO HDjoseAinda não há avaliações

- Software ICS TelecomDocumento6 páginasSoftware ICS Telecomdiana240wallAinda não há avaliações

- Uriel ControlesDocumento3 páginasUriel ControlesEmmanuel Alvarez0% (1)

- Validación de Técnicas de Migración y Herramientas ETLDocumento10 páginasValidación de Técnicas de Migración y Herramientas ETLmantenimiento especializadoAinda não há avaliações

- Carta Internet 300Documento2 páginasCarta Internet 300alonetazAinda não há avaliações

- Ingenieria de Software-Somerville - Ejercicios Del Proceso de SoftwareDocumento2 páginasIngenieria de Software-Somerville - Ejercicios Del Proceso de SoftwareHenry Miguel Ruiz ReyesAinda não há avaliações

- Net UnoDocumento2 páginasNet UnoLucasAinda não há avaliações

- 1 Manual Visual PDFDocumento104 páginas1 Manual Visual PDFHenry Paúl García HuacachiAinda não há avaliações

- Tesis Ensamblaje de PCDocumento100 páginasTesis Ensamblaje de PCRaul Alor VenturaAinda não há avaliações

- Las TIC para La Recopilacion de Datos El Monitoreo y La EvaluacionDocumento7 páginasLas TIC para La Recopilacion de Datos El Monitoreo y La Evaluacionelpanico258772Ainda não há avaliações

- Visual Basic BasicoDocumento7 páginasVisual Basic BasicocesarAinda não há avaliações

- Investigate BIOS or UEFI Settings HechoDocumento4 páginasInvestigate BIOS or UEFI Settings HechoSamuel José Roa VenturaAinda não há avaliações

- Circuitos Secuenciales Asincronos PDFDocumento51 páginasCircuitos Secuenciales Asincronos PDFAbigail CoraiteAinda não há avaliações

- RTPDocumento3 páginasRTPYaZmin MaGaña HereÐiaAinda não há avaliações

- 2012-09-24 CIDR Examen PDFDocumento5 páginas2012-09-24 CIDR Examen PDFGodofredoAinda não há avaliações

- Codigo en C para PuertosDocumento3 páginasCodigo en C para PuertosJuan Carlos Uicab AlcudiaAinda não há avaliações

- Pre Lab 5Documento4 páginasPre Lab 5Carlos CastroAinda não há avaliações

- NT - Cables Symbol Ls2208Documento1 páginaNT - Cables Symbol Ls2208pelotadetrapoAinda não há avaliações