Escolar Documentos

Profissional Documentos

Cultura Documentos

Arquitetura de Computadores: Modelo de Von Neumann e Elementos dos Sistemas Computacionais

Enviado por

HiagoalvesDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Arquitetura de Computadores: Modelo de Von Neumann e Elementos dos Sistemas Computacionais

Enviado por

HiagoalvesDireitos autorais:

Formatos disponíveis

UNIFACS Universidade Salvador Prof.: Sergio Luz Email: sergio.luz@unifacs.

br

Arquitetura de

Computadores

Diferena entre arquitetura e organizao

Modelo de Von Neumann (ou von Neumann)

Elementos dos Sistemas Computacionais

www.redes.unifacs.br

2

Arquitetura

Trata dos aspectos funcionais de um sistema computacional,

normalmente so perceptveis pelo programador. Exemplo: tamanho

(em bits) da palavra, conjunto de instrues, mecanismos de E/S,

formas de endereamento.

Organizao

Trata da estrutura do sistema computacional e normalmente no so

percebidos pelo programador. Exemplo: freqncia do relgio, sinais

de controle, tecnologias da memria e como uma operao

(multiplicao, por exemplo) implementada (atravs de somas

sucessivas ou por hardware especfico?).

Definir se um computador vai dispor de uma instruo de diviso uma deciso de

arquitetura. Definir se esta instruo ser implementada atravs de uma unidade

especfica de hardware ou se por um mecanismo de subtraes sucessivas uma

deciso de organizao..

Arquitetura x Organizao

www.redes.unifacs.br

3

NEUMANN, J. von. First draft of a report on the EDVAC. University of Pennsylvania, 1945.

(...) para ser eficiente e ter aplicao geral, um computador tem de ter

uma Unidade central de Lgica e Aritmtica (ULA), uma unidade central

de controle (UC) para 'orquestrar' as operaes, uma memria, uma

unidade de entrada, e uma unidade de sada (...)

MEMRIA

PRINCIPAL

UNIDADE

LGICA

E ARITMTICA

(ULA)

UNIDADE DE

CONTROLE

(UC)

DISPOSITIVO

DE ENTRADA

programa dados

UNIDADE CENTRAL DE

PROCESSAMENTO

DISPOSITIVO

DE ENTRADA

Modelo de Von Neumann

www.redes.unifacs.br

4

Em 1952 Von Neumann constri o IAS.

www.redes.unifacs.br

5

Em 1952 Von Neumann constri o IAS.

Computador de uso genrico.

Aritmtica binria.

Programa armazenado na

memria.

Consolidou a arquitetura

utilizada como padro nos

computadores modernos, que

passou a ser chamada de

Arquitetura de Von Neumann.

Funcionamento em turnos, ou

ciclos, de execuo das instrues.

A movimentao de dados e

instrues entre a unidade central

de processamento e a memria

acontece atravs de um

barramento compartilhado.

C

o

m

p

o

n

e

n

t

e

s

d

o

I

A

S

Contm os dados

lidos da, ou para

escrita na, memria

Contm os dados

lidos da, ou para

escrita na, memria

Contm o cdigo da

instruo que est

sendo executada

Armazena

temporariamente a

segunda instruo

do par lido da

memria

Contm o endereo

de memria do

prximo par de

instrues a ser

executado

Armazenam

temporariamente os

operandos e os

resultados das

operaes

efetuadas pela ULA

Interpreta as instrues

armazenadas no IR e

envia sinais ULA para

execuo.

www.redes.unifacs.br

7

Execuo de um ciclo de instrues no IAS

1.Uma instruo carregada no IR (I nstruction Register) e o

endereo de memria associado a ela carregado no MAR

(Memory Adress Register).

2.O circuito de controle interpreta o cdigo da operao e

executa a instruo, enviando os sinais de controle apropriados

para fazer com que dados sejam transferidos ou que uma

operao seja executada pela ULA.

O IAS possua um total de 21 instrues que podem ser

agrupadas da seguinte maneira:

Transferncia de dados;

Desvio incondicional;

Desvio condicional;

Aritmtica;

Alterao de endereo.

www.redes.unifacs.br

8

Memria no IAS (williams tube memory)

www.redes.unifacs.br

9

Memria no IAS

A memria do IAS era constituda de mil posies de memria,

chamadas de palavras.

Cada palavra constituda de 40 dgitos binrios (bits).

Tanto nmeros quanto instrues eram armazenadas na memria,

logo representadas em modo binrio, como nas figura a seguir:

(a) armazenamento de um nmero

(b) armazenamento de uma instruo

www.redes.unifacs.br

10

Organizao da memria principal (MP)

0

1

2

3

.

.

.

.

.

.

m-1

0000 1111

1010 0100

0000 0000

1111 1111

0000 1111

0000 1011

Endereo

Contedo: instruo

ou dados

tamanho da clula = 8 bits

Quantidade de posies de

memria endereveis = m

Armazena informaes (dados) e programas (sequncia de instrues);

Composta por vrias unidades, chamadas clulas;

Cada clula ocupa uma posio de memria;

Cada posio de memria tem um endereo;

Cada clula capaz de armazenar uma quantidade fixa e limitada

de its.

www.redes.unifacs.br

11

Tipos de memria

MEMRIA

PRINCIPAL

UNIDADE

LGICA

E ARITMTICA

(ULA)

UNIDADE DE

CONTROLE

(UC)

DISPOSITIVOS

DE ENTRADA

programa dados

UNIDADE CENTRAL DE

PROCESSAMENTO

(UCP)

DISPOSITIVOS

DE SADA

MEMRIA

SECUNDRIA

REGISTRADOR REGISTRADOR REGISTRADOR

...

CACHE

CACHE

A TROCA DE DADOS E SINAIS DE

CONTROLE ACONTECE ATRAVS

DOS BARRAMENTOS DO SISTEMA

www.redes.unifacs.br

12

Exemplos de memria

REGISTRADORES

MEMRIA PRINCIPAL

(RAM e ROM)

CACHE

MEMRIA SECUNDRIA

www.redes.unifacs.br

13

Barramento do sistema

BARRAMENTO DE DADOS

BARRAMENTO DE ENDEREOS

BARRAMENTO DE CONTROLE

B

A

R

R

A

M

E

N

T

O

D

O

S

I

S

T

E

M

A

CPU

(ULA + UC)

MEMRIA

ENTRADA

E

SADA

Barramento de dados: move dados

entre os componentes do sistema.

Barramento de endereos: identifica

os endereos de memria onde devem

ser lidas/escritas informaes.

Barramento de controle: coordena o

acesso aos demais barramentos e

direciona dados para componentes

especficos.

www.redes.unifacs.br

14

Tipos de barramentos

Interno

Interliga os componentes internos da UCP, como ULA, UC,

registradores e cache interno (L1).

Externo

Interliga UCP memria principal, unidades de entrada e sada,

cache externo (L2), memria secundria, etc.

Expanso

Permite a expanso das capacidades do computador atravs da

adio de novos componentes de hardware. Os barramentos de

expanso seguem padres, como:

ISA (Industry Standard Architecture),

MCA (Microchannel Architecture),

EISA (Extended Industry Standard Architecture),

VLB (Vesa Local Bus),

PCI (Peripheral Component Interconnect),

AGP (Accelerated Graphics Port),

USB (Universal Serial Bus)

Firewire (IEEE 1394)

www.redes.unifacs.br

15

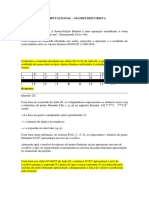

Microprocessador: quantidade de transistores

www.redes.unifacs.br

16

Dcada de 70

Intel 4004 (1971): 15 mcrons

8088 (1979): 3 mcrons (tamanho de um vrus)

Dcada de 80

Intel 486: 1 mcron

Dcada de 90

Pentium III: 0.18 mcron (tamanho de uma molcula de DNA)

Incio do sc. XXI

Pentium 4 e Athlon: 0.13 mcron

Intel Core 2: 0,065 mcron

Microprocessador: tamanho dos transistores

www.redes.unifacs.br

17

Processador & Conjunto de instrues

CISC (Complex I nstruction Set Computing)

Reconhece mais de uma centena de instrues;

mais lento na execuo das instrues;

A maioria dos microprocessadores so CISC.

RISC (Reduced I nstruction Set Computing)

Reconhece um nmero limitado de instrues

otimizadas para que sejam executadas com mais

rapidez;

As instrues no contempladas so executadas como

combinaes das existentes;

Desempenho entre 50 e 75% superior a um CISC.

www.redes.unifacs.br

18

CPU, Barramentos e Memria

www.redes.unifacs.br

19

DISPOSITIVOS DE ENTRADA

DISPOSITIVOS DE SADA

UNIDADE CENTRAL DE PROCESSAMENTO

(UNIDADE LGICA E ARITMTICA + UNIDADE DE CONTROLE)

MEMRIA PRINCIPAL

Elementos da Arquitetura de Von Neumann

www.redes.unifacs.br

20

Funcionamento em turnos (ciclos)

www.redes.unifacs.br

21

Clock

Coordena as aes do computador propagando pulsos eltricos

peridicos que se propagam pelo barramento externo.

Alimentado por um cristal de quartzo, responsvel pela

manuteno da freqncia constante no clock.

O clock expresso em termos de freqncia e sua unidade o

Hertz (Hz).

1 Hz = 1 ciclo por segundo (1 operao realizada a cada ciclo)

Um de de 1 GHz emite 1 bilho de pulsos eltricos por segundo e,

teoricamente, poderia realizar 1 bilho de operaes a cada

segundo.

A UCP no possui gerador de clock, opera multiplicando o sinal

recebido da placa me.

www.redes.unifacs.br

22

Um sistema computacional tpico

www.redes.unifacs.br

23

Organizao: Intel x AMD

www.redes.unifacs.br

24

Atividade

Organizem-se em equipes de, no mximo, duas

pessoas.

Preparem um nico slide sobre a arquitetura

no Von Neuman (non Von Neumann) que

preferir

Cada dupla dever fazer uma rpida

apresentao a respeito da arquitetura escolhida,

destacando suas diferenas em relao ao

modelo de Von Neuman.

Você também pode gostar

- Escritura Particular de Compra e VendaDocumento2 páginasEscritura Particular de Compra e VendaHiagoalves76% (21)

- Mercado Sombrio - o Cybercrime e VocêDocumento14 páginasMercado Sombrio - o Cybercrime e VocêMarcello Augusto100% (2)

- Resumo Do Cap. 1 2 e 3 de AocDocumento9 páginasResumo Do Cap. 1 2 e 3 de Aocsandro ruiz lopesAinda não há avaliações

- Microcontroladores e Microprocessadores: Conceitos BásicosDocumento6 páginasMicrocontroladores e Microprocessadores: Conceitos BásicosDouglas Cintra ValençaAinda não há avaliações

- Exercicios ResolvidosDocumento16 páginasExercicios Resolvidosamilcarguimaraes17423100% (1)

- Passo a passo CTR 2000Documento8 páginasPasso a passo CTR 2000Gerson AraujoAinda não há avaliações

- 1° Periodo Arquitetura e Organização de ComputadoresDocumento8 páginas1° Periodo Arquitetura e Organização de ComputadoresCurso OpsAinda não há avaliações

- Modelo de Von Neumann: Arquitetura e ComponentesDocumento13 páginasModelo de Von Neumann: Arquitetura e Componentesobed ernesto NgoveneAinda não há avaliações

- Aula 3 Arquiteturas Microcontroladores e Microprocessadores PDFDocumento24 páginasAula 3 Arquiteturas Microcontroladores e Microprocessadores PDFAllas JonyAinda não há avaliações

- mac2166_aula1Documento27 páginasmac2166_aula1gotagey965Ainda não há avaliações

- TEMA - II Arquitectura de ComputadorDocumento27 páginasTEMA - II Arquitectura de ComputadorMomade VasconcelosAinda não há avaliações

- 2012-Arquitetura de Von Neumann1Documento12 páginas2012-Arquitetura de Von Neumann1rsoakenAinda não há avaliações

- Microprocess AdoresDocumento59 páginasMicroprocess AdoresRicardo GomesAinda não há avaliações

- Arquitetura E Organização de ComputadoresDocumento88 páginasArquitetura E Organização de ComputadoresEng. Eletricista - José Antonio RodriguesAinda não há avaliações

- Definições de Computador, Programa e LinguagensDocumento33 páginasDefinições de Computador, Programa e LinguagensChico OliveiraAinda não há avaliações

- Silo - Tips - Mapa Mental de Arquitetura e Organizaao de ComputadoresDocumento53 páginasSilo - Tips - Mapa Mental de Arquitetura e Organizaao de ComputadoresIvanildo SilvaAinda não há avaliações

- Arquitetura e Organização de ComputadoresDocumento7 páginasArquitetura e Organização de ComputadoresDiogo MullerAinda não há avaliações

- Organização Computador Von NeumannDocumento73 páginasOrganização Computador Von NeumannBruno MagalhaesAinda não há avaliações

- Microcontroladores vs MicroprocessadoresDocumento18 páginasMicrocontroladores vs Microprocessadores194digaoAinda não há avaliações

- Maiko Chintinguiza - Ficha01 SistDigDocumento6 páginasMaiko Chintinguiza - Ficha01 SistDigMaiko Hortêncio ChintinguizaAinda não há avaliações

- Organização de Computadores 3062-60-55903 - R - E1 - 20211 - 01 - Slides de Aula IIDocumento49 páginasOrganização de Computadores 3062-60-55903 - R - E1 - 20211 - 01 - Slides de Aula IIAdriano C OliveiraAinda não há avaliações

- CPU - Unidade Lógica-Aritmetica e Unidade de ControleDocumento4 páginasCPU - Unidade Lógica-Aritmetica e Unidade de Controledandico_Ainda não há avaliações

- Arquitectura Interna Do Computador - Mário SilvaDocumento22 páginasArquitectura Interna Do Computador - Mário Silvachilamen100% (1)

- Modulo 4 - Componente Do Comp.Documento46 páginasModulo 4 - Componente Do Comp.Eduar AndrighettiAinda não há avaliações

- Apostila Sistemas Operacionais I Parte1Documento18 páginasApostila Sistemas Operacionais I Parte1Patrick MenezesAinda não há avaliações

- Sistemas de Interconexão PDFDocumento31 páginasSistemas de Interconexão PDFLuiz FelipeAinda não há avaliações

- Arquitetura de Von Neumann e HarvardDocumento5 páginasArquitetura de Von Neumann e HarvardLibroLivroAinda não há avaliações

- Apresentação Aula 25 02 2021 v2Documento43 páginasApresentação Aula 25 02 2021 v2felipjimsAinda não há avaliações

- Guia sobre Hardware e SoftwareDocumento4 páginasGuia sobre Hardware e SoftwareMelissa NascimentoAinda não há avaliações

- Arquitetura de Microcontroladores e suas Principais PartesDocumento21 páginasArquitetura de Microcontroladores e suas Principais PartesEdgar DanielAinda não há avaliações

- Organização de ComputadoresDocumento17 páginasOrganização de ComputadoresAdriano FurtadoAinda não há avaliações

- Esquema de Estudo para Primeira Prova de Arq CompDocumento3 páginasEsquema de Estudo para Primeira Prova de Arq CompMateus VilasboasAinda não há avaliações

- Arquitetura de Computadores RISC x CISCDocumento2 páginasArquitetura de Computadores RISC x CISCCamilaSilva100% (1)

- Slides de Aula IDocumento46 páginasSlides de Aula IRaulAinda não há avaliações

- Estrutura Sistemas OperacionaisDocumento28 páginasEstrutura Sistemas OperacionaisEDGARAinda não há avaliações

- Arquiteturas de MicroprocessadoresDocumento20 páginasArquiteturas de MicroprocessadoresPaulo Figueiredo VicenteAinda não há avaliações

- bcc425 - AULA6Documento39 páginasbcc425 - AULA6DiegoGonçalvesAinda não há avaliações

- Aula03 - So (Modo de Compatibilidade)Documento28 páginasAula03 - So (Modo de Compatibilidade)IsaacMedeirosAinda não há avaliações

- Arquitetura de von NeumannDocumento1 páginaArquitetura de von NeumannpabjrAinda não há avaliações

- F3Documento9 páginasF3The BegginerAinda não há avaliações

- Algoritmos e Estruturas de Dados IDocumento40 páginasAlgoritmos e Estruturas de Dados IFrancisco Milton SiueiaAinda não há avaliações

- Capítulo 1 - ARQUITECTURA DE COMPUTADORES (MICRONTROLADORES)Documento21 páginasCapítulo 1 - ARQUITECTURA DE COMPUTADORES (MICRONTROLADORES)cedrick mansoniAinda não há avaliações

- Deivid Pessoa Dr1 atDocumento47 páginasDeivid Pessoa Dr1 atvanessavieiira2Ainda não há avaliações

- OC - 05 - Material Extre Sobre Pipeline PDFDocumento64 páginasOC - 05 - Material Extre Sobre Pipeline PDFchacalleonardoAinda não há avaliações

- Introdução aos conceitos básicos de computadoresDocumento49 páginasIntrodução aos conceitos básicos de computadoresLipe ZOAinda não há avaliações

- Microcontroladores - Arquitetura PDFDocumento24 páginasMicrocontroladores - Arquitetura PDFRubens Zenko SakiyamaAinda não há avaliações

- Fundamentos HardwareDocumento18 páginasFundamentos HardwareAludson FreitasAinda não há avaliações

- Resumir - ISS-SCDocumento518 páginasResumir - ISS-SCConcurseiroPersistenteAinda não há avaliações

- Texto de ApoioDocumento14 páginasTexto de ApoioRoy BattyAinda não há avaliações

- Apostila Msp430 - C - Parte IDocumento55 páginasApostila Msp430 - C - Parte ICecilio MartinsAinda não há avaliações

- Material Auxiliar para Curso Avançado I MSP430Documento48 páginasMaterial Auxiliar para Curso Avançado I MSP430Atahualpa BastosAinda não há avaliações

- Apostila CDocumento48 páginasApostila CRodrigo De Carvalho VieiraAinda não há avaliações

- Lista ApostilaDocumento7 páginasLista ApostilaThiago Henrique TullioAinda não há avaliações

- Aula 1 - Sistemas OperacionaisDocumento9 páginasAula 1 - Sistemas OperacionaisDaniel vidsAinda não há avaliações

- Unidade 1 - SlidesDocumento26 páginasUnidade 1 - SlidesRoberli SchuinaAinda não há avaliações

- Evolução ComputadoresDocumento2 páginasEvolução ComputadoresFernando BorbaAinda não há avaliações

- Apostila de Sistemas Microprocessados PDFDocumento221 páginasApostila de Sistemas Microprocessados PDFRomeu Corradi JúniorAinda não há avaliações

- SO Estrutura e ArquiteturaDocumento29 páginasSO Estrutura e ArquiteturaFelipe BarrosAinda não há avaliações

- Apostila de Sistemas MicroprocessadosDocumento221 páginasApostila de Sistemas MicroprocessadosronaldorarAinda não há avaliações

- Confere Ncia 02 - Conceitos de Hardware e SoftwareDocumento109 páginasConfere Ncia 02 - Conceitos de Hardware e SoftwareSebastião Kiago Tchianze JoséAinda não há avaliações

- Evolução e desempenho dos computadores ao longo das geraçõesDocumento50 páginasEvolução e desempenho dos computadores ao longo das geraçõesKaroline TorresAinda não há avaliações

- Arquitetura Von NewmannDocumento5 páginasArquitetura Von NewmannHiagoalvesAinda não há avaliações

- Arquitetura de von Neumann e seu impacto na computaçãoDocumento6 páginasArquitetura de von Neumann e seu impacto na computaçãoHiagoalvesAinda não há avaliações

- Arquitetura Von NewmannDocumento96 páginasArquitetura Von NewmannHiagoalvesAinda não há avaliações

- ArqVonNeumann DFDFDocumento3 páginasArqVonNeumann DFDFHiagoalvesAinda não há avaliações

- Arq Aula5Documento23 páginasArq Aula5HiagoalvesAinda não há avaliações

- Arquitetura Von NewmannDocumento23 páginasArquitetura Von NewmannAlvaro JuniorAinda não há avaliações

- ArqVonNeumann DFDFDocumento3 páginasArqVonNeumann DFDFHiagoalvesAinda não há avaliações

- Arqt Aula9 Modelo Von Aritmetica PDFDocumento70 páginasArqt Aula9 Modelo Von Aritmetica PDFdfernandes_650413Ainda não há avaliações

- Ac2 Modelodevonneumann 120316102215 Phpapp02Documento16 páginasAc2 Modelodevonneumann 120316102215 Phpapp02Johnantan SantosAinda não há avaliações

- Arquitetura Von NewmannDocumento23 páginasArquitetura Von NewmannAlvaro JuniorAinda não há avaliações

- Fórmula Da União de 3 ConjuntosDocumento3 páginasFórmula Da União de 3 ConjuntosPeter MoreiraAinda não há avaliações

- Integrais DuplasDocumento7 páginasIntegrais DuplasCristiano da silvaAinda não há avaliações

- Matematica Computacional Matriz DiscursivaDocumento4 páginasMatematica Computacional Matriz DiscursivaAdeline Ambrozim100% (1)

- download-39910-DTM Studio-REVIT 22 Importantes Dicas para Voce Iniciante-1373424 PDFDocumento39 páginasdownload-39910-DTM Studio-REVIT 22 Importantes Dicas para Voce Iniciante-1373424 PDFJosy Carvalho100% (1)

- SQL InjectionDocumento11 páginasSQL InjectionFrederico De Souza FerreiraAinda não há avaliações

- Listac 05Documento4 páginasListac 05Daniel AlbuquerqueAinda não há avaliações

- Avaliação ESTRUTURA DE DADOSDocumento5 páginasAvaliação ESTRUTURA DE DADOSanon_548679405Ainda não há avaliações

- 1 - Interpretação: Língua PortuguesaDocumento13 páginas1 - Interpretação: Língua PortuguesaMonique SilveiraAinda não há avaliações

- Hacker derruba servidor de pornografia infantil na deep webDocumento3 páginasHacker derruba servidor de pornografia infantil na deep webmarcelo groeAinda não há avaliações

- Analista de TR Onsito e Transportes Engenharia Mec Onica PDFDocumento16 páginasAnalista de TR Onsito e Transportes Engenharia Mec Onica PDFpedrothiagotauaAinda não há avaliações

- Benjamin Fulford Despejo de DocumentosDocumento5 páginasBenjamin Fulford Despejo de DocumentosGabriel Brandão de carvalho FrançaAinda não há avaliações

- Matemática Concursos FraçõesDocumento31 páginasMatemática Concursos FraçõesAdriana FerreiraAinda não há avaliações

- Instalação GNS3 UbuntuDocumento6 páginasInstalação GNS3 UbuntuWellington João da SilvaAinda não há avaliações

- O Programa MMANA de Makoto Mori JE3HHT - Parte 1Documento7 páginasO Programa MMANA de Makoto Mori JE3HHT - Parte 1Tomi Pasin100% (1)

- Resolução de sistemas de equações linearesDocumento19 páginasResolução de sistemas de equações linearesGonçalo LimaAinda não há avaliações

- AutoCad Mechanical 2014 ApostilaDocumento121 páginasAutoCad Mechanical 2014 ApostilaFernandovo10Ainda não há avaliações

- Passo A Passo para Imprimir Com Escala No AutocadDocumento2 páginasPasso A Passo para Imprimir Com Escala No AutocadLilianne MaiaAinda não há avaliações

- Gabarito Simulado 2 GranDocumento18 páginasGabarito Simulado 2 Granuf254983mmhAinda não há avaliações

- Tuturiais Fireworks MXDocumento448 páginasTuturiais Fireworks MXmiguelbessaAinda não há avaliações

- Manual RhinocerosDocumento11 páginasManual RhinocerosRo Saul CohenAinda não há avaliações

- Gráfico de GanttDocumento5 páginasGráfico de GanttTiago GirardiAinda não há avaliações

- Apostila Senai Mecatronica Fundamentos de Linguagem CDocumento156 páginasApostila Senai Mecatronica Fundamentos de Linguagem Crcimplast100% (1)

- Introdução A HTML e CSS - Desenvolvimento Web Com HTML, CSS e JavaScriptDocumento51 páginasIntrodução A HTML e CSS - Desenvolvimento Web Com HTML, CSS e JavaScriptJozimar BernardiAinda não há avaliações

- Conjunto Dos Números ReaisDocumento4 páginasConjunto Dos Números ReaisElisiane Aparecida Nunes SilvaAinda não há avaliações

- Segurança na webDocumento5 páginasSegurança na webDavi Melk Mazo de CarvalhoAinda não há avaliações

- Controle de atuadores pneumáticos em sistemas de automação industrialDocumento9 páginasControle de atuadores pneumáticos em sistemas de automação industrialRael GdionAinda não há avaliações

- 30 anos do Atari no BrasilDocumento66 páginas30 anos do Atari no BrasilRoberto Candido FranciscoAinda não há avaliações