Escolar Documentos

Profissional Documentos

Cultura Documentos

Arbitrary Cryptoarithmetic Oracle

Enviado por

Alan ChengDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Arbitrary Cryptoarithmetic Oracle

Enviado por

Alan ChengDireitos autorais:

Formatos disponíveis

Alan Cheng

Constraint Satisfaction Problems (CSP) are a standard benchmark for current hardware technologies. Evaluate the speed and processing power of new hardware. In new technologies, it is appropriate to compare results with current benchmarks.

A type of CSP Unique, in which there are not many results (unlike SAT and Graph-Coloring) Are consisted of letters and symbols which can represent numerical values. Substituted values must solve the given equation. Hence the name of cryptoarithmetic problems.

This problem is a crypto-arithmetic problem. TWO +TWO FOUR The letters must be replaced with numbers 09, but no two different letters can have the same value (T=0, W=0). The problem is solved if the numbers substituted satisfy the equation.

Field Programmable Gate Arrays (FPGA) are used in current hardware technologies. Examples of usage:

Used in supercomputers Printers

Are programmable boards which directly converts program coding into logic circuits. Have fast calculation rates.

Faster Directly connect to the hardware components (unlike from IDE or OS) Simulation uses a processor (hardware) to process. However, it gives slower processing to due the amount of coding in between the internal hardware and software.

The goal of the project is to create an oracle that would be able to solve arbitrary cryptoarithmetic problems. The user would be able to input the values he/she desires to have

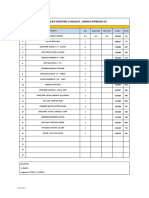

The circuit has to have limitation to prevent the circuit from having too much memory consumption. Therefore it is limited to only a 6+6=6 structure shown below:

X1 X2 X3 X4 X5 X6 + X7 X8 X9 X10 X11 X12 X13 X14 X15 X16 X17 X18

The circuit will have three parts

A Counter For testing all possible combinations and permutations A Good Number Checker For checking the validity of the input (if two number repeats or if similar letters have different values) The Main Oracle Which checks the validity of the given input

The Counter is consisted of 18 smaller counters (for each variable) connected by wires. It would only count 0-9, and will increase the counter to the left after each full cycle (from 0 to 9)

Counter 18 0 to 9

clk

over

over

Counter 2 0 to 9

clk

Counter 1 0 to 9

clk

Clock

This portion of the oracle consists of equality and inequality gates in which the whole circuit is re-compiled for each new problem. It maps each letter and uses equality for the same letter (i.e. o and o) and uses inequality for the rest

X1 X1 X2 X18 != = X2 X18

= !=

!= !=

= =

= !=

This oracle checks for the validity of the given inputs. This can easily be found out using the following series of equations:

X6 + X12 = 10C1 + X18 C1 + X5 + X11 = 10C2 + X17 ... C5 + X1 + X7 = X13

The full oracle can be expressed simply by the following diagram:

Counters

Main Oracle

Good Number

Output

I am still working on the TWO+TWO=FOUR problem in hardware

Partially working (2 solutions, with messed up HEX display outputs) Quartus ii error with the simulated RAM that I modeled.

In Verilog: Simulate arbitrary oracle circuit On FPGA: Run arbitrary oracle circuit Compare run time and analyze speed-up Write reports Emulate in Veloce

Sorry, no picture this time D:

Você também pode gostar

- Embedded Systems 220 Control Unit Design Notes: PC: PC + 1 PC: PC PC: Operand PC: PC + OperandDocumento3 páginasEmbedded Systems 220 Control Unit Design Notes: PC: PC + 1 PC: PC PC: Operand PC: PC + OperandMahesh JangidAinda não há avaliações

- Eda Lab ManualDocumento25 páginasEda Lab ManualAthiraRemeshAinda não há avaliações

- Projects With Microcontrollers And PICCNo EverandProjects With Microcontrollers And PICCNota: 5 de 5 estrelas5/5 (1)

- Coding and Peripheral DesignationDocumento4 páginasCoding and Peripheral DesignationMax GraniAinda não há avaliações

- Lab 06: Arrays (One Dimensional) : Semester BS CS - 01 & BS IT - 02Documento6 páginasLab 06: Arrays (One Dimensional) : Semester BS CS - 01 & BS IT - 02Eiman WahabAinda não há avaliações

- 07 DecodersDocumento21 páginas07 DecodersRafena17Ainda não há avaliações

- (You Are Currently Staying) (For Example 2020PEB5678) (Registered in MNIT)Documento2 páginas(You Are Currently Staying) (For Example 2020PEB5678) (Registered in MNIT)niteshAinda não há avaliações

- Computer Science 37 HW 2Documento5 páginasComputer Science 37 HW 2Alexander TaylorAinda não há avaliações

- Assembly Language LabDocumento32 páginasAssembly Language LabEri Matraku100% (1)

- What Are The Differences Between SIMULATION and SYNTHESISDocumento12 páginasWhat Are The Differences Between SIMULATION and SYNTHESISiyanduraiAinda não há avaliações

- CS LabDocumento15 páginasCS LabEncom InternationalAinda não há avaliações

- EE 2174 Lab 2 - Designing Digital Circuits Part 1Documento5 páginasEE 2174 Lab 2 - Designing Digital Circuits Part 1notdrphilAinda não há avaliações

- Lab 6Documento7 páginasLab 6Koteswara Rao VaddempudiAinda não há avaliações

- Introduction To Computer ArchitectureDocumento23 páginasIntroduction To Computer ArchitectureLwanga Charles Chas100% (1)

- A Beginner's Guide To Programming Digital Audio Effects in The KX Project EnvironmentDocumento15 páginasA Beginner's Guide To Programming Digital Audio Effects in The KX Project EnvironmentEsteban BikicAinda não há avaliações

- COA Lab Manual Experiment 1 PDFDocumento5 páginasCOA Lab Manual Experiment 1 PDFhimanshicAinda não há avaliações

- Lecture 12: More On Registers, Multiplexers, Decoders, Comparators and Wot-NotsDocumento5 páginasLecture 12: More On Registers, Multiplexers, Decoders, Comparators and Wot-NotsTaqi ShahAinda não há avaliações

- Glosario InglésDocumento10 páginasGlosario InglésLorena MonroyAinda não há avaliações

- Lecture 12: More On Registers, Multiplexers, Decoders, Comparators and Wot-NotsDocumento5 páginasLecture 12: More On Registers, Multiplexers, Decoders, Comparators and Wot-NotsrinobiAinda não há avaliações

- DocxDocumento20 páginasDocxmutindaAinda não há avaliações

- Sequential Prog. Lec 1Documento39 páginasSequential Prog. Lec 1aabdurrahaman647Ainda não há avaliações

- Digital Image Filter DesignDocumento6 páginasDigital Image Filter DesignKatia Rania BITAMAinda não há avaliações

- Verilog Interview Questions & Answers For FPGA & ASICDocumento5 páginasVerilog Interview Questions & Answers For FPGA & ASICprodip7Ainda não há avaliações

- Debugging: Catch Use of Assignment Operator Instead of Equality OperatorDocumento8 páginasDebugging: Catch Use of Assignment Operator Instead of Equality OperatorKashaan MahmoodAinda não há avaliações

- MPS Lab Ex5-MemoryDocumento10 páginasMPS Lab Ex5-Memoryअमरेश झाAinda não há avaliações

- Threads Locks UsageDocumento16 páginasThreads Locks UsagesimlulirduAinda não há avaliações

- Final Project DescriptionDocumento3 páginasFinal Project DescriptionVanlocTranAinda não há avaliações

- Pipelining Instruction Execution and Cache Memory PoliciesDocumento10 páginasPipelining Instruction Execution and Cache Memory PoliciesDinesh DevaracondaAinda não há avaliações

- Analog SimulationDocumento9 páginasAnalog SimulationMotaz Ahmad AmeenAinda não há avaliações

- Advanced Digital Systems DesignDocumento12 páginasAdvanced Digital Systems DesignlawrencerajasekaranAinda não há avaliações

- Master SetDocumento624 páginasMaster SetEr Lokesh MahorAinda não há avaliações

- Assignment#1 DbmsDocumento8 páginasAssignment#1 DbmsНурбике СаитоваAinda não há avaliações

- PLDTUTORDocumento13 páginasPLDTUTORAjay Nath S AAinda não há avaliações

- How To Write FSM Is VerilogDocumento8 páginasHow To Write FSM Is VerilogAyaz MohammedAinda não há avaliações

- UWI ECNG 3016 Lab - Frequency Divider & Time Mux DisplaysDocumento10 páginasUWI ECNG 3016 Lab - Frequency Divider & Time Mux DisplaysMarlon BoucaudAinda não há avaliações

- MidtermDocumento5 páginasMidtermkhaledmosharrafmukutAinda não há avaliações

- Digital Logic and Microprocessor CourseDocumento5 páginasDigital Logic and Microprocessor CourseYash KAinda não há avaliações

- Calculator Tutorial: The Basics: High-Precision Scientific CalculatorDocumento10 páginasCalculator Tutorial: The Basics: High-Precision Scientific CalculatorAnonymous 2SQDbt2Ainda não há avaliações

- CSE 110 Homework 2Documento1 páginaCSE 110 Homework 2salmanshokhaAinda não há avaliações

- Nvidia Placement PaperDocumento4 páginasNvidia Placement PaperSaurabh Verma100% (2)

- Sequential Parallel Algorithms For Big-Integer PDFDocumento7 páginasSequential Parallel Algorithms For Big-Integer PDFOleg FarenyukAinda não há avaliações

- STMW Internet_of_Things_Lab_manualDocumento50 páginasSTMW Internet_of_Things_Lab_manualthummalakuntasAinda não há avaliações

- Lab 7Documento6 páginasLab 7Minh NamAinda não há avaliações

- SampleExamSolutions 2upDocumento7 páginasSampleExamSolutions 2upspikysimAinda não há avaliações

- Lab Project: Shift-and-Add Multiplication Circuit With StorageDocumento5 páginasLab Project: Shift-and-Add Multiplication Circuit With StoragesneophAinda não há avaliações

- VLSI Interview QuestionsDocumento7 páginasVLSI Interview QuestionsVlsi GuruAinda não há avaliações

- Subiect EngDocumento3 páginasSubiect EngVictoria IacobAinda não há avaliações

- Task 1: You Need To Do Only 1 Task. Feel Free To Do All of Them, It Might Be A Good Learning OpportunityDocumento9 páginasTask 1: You Need To Do Only 1 Task. Feel Free To Do All of Them, It Might Be A Good Learning OpportunityMARIA FERNANDA MARTINEZ VAZQUEZAinda não há avaliações

- O Level Computer Science Hardware & Software WorkbookDocumento109 páginasO Level Computer Science Hardware & Software WorkbookTrynosAinda não há avaliações

- CS211 Test 1 Solution S1 2022Documento7 páginasCS211 Test 1 Solution S1 2022Jerold YangAinda não há avaliações

- Difference between new() and new in SystemVerilogDocumento9 páginasDifference between new() and new in SystemVerilogAshwini PatilAinda não há avaliações

- Fiches TDDocumento28 páginasFiches TDDounia PnlaAinda não há avaliações

- Lab 3Documento6 páginasLab 3anonymous bunnyAinda não há avaliações

- Logic Circuits Design FundamentalsDocumento52 páginasLogic Circuits Design FundamentalsMubeen NaeemAinda não há avaliações

- Tutorial ProjectDocumento16 páginasTutorial ProjectMuhammadNizarArifansyahAinda não há avaliações

- Lab 5 DSP and FPGA Embedded Resources Signal Filtering and DisplayDocumento5 páginasLab 5 DSP and FPGA Embedded Resources Signal Filtering and DisplayZisa KrageAinda não há avaliações

- Logic Circuits and Switching Theory Module 1 ReviewDocumento15 páginasLogic Circuits and Switching Theory Module 1 ReviewRhea Daluddung SanchezAinda não há avaliações

- Practice Assignment No-4Documento8 páginasPractice Assignment No-4Seemab RamzanAinda não há avaliações

- Man-In-The-Middle-Attack: Understanding in Simple Words: Avijit MallikDocumento26 páginasMan-In-The-Middle-Attack: Understanding in Simple Words: Avijit MallikSul SyaAinda não há avaliações

- Releasenotes FR FRDocumento9 páginasReleasenotes FR FRdadjudadju11Ainda não há avaliações

- Schools Division of Parañaque City TLE - Electrical Installation & Maintenance 9 Quarter 4 Week 3 & 4 Electrical ToolsDocumento4 páginasSchools Division of Parañaque City TLE - Electrical Installation & Maintenance 9 Quarter 4 Week 3 & 4 Electrical ToolsWinsher PitogoAinda não há avaliações

- Advanced e-Voting Project ReportDocumento7 páginasAdvanced e-Voting Project ReportEducation Tech PoolAinda não há avaliações

- Tamilnadu Food Ind PDFDocumento150 páginasTamilnadu Food Ind PDFdeva nesan100% (4)

- FNPT Screening: 3. Power Tabelle FNPT / Flap SettingDocumento3 páginasFNPT Screening: 3. Power Tabelle FNPT / Flap SettingMarian GrigoreAinda não há avaliações

- List of Program Using FunctionDocumento3 páginasList of Program Using FunctionKanchan KhuranaAinda não há avaliações

- Samsung M31Documento1 páginaSamsung M31mahmudhassanAinda não há avaliações

- ROX PVPCalcAA Crit FalconDocumento6 páginasROX PVPCalcAA Crit FalconGanorienAinda não há avaliações

- Sirena WT4911 ManualDocumento32 páginasSirena WT4911 ManualMateescu CristianAinda não há avaliações

- Proposal On Online Bookstore SystemDocumento12 páginasProposal On Online Bookstore Systembishan sxthaAinda não há avaliações

- Techniques and Tools For Software Analysis: Freescale SemiconductorDocumento7 páginasTechniques and Tools For Software Analysis: Freescale SemiconductorjohnAinda não há avaliações

- Guru Nanak Dev UniversityDocumento17 páginasGuru Nanak Dev UniversityAnimesh salhotraAinda não há avaliações

- ASCET-RP V6.4 Users GuideDocumento177 páginasASCET-RP V6.4 Users GuidecqlAinda não há avaliações

- A Deep Learning Model Based On Concatenation Approach For The Diagnosis of Brain TumorDocumento10 páginasA Deep Learning Model Based On Concatenation Approach For The Diagnosis of Brain Tumorhamed razaAinda não há avaliações

- Deltek First Vision Essentials: Administrator GuideDocumento65 páginasDeltek First Vision Essentials: Administrator Guidesivas.onlineAinda não há avaliações

- Terminology Introduction 1Documento18 páginasTerminology Introduction 1Paula ChenaAinda não há avaliações

- Altec Lansing ACS54 4.1 Speaker System - User ManualDocumento4 páginasAltec Lansing ACS54 4.1 Speaker System - User ManuallockhimupasapAinda não há avaliações

- Chapter 7Documento16 páginasChapter 7YvesExequielPascua100% (2)

- CommInsights Issue6 It S All About ContentDocumento40 páginasCommInsights Issue6 It S All About ContentLucijano Andreas SoftićAinda não há avaliações

- Google Forms Tutorial - Part 1 Create Online SurveysDocumento71 páginasGoogle Forms Tutorial - Part 1 Create Online SurveysMuhammad Adhi WikantyosoAinda não há avaliações

- MPEG Encoding BasicsDocumento7 páginasMPEG Encoding BasicsUnderseen100% (2)

- Isaca: Cobit Assessment Programme (PAM) Tool Kit: Using COBIT 5Documento2 páginasIsaca: Cobit Assessment Programme (PAM) Tool Kit: Using COBIT 5lgaleanoc0% (1)

- SWEG3091 Software Architecture DesignDocumento65 páginasSWEG3091 Software Architecture Designsibhat mequanintAinda não há avaliações

- Oph3W: Technical DataDocumento2 páginasOph3W: Technical DataArdhan BoyzzAinda não há avaliações

- QAF5180 Rev0 First Aid Kit Inventory Sheet - ARAMCO TYPEDocumento1 páginaQAF5180 Rev0 First Aid Kit Inventory Sheet - ARAMCO TYPEMohamed El-SawahAinda não há avaliações

- ZTWS AssignmentsDocumento1 páginaZTWS AssignmentsPushkar Joshi100% (1)

- Looking at The Future of Manufacturing Metrology R PDFDocumento7 páginasLooking at The Future of Manufacturing Metrology R PDFAdven BrilianAinda não há avaliações

- Railway Applications - Welding of Railway Vehicles and Components - Part 3: Design RequirementsDocumento14 páginasRailway Applications - Welding of Railway Vehicles and Components - Part 3: Design Requirementsram venkatAinda não há avaliações

- High-Shear Mixer: Principles of WorkDocumento2 páginasHigh-Shear Mixer: Principles of WorkGulzar HussainAinda não há avaliações