Escolar Documentos

Profissional Documentos

Cultura Documentos

Processador Simplificado - Parte III

Enviado por

Diego Ascanio SantosDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Processador Simplificado - Parte III

Enviado por

Diego Ascanio SantosDireitos autorais:

Formatos disponíveis

Parte III

As partes anteriores deste projeto apresentaram a estrutura de um processador simples. A

parte I apresentou o projeto e na parte II o processador foi conectado a um contador externo e a

uma unidade de memória. Nesta nova etapa serão descritas outras partes do projeto deste

processador.

O primeiro passo é a extensão do processador de maneira que um contador externo não

seja necessário e que e adição da habilidade de realização de operações de leitura e escrita

usando dispositivos de memória. Serão adicionados três novos tipos de instruções ao processador

conforme apresentado na tabela 1. A instrução ld(load) carrega no registrador RX o dado

encontrado na memória na posição encontrada no registrador RY. A instrução st(store) armazena

o dado contido no registrador RX na posição de memória cujo endereço está no registrador RY.

Finalmente, a instrução mvnz(move if not zero) permite que a operação mv seja executada

somente sob a condição de que o conteúdo do registrador G não seja igual à 0.

Operação Função Realizada

ld Rx, [Ry] RX ← [[RY]]

st Rx, [Ry] [Ry] ← [Rx]

mvnz Rx, Ry if G != 0, Rx ← [RY]

Tabela 1

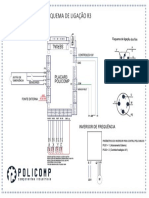

Um diagrama esquemático do processador aprimorado é dado na figura 1. Os

registradores R0 a R6 são os mesmos da implementação do processador simples, mas o R7 foi

substituído por um contador. Este é usado para prover o endereço de memória em que o

processador busca sua instrução e será citado como o contador do programa (PC). Quando o

sinal reset do processador é ativado o PC é setado com o valor 0. No início de cada instrução (no

passo de tempo 0) o conteúdo do PC é usado como um endereço para a leitura de uma instrução

encontrada na memória. A instrução é então armazenada no IR e o PC é automaticamente

incrementado para o endereço da próxima instrução (no caso de um mvi o PC provê o endereço

do dado e então é incrementado novamente).

A unidade de controle implementa o PC através do uso de um sinal incr_PC que nada

mais é do que um enable para o próprio contador. Também é possível caregar diretamente o

endereço no PC (R7) fazendo com que o processador execute uma instrução mv ou mvi na qual o

registrador de destino seja especificado com R7. Neste caso a unidade de controle realiza um

carregamento paralelo no contador. Desta maneira o processador pode executar instruções de

qualquer endereço da memória. De maneira similar o conteúdo do PC pode ser copiado em

qualquer outro registrador através do uso da instrução mv. Um exemplo de código que utilize o

registrador PC para a implementação de um loop é apresentado abaixo, os textos depois do

caracter "%" são apenas comentários. A instrução mv R5, R7 coloca no R5 o endereço de

memória da instrução sub R4, R2. Então a instrução mvnz R7, R5 provoca a execução da

instrução sub até que o valor em R4 seja 0.

mvi R2,#1

mvi R4,#10000000 % binary delay value

mv R5,R7 % save address of next instruction

sub R4,R2 % decrement delay count

mvnz R7,R5 % continue subtracting until delay count gets to 0

A figura 1 mostra dois registradores no processador que são usados para transferência de

dados. O registrador ADDR é usado para enviar o endereço à um dispositivo externo como um

módulo de memória, por exemplo, e o registrador DOUT é usado pelo processador para prover

os dados que serão armazenados fora do processador. Um dos usos do registrador ADDR é para

a leitura ou busca de instruções da memória; quando o processador precisa buscar uma instrução,

o conteúdo do PC (R7) é transferido no barramento e carrehado em ADDR. Este endereço é

então provido à memória. Além da busca de instruções, o processador pode ler dados de

qualquer posição de memória através da utilização deste mesmo registrador ADDR. Tanto dados

quanto instruções são recebidos no processador pela entrada DIN. O processador pode escrever

dados em um dispositivo externo através do armazenamento do endereço no registrador ADDR,

do armazenamento dos dados no registrador DOUT e da habilitação do sinal W (write).

A figura 2 ilustra como este processador aprimorado é conectado à memória e a outros

dispositivos. A unidade de memória da figura suporta operações de leitura e escrita, possui

entrada de dados e de endereço e também uma entrada que ative a escrita. Além destes sinais, a

memória possui uma entrada de clock porque os dados são carregados quando há uma borda

ativa do sinal de clock. Este tipo de memória é geralmente chamada de synchronous random

access memory (synchronous RAM). A figura 2 inclui também um registrador de 16-bits que

pode ser usado para armazenar dados vindos do processador e que por sua vez é conectado à um

conjunto de leds que permitem a apresentação dos dados na placa DE2. Para que seja possivel a

seleção da unidade de memória ou do registrador quando ocorre uma operação de escrita, este

circuito inclui algumas portas lógicas que realizam a decodificação do endereço; se as linhas

A15A14A13A12 = 0000 então será escrito na posição de memória dado pelo endereço nas linhas de

indíce mais baixos. A figura 2 apresenta n linhas de endereço conectadas à memória; para este

trabalho uma memória com 128 palavras é suficiente, o que implica que n=7 e que a porta de

endereço da memória é ligada às linhas A6 ... A0. Quando o endereço começado por

A15A14A13A12 = 0001, então os dados escritos no processador serão carregados no registrador

que tem sua saída ligada nos leds.

Você também pode gostar

- Funções da UCP e componentes de uma CPUDocumento4 páginasFunções da UCP e componentes de uma CPUNatalFonseca0% (2)

- GABARITO ARQ COMP As 2018 2 Questionário 9 Sobre TEMA 9 Videos 24-25-26 Processadores Parte 1Documento7 páginasGABARITO ARQ COMP As 2018 2 Questionário 9 Sobre TEMA 9 Videos 24-25-26 Processadores Parte 1Yoshino sempaiAinda não há avaliações

- Aula 7 - Exerrcicios de Eletronica Analogica Resolvidos PDFDocumento40 páginasAula 7 - Exerrcicios de Eletronica Analogica Resolvidos PDFJorge Luis Alves Morgado100% (2)

- Exercícios resolvidos de microprocessadoresDocumento9 páginasExercícios resolvidos de microprocessadoresBárbara PulcineliAinda não há avaliações

- Quicksort Externo: ordenação externa in situDocumento8 páginasQuicksort Externo: ordenação externa in situKenner GonçalvesAinda não há avaliações

- Atividade Arquitetura de Computadores - João Victor - 202102104602Documento7 páginasAtividade Arquitetura de Computadores - João Victor - 202102104602João Víctor da Silva Barbosa0% (2)

- Manual Valvula AUMADocumento76 páginasManual Valvula AUMAclebeson_pontal88% (8)

- Implementação de um processador simples em VerilogDocumento13 páginasImplementação de um processador simples em VerilogDiego Ascanio SantosAinda não há avaliações

- Processador ReMember: Especificação de um processador de 8 bitsDocumento7 páginasProcessador ReMember: Especificação de um processador de 8 bitsDaniel FAinda não há avaliações

- Exercicios 3Documento3 páginasExercicios 3Armando inacio PumaAinda não há avaliações

- Programação em Assemblypate1Documento4 páginasProgramação em Assemblypate1bifosoAinda não há avaliações

- Processador Caminho de DadosDocumento35 páginasProcessador Caminho de DadosDenis TaveiraAinda não há avaliações

- Curso Sistemas Informações Arquitetura ComputadoresDocumento5 páginasCurso Sistemas Informações Arquitetura ComputadoresLuciano SilvaAinda não há avaliações

- RiSC-16 instruction set architectureDocumento5 páginasRiSC-16 instruction set architectureFlávia Nayana AzevedoAinda não há avaliações

- Componentes de HardwareDocumento19 páginasComponentes de Hardwarehenriquetg002Ainda não há avaliações

- Arquitetura do SAP1 - Computador DidáticoDocumento14 páginasArquitetura do SAP1 - Computador DidáticoRenato MilitãoAinda não há avaliações

- Programação em Assemblypate3Documento7 páginasProgramação em Assemblypate3bifosoAinda não há avaliações

- Lista 2Documento5 páginasLista 2FrânsciVieiraAinda não há avaliações

- Microcontroladores e Microprocessadores: Lista de Exercícios sobre 8051Documento8 páginasMicrocontroladores e Microprocessadores: Lista de Exercícios sobre 8051slytheriAinda não há avaliações

- Microcontrolador x HardwareDocumento4 páginasMicrocontrolador x HardwarePrecildo Azevedo JúniorAinda não há avaliações

- MCPDocumento5 páginasMCPHelton Damião BiéAinda não há avaliações

- Relatório - Laboratório 1Documento10 páginasRelatório - Laboratório 1daniel dagostimAinda não há avaliações

- Lista de Exercícios de Arquitetura - Modos de Endereçamento e Chamadas ao SODocumento10 páginasLista de Exercícios de Arquitetura - Modos de Endereçamento e Chamadas ao SOGracyeli GuarientiAinda não há avaliações

- Programa o AssemblyDocumento5 páginasPrograma o AssemblyFelipe BarrosAinda não há avaliações

- Capítulo 06Documento6 páginasCapítulo 06Samuel LeonhardtAinda não há avaliações

- MaquinaNeander PDFDocumento14 páginasMaquinaNeander PDFreh_techAinda não há avaliações

- Ap1 - QuestionárioDocumento5 páginasAp1 - QuestionárioThiago Francisco Paes AlvesAinda não há avaliações

- ManualDocumento5 páginasManualGustavo Garcia de AmoAinda não há avaliações

- Arquitetura e instruções do SAP-2Documento38 páginasArquitetura e instruções do SAP-2deapledAinda não há avaliações

- Quicksort Externo EficienteDocumento9 páginasQuicksort Externo EficienteTiago Henrique Vieira PiresAinda não há avaliações

- Registradores de funções especiais do 8051Documento33 páginasRegistradores de funções especiais do 8051Lendione BatistaAinda não há avaliações

- Arquitetura MIPSDocumento16 páginasArquitetura MIPSBruno OgataAinda não há avaliações

- Arquitetura MIPS Multiciclo: Descrição e Organização do ProcessadorDocumento15 páginasArquitetura MIPS Multiciclo: Descrição e Organização do ProcessadorFrancis DiegoAinda não há avaliações

- Primeiro Trabalho Sic XeDocumento8 páginasPrimeiro Trabalho Sic XeAnna Gabriele Marques de OliveiraAinda não há avaliações

- RegistradorDocumento2 páginasRegistradorEle101828Ainda não há avaliações

- Microcontrolador PIC 16F628A em WordDocumento5 páginasMicrocontrolador PIC 16F628A em WordNandoAinda não há avaliações

- Caderno QuestoesDocumento4 páginasCaderno Questoeseduardo veroneses de souzaAinda não há avaliações

- Arquitetura de computadores: registradoresDocumento69 páginasArquitetura de computadores: registradoresRomeu Corradi JúniorAinda não há avaliações

- UFAM relatório laboratório processador VHDLDocumento23 páginasUFAM relatório laboratório processador VHDLnataliaAinda não há avaliações

- 3 Unidade ControleDocumento8 páginas3 Unidade ControleGabriel ChagasAinda não há avaliações

- Cap 4 Caminho de Dados e ControleDocumento62 páginasCap 4 Caminho de Dados e ControleIgor GledsonAinda não há avaliações

- Cap 2Documento39 páginasCap 2Fernando CollAinda não há avaliações

- O Processador: Caminho de Dados e ControleDocumento53 páginasO Processador: Caminho de Dados e ControleRonnie100% (2)

- Modc 3 ProcessadoresDocumento9 páginasModc 3 ProcessadoresMaria ClaraAinda não há avaliações

- Funções de instruções, estados de execução e técnicas de interrupçãoDocumento2 páginasFunções de instruções, estados de execução e técnicas de interrupçãoHERMIL GLAUBER MARGALHO DAX REISAinda não há avaliações

- Principais Componentes MicroprocessadorDocumento19 páginasPrincipais Componentes MicroprocessadorJorge GamboaAinda não há avaliações

- Organização de Computadores - Lista de Exercícios 1Documento4 páginasOrganização de Computadores - Lista de Exercícios 1Junior ShoboyAinda não há avaliações

- Sistemas MicroprocessadosDocumento14 páginasSistemas MicroprocessadosGuilherme FernandesAinda não há avaliações

- Notas de Aula 04 - UFJF - Arquitetura de ComputadoresDocumento19 páginasNotas de Aula 04 - UFJF - Arquitetura de ComputadoresdanielfmmiguelAinda não há avaliações

- Microcontroladores - Timers e ContagemDocumento45 páginasMicrocontroladores - Timers e ContagemIrina PavelAinda não há avaliações

- 1 Lista de exercícios de revisão - microcontroladoresDocumento2 páginas1 Lista de exercícios de revisão - microcontroladoresMarcelo AmaralAinda não há avaliações

- Aula 15 Modulo USBDocumento14 páginasAula 15 Modulo USBLeo SilvaAinda não há avaliações

- SDAC-Arquitetura de MicroprocessadoresDocumento29 páginasSDAC-Arquitetura de Microprocessadoresapinheiro100% (1)

- Modelos de ProgramaçãoDocumento23 páginasModelos de ProgramaçãoRogério RochaAinda não há avaliações

- 03-Organização de ComputadorDocumento17 páginas03-Organização de ComputadorAdalberto MendesAinda não há avaliações

- SD AtividadeLab 09 DatapathDocumento5 páginasSD AtividadeLab 09 DatapathAnelize SalviAinda não há avaliações

- Aula 8 Programacao Do 8085 (Cont.)Documento30 páginasAula 8 Programacao Do 8085 (Cont.)joaoluisjorge4Ainda não há avaliações

- Diagrama Geral de Um Computador - 2009Documento6 páginasDiagrama Geral de Um Computador - 2009RafaelAinda não há avaliações

- MIPS_S: Arquitetura do processador MIPS subsetDocumento14 páginasMIPS_S: Arquitetura do processador MIPS subsetMateus CarvalhoAinda não há avaliações

- WEBCONFERÊNCIA III e IV - Organização e Arquitetura de Computadores (Unid. 3 e 4) v2 - DIGDocumento61 páginasWEBCONFERÊNCIA III e IV - Organização e Arquitetura de Computadores (Unid. 3 e 4) v2 - DIGnetosantosbmAinda não há avaliações

- Algoritmos de Busca no PacmanDocumento4 páginasAlgoritmos de Busca no PacmanDiego Ascanio SantosAinda não há avaliações

- Arquitetura Computadores II Projeto Análise QuantitativosDocumento43 páginasArquitetura Computadores II Projeto Análise QuantitativosDiego Ascanio SantosAinda não há avaliações

- Organização e Arquitetura de Computadores II - Lista IIIDocumento4 páginasOrganização e Arquitetura de Computadores II - Lista IIIDiego Ascanio SantosAinda não há avaliações

- Crimes Bolsonaro Covid documentadosDocumento3 páginasCrimes Bolsonaro Covid documentadosDiego Ascanio SantosAinda não há avaliações

- Transmissor de TV para Ser Usado Com Câmera, DVD, Video k7, ComputadorDocumento3 páginasTransmissor de TV para Ser Usado Com Câmera, DVD, Video k7, ComputadornhcmediaAinda não há avaliações

- Colheitadeira Florestal PotenteDocumento8 páginasColheitadeira Florestal PotenteChagas OliveiraAinda não há avaliações

- Recuperar BootloaderDocumento6 páginasRecuperar BootloadercrboguitarAinda não há avaliações

- Estruturacabosseriais v23-0Documento4 páginasEstruturacabosseriais v23-0monismsantosAinda não há avaliações

- RaspBerry, Arduíno e DisplaysDocumento19 páginasRaspBerry, Arduíno e DisplaysedermadrugaAinda não há avaliações

- Catalogo VDO - 2011 PDFDocumento456 páginasCatalogo VDO - 2011 PDFFelipeNikito100% (2)

- Manual de serviços SM-100Documento89 páginasManual de serviços SM-100drbalanca100% (2)

- Montagem de circuito decodificador BCD para display 7 segmentosDocumento3 páginasMontagem de circuito decodificador BCD para display 7 segmentosCheilaSilvaAinda não há avaliações

- Catálogo e Especificações Série RP1000 1Documento15 páginasCatálogo e Especificações Série RP1000 1Gustavo OliveiraAinda não há avaliações

- Auto MacaoDocumento88 páginasAuto MacaoMoacyr_JrAinda não há avaliações

- Chaves Controladas (IRF640)Documento4 páginasChaves Controladas (IRF640)AntoniaMariaAinda não há avaliações

- Resumo de Navegacao PC Versao 1.0Documento8 páginasResumo de Navegacao PC Versao 1.0vitor.vmAinda não há avaliações

- Apostila MikroC PDFDocumento261 páginasApostila MikroC PDFVinícius Oliveira0% (1)

- CMOS Logic Circuits ExperimentsDocumento21 páginasCMOS Logic Circuits ExperimentsDi OliveiraAinda não há avaliações

- Z80 Eleição TurmaDocumento16 páginasZ80 Eleição TurmaElias Eugenio Machava100% (2)

- Manual de operação para audiômetro digital AVS 500Documento20 páginasManual de operação para audiômetro digital AVS 500aiaiaiaiaiaAinda não há avaliações

- Manual Iselab NovoDocumento42 páginasManual Iselab NovoLuana ZuffoAinda não há avaliações

- Teste Nobreak Sms Slim PDFDocumento6 páginasTeste Nobreak Sms Slim PDFMaiquel MendesAinda não há avaliações

- Como Montar Uma Loja de EletrônicosDocumento7 páginasComo Montar Uma Loja de EletrônicosMarcos Da Luz JúniorAinda não há avaliações

- Transmissor FM CaseiroDocumento4 páginasTransmissor FM CaseiroCarlos RobertoAinda não há avaliações

- Catálogo Easy9 2013-2014Documento26 páginasCatálogo Easy9 2013-2014Franklin CNAinda não há avaliações

- Esquema de ligação R3 USBDocumento1 páginaEsquema de ligação R3 USBJefferson Alcantara GomesAinda não há avaliações

- Electrónica de Rádio: Amplificadores, Osciladores e Sistemas RFDocumento5 páginasElectrónica de Rádio: Amplificadores, Osciladores e Sistemas RFfernandoAinda não há avaliações

- Manual - CA-40Documento34 páginasManual - CA-40dale8Ainda não há avaliações

- Sistema de Telefonia Multipla FDM e TDMDocumento28 páginasSistema de Telefonia Multipla FDM e TDMXavier Luieno MualiloAinda não há avaliações

- TC14A10Documento16 páginasTC14A10cheteubaAinda não há avaliações

- O Anuário do Setor ElétricoDocumento40 páginasO Anuário do Setor ElétricoGleydson RabeloAinda não há avaliações

- All-Products - Esuprt - Laptop - Esuprt - Latitude - Laptop - Latitude-E6410-Atg - Service Manual - PT-BRDocumento52 páginasAll-Products - Esuprt - Laptop - Esuprt - Latitude - Laptop - Latitude-E6410-Atg - Service Manual - PT-BRInacio DimitriAinda não há avaliações