Escolar Documentos

Profissional Documentos

Cultura Documentos

Tutorial Xilinx V 2

Enviado por

Philipe Dias MattosTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Tutorial Xilinx V 2

Enviado por

Philipe Dias MattosDireitos autorais:

Formatos disponíveis

Como utilizar o Xilinx ISE WebPACK

Passo 01: Abrir o Programa Xilinx ISE 9.2i clicando no cone ISE, ou boto Iniciar Programas Xilinx Ise 9.2i Project Navigator.

Passo 02: Clique no menu File, escolha a opo New Project

Passo 02-a: Na janela que aparece: coloque um nome para o projeto. O nome no deve conter espaos e no pode ser igual ao nome do circuito. No utilize acentuao grfica nem a letra . Sugesto: teste Selecione em Top-Level Source Type: Schematic e clique em Next.

Passo 03: Na janela seguinte, como utilizaremos a Placa Basys da Digilent, devemos marcar: Family: Spartan 3E Device: XC3S100E Package: TQ144 Synthesis Tool: XST VHDL / Verilog Simulator: ISE Simulator (VHDL / Verilog) Prefered Language: VHDL

Passo 04: Na caixa Create a New Source, clique em New Source.

Passo 04a: Na janela que aparece, Em Select Source Type selecione Schematic, e em File name digite um nome para o seu circuito. Em seguida clique em Next Clique em Next em todas as caixas seguintes at aparecer a janela Project Summary com uma descrio do projeto, clique em Finish e o programa voltar a janela principal. Pronto seu projeto j est criado.

Passo 05: Agora temos o Design Summary apresentado na janela inicial Xilinx ISE.

Passo 06: Clique na aba com o nome_do_arquivo.sch criado, que est ao lado da aba Design Sumary.

Agora vc pode desenhar o seu circuito Depois Salvar O seguinte passo para testar o circuito: Passo 07: Clique com o boto direito do mouse com o cursor sobre <Meu_arquivo.sch> escolha a opo Use New Source.

Na caixa Select Source Type selecione a opo Test Bench WaveForm e d um nome ao arquivo que ser gerado, clique em Next. O arquivo gerado ter extenso: nome.tbw

Na caixa Associate Source selecione o arquivo que ser associado ao que est sendo gerado e clique Next e depois Finish. Ir aparecer a seguinte janela:

4. Selecione Combinatorial na opo Clock Information. 6. Initial Length of Test Bench 900ns ou 1000 ns. 7. Time scale deixe como ns. 8. Clique finish.

Aparecer a seguinte janela:

Faa todas as possveis combinaes de entrada e salve PA R A SIMUL A R , 1. Verifique se est em Beha vi o r a l Si m u l a t i o n e se o arqui v o. t b w

est selecionado em Sou r c e s .

Na parte Proce s so s (na parte de baixo de sou rce s ) d duplo clique em Si m u l a t e Beha v i o r a l Model

O programa ir simular seu circuito:

Verifique se a tabela verdade est correta. Estando correta, volte para Sy n e s t h e s i s/I m p l e m e n t a t i o n (o primeiro).

Na janela Processes clique em + User Constraints. Em seguida d um duplo clique em Assign Package Pins.

Clique em YES e abrir uma nova janela Xilinx PACE. Em Design Object List I/O Pins, no campo Loc escolha os pinos para cada entrada e/ou sada, de acordo com o esquema eltrico da Placa Basys.

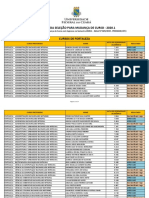

Voc ir atribuir as entradas e as sadas de acordo com a tabela abaixo: Sendo os SW as entradas e os LED s , as sadas.

Exemplo

Em seguida clique em Salvar. Em seguida clique em Ok. E por fim feche a janela.

Fig. 14 Finalizando a criao dos pinos de I/O J no Xilinx, d um duplo clique em Implement Design na Janela Processes:

Fig. 15 Compilando o cdigo aps a determinao do pinos de I/O

O arquivo est funcionando perfeitamente bem. Agora para gerar o arquivo .bit para ser usado na placa Basys, d um duplo clique em Generate Programming File e feche a Janela que aparecer, usando a opo Decline

Fig. 16 Gerando o arquivo.bit para utiliz-lo na placa Basys

Pronto. Temos nosso arquivo.bit para ser gravado na Placa Basys.

Agora abra o Digilen t ExPo r t :

Aps abrir o Digilen t ExPo r t , clique em Initialize Chai n :

Ir aparecer a seguinte tela:

Clique em FP G A e depois em Bro w s e ... V na pasta onde o projeto foi criado e selecione o seu projeto seup r o j e to.bi t ABR I R

Depois disso feito, clique em Progr a m e Chai n

O seu programa j est pronto e gravado na placa. Agora teste o comportamento de seu circuito.

Você também pode gostar

- Regras Netiqueta CNJDocumento4 páginasRegras Netiqueta CNJLuiz X Mariane NascimentoAinda não há avaliações

- IHC Atividade 1Documento9 páginasIHC Atividade 1wolfleoAinda não há avaliações

- Edital Verticalizado DPE RS Conhecimentos Básicos para Todos Os CargosDocumento6 páginasEdital Verticalizado DPE RS Conhecimentos Básicos para Todos Os CargosRenata ConradoAinda não há avaliações

- DIMEP - MinipointDocumento3 páginasDIMEP - MinipointFábio Marques50% (2)

- Desenvolvendo Soluções Com Visual Foxpro 8 e 9Documento5 páginasDesenvolvendo Soluções Com Visual Foxpro 8 e 9luiz santosAinda não há avaliações

- Organização e Funcionamento Do ComputadorDocumento9 páginasOrganização e Funcionamento Do ComputadorJovanijr0% (1)

- Apostila C++ EssencialDocumento43 páginasApostila C++ EssencialDenise J CamargoAinda não há avaliações

- Projeções MongeanasDocumento21 páginasProjeções MongeanasJuliana.MarysAinda não há avaliações

- Análise SWOT - Projeto de PesquisaDocumento8 páginasAnálise SWOT - Projeto de PesquisawildemannAinda não há avaliações

- Aula 05 - Introducao ArduinoDocumento35 páginasAula 05 - Introducao ArduinoBRASIL , SELVA ORDEM E PROGRESSOAinda não há avaliações

- LEX e YACCDocumento9 páginasLEX e YACCGleiserpbAinda não há avaliações

- COMPUTACAO GRaficaDocumento12 páginasCOMPUTACAO GRaficaOrisvaldo PontaziaAinda não há avaliações

- LISTA DE EXERCÍCIOS 1a Prova Parcialmente RespondidoDocumento4 páginasLISTA DE EXERCÍCIOS 1a Prova Parcialmente RespondidoJez CasAinda não há avaliações

- Apostila Abende EvsDocumento2 páginasApostila Abende EvsRScarlate100% (1)

- Matemática IIDocumento1 páginaMatemática IIAlan Wallacy0% (1)

- IVAN - Portfólio AtualizadoDocumento22 páginasIVAN - Portfólio AtualizadoivancgctbaAinda não há avaliações

- Apresentaçao BC e ECODocumento31 páginasApresentaçao BC e ECOgoaldmAinda não há avaliações

- Modificador de FraseDocumento2 páginasModificador de FraseRúben CastroAinda não há avaliações

- 01 - Relatório - Reta em Papel Milimetrado, Monolog e DilogDocumento9 páginas01 - Relatório - Reta em Papel Milimetrado, Monolog e DilogFelipe Portilho SilvaAinda não há avaliações

- Resultado Edital 029 2019 Mudanca de CursoDocumento14 páginasResultado Edital 029 2019 Mudanca de CursoDostoiuvskiAndradeAinda não há avaliações

- Trabalho Final: Banco de DadosDocumento4 páginasTrabalho Final: Banco de DadosAcademicosTIAinda não há avaliações

- Códigos de Programação TdmaDocumento0 páginaCódigos de Programação TdmaSergio Lemos HermsdorffAinda não há avaliações

- Descritivo de PDMDocumento1 páginaDescritivo de PDMANTONIO LUIZ DE O. S. ISABELAinda não há avaliações

- Mapa Da Jornada Do Cliente - TemplateDocumento1 páginaMapa Da Jornada Do Cliente - TemplateVincentbAinda não há avaliações

- Como Baixar Arquivos Sem Limites de Tempo Ou LocalizacaoDocumento5 páginasComo Baixar Arquivos Sem Limites de Tempo Ou LocalizacaoAynna KeltAinda não há avaliações

- Ficha Trabalho InternetDocumento2 páginasFicha Trabalho InternetJoana RochaAinda não há avaliações

- Questionário 1Documento2 páginasQuestionário 1jganascimentoAinda não há avaliações

- DI MANUAL TOTVS Educacional BackOffice Protheus - Integrações - TDNDocumento46 páginasDI MANUAL TOTVS Educacional BackOffice Protheus - Integrações - TDNLuciano Silva de SouzaAinda não há avaliações

- Adafruit IO - Uma Nova Plataforma de IoT - FilipeFlopDocumento21 páginasAdafruit IO - Uma Nova Plataforma de IoT - FilipeFlopEverton Klinger Sousa SilvaAinda não há avaliações