Escolar Documentos

Profissional Documentos

Cultura Documentos

GuiaResumido-Quartus II 91 Corrigida v1.1 FPGA Cyclone II

Enviado por

AlphinhaDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

GuiaResumido-Quartus II 91 Corrigida v1.1 FPGA Cyclone II

Enviado por

AlphinhaDireitos autorais:

Formatos disponíveis

Tutorial para Criar e Simular Circuitos Digitais

no Altera Quartus(R) II verso 9.1 Verso 1.1

Laboratrio Digital

Marlim Pereira Menezes

Profa. Dra. Liria M. Sato

Prof. Dr. Edson Midorikawa

Departamento de Engenharia de Computao e Sistemas Digitais

Escola Politcnica - USP - Campus So Paulo

2011

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Licena de Uso

Este tutorial tem a finalidade nica e exclusiva para uso educacional sem fins lucrativos, sendo que

sua cpia, parcial ou total, est plenamente autorizada pelos autores.

Este documento um guia rpido que se aplica verso 9.1 do Quartus(R) II para a plataforma

Windows da Microsoft, no intuito de facilitar o aprendizado dos alunos num primeiro contato com

essa ferramenta. O mesmo foi desenvolvido para uso nas aulas prticas das disciplinas Laboratrio

Digital I e II do Departamento de Engenharia de Computao e Sistemas Digitais da Escola

Politcnica da USP, campus Butant.

Sua apresentao ser atravs da utilizao de um simples circuito digital, cujo objetivo

apresentar alguns dos comandos mais bsico do software Altera Quartus(R) II 9.1, que possui um

simulador incorporado. Essa tarefa ser realizada passo a passo.

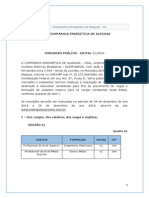

1. Problema proposto

Deseja-se montar e simular o circuito digital, utilizando portas lgicas discretas, representado pela

expresso booleana:

(

utilizando-se a ferramenta Quartus(R) II verso 9.1 da Altera.

A figura 1 mostra o circuito lgico obtido da expresso booleana anterior e, foi desenhado

utilizando-se o software Quartus(R) II 9.1. O objetivo deste tutorial reproduzi-lo, passo a passo da

forma mais simples possvel.

(R)

Figura 1 - Circuito da expresso F(A,B,C,D) modelado no Quartus II 9.1.

-2-

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Certifique-se de que o Altera Quartus(R) II verso 9.1 esteja instalado e pronto para uso no seu

microcomputador.

Passo 1: Iniciando o Quartus(R) II 9.1

Localize o cone de partida do Quartus(R) II na rea de trabalho do Windows, d duplo clique ou

selecione-o com um clique do mouse em seguida pressione a tecla ENTER, ou um clique se o

mesmo estiver na barra de ferramentas. Veja as figuras 2 e 3:

(R)

Figura 2 - cone de partida do Altera Quartus II 9.1 Web Edition na rea de trabalho do Windows.

(R)

Figura 3 - cone de partida do Altera Quartus II 9.1 Web Edition na barra de ferramenta do Windows.

No caso do cone no estar na rea de trabalho, siga um dos roteiros a seguir:

Em Portugus:

Iniciar -> Todos os Programas -> Altera -> Quartus II 9.1 Web Edition -> Quartus II 9.1 Web

Edition (ENTER ou clique simples).

Em Ingls:

Start -> All Programs -> Altera -> Quartus II 9.1 Web Edition -> Quartus II 9.1 Web Edition

(ENTER ou clique simples).

Se aparecer uma janela intitulada Getting Started With Quartus(R) II Software, ento clique com o

boto esquerdo do mouse no "X" localizado no canto superior direito, para fech-la. Aguarde a

janela de Splash sumir e o Quartus(R) II estar pronto para uso.

Passo 2: Criando um projeto digital novo

Criaremos um projeto para o circuito apresentado na figura 1. O nome deste projeto ser tutorial.

Lembrete: Se no se deseja criar um projeto novo, e sim prosseguir o desenvolvimento de um

projeto j existente, ou utilizar um arquivo esquemtico de um circuito j editado, os respectivos

procedimentos esto apresentados na seo Outras Informaes.

-3-

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

File -> New Project Wizard... (na janela New Project Wizard: Introduction) -> Next >;

Aparecer uma sequncia de cinco pginas numeradas, mas no ser necessrio preencher todas

neste tutorial. Para cancelar a criao do projeto, em qualquer momento, basta clicar no boto

Cancel da pgina corrente.

Preencha os campos necessrios ao projeto nas pginas conforme indicado nas linhas que se

seguem:

Tela 1 de 5: New Project Wizard: Directory, Name, Top-Level Entity

Na primeira caixa de texto, clique no boto (

) para escolher uma pasta onde ser

criado o seu projeto, na segunda caixa de texto digite tutorial para o nome do

projeto e, a terceira ser automaticamente preenchida com o texto digitado na

segunda caixa de texto, mas poder ser alterado. Em nosso caso, aceitaremos o

mesmo nome dado ao projeto (tutorial). Veja a imagem na figura 4:

Figura 4: Tela 1 da criao de projeto.

Pressione no boto Next > para avanar;

Tela 2 de 5: New Project Wizard: Add Files

No ser inserido arquivo externo, ento pressione em Next > para avanar;

Pgina 3 de 5: New Project Wizard: Family & Device Settings

Aqui possvel selecionar o FPGA a ser utilizado no projeto durante a sua criao.

Mas, esta opo ser mostrada mais adiante no Passo 4 deste tutorial;

Pressione em Next > para avanar;

Pgina 4 de 5: New Project Wizard: EDA Tool Settings

Ignore esta pgina e pressione em Next > para avanar;

Pgina 5 de 5: New Project Wizard: Summary

Esta pgina contm um resumo das configuraes feitas anteriormente para o

projeto sendo criado;

Pressione em Finish para concluir a criao do projeto.

-4-

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Passo 3: Criando o arquivo para o circuito digital do projeto

Um projeto criado no Quartus(R) II 9.1, normalmente estar vazio, entretanto, deveremos criar os

mdulos que o compe. Nesta seo prepararemos o ambiente de desenvolvimento para receber o

circuito digital que ser simulado. Para isto execute os comandos a seguir:

File -> New (Aparecer uma janela intitulada New);

Design Files -> Block Diagram/Schematic File -> OK, note que a rea direita da janela

principal do Quartus(R) II aparecer com uma grade de pontos (esses pontos so utilizados

como coordenadas da tela para a disposio dos diversos componentes que constituem o

circuito digital).

Na margem esquerda da rea de desenho h uma rgua vertical com alguns botes, que

disponibilizam as opes de projeto tais como a biblioteca dos componentes, caixa de edio de

texto, lupa para zoom etc. Vide figura 5.

(R)

Figura 5 - Rgua de ferramentas de desenvolvimento do Quartus II 9.1.

Passo 4: Escolhendo o FPGA a ser usado no projeto

Para especificar o FPGA que ser usado no projeto execute as seguintes instrues:

Assignments -> Device... (Aparecer a janela Settings); ento selecione:

(Category: Device) -> (Family: Cyclone II) -> (Available devices: Name: EP2C35F672C6) -> OK

(Este chip FPGA foi selecionado porque o que tem no Laboratrio Digital).

-5-

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Para verificar qual o FPGA sendo usado no projeto, basta observar a regio Project Navigator:

Entity, normalmente localizado esquerda do ambiente do Quartus(R) II 9.1. Veja a figura 6.

Figura 6 Project Navigator: Entity com o FPGA selecionado.

Passo 5: Colocando os componentes na rea de desenho

Utilize a figura 1 como referncia, se necessrio.

Execute uma das sequncias de comandos abaixo para abrir a janela Symbol contendo a biblioteca

dos diversos componentes disponibilizados pelo Quartus(R) II 9.1.

[Boto direito do mouse, na rea de desenho] -> Insert -> Symbol... ou;

[Boto direito do mouse, na rea de desenho] -> Insert -> Symbol as Block... ou;

Clique no boto com o desenho de uma porta lgica (

ferramentas da figura 5.

), localizado na rgua de

Na janela Symbol, execute a sequncia de comandos:

Se voc desejar mais de uma cpia do componente selecionado, ento ative o recurso (

) caso contrrio mantenho-o desativado (

). Este recurso

estando ativado no nos impede de colocar apenas uma cpia do componente desejado na rea de

desenho, bastando para isto pressionar a tecla [ESC] ou executando a sequncia de comandos com

o mouse: [Boto direito do mouse] -> Cancel.

Vamos colocar os componentes necessrios ao nosso exemplo na rea de desenho. Para isto,

execute os comandos a seguir:

Uma porta lgica AND de duas entradas:

( ) -> Libraries -> [+] c:/altera/91/quartus/libraries/ -> [+] Primitives -> [+] logic ->

and2 -> OK -> [Boto esquerdo do mouse]

Duas portas lgicas AND de trs entradas:

( ) -> Libraries -> [+] c:/altera/91/quartus/libraries/ -> [+] Primitives -> [+] logic ->

and3 -> OK -> [Boto esquerdo do mouse]

Uma porta lgica OR de trs entradas:

-6-

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

( ) -> Libraries -> [+] c:/altera/91/quartus/libraries/ -> [+] Primitives -> [+] logic ->

or3 -> OK -> [Boto esquerdo do mouse]

Quatro portas inversoras NOT:

( ) -> Libraries -> [+] c:/altera/91/quartus/libraries/ -> [+] Primitives -> [+] logic ->

not -> OK -> [Boto esquerdo do mouse]

Quatro pinos INPUT para as entradas A, B, C e D:

( ) -> Libraries -> [+] c:/altera/91/quartus/libraries/ -> [+] Primitives -> [+] pin ->

input -> OK -> [Boto esquerdo do mouse]

Um pino OUTPUT para a sada FIBO:

( ) -> Libraries -> [+] c:/altera/91/quartus/libraries/ -> [+] Primitives -> [+] pin ->

output -> OK -> [Boto esquerdo do mouse]

Arraste o pino OUTPUT para prximo da sada da porta lgica or3, conforme figura 1.

Vamos girar os quatro pinos de entrada INPUT em 270o, de modo que fiquem com a extremidade

"pontiaguda" para baixo, vide figura 1. Para isto, selecione um pino de cada vez (clicando com o

mouse sobre ele) e execute os seguintes passos:

[Boto direito do mouse] -> Rotate by Degrees -> 270

Repita a operao anterior para girar os quatro inversores em 270o.

Agora reorganize todos os componentes na rea de desenho, de modo a ficarem dispostos como na

figura 1. Pronto, ento salve o projeto em disco, conforme descrito no Passo 6.

Passo 6: Salvando o projeto em disco

boa prtica de desenvolvimento salvar, frequentemente, o projeto ao longo de seu

desenvolvimento. Execute os comandos a seguir:

File -> Save -> (Save as type: Block Diagram/Schematic File (*.bdf)) -> (File Name: tutorial) > (Save in: Tutorial) -> Save.

Passo 7: Dando nomes aos componentes

Para dar nome a um componente basta dar duplo clique sobre o componente desejado e seguir os

passos (use a figura 1 como referncia, se necessrio):

Pinos de entrada: D, C, B, A.

Pin name(s): D -> OK (Na janela "Pin Properties").

-7-

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Pin name(s): C -> OK (Na janela "Pin Properties").

Pin name(s): B -> OK (Na janela "Pin Properties").

Pin name(s): A -> OK (Na janela "Pin Properties").

Pino de sada: FIBO

Pin name(s): FIBO -> OK (Na janela "Pin Properties").

No ser necessrio mudar os nomes das portas lgicas, mas os procedimentos so os mesmos.

Passo 8: Conectando os diversos componentes

Conectar os componentes do circuito (veja a figura 1) muito simples, bastando para isto

posicionarmos o ponteiro do mouse sobre o terminal desejado do componente de origem,

pressionar o boto esquerdo, mant-lo pressionado e arrastar at o ponto ou terminal desejado do

componente destino, soltando-o em seguida. O aspecto do ponteiro do mouse ser uma cruz com o

desenho Fio simples, vide figura 5.

Lembrete: boa prtica de desenvolvimento usando computador SEMPRE salvar o arquivo em

disco, para prevenir contra uma eventual queda de energia ou pane na mquina.

Passo 9: Salvando o arquivo do circuito

Execute os comandos a seguir:

File -> Save (ou [Ctrl+S]).

Passo 10: Compilando o projeto

Uma vez terminado o desenho do circuito, devemos compil-lo, para em seguida fazermos a

simulao. A compilao feita seguindo-se os passos abaixo:

Processing -> Start Compilation, ou um clique no boto indicado na figura 7, da barra de

ferramentas do Quartus(R) II 9.1.

(R)

Figura 7 - Barra de ferramentas do Quartus II 9.1, destacando o boto de compilao.

-8-

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Durante a compilao diversos relatrios so gerados e mantidos disposio do usurio.

Passo 11: Criando a Simulao do projeto

Execute os comandos a seguir, para criar uma simulao:

File -> New -> [+] Verification/Debugging Files -> Vector Waveform File -> OK

Neste momento um arquivo que conter os dados da simulao ser criado e uma janela prpria da

ferramenta de simulao do Quartus(R) II 9.1 ser aberta e ficar pronta para uso. Essa janela

dividida em quatro partes:

Rgua de ferramentas para as configuraes da simulao;

Rgua com as bases de tempo;

Coluna para os nomes dos pontos de teste com a base de tempo e;

rea das cartas de tempo (timing chart) do circuito

Passo 12: Salvando a simulao

Salve o arquivo de simulao com o mesmo nome do projeto, ou seja, tutorial. Para isto execute a

sequncia de comandos a seguir:

File -> Save -> (Save as type: Vector Waveform File (*.vwf)) -> (Save in: Tutorial) -> (File

name: tutorial) -> Save

Passo 13: Incluindo os pontos de teste para a Simulao

Clique o boto direito do mouse sobre a regio dos pontos de teste do circuito simulado (colunas:

Name e Value at). Veja a figura 8:

Figura 8 rea destinada declarao dos pontos de teste do circuito.

Podemos entrar com um ponto de teste de cada vez ou um conjunto, dentre os disponveis, em

uma operao s. Veremos os dois jeitos:

-9-

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Entrando um ponto de teste por vez:

[Boto Diteiro do Mouse] -> Insert -> Insert Node or Bus... -> (Name: A) -> OK

Entrando um conjunto dentre os pontos de teste disponveis ou todos de uma s vez:

[Boto Diteiro do Mouse] -> Insert -> Insert Node or Bus... -> Node Finder... -> (Named: *) > (Filter: Pins: All) -> List -> [>>] -> OK -> OK

Passo 14: Determinando os sinais dos pontos de teste para simulao

No nosso caso temos cinco pontos de teste, isto , quatro variveis de entrada (D, C, B, A) e uma de

sada (FIBO), ento configuraremos os sinais das entradas conforme disposto numa tabela verdade

de quatro variveis, onde 0 indica nvel lgico zero e 1 indica nvel lgico um. Veja a figura 9.

Figura 9 - Pontos de teste para anlise da simulao do projeto.

Siga os passos abaixo: Utilize a regio dos pontos de teste, vide figura 9:

Varivel A (linha 0): [Clique no desenho

(Multiplied by: 1) -> OK

] ->

-> (Radix: Binary) ->Timing ->

Varivel B (linha 1): [Clique no desenho

(Multiplied by: 2) -> OK

] ->

-> (Radix: Binary) ->Timing->

Varivel C (linha 2): [Clique no desenho

(Multiplied by: 4) -> OK

] ->

-> (Radix: Binary) ->Timing->

Varivel D (linha 3): [Clique no desenho

(Multiplied by: 8) -> OK

] ->

-> (Radix: Binary) Timing->->

Deixe o ponto de teste FIBO com a configurao original.

Passo 15: Configurando a simulao

O Altera Quartus(R) II 9.1 tem trs modos de simulao: Functional; Timing e; Timing using Fast

Timing Model.

- 10 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

O default o modo Timing que considera os atrasos internos do tempo no FPGA e ser aqui

adotado.

Na seo Outras Informaes apresentado como proceder para configurar o modo de simulao

Functional.

Vamos configurar o instante final (End Time) e a largura da grade de tempos (Grid Size) da

simulao. Clique na aba tutorial.vwf, para trazer a sua janela ao primeiro plano do ambiente de

desenvolvimento.

Edit -> End Time... -> (Time: 1.0 s) -> OK (Para podermos analisar melhor o

comportamento do circuito)

Edit -> Grid Size -> (Period: 40.0 ns) -> OK

Lembrete: Salve o arquivo com a sequncia de teclas [Ctrl+S] ou executando os comandos do Passo

12.

Passo 16: Executando a simulao

A simulao pode ser iniciada por trs caminhos diferentes:

1. Clique na aba [Quartus II] -> Simulator Tool -> Start -> OK (Janela de Dilogo informando o

resultado da compilao) -> Report;

2. Processing -> Start Simulation -> OK (Janela de Dilogo informando o resultado da

compilao) e;

3. Atravs da rgua de ferramentas, conforme indicado na figura 10.

Caso a simulao tenha sido iniciada a partir do menu (caminho 1) ou pressionando-se o boto em

destaque na figura 10 (caminho 3), ento poderemos visualizar os relatrios (inclusive a carta de

tempos) executando a sequncia de comandos: Processing -> Simulation Report, ou pelo atalho

[Ctrl+Shift+R].

A figura 10 mostra o boto da barra de ferramentas usado para executar a simulao.

(R)

Figura 10 - Boto para iniciar a simulao no Simulador do Quartus II 9.1.

O resultado da simulao mostrado na figura 11:

- 11 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Figura 11 Carta de tempos (Timing Chart) da simulao no modo Timing.

Note que o FPGA escolhido (Clyclone II EP2C35F672C6) apresenta atraso significativo no pino de

sada (FIBO) em relao aos pinos de entrada (A, B, C, D).

Outras Informaes

1. Abrindo um Projeto J Existente

Devemos apenas carreg-lo, executando os comandos a seguir:

File -> Open Project... -> Files of type: Quartus II Project File (*.qpf; *.quartus; *.quar) ->

Look in: Tutorial -> File name: tutorial -> Open

A figura 12 mostra como podemos identificar o projeto carregado e o FPGA selecionado para o

mesmo:

Figura 12 - Projeto carregado e FPGA selecionado.

Para carregar o arquivo com o circuito digital d duplo clique em Nome do projeto corrente,

conforme mostrado na figura 12.

2. Utilizando um Arquivo com Circuito Digital J Editado (*.dbf)

Para utilizar um arquivo de circuito digital j editado (*.dbf) em um projeto novo, execute os

comandos a seguir:

- 12 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Criaremos um projeto para o circuito apresentado na figura 1. O nome deste projeto ser tutorial2

e o arquivo do circuito digital circuito.dbf.

File -> New Project Wizard... (na janela New Project Wizard: Introduction) -> Next >;

Aparecer uma sequncia de cinco pginas numeradas, mas no ser necessrio preencher todas

neste tutorial. Para cancelar a criao do projeto, em qualquer momento, basta clicar no boto

Cancel da pgina corrente.

Preencha os campos necessrios ao projeto nas pginas conforme indicado nas linhas que se

seguem:

Pgina 1 de 5: New Project Wizard: Directory, Name, Top-Level Entity

Na primeira caixa de texto, clique no boto (

) para escolher uma pasta onde ser

criado o seu projeto, na segunda caixa de texto digite tutorial2 para o nome do

projeto e, a terceira dever ser preenchida com o nome do arquivo do circuito digital

a ser aproveitado (circuito.dbf). Veja a imagem na figura 13:

Figura 13 - Criao de projeto novo com incluso do arquivo do circuito editado.

Pressione no boto Next > para avanar;

Pgina 2 de 5: New Project Wizard: Add Files

No ser inserido arquivo externo, ento pressione em Next > para avanar;

Pgina 3 de 5: New Project Wizard: Family & Device Settings

Aqui possvel selecionar o FPGA a ser utilizado no projeto durante a sua criao.

Mas, esta opo ser mostrada mais adiante no Passo 4 deste tutorial;

Pressione em Next > para avanar;

Pgina 4 de 5: New Project Wizard: EDA Tool Settings

Ignore esta pgina e pressione em Next > para avanar;

Pgina 5 de 5: New Project Wizard: Summary

Esta pgina contm um resumo das configuraes feitas anteriormente para o

projeto sendo criado;

Pressione em Finish para concluir a criao do projeto.

Copie o arquivo circuito.dbf para o diretrio do novo projeto (Tutorial2).

- 13 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

3. Configurando o modo da simulao Functional

Para mudar o modo de simulao execute a sequncia de comando, a seguir:

Processing -> Simulator Tool. Veja a figura 14.

Para configurar o modo Funcional, deve-se preencher o modo de simulao com Functional. A

figura 14 , mostra esta configurao.

Figura 14 Modo Functional.

Note que no modo Functional o boto [Generate Functional Simulation Netlist] ficou ativo e esse

deve ser pressionado, para que a simulao neste modo funcione corretamente. Ento, a prxima

sequncia de comandos a ser seguida :

Clique em [Generate Functional Simulation Netlist] -> OK -> Start -> OK -> Report

O resultado da simulao mostrado na figura 15:

Figura 15 Carta de tempos (Timing Chart) da simulao no modo Functional.

Compare as cartas de tempo das figuras 11 e 15. Observe a diferena clara entre os resultados das

simulaes nos modos Timing e Functional.

4. Trabalhando com o Kit de Desenvolvimento Altera DE2

Este item no existia na verso anterior deste tutorial, entretanto foi acrescentado aqui para uso

com o kit de desenvolvimento DE2 da Altera. Esse kit possui um chip FPGA Cyclone II

- 14 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

(EP2C35F672C6) que ser utilizado nas prximas experincias de laboratrio. A figura 16 mostra a

foto da placa de desenvolvimento com a descrio de seus principais componentes.

Figura 16 Kit de desenvolvimento DE2 da Altera.

(Fonte: http://www.terasic.com.tw)

Neste ponto do curso o aluno j deve ter aprendido programar em VHDL, que a linguagem de

descrio de hardware utilizada para a programao e sintetizao de circuitos digitais em

dispositivos FPGA.

4.1. Transformando um circuito digital em um componente

A transformao de circuitos digitais inteiros em simples componente importante para a

diminuio da complexidade do sistema digital sendo projetado, pois isso acarreta na diminuio

de eventuais erros de projeto e, tambm um melhor entendimento da funcionalidade do mesmo

de forma mais abstrata.

Depois de implementado, compilado e testado com o simulador interno um circuito digital pode ser

facilmente transformado em um componente pelo Quartus(R) II de forma extremamente simples,

bastando para isto executar apenas uns poucos comandos como mostrado a seguir:

NOTA: Antes de executar os comandos abaixo certifique-se de estar com a rea de desenho de

circuitos (Block Diagram/Schematic File) ativa com o circuito digital a ser transformado em

componente carregado.

- 15 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Dessa forma, o primeiro circuito digital que transformaremos em componente ser aquele

apresentado na figura 1 deste tutorial e, o segundo ser o mostrado na figura 17, a seguir:

Figura 17 Circuito digital do detector de ao menos dois 1s de 3 bits, a ser transformado em componente.

File -> Create/Update -> Create Symbol Files for Current File

A figura 18 mostra a sequncia de comandos acima aplicada no Quartus(R) II.

(R)

Figura 18 Imagem parcial da janela do Quartus II 9.1 com a sequncia de comandos para a transformao

de um circuito digital em um componente.

- 16 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

A figura 19 mostra a caixa de dilogo para criao de diretrio, nomeao do arquivo

contendo o componente do circuito digital e gravao do mesmo em disco. O arquivo

contendo o componente pode ter qualquer nome e ser gravado no diretrio que o

projetista desejar.

Figura 19 Note que o componente ser gravado no diretrio myLibrary, com o nome fibo_4bit.bsf, diferentes

dos nomes originais.

A figura 20 mostra a caixa de dilogo de sucesso na gerao do componente.

Figura 20 Caixa de dilogo de sucesso na gerao do componente.

A partir deste ponto o componente gerado est pronto para ser utilizado em outros projetos

digitais, conforme a necessidade do projetista. Entretanto, para isto precisamos executar alguns

procedimentos, de modo a fazer com que o mesmo seja reconhecido pelo Quartus(R) II.

- 17 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

4.2. Usando componentes gerados no Quartus(R) II

Criaremos um novo projeto para demonstrar o uso do componente gerado no passo anterior. Para

isto seguiremos os passos j apresentados ao longo deste tutorial, entretanto mostraremos

somente os passos adicionais relacionados incluso dos novos componentes. A figura 21 mostra

as configuraes extras.

Figura 21 Opo no menu para incluso dos diagramas lgicos correspondentes aos componentes gerados no

(R)

Quartus II que sero utilizados no projeto.

A figura 22 mostra a janela para a incluso/remoo de arquivos esquemticos (circuitos digitais

correspondentes aos componentes gerados no Quartus(R) II, usados no projeto).

Figura 22 Janela de incluso/remoo de arquivos esquemticos representativos dos componentes gerados no

(R)

Quartus II, a serem usados no novo projeto.

Nesta tela o usurio deve clicar em (

) e, a partir da caixa de dilogo de seleo de arquivos

selecionar os arquivos esquemticos correspondentes aos componentes gerados no Quartus(R) II e

- 18 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

pressionar o boto (

) para inclui-lo na lista, um de cada vez. Ento, pressionar no boto

(

) para finalizar esta etapa do processo. Usaremos dois novos componentes gerados no

(R)

Quartus II no nosso sistema digital.

A figura 23 mostra como carregar um dos nossos componentes na folha de desenho do Quartus(R)

II. Mas, antes sigas estes passos: na rgua de ferramentas de desenvolvimento pressione em (

e, na janela Symbol pressione em (

) para abrir a caixa de dilogo de seleo de arquivos, em

que o projetista dever abrir o diretrio onde se encontram os componentes criados (geralmente

um diretrio com nome sugestivo como myLibrary, ou minhaBiblioteca, meusComponentes...) e

selecionar o arquivo com o nome do componente desejado, ento pressionar (

seguida pressionar o boto (

), em

) na janela da figura 22.

(R)

Figura 23 Carregando um componente gerado no Quartus II.

Da para frente s seguir os passos que faltam, conforme apresentado anteriormente neste

tutorial. A figura 24 apresenta o sistema digital do nosso projeto de demonstrao do uso de

componentes gerados no Quartus(R) II, aps sua concluso.

(R)

Figura 24 Sistema digital do nosso projeto de demonstrao do uso de componentes gerados nos Quartus II.

- 19 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Nesta figura, o componente tutorial contm o circuito digital da figura 1 deste tutorial e, o

componente detect_1 contm um circuito digital que detecta a ocorrncia de ao menos dois 1s

simultneos na faixa de 3 bits.

Como sugesto, experimente dar duplo clique em ambos componentes tutorial e detect_1 da

figura 24, no ambiente de desenvolvimento do Quartus(R) II e, observe o que acontece.

A figura 25 mostra a carta de tempos no modo Functional para a simulao do nosso sistema digital

mostrado na figura 24.

Figura 25 Carta de tempos do projeto da figura 23, no modo Functional.

4.3. Designando a pinagem do FPGA para o sistema digital no Quartus(R) II

Antes da gravao do sistema digital do projeto no kit de desenvolvimento devemos designar os

pinos correspondentes s entradas e sadas dos sinais no FPGA. Para isto basta executarmos a

sequncia de comandos a seguir.

Assignments -> Pins

Veja estes comandos na figura 26 abaixo:

Figura 26 Comandos para designao dos sinais de entrada e sada do SD nos pinos do FPGA.

Aps a execuo destes comandos aparecer uma janela de edio dos pinos no FPGA, conforme

mostrado na figura 27, a seguir.

- 20 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Figura 27 Janela de designao da pinagem do SD no FPGA.

A imagem colorida nesta figura mapa do FPGA selecionado no qual sero destacados os pinos

correspondentes aos sinais de entrada e sada do SD que foram automaticamente carregados na

regio de baixo da janela, em forma de planilha, pelo aplicativo. Observe as colunas Node Name e

Direction. Para completar a designao da pinagem basta apontarmos cada sinal da coluna Node

Name para uma localizao (Location) do mapa do chip.

Vamos designar alguns componentes (chaves e LEDs) da DE2 aos pinos correspondentes no mapa

de pinagem do FPGA, vide tabela 1 abaixo:

Tabela 1 Designao dos sinais do SD com chaves e LEDs da placa DE2.

Nome do Sinal

Sentido do Sinal

A

Entrada

B

Entrada

C

Entrada

D

Entrada

F

Sada

Y

Sada

- 21 -

Placa DE2

Chave 0

Chave 1

Chave 2

Chave 3

LED Verde 7

LED Vermelho 0

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Tenha em mos (impresso ou digital) o arquivo Altera DE2 Board Pin Table, do qual digitaremos os

nomes dos pinos nas linhas da coluna Location, conforme mostrado na figura 28, a seguir:

Figura 28 Mapa da designao dos pinos do FPGA com os sinais do SD e os componentes da placa DE2.

Lembrete: Mantenha a janela de designao de pinos (Pin Planner) aberta, apenas a minimize.

Volte janela principal do Quartus(R) II e recompile o circuito digital. Note que os nomes dos pinos

designados foram acrescentados ao esquema eltrico do sistema digital do projeto, conforme

mostrado na figura 29.

- 22 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Figura 29 Esquema eltrico do SD depois da designao dos pinos.

NOTA: O processo de compilao j foi apresentado anteriormente, neste tutorial.

4.4. Gravando o sistema digital no FPGA com o Quartus(R) II

Esta etapa consiste na gravao do nosso projeto no FPGA da placa DE2, para testes em tempo real.

Para isto basta executar os comandos a seguir:

Tools -> Programmer

A figura 30 mostra a sequncia de comandos anterior:

(R)

Figura 30 Sequncia de comandos para gravao na placa DE2, usando o Quartus

- 23 -

II.

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

Aps a execuo destes comandos a janela mostrada na figura 31 ser aberta.

(R)

Figura 31 Janela de gravao do Quartus II na placa de desenvolvimento.

Na figura 31, observe que o cdigo objeto do SD gerado pelo Quartus(R) II j foi carregado

automaticamente e, necessrio configurarmos o hardware da placa de desenvolvimento antes de

iniciar a programao da placa DE2. A configurao do hardware feita pressionando-se o boto (

), o qual abrir a caixa de dilogo da figura 32.

Figura 32 Caixa de dilogo de configurao do hardware de desenvolvimento.

Aps selecionar o dispositivo USB-Blaster na caixa de edio Currently selected hardware clique

em (

) para aceitar e retornar janela do programador. Vide figura 33.

- 24 -

Departamento de Engenharia de Computao e Sistemas Digitais Escola Politcnica USP Capital

Tutorial Resumido para uso com o Altera Quartus(R) II 9.1 - Verso 1.1 - 09/2011

(R)

Figura 33 Janela de gravao do Quartus II na placa de desenvolvimento, aps a configurao do hardware.

Na figura 33, no h a necessidade de selecionar o projeto a ser gravado na placa de

desenvolvimento, pois existe somente um. Note que o nome do hardware configurado aparece

direita do boto (

).

Para efetuar a programao da placa de desenvolvimento basta pressionar o boto (

) e o cdigo objeto do SD demoMyComps.sof ser transferido para a memria

SRAM da mesma, vide figura 16.

Aps o envio do cdigo objeto para a programao da placa DE2, o resultado se houve sucesso

aparece como na figura 33, que corresponde barra de progresso da programao Progress (

).

Concluso

Este tutorial procurou iniciar o usurio no Altera Quartus(R) II 9.1 passo a passo, de forma bastante

simples, de modo que o mesmo possa se aperfeioar, por conta prpria, a partir deste ponto.

Foram includas as sees de criao de componentes, designao de pinos e programao da placa

de desenvolvimento Altera DE2.

Referncias

Quartus II Introduction Using Schematic Designs

ftp://ftp.altera.com/up/pub/Altera_Material/10.1/Tutorials/Schematic/Quartus_II_Introduction.pdf

- 25 -

Você também pode gostar

- At - 22 - 2021 - Iluminação - Mercado de Carne - Cajueiro-ModelDocumento1 páginaAt - 22 - 2021 - Iluminação - Mercado de Carne - Cajueiro-ModelAlphinhaAinda não há avaliações

- Matriz 5W2HDocumento3 páginasMatriz 5W2HAlphinhaAinda não há avaliações

- O Que o MestradoDocumento5 páginasO Que o MestradoJullie SantanaAinda não há avaliações

- Edital Ceal Revisao 15122014Documento46 páginasEdital Ceal Revisao 15122014AlphinhaAinda não há avaliações

- Manual Eletrica CADDPROJ S8Documento184 páginasManual Eletrica CADDPROJ S8AlphinhaAinda não há avaliações

- NBR 5419 NB 165 - Protecao de Estruturas Contra Descargas Atmosfericas PDFDocumento32 páginasNBR 5419 NB 165 - Protecao de Estruturas Contra Descargas Atmosfericas PDFjamesantosAinda não há avaliações

- Configurando Linux SambaDocumento1 páginaConfigurando Linux SambaAlphinhaAinda não há avaliações