Escolar Documentos

Profissional Documentos

Cultura Documentos

Detecção de Componentes Ausentes em Placas de Circuito com Visão Computacional

Enviado por

Felipe OliveiraDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Detecção de Componentes Ausentes em Placas de Circuito com Visão Computacional

Enviado por

Felipe OliveiraDireitos autorais:

Formatos disponíveis

Inspeo Visual de Placas de Circuito Integrado com Alta Densidade de

Microcomponentes

Felipe Gomes de Oliveira e Jos Luiz de Souza Pio.

Departamento de Cincia da Computao/ICE Universidade Federal do Amazonas

fgo@dcc.ufam.edu.br josepio@dcc.ufam.edu.br

Abstract

This work presents a visual inspection approach to

detect absence/presence of surface mount components

(SMC) on printed circuit boards (PCB). We propose a

methodology based on Bayesian Statistics to detect

component absence, with more quality and precision,

using noised digital images acquired directly from

PCB industrial production line. The applicability of

method was tested for automatic visual inspection in

motherboards, where the demand of these components

is high. The results obtained demonstrates the

robustness of our methodology in images with high

levels of gaussian and salt and pepper noise, where all

tested cases of component absence are detected.

Key-words: Industrial Inspection, Computer Vision,

Bayesian Statistics.

1. Introduo

Na economia atual as indstrias visam

competitividade. Mas para alcanar tal competitividade

de grande importncia que as indstrias possam

assegurar o aumento da produtividade com a garantia

de qualidade de seus produtos [3].

A principal maneira de se garantir competitividade com

qualidade dispor de um processo de inspeo que

garanta um controle de qualidade rigoroso,

apresentando um mnimo de erros sobre um mximo de

produo. A automatizao do sistema de inspeo

elevaria os nveis de qualidade da indstria de modo

impossvel de se conseguir sem a automatizao. Sendo

os seus resultados almejados por qualquer empresa que

busque competitividade, tais como:

Reduo de desperdcios;

Aumento da lucratividade;

Melhoria da qualidade dos produtos finais.

A inspeo visual convencional, feita por um operador

humano treinado, efetiva para 80% a 90% dos casos

inspecionados e aps meia hora de trabalho apresentam

um decaimento da acuidade visual para um nico

defeito.

Melhorias no controle de qualidade tm sido

alcanadas por meio da inspeo automtica com uso

das tecnologias de viso de mquina [8]. Tendo a

automatizao do processo de inspeo de placas de

circuito impresso se mostrado uma maneira eficiente de

controle de qualidade, uma vez que garante a inspeo

de 100% do volume produzido, no tem interrupo,

no diminui a velocidade da linha de produo,

mantm o fluxo de produo consistente e o volume

inspecionado aumenta consideravelmente [8, 12].

Nesse contexto, este trabalho aborda o problema de

deteco da ausncia (ou da presena) de

microcomponentes de superfcies (SMC) em

dispositivos que utilizam a tecnologia SMD, como as

placas me de computadores pessoais.

O objetivo principal o desenvolvimento de uma

abordagem para a identificao de microcomponentes,

garantindo assim a velocidade, preciso e flexibilidade

do controle de qualidade com competitividade dos

produtos da empresa.

Este texto est organizado em seis sees. A seo

seguinte descreve os sistemas de inspeo visual

automtica e suas aplicaes no contexto deste

trabalho. A Seo 3 oferece uma viso geral do estado

da arte por meio dos principais trabalhos relacionados

com a inspeo de componentes eletrnicos. A

metodologia desenvolvida mostrada na Seo 4. A

seo 5 mostra os resultados experimentais e, por fim,

na Seo 6 so apresentadas as concluses deste

trabalho.

2. Inspeo Visual Automtica em Placas

de Circuito Integrado

Em placas de circuito impresso os componentes de

montagem em superfcie so pequenos e encontram-se

densamente agrupados em posies especficas das

placas de circuito impresso, tornando-se alvo freqente

de defeitos oriundos do processo de Insero

Automtica. Sendo assim a automatizao do processo

de inspeo de placas de circuito impresso surge como

melhoria para o controle de qualidade das empresas.

Os sistemas de inspeo automatizada com Viso de

Mquina atuam sobre os processos de manufatura por

meio de cmeras especiais que capturam as imagens

diretamente da linha de montagem, mesmo em esteiras

que trabalham em altas velocidades. Estas imagens so

digitalizadas em tempo real. Programas de computador

especificamente projetados analisam as imagens em

busca de defeitos, irregularidades e efetuam medies

precisas sobre os objetos visualizados pela cmera.

Baseando-se em sua anlise, esses programas so

capazes de tomar decises acerca de cada pea ou

produto analisado. Estas decises permitem a

implementao de aes corretivas, que podero ser

manuais ou automatizadas.

A Figura 1 ilustra um exemplo tpico de linha de

produo industrial com inspeo automtica por meio

de Viso de Mquina apresentando um controle de

cmera conectado a um computador que realiza o

processamento das imagens.

A Figura 2 mostra um segmento de uma placa me de

computador apresentando componentes ausentes que

so indicados pelas setas.

Neste trabalho desenvolvida uma abordagem para a

deteco da ausncia/presena de microcomponentes

(SMC) em placas de circuito impresso. Pois a ausncia

de componentes uma das principais causas de falhas

nas placas de circuito impresso ao sarem dos fornos de

insero das modernas linhas de produo.

A literatura cientfica muito rica em exemplos de

sistemas de inspeo visual para placas de circuito

impresso [4,7,10]. A maior parte desses trabalhos

tratam problemas relativos a identificao de trilhas de

soldas ou a identificao de componentes mal

posicionados. A seo seguinte destaca os trabalhos

relacionados com a identificao da ausncia de

componentes e oferece uma viso geral do estado da

arte.

3. Trabalhos Relacionados

Figura 1 Linha de produo manufaturada com

inspeo automatizada por meio de um sistema de

viso de mquina [12].

Figura 2 Segmento de placa de circuito impresso

apresentando ausncia de microcomponentes.

Um dos primeiros trabalhos com trilhas de solda em

placas de circuito impresso, foi o desenvolvido por

Borba e Facon [2]. Os autores desenvolveram um

mtodo de inspeo que mesmo sem prvio

conhecimento da placa e sem um padro de referncia,

detecta a falta ou excesso de cobre. Para a

padronizao de defeitos eles usaram trs regras de

inspeo. Segundo os autores, a imagem em escala de

cinza no a melhor soluo, por isso usaram o

conceito de binarizao da imagem. Desde que a escala

de cinza da imagem tenha uma boa resoluo a imagem

binarizada satisfatria e se houver algum rudo fcil

a sua eliminao com filtros. O sistema de captao da

imagem em escala de cinza utilizado composto por

uma caixa com uma fonte interna de luz e uma cmera

captando a imagem. Nesta configurao a cmera no

cria sombras e no existem reflexos e todas as partes

mais importantes da placa podem ser capturadas com

uma boa resoluo de escala de cinza. Como a

abordagem feita em uma placa nua e sem

componentes no temos nenhuma evidncia de como se

comportaria este sistema para detectar ausncia ou

presena de componentes, uma vez, que o sistema de

inspeo no utiliza um template para fazer uma

comparao com a imagem de teste captada.

O sistema desenvolvido por Acciani e Brunetti [1]

baseia-se em um Sistema de Inspeo Visual que

utiliza rede neural com a finalidade de detectar defeitos

encontrados nos terminais de solda nas placas de

circuito integrado. As imagens das placas de testes so

capturadas e processadas para extrair a regio de

interesse do diagnstico. Trs tipos de vetores de

caractersticas so avaliados em cada regio que so a

explorao das propriedades da onda, as caractersticas

geomtricas e o pr-processamento das imagens.

O trabalho de Du e Dickerson [4] apresenta um sistema

de inspeo automtica para componentes passivos,

para localizar componentes, medir seu tamanho e suas

propriedades, suas bordas e detectar defeitos na

superfcie em ambos os lados. Os autores utilizam um

algoritmo para detectar as bordas e os cantos. Por meio

da segmentao da imagem, extrai-se e calculam-se as

caractersticas do componente, como largura, tamanho,

localizao, orientao, etc., e com estas informaes

identifica defeitos, como componentes deslocados,

pontos de ruptura na solda, mau contato na superfcie.

Essa tcnica de inspeo no aborda informaes

quanto ausncia ou presena de componentes, pois na

abordagem que feita, cita a localizao do

componente como uma das caractersticas de

identificao de defeitos.

A pesquisa de Mostafa e Hwang [11] propuseram um

sistema de inspeo para medir as caractersticas

eltricas de uma PCB em um ambiente de manufatura

industrial. Para os autores, este sistema de inspeo

pode atuar on-line, substituindo a pessoa que

inspeciona e sendo de fcil adaptao em quaisquer

outros

sistemas

manufaturados.

O

sistema

desenvolvido baseado no microcontrolador 8031 de 8

bits e dividido em cinco partes a saber: placa de

circuito impresso, aquisio de dados, barramento de

interface, mesa de microswitch e ponta de contatos.

Dois robs so usados para auxiliar no processo. O

primeiro deles pega a placa j montada na mesa

denominada microswitch e coloca na esteira. O

segundo responsvel para fazer as medidas das

caractersticas eltricas da placa na estao de medio.

Como o sistema usa robs para auxiliar na inspeo das

placas, o custo para implementar este sistema

relativamente alto.

Sandra et all. [13] desenvolveu um sistema

automtico de inspeo de terminais de solda nos furos

em PCB. Duas aproximaes so utilizadas, o

reconhecimento de teste padro estatstico e uma

aproximao baseada em conhecimento. Um mtodo

objetivo de reduo de dimensionalidade usado para

realar o desempenho de aproximaes estatsticas

tradicionais de reconhecimento de teste padro,

gerando pesos caractersticos e reduzindo o tempo

computacional. O sistema inteligente e utiliza

caractersticas bem anlogas as que so utilizadas pelos

inspetores na inspeo visual para classificao de

defeitos. Segundo os autores, estas duas aproximaes

comparadas com o desempenho de inspetores humanos

so bem favorveis.

A prxima seo apresenta a metodologia desenvolvida

para a realizao da deteco automtica de

microcomponentes em placas de circuito impresso.

4. Metodologia

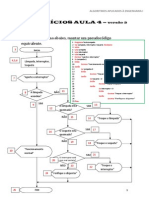

A Metodologia utilizada neste trabalho decomposta

em trs etapas principais, que podem ser observadas

Figura 2. As etapas so:

1. Aquisio das Imagens.

2. Pr-Processamento das Imagens.

3. Classificao Probabilstica da presena/ausncia de

componentes.

Figura 3 Esquematizao da metodologia adotada.

4.1. Aquisio das Imagens

Esse processo consiste na captura de uma imagem

colorida de uma placa de referncia e sequencialmente

na captura das imagens das placas de teste por meio de

uma cmera digital, transferindo ento as mesmas para

um computador. A imagem de referncia tem um papel

fundamental no processo. Sobre esta imagem ser

realizado o processamento de casamento entre as

imagens com a finalidade de encontrar semelhanas

entre os componentes das placas de teste e da placa de

referncia.

4.2. Pr-Processamento das Imagens

Esta etapa pode ser subdividida em procedimentos

menores que so:

Converso das Imagens: As imagens coloridas

capturadas contidas no computador so convertidas

para escala de cinza.

Alinhamento das Imagens: O alinhamento de

imagens pode ser definido como sendo um

mapeamento entre as duas imagens de forma que

essas diferenas sejam minimizadas. As imagens da

placa de referncia e da placa teste so alinhadas de

modo automtico, a fim de solucionar um problema

muito comum nas esteiras, que so as mudanas

sbitas que ocorrem no processo de captao.

Binarizao das Imagens: O processo de binarizao

utilizado, pois segundo [6] o meio mais bvio de

distinguir objetos do fundo por meio da seleo de

um limiar que separe os dois grupos.

Casamento de Padres: Neste procedimento so

feitas comparaes entre os componentes das placas

de referncia e de teste e a mscara binria. A

mscara binria consiste em uma imagem de um

componente ausente com rea hipoteticamente

perfeita, como pode ser observado na Figura 4.

Figura 4 Mscara binria de um componente ausente

[5].

As comparaes entre os componentes e a mscara

binria ocorrem por meio de uma operao lgica and,

podendo ser observado na Figura 5.

Figura 5 Operao lgica and entre um componente e

a mscara binria, para a extrao de rudos adquiridos

na captura da imagem [5].

4.3. Classificao Probabilstica da presena

/ausncia de componentes.

O processo de deciso do algoritmo baseia-se em um

mtodo estatstico de aprendizagem bastante

consolidado na literatura, a Aprendizagem Bayesiana.

A Aprendizagem Bayesiana calcula a probabilidade de

cada hiptese, considerando os dados, e faz previses

de acordo com ela. Isto , as previses so feitas com o

uso de todas as hipteses, ponderadas por suas

probabilidades, em vez de utilizar apenas uma nica

melhor hiptese. Desse modo, a aprendizagem

reduzida inferncia probabilstica. Seja X a

representao de todos os dados, com valor observado

x; ento, a probabilidade de cada hiptese obtida pelo

teorema de Bayes, expresso abaixo:

P(Wi| x) = [P(x| Wi).P(Wi)] / P(x),

onde

2

P(x) = P(x| Wi). P(Wi).

i=1

(1)

(2)

Nessa abordagem do teorema de Bayes so

consideradas as seguintes hipteses:

W1 a hiptese denominada componente (presena).

W2 a hiptese denominada almofada (ausncia).

Sendo P(W1) definida como a razo entre D1/(D1+D2)

e P(W2) definida como a razo entre D2/(D1+D2), onde

D1 a diferena do nmero de pixels brancos do

componente da placa referncia pelo nmero de pixels

brancos da mscara binria e D2 a diferena do

nmero de pixels brancos do componente da placa teste

pelo nmero de pixels brancos da mscara binria.

Estas so as probabilidade a priori das hipteses W1 e

W2 respectivamente.

P(x) representa a freqncia com a qual encontramos

determinada caracterstica, onde considera-se x como

um vetor de caractersticas formado a partir do nmero

de pixels brancos extrados de um componente da

imagem.

A probabilidade P(W1|x) representa a probabilidade que

o componente da placa referncia satisfaa a hiptese

W1 dado a caracterstica x. A probabilidade P(W2| x)

representa a probabilidade que o componente da placa

teste satisfaa a hiptese W2 dado a caracterstica x [9].

Utilizando o teorema de Bayes, queremos determinar

qual a probabilidade do componente est na placa de

teste dado que se sabe a priori que o componente est

na placa referncia. Em outras palavras, deseja-se

determinar P(W2 | x).

Agora supondo que se queira fazer uma previso sobre

uma quantidade desconhecida N de componentes.

Ento temos a seguinte representao matemtica da

aprendizagem bayesiana:

P(x) = P(N| Wi). P(Wi | x),

i

(3)

Onde tm-se que, P(Wi | x) representa o valor

resultante do teorema de Bayes para cada componente

e P(N| Wi) consiste na representao do conhecimento

adquirido pelo mtodo de aprendizagem a cada

componente inspecionado.

5. Resultados Experimentais

Os experimentos realizados visaram mostrar a

aplicabilidade da abordagem para a deteco da

ausncia de componentes em placas me de

computadores pessoais. Para isso foram testadas 25

placas com 300 componentes cada, com componentes

ausentes em diversas posies da placa. Com o ajuste

dos parmetros de probabilidade, foi possvel detectar

todas as ausncias com a realizao automtica do

processo de alinhamento de imagens, onde buscam-se

as coordenadas dos vrtices das placas, com a

finalidade de encontrar pontos de controle que sejam

comuns tanto imagem da placa de referncia quanto

s imagens das placas de teste.

Para avaliar a robustez do mtodo, foram adicionados

rudos Gaussianos e Salt and Pepper imagem, a

fim de simular ambientes com condies crticas para a

aquisio das imagens e podendo assim verificar a

robustez do mtodo quanto a problemas reais

encontrados nas linhas de montagens das indstrias.

Para a adio de rudo Gaussiano foram feitos

experimentos com a densidade de rudo iniciando de

0.01 at 0.08, onde pde-se observar o bom

desempenho do algoritmo, que reconheceu todas as

ausncias da placa com densidade at 0.05.

Para a insero de rudos salt and pepper o mtodo

detectou todas as ausncias iniciando de 0.01 at 0.30

como pode ser observado na Figura 5.

Figura 8 Relao Deteco X Densidade de rudo Salt

and Pepper, mostrando um bom desempenho mesmo

com uma grande concentrao de rudo.

Na Figura 6 pode ser observada a grande perturbao

sofrida pela imagem da placa inspecionada na insero

de rudo salt and pepper com densidade 0.30

(Pixel/U.A), constatando-se a grande complexidade da

abordagem em detectar com boa preciso a

ausncia/presena de microcomponentes em placas de

circuito impresso.

Figura 6 Relao Deteco X Densidade de rudo

Gaussiano, onde observa-se a eficincia da abordagem

at a densidade 0.05.

Na Figura 7 pode ser observada a grande concentrao

de rudo Gaussiano na imagem da placa inspecionada,

com densidade 0.05 (Pixel/U.A), constatando-se a boa

preciso da abordagem em detectar a ausncia/presena

de microcomponentes em placas de circuito impresso.

Figura 9 Placa com densidade de 0.30 de rudo Salt

and Pepper.

6. Concluses

Figura 7 Placa altamente carregada de rudo,

apresentando densidade de 0.05 de rudo Gaussiano.

Este trabalho mostrou uma abordagem metodolgica

para

a

deteco

da ausncia/presena

de

microcomponentes em placas de circuito de SMD.

Utilizou-se a Aprendizagem Bayesiana como

ferramenta principal de deciso para a identificao de

pixels que pertenam ao corpo de um componente ou

que faa parte do rudo adicionado pelo processo ou

dispositivo de captura da imagem. Um avano

importante no trabalho foi a realizao automtica do

alinhamento de imagens, minimizando a interferncia

humana no processo de inspeo. Tambm se destaca a

identificao precisa dos parmetros para a aplicao

da Aprendizagem Bayesiana, que visa adquirir

conhecimento sobre os componentes medida que os

inspeciona, garantindo assim resultados mais precisos e

confiveis.

Para a avaliao da robustez e viabilidade desse

mtodo foram realizados vrios testes com a adio de

rudos Gaussianos e Salt and Pepper, buscando

verificar a robustez da abordagem frente a uma grande

concentrao de rudo nas imagens.

Os resultados obtidos garantem a viabilidade da

utilizao desta abordagem no processo de manufaturas

de placas me. Os experimentos foram realizados em

placas reais obtidas diretamente da linha de produo.

Utilizou-se como imagem de referncia, uma placa

padro usual para comparao nas inspees do

Controle de Qualidade de uma empresa de manufatura

de placas me de computadores pessoais.

Mesmo sendo as imagens submetidas a situaes

extremas de rudo os resultados apresentaram-se

aceitveis dentro do limiar de separabilidade de

probabilidade utilizado, garantindo assim a viabilidade

da abordagem.

A concretizao do trabalho amplia consideravelmente

as possibilidades de aplicao da viso de mquina e da

estatstica Bayesiana para diversos outros tipos de

inspeo industrial.

Como trabalhos futuros pretende-se adequar a

metodologia em ambientes de inspeo visual real e

aprimorar o processo de aprendizagem Bayesiana,

agregando mais informao as caractersticas dos

componentes e provendo ao sistema a deteco

automtica das coordenadas de todos os componentes

por meio da decomposio espacial da placa..

Agradecimentos

Os autores agradecem ao CNPq pelo apoio e

incentivo dado ao projeto de pesquisa o qual este

trabalho vinculado.

Referncias

[1] ACCIANI, Giuseppe; Brunetti, Gioacchino e

Fornarelli, Girolamo. Application of Neural Networks

Optical Inspection and Classification of Solder Joints

in surface Mount Technology, 2006.

[2] BORBA, J.F. e Facon, J. A PRINTED CIRCUIT

BOARD AUTOMATED INSPECTION SYSTEM,

Anais do IEEE Midwest Symposium on Circuits and

Systems, Rio de Janeiro, Brazil, pp. 69-72, Aug. 1996.

[3] DA FONTOURA Costa, L. and Meriaudeau, F.

Special Issue on Applied Visual Inspection, Journal of

Applied Signal Processing, N.7, pginas 647-648,

julho, 2002.

[4] DU, Winncy Y. e Dickerson, Stephen L. Passive

Component Inspection Using Machine Vision, 1998.

[5] GONALVES de Arajo, Wilson. Deteco

Automtica de Componentes de Montagem em

Superfcie sobre Placas de Circuito Impresso. 2008.

Dissertao (Mestrado em Engenharia Eltrica)

Curso de Ps-Graduao em Engenharia Eltrica,

Universidade Federal do Amazonas, Manaus.

[6] GONZALEZ, Rafael C. e Woods, Richard E.

Processamento de Imagens Digitais. Rio de Janeiro.

EDITORA EDGARD BLUCHER, 2000.

[7] HATA, S. Practical Visual Inspection Techniques:

Optics, Micro-electronics and Advanced Software

Technology. Anais da International Conference on

Pattern Recognition 2000, vol. IV, pginas 114-117.

[8] SASAI, M. Inspection Technique for Flexible

Manufacture. Electronic Packaging Technology, vol. 2,

pginas 41-46, 1998.

[9] MARINOVO Doro, Marcos. Sistemtica para

Implantao da Garantia da Qualidade em Empresas

Montadoras de Placas de Circuito Impresso. 2004.

Dissertao (Mestrado em Metrologia) Programa de

Ps-Graduao em Metrologia Cientfica e Industrial,

Universidade Federal de Santa Catarina, Florianpolis.

[10] MARTINEZ, Valguima V. V. A. Odakura_;

Campos, Geraldo Lino. Uma Tcnica para

Alinhamento de Imagens de Documentos Antigos,

2006.

[11] MOSTAFA, Dulal G.M. e Hwang, Santai. Design

of an Inspection System for Electrical Characteristics

of a PC Board, 1993.

[12] PIO, Jos Luiz de S. Viso de Mquina: uma

introduo

aos

sistemas

de

inspeo automatizada, UEA editoras, no prelo, 2007.

[13] SANDRA, B.L. et all. Automatic Solder Joint

Inspection. Ieee Transactions on Pattern Analysis and

Machine Intelligence, Vol. 10. NO.1, JANUARY 1988.

Você também pode gostar

- 3G No LinuxDocumento6 páginas3G No Linuxanderson_alexxAinda não há avaliações

- Baixar Arquivos SWFDocumento2 páginasBaixar Arquivos SWFRogerio VilelaAinda não há avaliações

- Automação Industrial - LivroDocumento117 páginasAutomação Industrial - Livrokaka43Ainda não há avaliações

- Curso de Marketing Digital OnlineDocumento3 páginasCurso de Marketing Digital OnlineCurso de E-CommerceAinda não há avaliações

- Apostila Prática Autocad 2D PDFDocumento30 páginasApostila Prática Autocad 2D PDFalemaneto1056100% (1)

- Compiladores ProvaDocumento11 páginasCompiladores ProvaDavi B.C.Ainda não há avaliações

- Análise Global Do Programa de Prevenção de Riscos Ambientais2Documento10 páginasAnálise Global Do Programa de Prevenção de Riscos Ambientais2arlenemoreira50% (2)

- Leilão de máquinas e equipamentos para indústria calçadistaDocumento12 páginasLeilão de máquinas e equipamentos para indústria calçadistaAnonymous 588rrrwZAinda não há avaliações

- Desligar CapsDocumento7 páginasDesligar CapsDiscípulo Paulo HenriqueAinda não há avaliações

- Livro Eletromecânica FBEDocumento291 páginasLivro Eletromecânica FBEandreia_lopes2398Ainda não há avaliações

- STC ng6 dr3 ft01Documento3 páginasSTC ng6 dr3 ft01Eva PintoAinda não há avaliações

- Mini-Curso Refinamento Rietveld Utilizando GSASDocumento13 páginasMini-Curso Refinamento Rietveld Utilizando GSASandersanti19Ainda não há avaliações

- Software para Estudo de Viabilidade, Aproveitamento Hidrelétrico, Cadastro Multifinalitário.Documento18 páginasSoftware para Estudo de Viabilidade, Aproveitamento Hidrelétrico, Cadastro Multifinalitário.MARIA NELY ALVARENGA LIMAAinda não há avaliações

- Introdução a um Sistema OperativoDocumento3 páginasIntrodução a um Sistema OperativoHugo AmaralAinda não há avaliações

- SR110162 - Carga 094 Remap Light - Casamento Mercedessprinter Processador L52H PDFDocumento13 páginasSR110162 - Carga 094 Remap Light - Casamento Mercedessprinter Processador L52H PDFSimone G. GoularteAinda não há avaliações

- Funções avançadas Excel previsão vendas agrícolaDocumento9 páginasFunções avançadas Excel previsão vendas agrícolaNicholas Vinicius SilvaAinda não há avaliações

- Criptoativos Dados Abertos 03112022Documento90 páginasCriptoativos Dados Abertos 03112022Rodrix DigitalAinda não há avaliações

- Apostila Matemática Cálculo CEFET Capítulo 04 DerivadasDocumento50 páginasApostila Matemática Cálculo CEFET Capítulo 04 DerivadasMatemática Mathclassy100% (1)

- SAVAM - Upload 3.0.0 - SpedDocumento2 páginasSAVAM - Upload 3.0.0 - Spedfabiofiorani.sAinda não há avaliações

- Exercicios Pseudocodigo e Fluxograma Aula 4 v3 GabaritoDocumento7 páginasExercicios Pseudocodigo e Fluxograma Aula 4 v3 GabaritoRonaldo RoqueAinda não há avaliações

- Circuitos Lógicos TTLDocumento7 páginasCircuitos Lógicos TTLGabriela ShimaAinda não há avaliações

- Protocolo de Transporte Simples (STP) para entrega de cartas entre famílias em um planetaDocumento5 páginasProtocolo de Transporte Simples (STP) para entrega de cartas entre famílias em um planetaAna Paula Simiqueli100% (1)

- TI-Nspire CASDocumento289 páginasTI-Nspire CASbrunei952352Ainda não há avaliações

- Teoria dos NúmerosDocumento139 páginasTeoria dos NúmerosCristiane100% (1)

- Resumo - 719100 Luis Telles - 28593405 Raciocinio Logico Certo e Errado Aula 19 Equivalencias III PDFDocumento3 páginasResumo - 719100 Luis Telles - 28593405 Raciocinio Logico Certo e Errado Aula 19 Equivalencias III PDFElvis José100% (1)

- Jogos 2D: Estilos e FormatosDocumento8 páginasJogos 2D: Estilos e FormatosJosemar JuniorAinda não há avaliações

- Manual de Layout TXT-NF-e v4.0.0Documento16 páginasManual de Layout TXT-NF-e v4.0.0danilojdsAinda não há avaliações

- Tutorial The KMPlayerDocumento7 páginasTutorial The KMPlayerEd Carlos de Paula100% (8)

- Aprendizagem significativa AusubelDocumento2 páginasAprendizagem significativa AusubelAndré TavaresAinda não há avaliações

- Como criar formato personalizado no AutoCADDocumento8 páginasComo criar formato personalizado no AutoCADLotharSchmidtAinda não há avaliações