Escolar Documentos

Profissional Documentos

Cultura Documentos

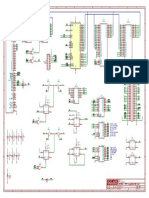

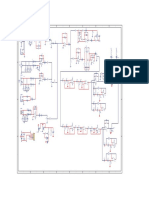

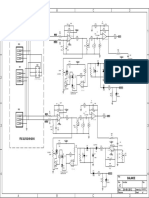

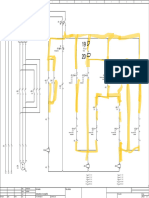

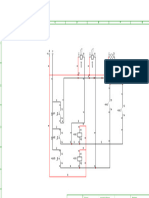

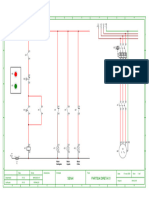

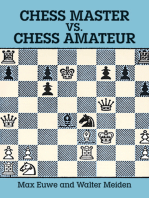

Dragon32 MKII

Enviado por

d.simTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Dragon32 MKII

Enviado por

d.simDireitos autorais:

Formatos disponíveis

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

+5V +5V

C72 C37

C73 C22

R40 R41 R14 R13 100nF 4u7

100nF 100uF +5V

4K7 4K7 4K7 4K7

IC15 C45

40

7

R/W 74LS783 22R D[0..7]

10nF

A 11 Places A

A[0..15] 15 28

VCC

4

VCC

8 A0 Z0 3

20

FIRQ FIRQ A0 R/W Z0 R25

IC31A PL7

IC26

3 9 A1 A0 16 29 Z1 1

IRQ IRQ A1 A0 Z1 R24

74LS02 40 WAY CARD EDGE SOCKET

D[0..7] 6821 KB[0..6] KEYBOARD MATRIX RETURN

NMI

2

NMI A2

10 A2 A1 17 A1 Z2 30 R23 Z2 2

33 2

VCC

D0 KB0

40 11 A3 A2 18 31 Z3 +12V 1 2 +12V D0 PA0

HALT HALT A3 A2 Z3 R22 +12V +12V D1 32 3 KB1 KB0 RIGHT FIRE BUTTON

12 A4 A3 19 32 Z4 HALT 3 4 NMI D1 PA1 +5V

A4 A3 Z4 R21 HALT NMI D2 31 4 KB2

13 A5 A4 21 33 Z5 RES 5 6 E D2 PA2

A5 A4 Z5 R19 6 RES E D3 30 D3 PA3 5 KB3 KB1 LEFT FIRE BUTTON PL3

14 A6 A5 22 34 Z6

IC31B Q 7 8 CART

A6 A5 Z6 R20 4 Q CART D4 29 D4 PA4 6 KB4 R1 Right Joystick

15 A7 A6 23 A6 74LS02 +5V 9 10 D0 +5V

IC19 A7 5 +5V D5 28 7 KB5 100R

16 A8 A7 24 Z[0..6] D1 11 12 D2 D5 PA5 KEYBOARD MATRIX RETURN

6809E A8 A7 D6 27 8 KB6 PL1

17 A9 A8 4 35 D3 13 14 D4 D6 PA6 5 1

A9 A8 Z7/RAS1 R12 RAS1 D7 26 9 +5V KB[0..6] KEYBOARD CONNECTOR L2 +12V R54

18 A10 A9 3 12 D5 15 16 D6 D7 PA7 COMPARATOR +5V +5V

A10 A9 RAS0 R26 RAS0 KB0 1 3u3 R53 1K

34 19 A11 A10 2 11 D7 17 18 R/W C43 4 2

E E A11 A10 CAS R27 CAS R/W 36 40 KB1 2 KB0 10M

35 20 A12 A11 1 10 A0 19 20 A1 A0 RS0 CA1 NHS 10nF +5V

Q Q A12 A11 WE R28 WE 35 39 R38 PL2 3 C38 IC20

16

21 A13 A12 39 A2 21 22 A3 A1 RS1 CA2 SND_SEL0 R55

A13 A12 IC24 4K7 PRINTER PORT KB2 4 10nF 4529

20

8

22 A14 A13 38 A4 23 24 A5 10K

A14 A13 74LS244

3

+5V 1 2 KB3 5 2 X0 Z 9 5

V+

D11 37 14 A6 25 26 A7 STROBE +

VDD

23 A15 A14

A15 A14 E E 22 10 KP0 KP7 2 18 PD7 PD0 3 4 KB4 6 3 7

VCC

1N3592 A15 36 13 A8 27 28 A9 CS0 PB0 1A1 1Y1 X1 COMPARATOR

A15 Q Q 24 11 KP1 KP5 4 16 PD5 PD1 5 6 KB5 7 4 6

V-

A7 PULLDOWN PREVENTS WRITE 5 31 D0 A[0..15] C40 +5V A10 29 30 A11 CS1 PB1 1A2 1Y2 X2 DACOUT _

BS D0

22pF P0

23 CS2 PB2 12 KP2 KP3 6 1A3 1Y3 14 PD3 PD2 7 8 KB6 8 PL5 5 X3

IC25B

TO SAM DURING RESET 6 30 D1 +5V A12 31 32 R2

4

BA D1 R2

PB3 13 KP3 KP1 8 1A4 1Y4 12 PD1 PD3 9 10 KP0 9 Left Joystick LM393

B 33

BUSY D2

29 D2 5 OSCin VCLK 7 VCLK R39 GND

GND 33 34 GND GND B

A7 R/W

21 R/W PB4 14 KP4 KP0 11 2A1 2Y1 9 PD0 PD4 11 12 KP1 10

DACOUT

14 Y0 W 10 SOUND

36

AVMA D3

28 D3

DA0 8 DA0 4K7 EXTSND

EXTSND 35 36 P2 P2 25 15 KP5 KP2 13 7 PD2 PD5 13 14 KP2 11 13

16

+5V 38 27 D4 XL2 9 IC33 A13 37 38 A14 E ENABLE PB5 2A2 2Y2 5 1 CASSND Y1

LIC D4 HS NHS 16 KP6 KP4 15 5 PD4 PD6 15 16 KP3 12 L1 12

R74 D10 39 26 D5 14.218MHz EXTMEM 74LS138 A15 39 40 EXTMEM PB6 2A3 2Y3 EXTSND Y2 R56

TSC D5 EXTMEM 38 17 KP7 KP6 17 3 PD6 PD7 17 18 KP4 13 3u3 11

Not Fitted 1N3597 25 D6 C41 27 1 15 IRQ IRQA PB7 2A4 2Y4 4 2 Y3 10K

VCC

D6 R37 S0 A Y0 MEM 37 19 20 KP5 14 KB1

R15 24 D7 33pF 26 2 14 IRQB ACK BUSY

S1 B Y1

GND

D7 1K5 R0 18 1 KP6 15 C39 6

GND

1N914 6 25 3 13 A[0..15] CB1 FS 1G SND_SEL0 A

VSS

OSCout S2 C Y2 R1 34 19 19 10nF C1 7

BITSND

KP7 16

GND

37 32 D[0..7] 12 RES RES CB2 SND_SEL1 2G SND_SEL1 B

RES RES R/W Y3 R2

3

10nF +5V 1

VSS

11 STX

CRYSTAL / MPU RATE / VSYNC RATE Y4 P0 KP[0..7] 15

20

10

+5V +5V 14.218MHz / 889KHz / 49.97Hz 12 6 10 SND_ENA STY

R/W G1 Y5 P1

1

C23 KEYBOARD MATRIX DRIVE

IC31D 4 9 KP[0..7]

1

14.318MHz / 895KHz / 50.32Hz 13

D5 33uF G2A Y6 P2

GND

74LS02

8

1N914 E

11 5 G2B Y7 7 KEYBOARD MATRIX DRIVE

D6 R36

1N914 100K

8

+5V

+5V

C42

C4 SW1 +5V

D4 10uF

100nF RESET C69 C36

1N914

100nF 100uF

20

IC35 +5V R64

C C

D[0..7] 6821 9 100K

17

VCLK R62

33 2 IC31C

VCC

+5V D0 10 IC34D

VCLK PULLED LOW TO

DD[0..7] D0 PA0 CASIN STROBE 10K

D1 32 3 8 74LS02 DAC5 9 10

PARTIALLY RESET SAM DD0 3 C74 D1 PA1 RLA1

VCC

22

+5V DD0 DA0 DA0 +5V D2 31 4 DAC0 +12V

DD1 4 23 100nF D2 PA2 4050

DD1 DA1 D3 30 5 DAC1

DD2 5

DD2 DA2

24 D3 PA3 R57

D3 PL4

D4 29 6 DAC2 +5V IC34C +5V

IC16 DD3 6 25 IC17 IC18 D4 PA4 20K CASSETTE

20

24

24

DD3 DA3 D5 28 7 DAC3 DAC4 7 6 D1 16V C27

MD[0..7] 74LS244 DD4 7

DD4 DA4

26

A[0..12]

ROM8K A[0..12]

ROM8K D5 PA5

1N914 D2 100nF R50 R49

D6 27 D6 PA6 8 DAC4

R42 R43 R73 R63 R51

MD0 2 18 D0 DD5 8 13 4050

VCC

1A1 1Y1 DD5 DA5 8 9 8 9 26 9 16V 56K 1K

VCC

VCC

A0 D0 A0 D0 D7 DAC5

MD1 4 16 D1 DD6 2 14 A0 D0 A0 D0 D7 PA7 10K 10K 4K7 4K7 R61 1M5

1A2 1Y2 DD6 DA6 A1 7 10 D1 A1 7 10 D1 IC34E 3 1

MD4 6 14 D4 DD7 40 IC12 15 A1 D1 A1 D1 DAC[0..5] 40K

1A3 1Y3 DD7 DA7 A2 6 11 D2 A2 6 11 D2 36 40 DAC3 11 12 R52

MD7 8 12 D7 6847 16 A2 D2 A2 D2 A0 RS0 CA1 ACK R32 5 4 +12V

1A4 1Y4 DA8 CASOUT 56K

C

A3 5 A3 D3 13 D3 A3 5 A3 D3 13 D3

A1

35 RS1 CA2 39 MOTOR 4K7

MD5 11 2A1 2Y1 9 D5 32

INV DA9

18 4050 TR1

A4 4 A4 D4 14 D4 A4 4 A4 D4 14 D4

R58 DACOUT MOTOR

B

MD3 13 7 D3 34 19

8

2A2 2Y2 A/S DA10 A5 3 15 D5 A5 3 15 D5 +5V IC34B BC182 R71

A5 D5 A5 D5

2

MD2 15 5 D2 20 80K 3

2A3 2Y3

V+

DA11 2 16 2 16 22 10 C48 470R R47 R45 +

E

A6 D6 A6 D6 DAC2 5 4

MD6 17 3 D6 21 A6 D6 A6 D6 CS0 PB0 BUSY 1

2A4 2Y4 DA12 A7 1 17 D7 A7 1 17 D7 24 11 22pF 8K2 6K8 CASIN

A7 D7 A7 D7 CS1 PB1 BITSND 4050 2

V-

A8 23 A8 23 23 12 _

1 D[0..7] A8 A8 P1 CS2 PB2 R59 IC25A

GND

1G A9 22 D[0..7] A9 22 D[0..7] 13

4

19 39 36 A9 A9 PB3 CSS R73 PULLUP INDICATES DRAM IS IC34A 160K C44 D7 LM393

MEM 2G CSS CSS RP A10 19 A10 19 21 14 ORGANISED IN 2 x 16K BANKS DAC1 3 2 R46 R48

31 37 A10 A10 R/W R/W PB4 GM0

(PULLDOWN WOULD INDICATE

20nF 1N914

D INT/EXT FS FS A11 18 A11 18 25 15 220R 15K D

ENABLE MEMORY DATA A11 A11 ENABLE PB5

GND

GND

30 38 E GM1 1 x 64K BANK) 4050

10

TO DATA BUS GM0 GM0 HS HS A12 21 20 A12 21 20 16

29 12 A12 E R1 A12 E R0 PB6 GM2 R60

GM1 GM1 MS 38 17

27 FIRQ IRQA PB7 A/G IC34F 330K

GM2 GM2 37 DAC0 14 15

35 IRQB

12

12

A/G A/G 18

+5V 9 CB1 CART

VSS

CHB CHB 34 19 DAC[0..5] 4050 +5V

10 RES RES CB2 SND_ENA

ØB ØB

11 R29

IC13 ØA ØA C35 D9 R31

20

VSS

33 28 68K

MD[0..7] 74LS273 CLK CLK Y LUM 1N914

1

10uF 4K7

MD0 3 D0 Q0 2 DD0

CASOUT CASSND

VCC

MD1 4 5 DD2 Rflying2

D1 Q1

1

MD4 7 6 DD4 15K R16 C26

D2 Q2 D8 R30

MD5 8 9 DD5 33K 2nF

D3 Q3 FLYING RESISOR FITTED 1N914 4K7

MD7 13 D4 Q4 12 DD7 -5V TO REDUCE COLOUR BLEED

MD3 14 D5 Q5 15 DD3

MD1 17 D6 Q6 16 DD1

MD6 18 D7 Q7 19 DD6

11 DD[0..7]

GND

RAS0 Cp

+5V 1 Mr

E E

10

3us PULSE (APPROX) C2

RISING EDGE OF RAS0 CLOCKS MEMORY DATA TO VDG 100nF

(NOTE: FOR 2 x 16K MACHINES, RAS0 IS ONLY ACTIVE +5V C34 C6

R44 SUBSTITUTE ØB FOR ØA DURING BACK PORCH

FOR THE LOWER 16K OF MEMORY. THEREFORE IT'S 330pF 4p7

NOT POSSIBLE TO HAVE A DISPLAY IN THE UPPER 16K) 27K SO THAT CHROMA BURST IS INCLUDED IN

PHASE ALTERNATION R18 +5V

10K C24 C3

15

14

R2

IC11B 47u 33pF

+5V 1K

4053

IC9

RCext

Cext

ALTERNATING PHASE

IC28A 1

1 3 A 13 10 LM1889

HS Cp Q0 Q SEL R17 IC10 IC11C

7

Q1

4

NHS

2

B ØA

2 X 10K SFC2318 4053 1

CHROMA_LEAD CHROMA_LAG

18 C5 R5

Q2

5

ØB

1 Y Z 15 2

-

3 Y Z 4 2

R-Y CHROMA_OSC

17 33pF 1K

V+

2 6 6 5 3 16 R3 XL1

FS Mr Q3 X CHB BIAS CHROMA_SUPP

+5V IC21A 3 9 4 15 2K7 4.433619MHz

V-

74LS393 CHB + SEL ØB B-Y SND_TANK

24 LINE DELAY 74LS123 5 14

GND RF_SUPP

5 STEER VCLK TO VDG 4 +5V C25 6 13

4

IC28B OR LINE PULSE CIRCUIT Q CHB_TANK CHROMA_OUT CHROMA

10

F 13 11 4 FS' IC23B 10nF 7 12 R4 C7 F

Cp Q0 IC27A CHB_TANK VIDEO_IN

Clr

6 9

10 2 74LS74 8 11 3K3 2-22pF

Q1 74LS20 IC14C 8 12 9 12 -5V

CHA_TANK CHA_OUT

D Q IC23A

4

9 1 9 10

Sd

Q2 10 74LS86 IC22D 11 CHA_TANK CHB_OUT -5V

CLK 74LS74

3

12 8 +5V

Mr Q3 11 13 74LS00 2 5 HSYNC DIVIDED BY 2 -5V

Cp VCLK D Q

Sd

74LS393 C28

Cd

8 3 4u7

Q Cp

12

+5V 1 9

Cd

IC14D 11 IC29A 6

13

IC14A 3 +5V IC22C 8 1 3 Q

+5V 13 74LS86 Cp Q0

2 74LS86 10 74LS00 4

VCLK Q1

1

5 +5V

Q2

2 6

+5V Mr Q3

ENA_LP

IC32A 74LS393 DIVIDE VCLK BY 228

1 CKA QA 3 TO CREATE LINE PULSE FREQUENCY

4 CKB QB 5

LINE_PULSES IC29B

QC 6 13

Cp Q0

11 13

+5V

2 7 LINE PULSE TIMING 10 12 C8

Mr QD Q1 IC27B 8 R65

MIX CHROMA & LUMA

9 10 10nF

74LS390 Q2 74LS20 680R AMPLIFY / BUFFER

FS 12 8 9 HSYNC SIGNAL FOR +5V R8

Mr Q3 CHROMA

DIVIDE REST OF SYSTEM 470R

G IC32B BY 50 24L 33L 74LS393 5 G

15 13 HS

CKA QA IC14B 6 R7 R67 +12V

12 11 NHS SELECT LUMA SIGNAL FROM VDG +5V

CKB QB FS' 4 74LS86

OR EXTRA SYNCS FROM

1K 1K2

10 4 C29

QC LINE PULSE CIRCUIT +5V

14 9 6 IC22B 4u7 C9 R9 Rflying1 C11

Mr QD

74LS00 5 3p3 270R 1K 4u7

LINE PULSES VIDEO SIGNAL TO

74LS390 +5V

16

GND IC11A R68 TV MODULATOR

25L 25L OUTPUT LOW ON COUNT 0-15

LINE_PULSES

4053 5K6

E

10

C

IC30C LINE PULSE WIDTH = 4.5us

R34

6 INH TR4

VDD

8 B

11 B TR2 +5V

9 74LS32 R35 8K2 ENA_LP SEL R6 BC212L PL6 PWR_FLAG

2N2369

C

5 1 12

VEE

VSS

12K LUM X 1K2 POWER/VIDEO C12 C13

C

IC30B IC22A 13 14 TR3 +12V

E

6 3 B

Y Z 9 100nF 10uF

4 74LS32 2 2N2369

-5V

1 13 74LS00 8 PWR_FLAG

R70 +5V

E

IC30A IC30D

8

3 11 R33 +5V 7

C46 C47 10R SOUND +5V

2 74LS32 12 74LS32 C71 1K8 R11 R10 VIDEO 6

180pF 180pF

180pF 1K2 3K3 5 PWR_FLAG

RV1

4

10K -5V

3 C10

-5V

R69 2 4u7 PWR_FLAG

+5V

330R 1

DC LEVEL +12V GND

H ADJUST H

-5V

-5V

IC1 IC2 IC3 IC4 IC5 IC6 IC7 IC8

+5V

4116 4116 4116 4116 4116 4116 4116 4116

+12V +5V +12V +5V +12V +5V +12V +5V +12V +5V +12V +5V +12V +5V +12V

8 VDD VCC 9 8 VDD VCC 9 8 VDD VCC 9 8 VDD VCC 9 8 VDD VCC 9 8 VDD VCC 9 8 VDD VCC 9 8 VDD VCC 9

RAS0

Z[0..6] Z[0..6] Z[0..6] Z[0..6] Z[0..6] Z[0..6] Z[0..6] Z[0..6]

I C59 R66

Z0 5 A0 Z0 5 A0 Z0 5 A0 Z0 5 A0 Z0 5 A0 Z0 5 A0 Z0 5 A0 Z0 5 A0 I

33pF 1K5

Z1 7 A1 Z1 7 A1 Z1 7 A1 Z1 7 A1 Z1 7 A1 Z1 7 A1 Z1 7 A1 Z1 7 A1

Z2 6 A2 Z2 6 A2 Z2 6 A2 Z2 6 A2 Z2 6 A2 Z2 6 A2 Z2 6 A2 Z2 6 A2

Z3 12 A3 Z3 12 A3 Z3 12 A3 Z3 12 A3 Z3 12 A3 Z3 12 A3 Z3 12 A3 Z3 12 A3

Z4 11 A4 Z4 11 A4 Z4 11 A4 Z4 11 A4 Z4 11 A4 Z4 11 A4 Z4 11 A4 Z4 11 A4

Z5 10 A5 Z5 10 A5 Z5 10 A5 Z5 10 A5 Z5 10 A5 Z5 10 A5 Z5 10 A5 Z5 10 A5

RAS1 Z6 13 A6 Z6 13 A6 Z6 13 A6 Z6 13 A6 Z6 13 A6 Z6 13 A6 Z6 13 A6 Z6 13 A6

C61 R72 2 14 2 14 2 14 2 14 2 14 2 14 2 14 2 14

D7 Din Dout MD7 D6 Din Dout MD6 D5 Din Dout MD5 D4 Din Dout MD4 D3 Din Dout MD3 D2 Din Dout MD2 D1 Din Dout MD1 D0 Din Dout MD0

33pF 1K5

WE

3 WE WE

3 WE WE

3 WE WE

3 WE WE

3 WE WE

3 WE WE

3 WE WE

3 WE

RAS0

4 RAS RAS0

4 RAS RAS0

4 RAS RAS0

4 RAS RAS0

4 RAS RAS0

4 RAS RAS0

4 RAS RAS0

4 RAS

CAS

15 CAS CAS

15 CAS CAS

15 CAS CAS

15 CAS CAS

15 CAS CAS

15 CAS CAS

15 CAS CAS

15 CAS

16 VSS VBB 1 16 VSS VBB 1 16 VSS VBB 1 16 VSS VBB 1 16 VSS VBB 1 16 VSS VBB 1 16 VSS VBB 1 16 VSS VBB 1

-5V -5V -5V -5V -5V -5V -5V -5V

J J

IC36 IC37 IC38 IC39 IC40 IC41 IC42 IC43

4116 4116 4116 4116 4116 4116 4116 4116

+12V +5V +12V +5V +12V +5V +12V +5V +12V +5V +12V +5V +12V +5V +12V +5V

8 VDD VCC 9 8 VDD VCC 9 8 VDD VCC 9 8 VDD VCC 9 8 VDD VCC 9 8 VDD VCC 9 8 VDD VCC 9 8 VDD VCC 9

Z[0..6] Z[0..6] Z[0..6] Z[0..6] Z[0..6] Z[0..6] Z[0..6] Z[0..6]

Z0 5 A0 Z0 5 A0 Z0 5 A0 Z0 5 A0 Z0 5 A0 Z0 5 A0 Z0 5 A0 Z0 5 A0

Z1 7 A1 Z1 7 A1 Z1 7 A1 Z1 7 A1 Z1 7 A1 Z1 7 A1 Z1 7 A1 Z1 7 A1

Z2 6 A2 Z2 6 A2 Z2 6 A2 Z2 6 A2 Z2 6 A2 Z2 6 A2 Z2 6 A2 Z2 6 A2

Z3 12 A3 Z3 12 A3 Z3 12 A3 Z3 12 A3 Z3 12 A3 Z3 12 A3 Z3 12 A3 Z3 12 A3

Z4 11 A4 Z4 11 A4 Z4 11 A4 Z4 11 A4 Z4 11 A4 Z4 11 A4 Z4 11 A4 Z4 11 A4

Z5 10 A5 Z5 10 A5 Z5 10 A5 Z5 10 A5 Z5 10 A5 Z5 10 A5 Z5 10 A5 Z5 10 A5

Z6 13 A6 Z6 13 A6 Z6 13 A6 Z6 13 A6 Z6 13 A6 Z6 13 A6 Z6 13 A6 Z6 13 A6

D7

2 Din Dout 14 MD7 D6

2 Din Dout 14 MD6 D5

2 Din Dout 14 MD5 D4

2 Din Dout 14 MD4 D3

2 Din Dout 14 MD3 D2

2 Din Dout 14 MD2 D1

2 Din Dout 14 MD1 D0

2 Din Dout 14 MD0

WE

3 WE WE

3 WE WE

3 WE WE

3 WE WE

3 WE WE

3 WE WE

3 WE WE

3 WE

RAS1

4 RAS RAS1

4 RAS RAS1

4 RAS RAS1

4 RAS RAS1

4 RAS RAS1

4 RAS RAS1

4 RAS RAS1

4 RAS

CAS

15 CAS CAS

15 CAS CAS

15 CAS CAS

15 CAS CAS

15 CAS CAS

15 CAS CAS

15 CAS CAS

15 CAS

16 VSS VBB 1 16 VSS VBB 1 16 VSS VBB 1 16 VSS VBB 1 16 VSS VBB 1 16 VSS VBB 1 16 VSS VBB 1 16 VSS VBB 1

K K

-5V -5V -5V -5V -5V -5V -5V -5V

Original design by Dragon Data Ltd

+5V +12V -5V

Captured in KiCad by Stewart Orchard

C50 C70 C14 C15 C16 C17 C18 C19 C20 C21 C49 C51 C52 C53 C54 C55 C56 C57 C58 C60 C62 C63 C64 C65 C66 C67 C68

100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF

Sheet: /

File: Dragon32_MKII.sch

Title: Dragon 32 MKII Schematic

Size: A1 Date: 2019-11-04 Rev: C

KiCad E.D.A. eeschema 5.0.2+dfsg1-1 Id: 1/1

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

Você também pode gostar

- Corte Bateria - ReguladoraDocumento1 páginaCorte Bateria - Reguladorarp.luanacosta100% (1)

- Plano General ConexionesDocumento1 páginaPlano General Conexionespatrick corcueraAinda não há avaliações

- KXHi1024 V1.1-13Documento1 páginaKXHi1024 V1.1-13Gabriel de LimaAinda não há avaliações

- TRX5000&6000 InputDocumento1 páginaTRX5000&6000 InputWilliam Vargas TorresAinda não há avaliações

- AZUMA 1 75-Model - PDF PAVIMENTO SUPERIORDocumento1 páginaAZUMA 1 75-Model - PDF PAVIMENTO SUPERIORGuilherme HenriqueAinda não há avaliações

- Buzo CanguroDocumento37 páginasBuzo Cangurocamilo camargoAinda não há avaliações

- gz80-B00 SCH 2Documento1 páginagz80-B00 SCH 2Bertrand Ber TrandAinda não há avaliações

- TK-85 RevkDocumento1 páginaTK-85 RevkDiego CruzAinda não há avaliações

- Baf 1285 Amp PDFDocumento1 páginaBaf 1285 Amp PDFGonzalo Rios100% (1)

- PS1501 Pre AtualizadoDocumento1 páginaPS1501 Pre AtualizadoAdriana Dundes100% (1)

- DiagramaDocumento1 páginaDiagramaAngelo ChaustreAinda não há avaliações

- Ether Board SCHDocumento1 páginaEther Board SCHUwe BeekhuisAinda não há avaliações

- Document - Onl Esquema Eletrico Placa Base Modulare IntelbrasDocumento6 páginasDocument - Onl Esquema Eletrico Placa Base Modulare IntelbrasAdolf Willer100% (2)

- Soft LigaçãoDocumento1 páginaSoft LigaçãoJonathan SostissoAinda não há avaliações

- Amara Terra MiaDocumento1 páginaAmara Terra MiaDebora MagniAinda não há avaliações

- Oneal Op2000Documento5 páginasOneal Op2000MarcosAinda não há avaliações

- Ponte H EsquemaDocumento1 páginaPonte H EsquemaCarlos Henrique SabinoAinda não há avaliações

- PCI Main Board Esquema de Montagem Dixtal EP-3Documento2 páginasPCI Main Board Esquema de Montagem Dixtal EP-3CRISLAYNE GUEDESAinda não há avaliações

- Motor DahlanderDocumento1 páginaMotor DahlanderAtubes100% (1)

- Etelj - NITRO2200, 3200, 4400, 6400Documento13 páginasEtelj - NITRO2200, 3200, 4400, 6400Bruno MagalhãesAinda não há avaliações

- Esquema DetectorMetaisDocumento1 páginaEsquema DetectorMetaismarlonAinda não há avaliações

- Solución Marcha y Paro, Máquina Estampadora.Documento3 páginasSolución Marcha y Paro, Máquina Estampadora.CRISTOFER ROBERTO CHAIRE GALLEGOSAinda não há avaliações

- RevolutionDocumento1 páginaRevolutionrphluthieriaAinda não há avaliações

- 10050-2 Esq Geral Trifásico R8Documento1 página10050-2 Esq Geral Trifásico R8ROBSON QUINAGLIAAinda não há avaliações

- Serigrafia Out CLPDocumento2 páginasSerigrafia Out CLPLucinei ManoelAinda não há avaliações

- Dobradeira de VergalhãoDocumento2 páginasDobradeira de Vergalhãonnv7rdmpc4Ainda não há avaliações

- Esquema Nanovna H4 V 2 1Documento1 páginaEsquema Nanovna H4 V 2 1Eugênio MagalhãesAinda não há avaliações

- Diezel VH4 PreampDocumento1 páginaDiezel VH4 PreampChristy AwansAinda não há avaliações

- Traçado de Redes 1Documento1 páginaTraçado de Redes 1Ivan ChicaneAinda não há avaliações

- Plano H2SDocumento1 páginaPlano H2Scarloncho1980Ainda não há avaliações

- Proj Ele A3 Casa Ex Curso CreaDocumento1 páginaProj Ele A3 Casa Ex Curso CreaVitor Hugo Segate CaetanoAinda não há avaliações

- SELF Água COMANDODocumento1 páginaSELF Água COMANDOAry Lima SilvaAinda não há avaliações

- Folha de Registro Aba Istituto 2020.2Documento1 páginaFolha de Registro Aba Istituto 2020.2Rita FernandesAinda não há avaliações

- Omron G9SP-N20S: TDK-LambdaDocumento14 páginasOmron G9SP-N20S: TDK-LambdaMimotoAinda não há avaliações

- Partida Direta Com ReverçãoDocumento1 páginaPartida Direta Com ReverçãoNicolas Barbosa SantosAinda não há avaliações

- 932REV0Documento3 páginas932REV0Wendel Teixeira MachadoAinda não há avaliações

- Unidade Termica 017Documento5 páginasUnidade Termica 017Weverton DamiãoAinda não há avaliações

- TV led+PH40R86DSGW+V.A+2392755Documento18 páginasTV led+PH40R86DSGW+V.A+2392755Ednaelson SilvaAinda não há avaliações

- Analise de Incidencia (Contusão e Vacina)Documento7 páginasAnalise de Incidencia (Contusão e Vacina)Hillary MafraAinda não há avaliações

- Arkimech: Moradia Unifamiliar Roberto Buque Arq. Milton Paúnde Arq. Milton Paúnde Rafael MandlateDocumento1 páginaArkimech: Moradia Unifamiliar Roberto Buque Arq. Milton Paúnde Arq. Milton Paúnde Rafael MandlateLiedson PaundeAinda não há avaliações

- Esquema Eletrico - 01Documento1 páginaEsquema Eletrico - 01Sarah SousaAinda não há avaliações

- Diagrama Logitech z506Documento1 páginaDiagrama Logitech z506kibatan53% (15)

- Vestido 44Documento18 páginasVestido 44fabiana100% (2)

- PV215D-115D SchemDocumento3 páginasPV215D-115D SchemRodrigo Coelho RCAinda não há avaliações

- FinalDocumento1 páginaFinalsergio.eng3937Ainda não há avaliações

- LX5200S DISPLAY SCH-a0.SchDocumento1 páginaLX5200S DISPLAY SCH-a0.SchjaihotAinda não há avaliações

- Schematics 1087130Documento1 páginaSchematics 1087130mcbneto5470Ainda não há avaliações

- Control FinalDocumento1 páginaControl FinalJess PaucarAinda não há avaliações

- Manual Armário PDFDocumento5 páginasManual Armário PDFAnonymous Z1jBJ3KUvFAinda não há avaliações

- CN5 CN8Documento1 páginaCN5 CN8ALEX SANTOSAinda não há avaliações

- PLL 2 MDocumento1 páginaPLL 2 MOscar SeminiAinda não há avaliações

- Britania BTV32G51SN LedDocumento14 páginasBritania BTV32G51SN LedRicardo BrasilAinda não há avaliações

- RG 33 Diagrama Elétrico 220 V TrifDocumento1 páginaRG 33 Diagrama Elétrico 220 V TrifSidney PaivaAinda não há avaliações

- 0027.00582P - Transportador Vibratorio-Pt02-04Documento1 página0027.00582P - Transportador Vibratorio-Pt02-04Kátia SagginAinda não há avaliações

- PC1 Microprocessor Board Schematic Drawing 0986-30-035-00CDocumento1 páginaPC1 Microprocessor Board Schematic Drawing 0986-30-035-00Cmargono akurasiAinda não há avaliações

- Si75000 - Inversor On-Grid 75.0KW Trifasico 380VDocumento1 páginaSi75000 - Inversor On-Grid 75.0KW Trifasico 380VMarco Wellington MenezesAinda não há avaliações

- Temporizador 555 PDFDocumento8 páginasTemporizador 555 PDFLECAPASAinda não há avaliações

- Grua Viajera - CadDocumento1 páginaGrua Viajera - CadCarlos NovaAinda não há avaliações

- Partida Direta 02 TeamsDocumento1 páginaPartida Direta 02 TeamssoulucastopAinda não há avaliações

- CEDM-80 - V1 - Esquema - Elétrico - Reconstruído Z80 V1 (Incompleto)Documento1 páginaCEDM-80 - V1 - Esquema - Elétrico - Reconstruído Z80 V1 (Incompleto)Alfredo Meurer JuniorAinda não há avaliações

- Exercicios de P.ADocumento8 páginasExercicios de P.ALeandro SilvestreAinda não há avaliações

- Nmiy 0020 FPDocumento1 páginaNmiy 0020 FPAngel BirrotAinda não há avaliações

- 4569-Espaços VetoriaisDocumento18 páginas4569-Espaços VetoriaisFilipe Dutra MayerAinda não há avaliações

- Catalogo UetaDocumento76 páginasCatalogo Uetaleandro donizetti de paivaAinda não há avaliações

- Give ThanksDocumento3 páginasGive ThanksfreedyAinda não há avaliações

- Iso1219 2Documento29 páginasIso1219 2Ricardo CamargoAinda não há avaliações

- 6 - Normas ISO 15504 12207Documento36 páginas6 - Normas ISO 15504 12207lucasfberAinda não há avaliações

- Aula 02 - Formatos e DobragemDocumento10 páginasAula 02 - Formatos e DobragemIgor TorresAinda não há avaliações

- Quiz Iso 14001Documento10 páginasQuiz Iso 14001Sonalt SousaAinda não há avaliações

- Abnt Cee 272Documento13 páginasAbnt Cee 272iscjuniorAinda não há avaliações

- Britania Bs390 DVD UsbDocumento12 páginasBritania Bs390 DVD UsbaditronicAinda não há avaliações

- Química - Volume 1 (2016)Documento388 páginasQuímica - Volume 1 (2016)jannastoAinda não há avaliações

- Broken Earth Map PDFDocumento1 páginaBroken Earth Map PDFRichard HarigAinda não há avaliações

- Página para Caderninho de Folhas Pontilhadas A4 e A5Documento2 páginasPágina para Caderninho de Folhas Pontilhadas A4 e A5Stephanie LimaAinda não há avaliações

- Schematic Divmmc 1.0Documento1 páginaSchematic Divmmc 1.0Mário João VicenteAinda não há avaliações

- Bagi Tugas Dan Jadwal Senap 2021 Per 2 JanDocumento15 páginasBagi Tugas Dan Jadwal Senap 2021 Per 2 JanFidelithu VristherAinda não há avaliações

- 26 - UNIMED BLUMENAU - RB82 - Uniflex Vale Empresarial - Apto 50Documento95 páginas26 - UNIMED BLUMENAU - RB82 - Uniflex Vale Empresarial - Apto 50Kassiane FrancoAinda não há avaliações

- Norma Iso 10018Documento6 páginasNorma Iso 10018Myrna Angélica Ortega CarroAinda não há avaliações

- TD 2Documento5 páginasTD 2Oussama EljaafariAinda não há avaliações

- CDP1802 Microprocessor Kit 2018Documento3 páginasCDP1802 Microprocessor Kit 2018ekrem kayaAinda não há avaliações

- Custodia e Visita AbrilDocumento51 páginasCustodia e Visita AbrilbugigangascriarcriandouauAinda não há avaliações

- UGD JuliDocumento771 páginasUGD JuliBumi AgungAinda não há avaliações

- Apostila Curso Auditores ISO 9001Documento12 páginasApostila Curso Auditores ISO 9001Andreia AiresAinda não há avaliações

- 18 BrasilenyneDocumento1 página18 BrasilenyneHAY DAYAinda não há avaliações

- 979 Unimed Do Ceará Na04 Univida MultiDocumento66 páginas979 Unimed Do Ceará Na04 Univida MultiLuciano BezerraAinda não há avaliações

- ZX 80Documento1 páginaZX 80HugoHuzanAinda não há avaliações

- 1 Mapa de Controle de Nao ConformidadesDocumento25 páginas1 Mapa de Controle de Nao ConformidadesDaniel RodrigoAinda não há avaliações

- Abnt NBR Iso-Iec 17025-2017Documento38 páginasAbnt NBR Iso-Iec 17025-2017Fernando Costa100% (1)

- Origami for Beginners: Over 30 Fun and Relaxating Projects from Simple to Advanced, Step by Step InstructionsNo EverandOrigami for Beginners: Over 30 Fun and Relaxating Projects from Simple to Advanced, Step by Step InstructionsAinda não há avaliações

- Weapons of Chess: An Omnibus of Chess StrategiesNo EverandWeapons of Chess: An Omnibus of Chess StrategiesNota: 4 de 5 estrelas4/5 (26)

- How To Beat Anyone At Chess: The Best Chess Tips, Moves, and Tactics to CheckmateNo EverandHow To Beat Anyone At Chess: The Best Chess Tips, Moves, and Tactics to CheckmateNota: 4 de 5 estrelas4/5 (6)

- Origami Masters Ebook: 20 Folded Models by the World's Leading Artists (Includes Step-By-Step Online Tutorials)No EverandOrigami Masters Ebook: 20 Folded Models by the World's Leading Artists (Includes Step-By-Step Online Tutorials)Ainda não há avaliações

- Tactics Training Paul Morphy: How to improve your Chess with Paul Morphy and become a Chess Tactics MasterNo EverandTactics Training Paul Morphy: How to improve your Chess with Paul Morphy and become a Chess Tactics MasterNota: 4.5 de 5 estrelas4.5/5 (2)

- Chess Pattern Recognition for Beginners: The Fundamental Guide to Spotting Key Moves in the MiddlegameNo EverandChess Pattern Recognition for Beginners: The Fundamental Guide to Spotting Key Moves in the MiddlegameNota: 3.5 de 5 estrelas3.5/5 (8)

- The ChessCafe Puzzle Book 1: Test and Improve Your Tactical VisionNo EverandThe ChessCafe Puzzle Book 1: Test and Improve Your Tactical VisionNota: 4 de 5 estrelas4/5 (2)

- Mastering Positional Sacrifices: A Practical Guide to a Vital Skill in ChessNo EverandMastering Positional Sacrifices: A Practical Guide to a Vital Skill in ChessAinda não há avaliações

- Naomiki Sato's Origami Roses: Create Lifelike Roses and Other BlossomsNo EverandNaomiki Sato's Origami Roses: Create Lifelike Roses and Other BlossomsNota: 5 de 5 estrelas5/5 (3)

- Learn Chess the Right Way: Book 3: Mastering Defensive TechniquesNo EverandLearn Chess the Right Way: Book 3: Mastering Defensive TechniquesNota: 5 de 5 estrelas5/5 (2)

- 1001 Chess Exercises for Beginners: The Tactics Workbook that Explains the Basic Concepts, TooNo Everand1001 Chess Exercises for Beginners: The Tactics Workbook that Explains the Basic Concepts, TooNota: 3.5 de 5 estrelas3.5/5 (4)

- On the Origin of Good Moves: A Skeptic's Guide at Getting Better at ChessNo EverandOn the Origin of Good Moves: A Skeptic's Guide at Getting Better at ChessAinda não há avaliações

- Winning Chess Middlegames: An Essential Guide to Pawn StructuresNo EverandWinning Chess Middlegames: An Essential Guide to Pawn StructuresNota: 3.5 de 5 estrelas3.5/5 (7)

- Advanced Origami: An Artist's Guide to Performances in Paper: Origami Book with 15 Challenging ProjectsNo EverandAdvanced Origami: An Artist's Guide to Performances in Paper: Origami Book with 15 Challenging ProjectsNota: 4 de 5 estrelas4/5 (15)

- Kaufman's New Repertoire for Black and White: A Complete, Sound and User-Friendly Chess Opening RepertoireNo EverandKaufman's New Repertoire for Black and White: A Complete, Sound and User-Friendly Chess Opening RepertoireAinda não há avaliações

- Tomoko Fuse's Origami Art: Works by a Modern MasterNo EverandTomoko Fuse's Origami Art: Works by a Modern MasterNota: 4.5 de 5 estrelas4.5/5 (8)

- The 100 Endgames You Must Know Workbook: Practical Endgame Exercises for Every Chess PlayerNo EverandThe 100 Endgames You Must Know Workbook: Practical Endgame Exercises for Every Chess PlayerNota: 5 de 5 estrelas5/5 (2)

- Chess: How To Play Chess For Beginners: Learn How to Win at Chess - Master Chess Tactics, Chess Openings and Chess Strategies!No EverandChess: How To Play Chess For Beginners: Learn How to Win at Chess - Master Chess Tactics, Chess Openings and Chess Strategies!Nota: 3.5 de 5 estrelas3.5/5 (2)

- Origami Valentine's Day: 24 Paper Folding for Valentine's DayNo EverandOrigami Valentine's Day: 24 Paper Folding for Valentine's DayNota: 5 de 5 estrelas5/5 (1)

- How Magnus Carlsen Became the Youngest Chess Grandmaster in the World: The Story and the GamesNo EverandHow Magnus Carlsen Became the Youngest Chess Grandmaster in the World: The Story and the GamesNota: 4 de 5 estrelas4/5 (8)