Escolar Documentos

Profissional Documentos

Cultura Documentos

Lista 1 - Organização de Computadores - Hierarquia de Memória e Barramento

Enviado por

Kaique Lima0 notas0% acharam este documento útil (0 voto)

7 visualizações1 páginaDireitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

7 visualizações1 páginaLista 1 - Organização de Computadores - Hierarquia de Memória e Barramento

Enviado por

Kaique LimaDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

Você está na página 1de 1

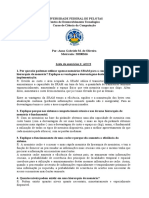

UNIVERSIDADE FEDERAL RURAL DO SEMI-ÁRIDO

Campus Angicos

Lista de Exercícios 1

Disciplina: Organização e Arquitetura de Computadores

Professor: Vinícius Samuel Valério de Souza

Assunto: Organização de Computadores – Hierarquia de Memória e Barramento

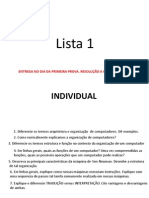

1) Descreva as partes que constituem a organização básica de um computador e a função de

cada uma delas.

2) Qual o objetivo da memória secundária? Faça um comparativo dessa memória com as

demais da hierarquia em termos de preço, tamanho e velocidade de acesso.

3) Qual o objetivo da memória primária (principal)? Faça um comparativo dessa memória com

as demais da hierarquia em termos de preço, tamanho e velocidade de acesso.

4) Como as informações armazenadas na memória principal são organizadas? Qual o

mecanismo utilizado para referenciar uma informação específica dentro dessa memória?

5) O que são palavras e como funcionam os mecanismos Big Endian e Little Endian?

6) Qual o objetivo da memória cache? Faça um comparativo dessa memória com as demais

da hierarquia em termos de preço, tamanho e velocidade de acesso.

7) O que aconteceria se a memória cache não existisse? Como ficaria o desempenho da

execução dos programas?

8) O que são linhas de cache? Em que situação ocorre uma falha de cache e o que acontece

quando essa falha é gerada?

9) Descreva os princípios da localidade espacial e temporal e diga por que eles proporcionam

um ganho de desempenho na execução dos programas.

10) Qual a diferença entre memórias cache unificadas e divididas (arquitetura Havard)? Qual a

vantagem e a desvantagem de cada uma delas?

11) Quais os níveis de cache existentes? Quais as diferenças entre eles?

12) Descreva as principais vias que compõem o barramento e a função de cada uma delas.

13) Qual a relação entre a quantidade de linhas de transmissão que compõem a via de dados e

o desempenho na transmissão de informações armazenadas em palavras da memória

principal?

14) Qual a relação entre a quantidade de linhas de transmissão que compõem a via de

endereços e o tamanho da memória principal?

15) Quantas linhas de transmissão são necessárias na via de endereços para endereçar uma

memória principal que possui 256 células? Nessas circunstancias, o que acontece se for

utilizado um barramento cuja via de endereços é composta por 6 linhas de transmissão?

Você também pode gostar

- Atividade de ComputaçãoDocumento2 páginasAtividade de ComputaçãoKaique LimaAinda não há avaliações

- Desenvolvimento De Software Ii C# Programação Em CamadasNo EverandDesenvolvimento De Software Ii C# Programação Em CamadasAinda não há avaliações

- Exercicios SODocumento3 páginasExercicios SOAna Carolina RossiAinda não há avaliações

- Lista ExerciciosDocumento2 páginasLista ExerciciosElder SouzaAinda não há avaliações

- Metodologias ativas, gamificação com quizz: instrumentos para potencializar o ensino presencial técnicoNo EverandMetodologias ativas, gamificação com quizz: instrumentos para potencializar o ensino presencial técnicoAinda não há avaliações

- ListadeExercicios02 (Memoria)Documento3 páginasListadeExercicios02 (Memoria)Audrey TelesAinda não há avaliações

- Metodologia Ativa: uma caracterização do uso de cenários de computação em nuvem em disciplinas de graduação em ComputaçãoNo EverandMetodologia Ativa: uma caracterização do uso de cenários de computação em nuvem em disciplinas de graduação em ComputaçãoAinda não há avaliações

- 1a ListaExerciciosDocumento4 páginas1a ListaExerciciosRilner Azevedo de MucioAinda não há avaliações

- Lista de Exercicios Sistemas Operacionais - Cap 5, 8, 11, 12 e 15Documento7 páginasLista de Exercicios Sistemas Operacionais - Cap 5, 8, 11, 12 e 15Paulo HemmelAinda não há avaliações

- Lista 02Documento1 páginaLista 02Júlia FrankAinda não há avaliações

- Sistemas Operacionais - QuestõesDocumento4 páginasSistemas Operacionais - Questõesr7ziczAinda não há avaliações

- Exerccios Livros MAIA - Sistemas OperacionaisDocumento22 páginasExerccios Livros MAIA - Sistemas OperacionaisLucas RodriguesAinda não há avaliações

- Lista de Exercícios 2 - Conceitos de Hardware e Software - EC36CDocumento1 páginaLista de Exercícios 2 - Conceitos de Hardware e Software - EC36CRodolfo FerreiraAinda não há avaliações

- Exercicios 07 Gerencia de Cache - To de EnderecosDocumento2 páginasExercicios 07 Gerencia de Cache - To de EnderecosFelipe AragãoAinda não há avaliações

- Questionário SO (P2)Documento3 páginasQuestionário SO (P2)kamilleAinda não há avaliações

- Exercícios Gerência Do Processador e Memória PDFDocumento3 páginasExercícios Gerência Do Processador e Memória PDFGlauco SantosAinda não há avaliações

- Lista de Exercicios I N1Documento1 páginaLista de Exercicios I N1ThiagoRodriguesAlvesAinda não há avaliações

- 3º Questionário de Sistemas OperativosDocumento2 páginas3º Questionário de Sistemas OperativosManuel CarvalhoAinda não há avaliações

- Threads - AtividadeDocumento2 páginasThreads - AtividadeKarolyne MunizAinda não há avaliações

- Lista 15 - Microprogramação - Memória CacheDocumento5 páginasLista 15 - Microprogramação - Memória CacheKaique LimaAinda não há avaliações

- Exercícios Memória Adint 2020Documento2 páginasExercícios Memória Adint 2020louieisexhausted160Ainda não há avaliações

- Lista2 - SubDocumento4 páginasLista2 - SubGustavo DetomiAinda não há avaliações

- Lista 2Documento2 páginasLista 2José MagalhãesAinda não há avaliações

- Lista Iso 04Documento5 páginasLista Iso 04Nicole FernandaAinda não há avaliações

- Exercícios M3Documento3 páginasExercícios M3Marcelo ItoAinda não há avaliações

- Respostas Do QuestionarioDocumento8 páginasRespostas Do Questionariolanagata100% (2)

- Questões - Java Como ProgramarDocumento15 páginasQuestões - Java Como ProgramarReginaldoAinda não há avaliações

- Questionario DSMDocumento10 páginasQuestionario DSMLucas Matos MunizAinda não há avaliações

- Questões para Estudo Dirigido de Organização de ComputadoresDocumento1 páginaQuestões para Estudo Dirigido de Organização de ComputadoresJosemar Muller LohnAinda não há avaliações

- Teorico PDFDocumento18 páginasTeorico PDFandre luiz pimentaAinda não há avaliações

- Lista 3 - SODocumento4 páginasLista 3 - SOCarolina FernandesAinda não há avaliações

- Exerci Cio SDocumento3 páginasExerci Cio SAnna Gabriele Marques de OliveiraAinda não há avaliações

- Segunda Lista de Exercícios de Sistema OperacionaisDocumento15 páginasSegunda Lista de Exercícios de Sistema OperacionaisVinicius César0% (1)

- ArquiteturaComput ATV2Documento3 páginasArquiteturaComput ATV2Ovídio FariasAinda não há avaliações

- Atividade 2 - Todas CorretasDocumento3 páginasAtividade 2 - Todas CorretasMarcos Roberto GonçalvesAinda não há avaliações

- Avaliação Do Curso de Lotus NotesDocumento3 páginasAvaliação Do Curso de Lotus NotesThiago CardosoAinda não há avaliações

- Organização de Computadores - Respostas Da Lista 3Documento12 páginasOrganização de Computadores - Respostas Da Lista 3Patrick LaraAinda não há avaliações

- 1a Lista de Exercicios - SMDocumento2 páginas1a Lista de Exercicios - SMMatheus LibórioAinda não há avaliações

- Organização e Projeto de Computadores: A Interface Hardware/softwareDocumento3 páginasOrganização e Projeto de Computadores: A Interface Hardware/softwareCarlos0% (1)

- Questionario S.O.Documento10 páginasQuestionario S.O.Barbara GuiraldelliAinda não há avaliações

- Lista 1 BCC266Documento16 páginasLista 1 BCC266Francisco CarreiroAinda não há avaliações

- Exercicios IntroducaoDocumento2 páginasExercicios IntroducaoMates SilvaAinda não há avaliações

- Ficha - I-S.d-2024Documento2 páginasFicha - I-S.d-2024Denny UdezioAinda não há avaliações

- ListaDocumento3 páginasListalucasAinda não há avaliações

- Revisar Envio Do Teste QUESTIONÁRIO UNIDADE IIIDocumento6 páginasRevisar Envio Do Teste QUESTIONÁRIO UNIDADE IIIalivitorAinda não há avaliações

- Questionário 6Documento4 páginasQuestionário 6Marcus RamosAinda não há avaliações

- Trabalho Sobre Gerenciamento de MemoriaDocumento4 páginasTrabalho Sobre Gerenciamento de Memoriaisabelmitchell100% (1)

- HARD COMP - Unidade 3 - Aula 6 - Sintetize - OKDocumento2 páginasHARD COMP - Unidade 3 - Aula 6 - Sintetize - OKteste100% (1)

- Topico6 - Sistema de Memória Organização e ArquiteturaDocumento29 páginasTopico6 - Sistema de Memória Organização e ArquiteturaIdagilson AmaralAinda não há avaliações

- Lista 2 Arq Comp IIDocumento2 páginasLista 2 Arq Comp IIJoao Pedro Da Cunha DiasAinda não há avaliações

- 50 Questões SigDocumento22 páginas50 Questões Sigalexandre sales guerraAinda não há avaliações

- 1º Questionário de Arquitectura de ComputadoresDocumento2 páginas1º Questionário de Arquitectura de ComputadoresElias DanielAinda não há avaliações

- Lista 02Documento4 páginasLista 02Júlia FrankAinda não há avaliações

- Sistemas Operacionais Temp 4Documento4 páginasSistemas Operacionais Temp 4Leticia CechinelAinda não há avaliações

- Memória Virtual Sistemas OperacionaisDocumento24 páginasMemória Virtual Sistemas OperacionaisCarlos PereiraAinda não há avaliações

- Capitulo 2 ExerciciosDocumento2 páginasCapitulo 2 ExerciciosJackson SantanaAinda não há avaliações

- Caches de Segmentação e PaginaçãoDocumento30 páginasCaches de Segmentação e PaginaçãoAvelino CorreiaAinda não há avaliações

- Lista de ExerciciosDocumento2 páginasLista de ExerciciosIsmael Ohlweiler Ohlweiler100% (1)

- Aulas Dias 24 e 25 de JanDocumento62 páginasAulas Dias 24 e 25 de JanKaique LimaAinda não há avaliações

- Lista 2Documento6 páginasLista 2Kaique LimaAinda não há avaliações

- SegundatividadearqDocumento3 páginasSegundatividadearqKaique LimaAinda não há avaliações

- Lista 15 - Microprogramação - Memória CacheDocumento5 páginasLista 15 - Microprogramação - Memória CacheKaique LimaAinda não há avaliações