Escolar Documentos

Profissional Documentos

Cultura Documentos

Ap EDG3 Ed

Enviado por

elvio002Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Ap EDG3 Ed

Enviado por

elvio002Direitos autorais:

Formatos disponíveis

Universidade Federal de Uberlandia

Faculdade de Engenharia Eletrica

Uma Breve Introdu cao `a

Elvio Prado da Silva

Kleber Lopes Fontoura

Terceira Edi cao

2002

Apresenta cao

S

o

b

r

e

o

c

o

n

t

e

u

d

o

d

e

s

t

e

t

u

t

o

r

i

a

l :

Esta

apostila foi es-

crita por Elvio Prado

da Silva, utilizando o pro-

cessador de textos L

A

T

E

X. Este

tutorial foi baseado em notas de aula

de Eletr onica Digital do Professor Kleber

Lopes Fontoura da Universidade Federal de

Uberl andia, Faculdade de Engenharia Eletrica. Ela

deve ser utilizada apenas como guia de consulta, n ao podendo

ser mantida como unica fonte de estudos do aluno, uma vez que aqui

somente ser a explorado os conceitos b asicos e introdut orios do

conte udo de Eletr onica Digital. Logo, aconselhamos que

o aluno possua em m aos um bom livro texto para

melhores detalhes e para exerccios propos-

tos. Aqui ser ao explorados conceitos

simples como Fun c oes L ogicas,

Portas L ogicas, Circuitos

L ogicos, Mapas de

Karnaugh e

outros.

Espero que aproveitem bastante este material!

Qualquer problema e ou erro encontrado, favor entrar em contato com:

elvio@ieg.com.br Elvio - 1 de fevereiro de 2003

2

Sumario

Apresenta cao 2

Sumario 3

1 Introdu cao 6

1.1 Circuitos L ogicos Combinacionais . . . . . . . . . . . . . . . . . . . . . 6

1.2 Circuitos L ogicos Sequenciais . . . . . . . . . . . . . . . . . . . . . . . 6

1.3 Sistemas Numericos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.3.1 Sistema Decimal . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.3.2 Sistema Octal . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.3.3 Sistema Hexadecimal . . . . . . . . . . . . . . . . . . . . . . . . 7

1.3.4 Sistema Bin ario . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.3.5 Leitura de um n umero Bin ario . . . . . . . . . . . . . . . . . . . 7

2 Fun c oes L ogicas e Portas L ogicas 10

2.1 Fun c ao L ogica E ou AND: . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.2 Fun c ao L ogica OU ou OR: . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.3 Fun c ao L ogica OU-Exclusivo: . . . . . . . . . . . . . . . . . . . . . . . . 13

2.4 Fun c ao L ogica N

AO ou NOT ou Inversora: . . . . . . . . . . . . . . . . 14

2.5 Fun c ao L ogica N

AO E ou NAND: . . . . . . . . . . . . . . . . . . . . . 15

2.6 Fun c ao L ogica N

AO OU ou NOR: . . . . . . . . . . . . . . . . . . . . . 16

3 Equivalencia entre Blocos L ogicos 17

4 Realiza cao de Circuitos L ogicos 19

4.1 Express oes Booleanas Geradas por Circuitos L ogicos: . . . . . . . . . . 19

4.2 Circuitos L ogicos Obtidos a partir de Express oes Booleanas: . . . . . . 20

4.3 Tabela Verdade Obtida a partir de uma Express ao Booleana: . . . . . . 21

4.4 Express ao e Tabela Verdade Obtidas a Partir de um Circuito: . . . . . 21

4.5 Express ao L ogica a partir da Tabela Verdade: . . . . . . . . . . . . . . 22

4.6 Procedimento para a constru c ao de um Circuito L ogico: . . . . . . . . . 23

5

Algebra de Boole 26

5.1 Postulados . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

5.1.1 Postulado da Complementa c ao . . . . . . . . . . . . . . . . . . 26

5.1.2 Postulado da Adi c ao (Semelhante a porta OU) . . . . . . . . . . 26

3

4 SUM

ARIO

5.1.3 Postulado da Multiplica c ao (Semelhante a porta E) . . . . . . . 26

5.2 Propriedades . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.2.1 Comutativa . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.2.2 Associativa . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.2.3 Distributiva . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.3 Teoremas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.3.1 Teoremas de Morgan: . . . . . . . . . . . . . . . . . . . . . . . . 27

5.3.2 Exemplo 1 - Provas: . . . . . . . . . . . . . . . . . . . . . . . . 27

5.3.3 Exemplo 2 - Simplica c oes: . . . . . . . . . . . . . . . . . . . . 28

6 Simplica cao de Fun c oes L ogicas com Mapas de Karnaugh 30

6.1 Formas Padr ao das Fun c oes L ogicas . . . . . . . . . . . . . . . . . . . . 30

6.1.1 Soma de Produtos: . . . . . . . . . . . . . . . . . . . . . . . . . 30

6.1.2 Produto de Somas: . . . . . . . . . . . . . . . . . . . . . . . . . 30

6.2 Numera c ao dos Mintermos e Maxtermos . . . . . . . . . . . . . . . . . 31

6.2.1 Mintermos (m) . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

6.2.2 Maxtermos (M) . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

6.3 Mapas de Karnaugh . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

6.3.1 Diagrama para 2 Vari aveis . . . . . . . . . . . . . . . . . . . . . 32

6.3.2 Diagrama para 3 Vari aveis . . . . . . . . . . . . . . . . . . . . . 33

6.3.3 Diagrama para 4 Vari aveis . . . . . . . . . . . . . . . . . . . . . 34

6.3.4 Mapa para 5 Vari aveis . . . . . . . . . . . . . . . . . . . . . . . 35

6.4 Exemplo de Mapas de Karnaugh . . . . . . . . . . . . . . . . . . . . . 35

6.5 Princpios de Mapas de Karnaugh . . . . . . . . . . . . . . . . . . . . . 36

6.5.1 Princpio Geral . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.5.2 Adjacencias L ogicas . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.5.3 Agrupamentos maiores em um mapa de Karnaugh

(Simplica c oes) . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

6.5.4 Algoritmo para simplica c ao . . . . . . . . . . . . . . . . . . . . 37

6.5.5 Representa c ao por Maxtermos . . . . . . . . . . . . . . . . . . . 41

6.5.6 Fun c oes Incompletamente Especicadas . . . . . . . . . . . . . . 41

6.5.7 Mapeamento quando a fun c ao n ao e expressa

por Mintermos . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

7 Codica cao e Decodica cao 44

7.1 C odigo BCD 8421 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

7.2 C odigo Excesso 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.3 Existem outros tipos de c odigos BCD de 4 Bits . . . . . . . . . . . . . 45

7.4 C odigo BCD de 5 Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.4.1 C odigo Johnson . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.5 C odigo 9876543210 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7.6 C odigo ASCII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7.7 Decodicadores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Elvio 3

a

Ed./2002 Apostila de EDG

SUM

ARIO 5

8 Circuitos Multiplex e Demultiplex (MUX e DEMUX) 49

8.1 Multiplex (MUX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

8.1.1 Projeto e funcionamento . . . . . . . . . . . . . . . . . . . . . . 50

8.1.2 Mux de 16 canais . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Lista de Figuras 52

Lista de Tabelas 53

Indice Remissivo 54

Apostila de EDG 3

a

Ed./2002 Elvio

Captulo 1

Introdu cao

1.1 Circuitos L ogicos Combinacionais

As vari aveis de sada s o dependem das vari aveis de entrada.

Ex.: Somadores, subtratores, codicadores e decodicadores.

1.2 Circuitos L ogicos Sequenciais

As vari aveis de sada s ao dependentes das vari aveis de entradae/ou de seus estados

anteriores.

Ex.: Contadores e registradores.

1.3 Sistemas Numericos

1.3.1 Sistema Decimal

E o mais utilizado e o mais importante, tem 10 n umeros,0 ate 9.

1.3.2 Sistema Octal

Sistema com 8 n umeros, 0 ate 7. Ver Tabela 1.1 na p agina nesta p agina

Decimal 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

Octal 1 2 3 4 5 6 7 10 11 12 13 14 15 16 17 20

Tabela 1.1: Tabela do Sistema Octal

6

1.3 Sistemas Numericos 7

1.3.3 Sistema Hexadecimal

Sistema com 16 n umeros e letras, 0 ate 9 e A ate F. Ver Tabela 1.2 na p agina 7

Decimal 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

Hexad. 1 2 3 4 5 6 7 8 9 A B C D E F 10

Tabela 1.2: Tabela do Sistema Hexadecimal

1.3.4 Sistema Binario

E um sistema utilizado em computadores onde se necessita de apenas dois estados,

0 ou 1 foi criado para ser manipulado onde se tem a necessidade de se fazer uma

combina c ao de zeros e uns para que se entenda uma informa c ao:

0 Estado chamado BAIXO

1 Estado chamado ALTO

Ex.: Interruptores liga/desliga, transistor satura c ao/corte

Ver Tabela 1.3 na p agina 7

Decimal 0 1 2 3 4 5 6 7 8 9 10

Bin ario 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010

Tabela 1.3: Tabela do Sistema Bin ario

1.3.5 Leitura de um n umero Binario

No sistema decimal faz-se a leitura da seguinte maneira:

594 = 5.100 + 9.10 + 4

594 = 5.10

2

+ 9.10

1

+ 4.10

0

(594)

10

base 10

Para ler um n umero bin ario faz-se o mesmo processo, mas em base 2:

(1010)

2

= 1.2

3

+ 0.2

2

+ 1.2

1

+ 0.2

0

= (10)

10

Quanto a classica c ao dos n umeros bin arios:

Apostila de EDG 3

a

Ed./2002 Elvio

8 Introdu cao

Os algarismos Bin arios s ao chamados de BITS (Binary Digits).

Os de 4 Bits s ao chamados de NIBBLE.

Os de 8 Bits s ao chamados de BYTE.

Para a contagem em bin ario pode-se utilizar um hod ometro. Ver Tabela 1.4 na

p agina 8

00 0000 04 0100 08 1000 12 1100

01 0001 05 0101 09 1001 13 1101

02 0010 06 0110 10 1010 14 1110

03 0011 07 0111 11 1011 15 1111

Tabela 1.4: Hod ometro: Decimal Bin ario

Pode-se ent ao montar uma tabela, de 4 bits neste caso, que ser a muito utilizada. Ver

Tabela 1.5 na p agina 8.

Decimal Binario

0 0000

1 0001

2 0010

3 0011

4 0100

5 0101

6 0110

7 0111

8 1000

9 1001

10 1010

11 1011

12 1100

13 1101

14 1110

15 1111

Tabela 1.5: Tabela Decimal Bin ario de 4 BITS

Elvio 3

a

Ed./2002 Apostila de EDG

1.3 Sistemas Numericos 9

A equa c ao 1.1 mostra como montar a tabela 1.5:

2

n

= 2

4

=

16

2

= 8

8

2

= 4

4

2

= 2

2

2

= 1 (1.1)

A equa c ao 1.1 nos diz que:

n n umero de bits

8 zeros na 1

a

coluna, depois 8 uns

4 zeros na 2

a

coluna, depois 4 uns

2 zeros na 3

a

coluna, depois 2 uns

1 zeros na 4

a

coluna, depois 1 um

Apostila de EDG 3

a

Ed./2002 Elvio

Captulo 2

Fun c oes L ogicas e Portas L ogicas

As fun c oes l ogicas s ao:

E / AND OU / OR N

AO / NOT

N

AO E / NAND N

AO OU / NOR -

- OU-Exclusivo -

Analisando sempre em 2 est agios 0 ou 1 temos que:

0 signica

::::::::::

ausencia

:::

de

::::::::

tens ao, aparelho desligado,

::::::

chave

::::::::

aberta.

1 signica

::::::::::

presen ca

:::

de

::::::::

tens ao, aparelho ligado,

::::::

chave

:::::::::

fechada.

10

2.1 Fun cao L ogica E ou AND: 11

2.1 Fun cao L ogica E ou AND:

Analisando o circuito da gura 2.1, temos:

Figura 2.1: Circuito E

0 Chave aberta

1 Chave fechada

0 L ampada apagada

1 L ampada acesa

O funcionamento do circuito pode ser resumido em uma tabela, chamada Tabela Ver-

dade, com as seguintes caractersticas:

A, B Situa c oes possveis

S Resultados

A tabela verdade da Fun c ao L ogica E e a Tabela 2.1. Ent ao por essa tabela podemos

A B S

0 0 0

0 1 0

1 0 0

1 1 1

Tabela 2.1: Tabela Verdade da Fun c ao L ogica E

montar a Fun c ao L ogica 2.1 que a representa:

S = A B (2.1)

Que se le: A e B.

E tambem temos um Circuito L ogico (Porta L ogica) na gura 2.2:

Figura 2.2: Porta L ogica E

Apostila de EDG 3

a

Ed./2002 Elvio

12 Fun c oes L ogicas e Portas L ogicas

2.2 Fun cao L ogica OU ou OR:

Analisando o circuito da gura 2.3, temos:

Figura 2.3: Circuito OU

0 Chave aberta

1 Chave fechada

0 L ampada apagada

1 L ampada acesa

O funcionamento do circuito pode ser resumido em uma tabela, chamada Tabela Ver-

dade, com as seguintes caractersticas:

A, B Situa c oes possveis

S Resultados

A tabela verdade da Fun c ao L ogica OU e a Tabela 2.2. Ent ao por essa tabela podemos

A B S

0 0 0

0 1 1

1 0 1

1 1 1

Tabela 2.2: Tabela Verdade da Fun c ao L ogica OU

montar a Fun c ao L ogica 2.2 que a representa:

S = A + B (2.2)

Que se le: A ou B.

E tambem temos um Circuito L ogico (Porta L ogica) na gura 2.4:

Figura 2.4: Porta L ogica OU

Elvio 3

a

Ed./2002 Apostila de EDG

2.3 Fun cao L ogica OU-Exclusivo: 13

2.3 Fun cao L ogica OU-Exclusivo:

O funcionamento da Porta L ogica OU-Exclusivo e semelhante ` a Porta L ogica OU,

com a condi c ao de que Exclusivamente ou A ou B devem estar fechados (valor 1), n ao

permitindo a situa c ao em que A e B est ao fechados.

A Tabela Verdade est a exemplicada na Tabela 2.3 a seguir, compare-a com a

Tabela 2.2 (Tabela OU da p agina 12). Ent ao por essa tabela podemos montar a Fun c ao

A B S

0 0 0

0 1 1

1 0 1

1 1 0

Tabela 2.3: Tabela Verdade da Fun c ao L ogica OU-Exclusivo

L ogica 2.3 que a representa:

S = A B (2.3)

Que se le: A exclusivo B.

E tambem temos um Circuito L ogico (Porta L ogica) na gura 2.5:

Figura 2.5: Porta L ogica OU-Exclusivo

Apostila de EDG 3

a

Ed./2002 Elvio

14 Fun c oes L ogicas e Portas L ogicas

2.4 Fun cao L ogica N

AO ou NOT ou Inversora:

Analisando o circuito da gura 2.6, temos:

Figura 2.6: Circuito N

AO

A Tabela Verdade possui as seguintes caractersticas:

A,

A Situa c oes possveis

S =

A

A tabela verdade da Fun c ao L ogica N

AO e a Tabela 2.4. Logo, temos a Fun c ao

A

A

0 1

1 0

Tabela 2.4: Tabela Verdade da Fun c ao L ogica N

AO

L ogica 2.4:

S =

A (2.4)

Que se le: A barra, ou A barrado.

E tambem temos um Circuito L ogico (Porta L ogica) na gura 2.7:

Figura 2.7: Porta L ogica N

AO

Elvio 3

a

Ed./2002 Apostila de EDG

2.5 Fun cao L ogica N

AO E ou NAND: 15

2.5 Fun cao L ogica N

AO E ou NAND:

O funcionamento da Porta L ogica N

AO E e semelhante ` a Porta L ogica E, s o que

invertida.

A Tabela Verdade est a exemplicada na Tabela 2.5 a seguir, compare-a com a

Tabela 2.1 (Tabela E da p agina 11). Ent ao por essa tabela podemos montar a Fun c ao

A B S

0 0 1

0 1 1

1 0 1

1 1 0

Tabela 2.5: Tabela Verdade da Fun c ao L ogica N

AO E

L ogica 2.5 que a representa:

S = A B (2.5)

E tambem temos um Circuito L ogico (Porta L ogica) na gura 2.8:

Figura 2.8: Porta L ogica N

AO E

Apostila de EDG 3

a

Ed./2002 Elvio

16 Fun c oes L ogicas e Portas L ogicas

2.6 Fun cao L ogica N

AO OU ou NOR:

O funcionamento da Porta L ogica N

AO OU e semelhante ` a Porta L ogica OU, s o

que invertida.

A Tabela Verdade est a exemplicada na Tabela 2.6 a seguir, compare-a com a

Tabela 2.2 (Tabela OU da p agina 12). Ent ao por essa tabela podemos montar a Fun c ao

A B S

0 0 1

0 1 0

1 0 0

1 1 0

Tabela 2.6: Tabela Verdade da Fun c ao L ogica N

AO OU

L ogica 2.6 que a represente:

S = (A + B) (2.6)

E tambem temos um Circuito L ogico (Porta L ogica) na gura 2.9:

Figura 2.9: Porta L ogica N

AO OU

Elvio 3

a

Ed./2002 Apostila de EDG

Captulo 3

Equivalencia entre Blocos L ogicos

Os blocos l ogicos podem ser montados de forma que possam realizar as mesmas

tarefas, ou seja, ter as sadas funcionando de maneira igual a uma outra j a conhecida.

Ex.: Porta N

AO OU a partir de portas E e Inversoras como mostra a gura 3.1:

Figura 3.1: Porta L ogica N

AO OU Equivalente

A equa c ao 3.1 nos mostra a situa c ao da gura 3.1

B (A + B) (3.1)

A B

A

B

A

B (A +B)

0 0 1 1 1 1

0 1 1 0 0 0

1 0 0 1 0 0

1 1 0 0 0 0

Tabela 3.1: Tabela Verdade da Fun c ao L ogica N

AO OU Equivalente

Aqui na Tabela 3.2 mostraremos alguns Blocos L ogicos e seus Equivalentes que

podem ser montados facilmente com a combina c ao de outros blocos:

17

18 Equivalencia entre Blocos L ogicos

Bloco L ogico Bloco Equivalente

Tabela 3.2: Blocos L ogicos e seus respectivos Blocos Equivalentes

Elvio 3

a

Ed./2002 Apostila de EDG

Captulo 4

Realiza cao de Circuitos L ogicos

Processo que permite a realiza c ao de um circuito l ogico a partir das condi c oes

estabelecidas. Faremos interliga c oes entre express oes l ogicas, circuito e tabela verdade.

4.1 Express oes Booleanas Geradas por Circuitos L ogicos:

Analisando cada bloco em separado tem-se o resultado da gura 4.1:

Figura 4.1: Obten c ao de Equa c oes Booleanas

19

20 Realiza cao de Circuitos L ogicos

4.2 Circuitos L ogicos Obtidos a partir de Express oes

Booleanas:

Analisando cada bloco em separado tem-se o resultado da gura 4.2:

Figura 4.2: Obten c ao de Circuitos L ogicos

Elvio 3

a

Ed./2002 Apostila de EDG

4.3 Tabela Verdade Obtida a partir de uma Expressao Booleana: 21

4.3 Tabela Verdade Obtida a partir de uma Ex-

pressao Booleana:

A seguir temos uma equa c ao e sua referida Tabela Verdade representada pela

tabela 4.1 da p agina 21:

S =

A + B + AB

C (4.1)

1

o

Membro 2

o

Membro Auxiliar 3

o

Membro

A B C

A B

C AB

C Resultado Final

0 0 0 1 0 1 0 1

0 0 1 1 0 0 0 1

0 1 0 1 1 1 0 1

0 1 1 1 1 0 0 1

1 0 0 0 0 1 0 0

1 0 1 0 0 0 0 0

1 1 0 0 1 1 1 1

1 1 1 0 1 0 0 1

Tabela 4.1: Tabela Verdade obtida pela Fun c ao L ogica da equa c ao 4.1

4.4 Expressao e Tabela Verdade Obtidas a Partir

de um Circuito:

A seguir temos um Circuito L ogico na gura 4.3 e sua referida Tabela Verdade

representada pela tabela 4.2 da p agina 22:

Figura 4.3: Obten c ao de Equa c oes Booleanas

Apostila de EDG 3

a

Ed./2002 Elvio

22 Realiza cao de Circuitos L ogicos

1

o

Membro Auxiliar 3

o

Membro

A B C A + B B C (B C) Resultado Final

0 0 0 0 0 1 0

0 0 1 0 0 1 0

0 1 0 1 0 1 1

0 1 1 1 1 0 0

1 0 0 1 0 1 1

1 0 1 1 0 1 1

1 1 0 1 0 1 1

1 1 1 1 1 0 0

Tabela 4.2: Tabela Verdade obtidas a partir do Circuito da gura 4.3

4.5 Expressao L ogica a partir da Tabela Verdade:

Analisa-se onde a sada S = 1 e monta-se a Fun c ao L ogica adequada. Analisemos

a Tabela Verdade 4.3

A B C S

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 (1)

a

1 0 0 0

1 0 1 (1)

b

1 1 0 (1)

c

1 1 1 (1)

d

Tabela 4.3: Tabela Verdade de onde se obter a a Express ao L ogica da equa c ao 4.2

Para se ter 1 na sada S , monta-se a Fun c ao L ogica mostrada na equa c ao 4.2:

S = ABC

. .

a

+A BC

. .

b

+ABC

. .

c

+ABC

. .

d

(4.2)

Elvio 3

a

Ed./2002 Apostila de EDG

4.6 Procedimento para a constru cao de um Circuito L ogico: 23

4.6 Procedimento para a constru cao de um Cir-

cuito L ogico:

1. Analisar o problema;

2. Estabelecer conven c oes;

3. Montar a Tabela Verdade;

4. Montar o Circuito L ogico;

::::::::::::

Exemplo:

Observe o cruzamento entre a Rua A, preferencial e a Rua B, Secund aria e os

sem aforos 1, 2, 3 e 4 mostrados na gura 4.4:

Figura 4.4: Cruzamento entre a Rua A e a Rua B

O desenho da gura 4.4 representa o cruzamento das Ruas A e B. Neste cruza-

mento queremos instalar um sistema autom atico para os Sem aforos, com as seguintes

caractersticas:

Quando houver carros transitando somente na Rua B, o Semaforo 2 de-

ver a permanecer Verde para que os carros possam trafegar livremente;

Quando houver carros transitando somente na Rua A, o Semaforo 1

dever a permanecer Verde pelo mesmo motivo;

Quando houver carros transitando nas Ruas A e B, devemos abrir o

sem aforo para a Rua A pois e preferencial;

Apostila de EDG 3

a

Ed./2002 Elvio

24 Realiza cao de Circuitos L ogicos

:::::::::

Resposta:

Estabelecendo conven c oes:

a) Existencia de carros na Rua A A = 1;

b) N ao existencia de carros na Rua A A = 0;

c) Existencia de carros na Rua B B = 1;

d) N ao existencia de carros na Rua B B = 0;

e) Verde do Sem aforo 1 aceso Vrd1 = 1;

f) Verde do Sem aforo 2 aceso Vrd2 = 1;

g) Quando Vrd1 = 1:

Vermelho do Sem aforo 1 apagado Vrm1 = 0;

Vermelho do Sem aforo 2 aceso Vrm2 = 1;

Verde do Sem aforo 2 apagado Vrd2 = 0;

h) Quando Vrd2 = 1:

Vermelho do Sem aforo 2 apagado Vrm2 = 0;

Vermelho do Sem aforo 1 aceso Vrm1 = 1;

Verde do Sem aforo 1 apagado Vrd1 = 0;

Montando a Tabela Verdade 4.4:

Entrada Sada

A B Vrd1 Vrm1 Vrd2 Vrm2

0 0 X

=0

X

=(1)

X

=(1)

X

=0

0 1 0 (1) (1) 0

1 0 (1) 0 0 (1)

1 1 (1) 0 0 (1)

Tabela 4.4: Tabela Verdade do Cruzamento entre as Ruas A e B

X = Condi c ao irrelevante Dont Care( Pode ser 0 ou 1 ), adotando a situa c ao em

que: Vrd1 = 0, Vrm1 = 1, Vrd2 = 1, Vrm2 = 0.

Elvio 3

a

Ed./2002 Apostila de EDG

4.6 Procedimento para a constru cao de um Circuito L ogico: 25

Analisando onde temos (1) na sada, montamos as equa c oes a seguir:

Vrd1 = A B + A B

Vrm1 = A B +

A

B

Vrd2 =

A

B + A B

Vrm2 = A B + A B

_

_

Vrd1 = Vrm2 = A B + A B

Vrd2 = Vrm1 = A B +

A

B

(4.3)

Analisando as equa c oes 4.3 podemos montar o Circuito L ogico 4.5:

Figura 4.5: Circuito dos Sem aforos da Rua A a Rua B

Apostila de EDG 3

a

Ed./2002 Elvio

Captulo 5

Algebra de Boole

Desenvolvida por George Boole, e tambem conhecida por

Algebra L ogica, constitui

importante ferramenta matem atica para projetos de Circuitos L ogicos.

5.1 Postulados

5.1.1 Postulado da Comple-

menta cao

se A = 0 A = 1

se A = 1 A = 0

:::::::::::::

Identidade

::::::::::::::::

Associativa:

I = A = A

5.1.2 Postulado da Adi cao

(Semelhante a porta OU)

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 1

::::::::::::::

Identidades

::::::::::::::::::

Associativas:

A + 0 = A

A + 1 = 1

A + A = A

A + A = 1

5.1.3 Postulado da Multi-

plica cao (Semelhante a

porta E)

0 0 = 0

0 1 = 0

1 0 = 0

1 1 = 1

::::::::::::::

Identidades

::::::::::::::::::

Associativas:

A 0 = 0

A 1 = A

A A = A

A A = 0

26

5.2 Propriedades 27

5.2 Propriedades

5.2.1 Comutativa

:::

Na

:::::::::

Adi cao:

A + B = B + A

:::

Na

::::::::::::::::

Multiplica cao:

A B = B A

5.2.2 Associativa

:::

Na

:::::::::

Adi cao:

A+(B + C) = (A + B)+C

:::

Na

::::::::::::::::

Multiplica cao:

A (B C) = (A B) C

5.2.3 Distributiva

A (B + C) = A B+A C

5.3 Teoremas

5.3.1 Teoremas de Morgan:

A + B = A B

(A B) = A + B

::::::::::::::

Identidades

::::::::::::::

Auxiliares:

1. A + A B = A A (1 + B) = A

2. A + A B = A + B

3. (A + B) (A + C) = A + B C

4. A B + A C + B C = A B + A C

5.3.2 Exemplo 1 - Provas:

:::::::

Provar que A = A:

se A = 0 A = 1 se A = 1 A = 0

se A = 1 A = 0 se A = 0 A = 1

Apostila de EDG 3

a

Ed./2002 Elvio

28

Algebra de Boole

:::::::

Provar que A + 0 = A:

se A = 0 0 + 0 = 0 se A = 1 1 + 0 = 1

:::::::

Provar que A + A B = A:

A (1 + B)

. .

1

= A A 1 = A A = A

:::::::

Provar que (A + B) (A + C) = A + B C:

A A+A C+A B+B C = A+B C A+A C+A B+B C = A+B C

A (1 + C + B)

. .

1

+B C = A + B C A + B C = A + B C

5.3.3 Exemplo 2 - Simplica c oes:

::::::::::::::

Simplica cao

:::

de

::::::::::

Fun c oes

:::::::::

L ogicas:

:::::::::::::

Simplicar: X = A B C + A B C + A B C

X = A C

_

B + B

_

. .

1

+A B C X = A C + A B C

X = A

_

C + B C

_

X = A (C + B)

X = A C + A B

:::::::::::::

Simplicar: X = (A + B + C)

_

A + B + C

_

X = (A + B + C)

_

A B C

_

X = (A + B + C)

_

A B C

_

X =

_

_

_

A A

_

. .

0

B C

_

_

+

_

_

A (B B)

. .

B

C

_

_

+

_

_

A B

_

C C

_

. .

0

_

_

X = A B C X = A + B + C

Elvio 3

a

Ed./2002 Apostila de EDG

5.3 Teoremas 29

:::::::::::::

Simplicar: S = A B C + A B C + A B C

S = A C

_

B + B

_

. .

1

+A B C S = A C + A B C

:::::::::::::

Simplicar: S = A B C + A C + A B

S = A

_

B C + C + B

_

S = A

_

B C +

_

C + B

__

S = A

_

B C +

_

C + B

_

_

S = A

_

B C +

_

C B

__

fazendo B C = x

S = A (x + x)

. .

1

S = A

Apostila de EDG 3

a

Ed./2002 Elvio

Captulo 6

Simplica cao de Fun c oes L ogicas

com Mapas de Karnaugh

Para simplicar as fun c oes l ogicas pelo Mapa de Karnaugh, precisa-se denir os

tipos de processos:

6.1 Formas Padrao das Fun c oes L ogicas

6.1.1 Soma de Produtos:

::::::::::::

Exemplo: S = A B + A C D + B C

A soma de produtos e a soma de termos em que cada termo e o produto das vari aveis

l ogicas individuais.

:::::::

Soma

::::::::::

padr ao

:::::

de

::::::::::::::

Produtos:

::::::::::::

Exemplo: S = A B C + A B C + A B C + A B C + A B C

Na soma padr ao de produtos, as vari aveis aparecem (complementadas ou

n ao) em cada um dos termos do produto.

Cada um dos termos e denido como MINTERMO.

6.1.2 Produto de Somas:

::::::::::::

Exemplo: S =

_

A + B

_

_

A + C + D

_

(B + C)

30

6.2 Numera cao dos Mintermos e Maxtermos 31

O produto de somas e o produto de termos em que cada termo e a soma das vari aveis

l ogicas individuais.

::::::::::

Produto

:::::::::::

padr ao

::::

de

::::::::::

Somas:

::::::::::::

Exemplo: S = (A + B + C)

_

A + B + C

_

_

A + B + C

_

_

A + B + C

_

_

A + B + C

_

No produto padr ao de somas, as vari aveis aparecem (complementadas ou

n ao) em cada um dos termos do produto.

Cada um dos termos e denido como MAXTERMO.

6.2 Numera cao dos Mintermos e Maxtermos

6.2.1 Mintermos (m)

Dene-se por Mintermo:

A 1

A 0

P

o

d

e

a

c

o

n

t

e

c

e

r

q

u

e

v

a

r

i

a

s

o

r

d

e

n

a

c

o

e

s

p

r

o

d

u

z

a

m

m

e

s

m

a

n

u

m

e

r

a

c

a

o

,

c

o

m

o

m

o

s

t

r

a

o

e

x

e

m

p

l

o

a

o

l

a

d

o

.

::::::::::::

Exemplo:

A B C = 110 = (6)

10

m

6

A B C = 011 = (3)

10

m

3

C B A = 011 = (3)

10

m

3

S = A B C

011

3

+A B C

100

4

+A B C

101

5

+A B C

110

6

f (A, B, C) = m

3

+ m

4

+ m

5

+ m

6

f (A, B, C) =

m(3, 4, 5, 6)

Apostila de EDG 3

a

Ed./2002 Elvio

32 Simplica cao de Fun c oes L ogicas com Mapas de Karnaugh

6.2.2 Maxtermos (M)

Dene-se por Maxtermo:

A 0

A 1

::::::::::::

Exemplo:

A + B + C = 100 = (4)

10

M

4

F (A, B, C) = (A + B + C)

000

A + B + C

001

A + B + C

010

2

F(A, B, C) = M

0

M

1

M

2

F(A, B, C) = M(0, 1, 2)

6.3 Mapas de Karnaugh

E um dispositivo extremamente util na simplica c ao e minimiza c ao das fun c oes

algebricas booleanas com a qual chega-se mais facilmente ` a express ao mnima.

6.3.1 Diagrama para 2 Variaveis

O diagrama para 2 vari aveis est a na tabela 6.1:

Linha n

o

A B f(A,B)

0 0 0 . . .

1 0 1 . . .

2 1 0 . . .

3 1 1 . . .

Tabela 6.1: Diagrama para 2 vari aveis

Elvio 3

a

Ed./2002 Apostila de EDG

6.3 Mapas de Karnaugh 33

Os mapas de Karnaugh para 2 vari aveis est ao na gura 6.1:

Figura 6.1: Mapa para 2 Vari aveis

6.3.2 Diagrama para 3 Variaveis

O diagrama para 3 vari aveis est a na tabela 6.2:

Linha n

o

A B C

0 0 0 0

1 0 0 1

2 0 1 0

3 0 1 1

4 1 0 0

5 1 0 1

6 1 1 0

7 1 1 1

Tabela 6.2: Diagrama para 3 vari aveis

Os mapas de Karnaugh para 3 vari aveis est ao na gura 6.2:

Figura 6.2: Mapa para 3 Vari aveis

Apostila de EDG 3

a

Ed./2002 Elvio

34 Simplica cao de Fun c oes L ogicas com Mapas de Karnaugh

6.3.3 Diagrama para 4 Variaveis

O diagrama para 4 vari aveis est a na tabela 6.3:

Linha n

o

A B C D

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

10 1 0 1 0

11 1 0 1 1

12 1 1 0 0

13 1 1 0 1

14 1 1 1 0

15 1 1 1 1

Tabela 6.3: Diagrama para 4 vari aveis

Os mapas de Karnaugh para 4 vari aveis est ao na gura 6.3:

Figura 6.3: Mapa para 4 Vari aveis

Elvio 3

a

Ed./2002 Apostila de EDG

6.4 Exemplo de Mapas de Karnaugh 35

6.3.4 Mapa para 5 Variaveis

Os mapas de Karnaugh para 5 vari aveis est ao na gura 6.4, mas est ao aqui somente

a ttulo de enriquecimento e curiosidade, pois n ao ser ao detalhados neste material:

Figura 6.4: Mapa para 5 Vari aveis

6.4 Exemplo de Mapas de Karnaugh

::::

Obs.: Quadrculos adjacentes horizontalmente e verticalmente (n ao diagonalmente)

correspondem a Mintermos e Maxtermos que diferem em apenas uma vari avel (comple-

mentada e n ao complementada).

:::::::::

Exemplo:(ver mapa exemplo na gura 6.5)

1

m

8

= A B C D (8)

10

= (1000)

2

m

12

= A B C D (12)

10

= (1100)

2

m

8

+ m

12

= A B C D + A B C D

m

8

+ m

12

= A C D

_

B + B

_

. .

1

m

8

+ m

12

= A C D

1

A partir de agora trataremos em sua maioria de Mintermos A 1 , mas todos os casos valem

tambem para Maxtermos A 0 .

Apostila de EDG 3

a

Ed./2002 Elvio

36 Simplica cao de Fun c oes L ogicas com Mapas de Karnaugh

Figura 6.5: Mapa Exemplo

6.5 Princpios de Mapas de Karnaugh

6.5.1 Princpio Geral

Qualquer par de Mintermos

2

adjacentes pode ser combinado em um unico termos

que inclui uma vari avel a menos que as includas pelo Mintermo.

6.5.2 Adjacencias L ogicas

Mintermos geometricamente adjacentes no mapa de Karnaugh, s ao tambem logica-

mente adjacentes (diferem apenas 1 vari avel

3

), ver exemplos na gura 6.6:

Figura 6.6: Exemplos de Adjacencia L ogica

Todas as adjacencias podem ser visualizadas se imaginarmos o mapa

enrolado sobre um tor oide.

2

Enfatizando novamente: A partir de agora trataremos em sua maioria de Mintermos A 1 , mas

todos os casos valem tambem para Maxtermos A 0 .

3

As vari aveis s ao: A, B, C, D, . . .

Elvio 3

a

Ed./2002 Apostila de EDG

6.5 Princpios de Mapas de Karnaugh 37

6.5.3 Agrupamentos maiores em um mapa de Karnaugh

(Simplica c oes)

Ver tabela 6.4 de simplica c oes e elimina c ao: de vari aveis

4

:

Quadrculos Variaveis Eliminadas

1 = 2

0

1 0

2 = 2

1

2 1

4 = 2

2

4 2

8 = 2

3

8 3

16 = 2

4

16 4

Tabela 6.4: Tabela de simplica c oes e elimina c ao de vari aveis

A simplica c ao que elimina 4 vari aveis resulta

na simplica c ao m axima que e igual a 1.

(ver gura 6.7)

6.5.4 Algoritmo para simplica cao

1. Assinalar e considerar como implicante primo essencial, qualquer quadrculo

que n ao possa ser combinado com nenhum outro;

2. Identicar os quadrculos que podem ser combinados com um unico

outro quadrculo, somente de uma maneira. Assinalar estas com-

bina c oes. Quadrculos que podem ser combinados em grupos de 2,

de mais de uma maneira, s ao deixados temporariamente de lado;

3. Identicar os quadrculos que podem ser combinados com 3 outros

quadrculos somente de uma maneira. Se os 4 quadrculos de tais

combina c oes ainda n ao estiverem includos em grupos de dois, assi-

nalar a combina c ao de 4. Novamente, um quadrculo que pode ser

combinado num grupo de 4, de mais de uma maneira e deixado de

lado;

4. Repetir o processo para grupos de 8 quadrculos;

5. Se encerrado o processo acima e ainda restarem alguns quadrculos n ao

includos em nenhum agrupamento, eles podem ser combinados uns

aos outros ou com quadrculos j a includos em outros agrupamentos

lembrando que a inten c ao e de obter o menor n umero de agrupamentos

possvel.

4

Enfatizando Novamente: As vari aveis s ao: A, B, C, D, . . .

Apostila de EDG 3

a

Ed./2002 Elvio

38 Simplica cao de Fun c oes L ogicas com Mapas de Karnaugh

Na gura 6.7 temos alguns exemplos de simplica c ao por mapas de Karnaugh.

Figura 6.7: Exemplos de Adjacencia L ogica

Elvio 3

a

Ed./2002 Apostila de EDG

6.5 Princpios de Mapas de Karnaugh 39

::::::::::::

Exemplo:

5

Simplicar pelo mapa de Karnaugh: (ver gura 6.8)

f (A, B, C, D) =

m(0, 1, 3, 5, 6, 9, 11, 13, 15)

Figura 6.8: Exemplo de Simplica c ao pelo Mapa de Karnaugh

Analisando o grupo dos quadrculos (13, 9, 15, 11), conra na tabela guia da

gura 6.8 os locais destes quadrculos:

A Na horizontal de 13 para 9 n ao variou, era 1 e no quadrculo 13

e continuou 1 no quadriculo 9, em Mintermos o 1 ca A;

B e C variaram, B e 1 no quadriculo 13 e mudou para 0 no quadrculo

9, e C e 0 no quadrculo 13 e mudou para 1 no quadrculo 15, como

variaram, eles nao entram na analise;

D Na vertical de 13 para 15 n ao variou, era 1 e no quadrculo 13 e

continuou 1 no quadriculo 15, em Mintermos o 1 ca D;

Logo a equa c ao para os quadrculos 13,9,15,11 e A D.

Resposta:

Ap os analisarmos todos os quadrculos, temos:

f (A, B, C, D) = A B C D + A B C + A D + C D + B D

5

Sempre tentar formar grupos com maior n umero de elementos possvel;

Analisar as vari aveis que N

AO VARIAREM;

Lembre-se:

Em Mintermos: A 1 A 0

Em Maxtermos: A 0 A 1

Apostila de EDG 3

a

Ed./2002 Elvio

40 Simplica cao de Fun c oes L ogicas com Mapas de Karnaugh

::::::::::::

Exemplo:

Simplicar pelo mapa de Karnaugh: (ver gura 6.9)

f (A, B, C, D) =

m(0, 2, 3, 4, 5, 7, 8, 9, 13, 15)

Figura 6.9: Exemplo de Simplica c ao pelo Mapa de Karnaugh

Analisando o grupo dos quadrculos (8, 9), conra na tabela guia da gura 6.9 os

locais destes quadrculos:

A Na horizontal de 8 para 8 n ao variou, era 1 e no quadrculo 8 e

continuou 1, em Mintermos o 1 ca A;

B Na horizontal de 8 para 8 n ao variou, era 0 e no quadrculo 8 e

continuou 0, em Mintermos o 0 ca B;

C Na vertical de 8 para 9 n ao variou, era 0 no quadrculo 8 e

continuou 0, no quadrculo 9 em Mintermos o 0 ca C;

D variou, era 0 no quadrculo 8 e mudou para 1 no quadrculo 9

como variou, ele nao entra na analise;

Logo a equa c ao para os quadrculos 8,9 e A B C.

Resposta:

Ap os analisarmos todos os quadrculos, temos:

f (A, B, C, D) = B D + A C D + A B C + A B C

Elvio 3

a

Ed./2002 Apostila de EDG

6.5 Princpios de Mapas de Karnaugh 41

6.5.5 Representa cao por Maxtermos

O resultado da representa c ao por Maxtermose um produto de somas. A regra que

determina se uma vari avel aparece complementada ou n ao, e invertida em rela c ao a

Mintermos, ou seja:

A 0

A 1

As demais regras de resolu c ao para Maxtermos s ao as mesmas de Mintermos

6

.

Ver exemplos na gura 6.10.

Figura 6.10: Exemplos de Simplica c ao por Maxtermos

6.5.6 Fun c oes Incompletamente Especicadas

Nao interessa que valor a fun c ao assume para certas combina c oes de vari aveis;

Certas combina c oes de vari aveis n ao ocorrem;

S ao combina c oes de Dont Cared.

:::::::::::

Exemplo: (Ver gura 6.11)

f(A, B, C, D) =

m(1, 2, 5, 6, 9) + d (10, 11, 13, 14, 15)

Considerando os quadrculos 11, 13 e 14, do mapa mostrado na gura 6.11 que s ao

Dont Care (X), valendo 1, podemos simplicar bem mais a equa c ao.

6

O ideal seria o aluno resolver os problemas utilizando os dois metodos (Mintermos e Maxtermos),

e optar pela equa c ao mais simplicada.

Apostila de EDG 3

a

Ed./2002 Elvio

42 Simplica cao de Fun c oes L ogicas com Mapas de Karnaugh

A equa c ao simplicada do mapa da gura 6.11 ca:

f(A, B, C, D) = C D + C D

Figura 6.11: Fun c oes Incompletamente Especicadas

6.5.7 Mapeamento quando a fun cao nao e expressa

por Mintermos

:::::::::::

Exemplo:

A equa c ao 6.1 est a relacionada com os mapas da gura 6.12.

f(A, B, C, D) = A B C D + B C D + A C + A (6.1)

Elvio 3

a

Ed./2002 Apostila de EDG

6.5 Princpios de Mapas de Karnaugh 43

Figura 6.12: Mapeamento

Apostila de EDG 3

a

Ed./2002 Elvio

Captulo 7

Codica cao e Decodica cao

Equipamentos digitais e alguns sistema de computa c ao tem seus dados de entrada

e sada expressos em decimal, facilitando o trabalho do operador. Entretanto esses

dados s ao processados internamente em bin ario sendo a convers ao efetuada interna e

autom aticamente. Essa convers ao e denominada codica cao.

7.1 C odigo BCD 8421

O c odigo BCD

1

e o mais utilizado. Utiliza 4 Bits para representar cada dgito dec-

imal.

2

4

= 16

Dezesseis combina c oes possveis mas s ao utilizados apenas 10, como mostra a tabela 7.1:

Decimal BCD 8421

0 0000

1 0001

2 0010

3 0011

4 0100

5 0101

6 0110

7 0111

8 1000

9 1001

Tabela 7.1: C odigo BCD 8421

1

Binary Coded Decimal Decimal Codicado em Bin ario

44

7.2 C odigo Excesso 3 45

7.2 C odigo Excesso 3

E utilizado em circuitos aritmeticos de computadores e n ao possui valor posicional.

0

11

= 0000 + 3unidades = 0011

A tabela 7.2 nos mostra a codica c ao por excesso 3:

Decimal Excesso 3

0 0011

1 0100

2 0101

3 0110

4 0111

5 1000

6 1001

7 1010

8 1011

9 1100

Tabela 7.2: C odigo Excesso 3

7.3 Existem outros tipos de c odigos BCD de 4 Bits

Exemplo de c odigos BCD de 4 Bits:

BCD 7421;

BCD 5211;

BCD 2421;

7.4 C odigo BCD de 5 Bits

C odigo 2 entre 5:

Trata-se de um c odigo que possui sempre 2 bits iguais a 1 dentre 5 bits.

7.4.1 C odigo Johnson

E utilizado na constru c ao de compiladores.

Veja o exemplo do c odigo na tabela 7.3:

Apostila de EDG 3

a

Ed./2002 Elvio

46 Codica cao e Decodica cao

Decimal ABCDE

0 00000

1 00001

2 00011

3 00111

4 01111

5 11111

6 11110

7 11100

8 11000

9 10000

Tabela 7.3: C odigo Johnson

7.5 C odigo 9876543210

Utilizado para identicar determinado n umero. A tabela 7.4 nos mostra o c odigo:

Decimal 9 8 7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 0 0 0 1

1 0 0 0 0 0 0 0 0 1 0

2 0 0 0 0 0 0 0 1 0 0

3 0 0 0 0 0 0 1 0 0 0

4 0 0 0 0 0 1 0 0 0 0

5 0 0 0 0 1 0 0 0 0 0

6 0 0 0 1 0 0 0 0 0 0

7 0 0 1 0 0 0 0 0 0 0

8 0 1 0 0 0 0 0 0 0 0

9 1 0 0 0 0 0 0 0 0 0

Tabela 7.4: C odigo 9876543210

7.6 C odigo ASCII

O C odigo ASCII

2

e formado por um conjunto de caracteres que podem ser letras,

n umeros, smbolos especiais ou de controle, codicados em 7 bits, cada caracter e cod-

icado em 2 grupos, um de 3 bits e outro de 4 bits.

O Primeiro bit ` a direita do grupo e o menos signicativo e o ultimo bit a esquerda do

grupo de 3 e o mais signicativo.

2

ASCII American Standard Code for Information Interchange (C odigo Padr ao Americano para

Interc ambio de Informa c oes)

Elvio 3

a

Ed./2002 Apostila de EDG

7.7 Decodicadores 47

b7 b6 b5 b4 b3 b2 b1

Tabela 7.5: C odigo ASCII

3 bits b7, b6, b5 onde b7 e o mais signicativo;

4 bits b4, b3, b2, b1 onde b1 e o menos signicativo;

2

7

= 128 Combina c oes que contem:

Dgitos decimais (0 ate 9);

Letras do alfabeto (a ate z , A ate Z);

Smbolos especiais;

Controle.

7.7 Decodicadores

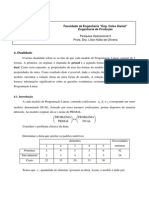

A gura 7.1 nos mostra o esquema de funcionamento de um decodicador:

Figura 7.1: Decodicadores

Exemplo:

Decodicar o c odigo BCD 8421 para o c odigo 9876543210:

::::::::::::

Resposta:

Primeiramente construiremos a tabela 7.6 da p agina 48, lembrando que as partes mar-

cadas com um X representam condi c oes de Dont Care.

Utilizremos os mapas de Karnaugh da gura 7.2 na p agina 48 para simplicar os

circuitos de sada. Construindo os outros mapas que faltam, teremos:

S

5

= B C D, S

4

= B C D,

S

3

= A B C D, S

2

= A B C D,

S

1

= A B C D

Apostila de EDG 3

a

Ed./2002 Elvio

48 Codica cao e Decodica cao

Decimal A B C D S9 S8 S7 S6 S5 S4 S3 S2 S1 S0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

1 0 0 0 1 0 0 0 0 0 0 0 0 1 0

2 0 0 1 0 0 0 0 0 0 0 0 1 0 0

3 0 0 1 1 0 0 0 0 0 0 1 0 0 0

4 0 1 0 0 0 0 0 0 0 1 0 0 0 0

5 0 1 0 1 0 0 0 0 1 0 0 0 0 0

6 0 1 1 0 0 0 0 1 0 0 0 0 0 0

7 0 1 1 1 0 0 1 0 0 0 0 0 0 0

8 1 0 0 0 0 1 0 0 0 0 0 0 0 0

9 1 0 0 1 1 0 0 0 0 0 0 0 0 0

10 1 0 1 0 X X X X X X X X X X

11 1 0 1 1 X X X X X X X X X X

12 1 1 0 0 X X X X X X X X X X

13 1 1 0 1 X X X X X X X X X X

14 1 1 1 0 X X X X X X X X X X

15 1 1 1 1 X X X X X X X X X X

Tabela 7.6: Exemplo de Decodica c ao

Figura 7.2: Decodicadores com Mapas de Karnaugh

Elvio 3

a

Ed./2002 Apostila de EDG

Captulo 8

Circuitos Multiplex e Demultiplex

(MUX e DEMUX)

8.1 Multiplex (MUX)

Os circuitos Multiplex s ao utilizados nos casos em que necessita-se enviar um certo

n umero de informa c oes contidas em v arios canais a um s o canal.

Canal Fio

A gura 8.1 nos mostra o esquema de um circuito Mux.

Circuito Elementar:

Chave de 1 p olo e N posi c oes, como mostra a gura 8.2.

Figura 8.1: Circuito MUX Figura 8.2: Circuito MUX Elementar

Entradas de Sele c ao:

Indicam qual a informa c ao deve ser conectada a sada, ou seja, as vari aveis de sele c ao

ir ao comutar a posi c ao da chave seletora.

49

50 Circuitos Multiplex e Demultiplex (MUX e DEMUX)

Strobe:

E uma entrada que e utilizada para controle da entrada de dados, onde dados somente

ser ao transferidos para a sada se o strobe estiver habilitado.

8.1.1 Projeto e funcionamento

::::::::::::

Exemplo: MUX de 4 entradas e 1 sada.

MUX 4x1

N umero de entradas = 2

n

;

N umero de vari aveis de sele c ao = n;

Podemos montar a tabela 8.1 e a gura 8.3:

Vari aveis de sele c ao Sada

A B S

0 0 I

0

0 1 I

1

1 0 I

2

1 1 I

3

Tabela 8.1: Projeto de um MUX

Figura 8.3: Funcionamento de um MUX

.

Produtos Can onicos:

A B S = I

0

A B S = I

1

A B S = I

2

A B S = I

3

Elvio 3

a

Ed./2002 Apostila de EDG

8.1 Multiplex (MUX) 51

8.1.2 Mux de 16 canais

Apostila de EDG 3

a

Ed./2002 Elvio

Lista de Figuras

2.1 Circuito E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.2 Porta L ogica E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.3 Circuito OU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.4 Porta L ogica OU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.5 Porta L ogica OU-Exclusivo . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.6 Circuito N

AO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.7 Porta L ogica N

AO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.8 Porta L ogica N

AO E . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.9 Porta L ogica N

AO OU . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.1 Porta L ogica N

AO OU Equivalente . . . . . . . . . . . . . . . . . . . . 17

4.1 Obten c ao de Equa c oes Booleanas . . . . . . . . . . . . . . . . . . . . . 19

4.2 Obten c ao de Circuitos L ogicos . . . . . . . . . . . . . . . . . . . . . . . 20

4.3 Obten c ao de Equa c oes Booleanas . . . . . . . . . . . . . . . . . . . . . 21

4.4 Cruzamento entre a Rua A e a Rua B . . . . . . . . . . . . . . . . . . . 23

4.5 Circuito dos Sem aforos da Rua A a Rua B . . . . . . . . . . . . . . . . 25

6.1 Mapa para 2 Vari aveis . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

6.2 Mapa para 3 Vari aveis . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

6.3 Mapa para 4 Vari aveis . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.4 Mapa para 5 Vari aveis . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.5 Mapa Exemplo . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.6 Exemplos de Adjacencia L ogica . . . . . . . . . . . . . . . . . . . . . . 36

6.7 Exemplos de Adjacencia L ogica . . . . . . . . . . . . . . . . . . . . . . 38

6.8 Exemplo de Simplica c ao pelo Mapa de Karnaugh . . . . . . . . . . . . 39

6.9 Exemplo de Simplica c ao pelo Mapa de Karnaugh . . . . . . . . . . . . 40

6.10 Exemplos de Simplica c ao por Maxtermos . . . . . . . . . . . . . . . . . 41

6.11 Fun c oes Incompletamente Especicadas . . . . . . . . . . . . . . . . . . 42

6.12 Mapeamento . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

7.1 Decodicadores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

7.2 Decodicadores com Mapas de Karnaugh . . . . . . . . . . . . . . . . . 48

8.1 Circuito MUX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

8.2 Circuito MUX Elementar . . . . . . . . . . . . . . . . . . . . . . . . . . 49

52

LISTA DE FIGURAS 53

8.3 Funcionamento de um MUX . . . . . . . . . . . . . . . . . . . . . . . . 50

Apostila de EDG 3

a

Ed./2002 Elvio

Lista de Tabelas

1.1 Tabela do Sistema Octal . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.2 Tabela do Sistema Hexadecimal . . . . . . . . . . . . . . . . . . . . . . 7

1.3 Tabela do Sistema Bin ario . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.4 Hod ometro: Decimal Bin ario . . . . . . . . . . . . . . . . . . . . . . 8

1.5 Tabela Decimal Bin ario de 4 BITS . . . . . . . . . . . . . . . . . . . 8

2.1 Tabela Verdade da Fun c ao L ogica E . . . . . . . . . . . . . . . . . . . . 11

2.2 Tabela Verdade da Fun c ao L ogica OU . . . . . . . . . . . . . . . . . . . 12

2.3 Tabela Verdade da Fun c ao L ogica OU-Exclusivo . . . . . . . . . . . . . . 13

2.4 Tabela Verdade da Fun c ao L ogica N

AO . . . . . . . . . . . . . . . . . . 14

2.5 Tabela Verdade da Fun c ao L ogica N

AO E . . . . . . . . . . . . . . . . . 15

2.6 Tabela Verdade da Fun c ao L ogica N

AO OU . . . . . . . . . . . . . . . . 16

3.1 Tabela Verdade da Fun c ao L ogica N

AO OU Equivalente . . . . . . . . . 17

3.2 Blocos L ogicos e seus respectivos Blocos Equivalentes . . . . . . . . . . 18

4.1 Tabela Verdade obtida pela Fun c ao L ogica da equa c ao 4.1 . . . . . . . . 21

4.2 Tabela Verdade obtidas a partir do Circuito da gura 4.3 . . . . . . . . 22

4.3 Tabela Verdade de onde se obter a a Express ao L ogica da equa c ao 4.2 . 22

4.4 Tabela Verdade do Cruzamento entre as Ruas A e B . . . . . . . . . . . 24

6.1 Diagrama para 2 vari aveis . . . . . . . . . . . . . . . . . . . . . . . . . 32

6.2 Diagrama para 3 vari aveis . . . . . . . . . . . . . . . . . . . . . . . . . 33

6.3 Diagrama para 4 vari aveis . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.4 Tabela de simplica c oes e elimina c ao de vari aveis . . . . . . . . . . . . 37

7.1 C odigo BCD 8421 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

7.2 C odigo Excesso 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.3 C odigo Johnson . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7.4 C odigo 9876543210 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7.5 C odigo ASCII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

7.6 Exemplo de Decodica c ao . . . . . . . . . . . . . . . . . . . . . . . . . 48

8.1 Projeto de um MUX . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

54

Indice Remissivo

X, 24, 41

Adjacencia L ogica, 36

Agrupamentos, 37

Algebra de Boole, 26

Algortmo, 37

Associativa, 27

Bin ario, 7

C odigo

9876543210, 46

BCD 2421, 45

BCD 5211, 45

BCD 7421, 45

BCD 8421, 44

C odigo ASCII, 46

C odigo Johnson, 45

Excesso 3, 45

chave seletora, 49

Circuitos

L ogicos Combinacionais, 6

L ogicos Sequenciais, 6

Codica c ao, 44

Comutativa, 27

Decimal, 6

Decodica c ao, 44

Decodicadores, 47

Demultiplex, 49

Demux, 49

Distributiva, 27

Dont Care, 24, 41

Entradas de Sele c ao, 49

Equivalencia, 17

Formas Padr ao, 30

Fun c oes L ogicas, 10

Fun c oes L ogicas

Fun c ao L ogica E ou AND, 11

Fun c ao L ogica N

AO E, 15

Fun c ao L ogica N

AO OU, 16

Fun c ao L ogica N

AO, 14

Fun c ao L ogica OU-Exclusivo, 13

Fun c ao L ogica OU ou OR, 12

Hexadecimal, 7

hod ometro, 8

Inversora, 14

Mapas de Karnaugh, 30, 32

Maxtermos, 31, 32, 41

Mintermos, 30, 31

Morgan, 27

Multiplex, 49

Mux, 49

Octal, 6

Portas L ogicas, 10

Postulados, 26

Postulados

Postulado da Adi c ao, 26

Postulado da Complementa c ao, 26

Postulado da Multiplica c ao, 26

Produto de Somas, 30

Propriedades, 27

Provas, 27

Rua, 23

Sem aforo, 23

Simplica c ao, 30, 37

simplica c ao, 38

Simplica c oes, 28, 37

Soma de Produtos, 30

55

56

INDICE REMISSIVO

Strobe, 50

Teoremas, 27

tor oide, 36

vari aveis, 37

Elvio 3

a

Ed./2002 Apostila de EDG

Você também pode gostar

- Cartão de Convocação Individual - Cci PDFDocumento1 páginaCartão de Convocação Individual - Cci PDFLucas HonoratoAinda não há avaliações

- Função de Utilidade IndiretaDocumento30 páginasFunção de Utilidade IndiretaDeborahrabelloAinda não há avaliações

- Limites de SucessõesDocumento12 páginasLimites de SucessõesMiguel A Garbey RamirezAinda não há avaliações

- Inversor de Frequencia hd300 173Documento2 páginasInversor de Frequencia hd300 173Rogerio Alves ResendeAinda não há avaliações

- Operations::// - Ec. /de - A DDocumento18 páginasOperations::// - Ec. /de - A DBhanu GarapatiAinda não há avaliações

- Portifólio - Analise Orientado de ObjetosDocumento11 páginasPortifólio - Analise Orientado de ObjetosCarlos PolicarpoAinda não há avaliações

- Manual SisparkDocumento9 páginasManual Sisparkr_tavares1270Ainda não há avaliações

- Pmbok UnipDocumento31 páginasPmbok UnipBruno HenriqueAinda não há avaliações

- Padrão UVM - Concepção Estruturada de Circuitos IntegradosDocumento4 páginasPadrão UVM - Concepção Estruturada de Circuitos IntegradosÍcaro TarginoAinda não há avaliações

- Matriz de ComunicaçãoDocumento1 páginaMatriz de ComunicaçãoAnderson Reimão100% (1)

- Aula4 - DualidadeDocumento15 páginasAula4 - DualidadeniltonsamaralAinda não há avaliações

- Exercícios de Circuitos DigitaisDocumento4 páginasExercícios de Circuitos DigitaisDiegoAlbertoAinda não há avaliações

- Totvs MesDocumento46 páginasTotvs MesLuciana Borges AraujoAinda não há avaliações

- Banner Sem 8Documento1 páginaBanner Sem 8Fernanda RibeiroAinda não há avaliações

- Guia MoodleDocumento219 páginasGuia MoodleAnonymous pYEJQDTqAinda não há avaliações

- Manual G31DM D2Documento16 páginasManual G31DM D2Flávia Lima100% (1)

- Como Importar Arquivos .Nk2 para o Outlook 2010Documento2 páginasComo Importar Arquivos .Nk2 para o Outlook 2010Claudio JuniorAinda não há avaliações

- Manual Vigilância/ExamesDocumento19 páginasManual Vigilância/ExamesInforários Software LdaAinda não há avaliações

- Tutorial Working ModelDocumento4 páginasTutorial Working ModelbenettiluanaAinda não há avaliações

- Teoria Da Informação - ExercíciosDocumento2 páginasTeoria Da Informação - ExercíciosHenrique BeloAinda não há avaliações

- Mapa Mental TCPDocumento1 páginaMapa Mental TCPRianRosalAinda não há avaliações

- Implantação de Um Ambiente de Armazenamento em Nuvem Corporativo Utilizando A Ferramenta Livre Owncloud Aplicado No Parque Tecnológico ItaipuDocumento13 páginasImplantação de Um Ambiente de Armazenamento em Nuvem Corporativo Utilizando A Ferramenta Livre Owncloud Aplicado No Parque Tecnológico ItaipuAirton Bordin JuniorAinda não há avaliações

- TOP 10 Principais SGBDs Do Mercado GlobalDocumento14 páginasTOP 10 Principais SGBDs Do Mercado GlobalCarlos Torres de FreitasAinda não há avaliações

- Parametros e SocialDocumento11 páginasParametros e SocialRoberto LimaAinda não há avaliações

- PortugolDocumento23 páginasPortugolhermanherzel100% (1)

- Shuttle 71R H14BT4 T830 H14BT01 4L SchematicDocumento33 páginasShuttle 71R H14BT4 T830 H14BT01 4L Schematicmarcio100% (2)

- BCDocumento24 páginasBCvinicusAinda não há avaliações

- Manual LinuxDocumento239 páginasManual LinuxLuis FernandoAinda não há avaliações

- Como Invadir TelegramDocumento6 páginasComo Invadir TelegramDomAinda não há avaliações

- Jogo Do MosquitoDocumento129 páginasJogo Do MosquitoAldo BëlfiaAinda não há avaliações