Escolar Documentos

Profissional Documentos

Cultura Documentos

Universidade de Passo Fundo

Enviado por

Ricardo AtaídeTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Universidade de Passo Fundo

Enviado por

Ricardo AtaídeDireitos autorais:

Formatos disponíveis

UNIVERSIDADE DE PASSO FUNDO

FACULDADE DE ENGENHARIA E ARQUITETURA

CURSO DE ENGENHARIA ELTRICA

ESTUDO SOBRE SDR (SOFTWARE DEFINED RADIO):

UMA APLICAO

Disciplina: Projeto de Graduao

Acadmico: Leonardo Perera Cassol

Professor: Carlos Allan Caballero Petersen

Passo Fundo, dezembro de 2009.

Leonardo Perera Cassol

Estudo sobre SDR (Software Defined Radio):

uma aplicao

Trabalho apresentado ao curso de Engenharia

Eltrica, da Faculdade de Engenharia e

Arquitetura, da Universidade de Passo Fundo,

como requisito para obteno do ttulo de

Engenheiro Eletricista, sob orientao do Prof.

Dr. Carlos Allan Caballero Petersen.

Passo Fundo, 2009

Leonardo Perera Cassol

Estudo sobre SDR (Software Defined Radio):

uma aplicao

Banca Examinadora:

____________________________________________________

Professor Dr. Carlos Allan Caballero Petersen UPF Orientador

__________________________________________________

Professor Dr. Paulo Srgio Corra Molina UPF Examinador

___________________________________________________

Professora Dra. Blanca Rosa Maquera Sosa UPF - Examinador

Passo Fundo, 2009

Dedico este trabalho aos meus pais

Hlio e Marizete que tanto lutaram

pela minha educao e pelo apoio

que me deram durante toda a

caminhada no curso de Engenharia

Eltrica, a minha irm Suelen por

toda a compreenso e a minha

namorada Gabriela pelo

companheirismo, pacincia,

compreenso e apoio durante a

realizao deste trabalho.

AGRADECIMENTOS

Primeiramente a Deus, por me dar fora, coragem, sabedoria e oportunidade. Aos

meus pais por estarem sempre do meu lado me dando foras para prosseguir, principalmente

nos momentos em que minhas foras j no existiam mais, aos meus amigos particulares e da

graduao por termos dividido nestes anos de graduao nossas tristezas, alegrias, angstias,

dvidas e vitrias. A todos os professores do curso de Engenharia Eltrica da Universidade de

Passo Fundo pela transmisso de seus conhecimentos. Um agradecimento especial ao

professor Carlos, professor orientador deste trabalho por ter acreditado no meu potencial e ter

me auxiliado na realizao do mesmo. Enfim, a todos que de uma forma ou outra

contriburam para a realizao deste trabalho e pela minha formao acadmica.

No cruzes os braos diante de

uma dificuldade, pois o maior

homem do mundo morreu de

braos abertos!

Bob Marley

RESUMO

A tecnologia SDR (Software Defined Radio) ainda algo novo e, particularmente no

Brasil, poucas instituies dedicam-se ao seu estudo. Idealmente, ter-se-ia uma arquitetura

nica, digital, responsvel por todo o processamento de sinais do rdio, desde os sinais de

rdio-freqncia at os sinais de controle.

A concepo de um SDR consiste basicamente na substituio dos mdulos de

hardware por software, tornando o rdio bastante flexvel aumentando conseqentemente sua

empregabilidade. Muitas vantagens podem ser obtidas indiretamente com esta substituio,

como o aumento da autonomia da bateria e a diminuio do peso, particularmente a aqueles

destinados a serem portteis.

Este projeto teve por finalidade o estudo sobre os SDR s e suas respectivas formas de

demodulao de sinais de radio freqncia bem como o desenvolvimento de uma aplicao de

um SDR definido por um receptor de sinais de radio freqncia (RF) modulados em

amplitude (AM - amplitude modulation) para operar na faixa de freqncias de 530 kHz a

1600 kHz, sendo a sintonia realizada via software atravs de um microcomputador bem como

a utilizao do sistema de udio do mesmo para reproduo dos sinais de banda base.

Palavras-chave: SDR, receptor de sinais AM, demodulao.

LISTA DE FIGURAS

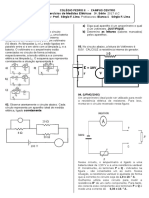

FIGURA 1 - DIAGRAMA DE BLOCOS DE UM RECEPTOR SUPER-HETERDINO.[9] ............................ 16

FIGURA 2 - DIAGRAMA DE BLOCOS DE UM RECEPTOR DE CONVERSO DIRETA.[5] ..................... 17

FIGURA 3 - PRINCPIO DE FUNCIONAMENTO DE UM SDR. ..................................................................... 19

FIGURA 4 - ESPECTRO DA BANDA RECEBIDA EM UM SDR.[9]............................................................... 20

FIGURA 5 - DIAGRAMA DE BLOCOS DE UM MISTURADOR EM QUADRATURA.[6] ........................... 23

FIGURA 6 - CIRCUITO BSICO DE UM DETECTOR POR AMOSTRAGEM EM QUADRATURA.[6] ..... 24

FIGURA 7 - CIRCUITO DO DETECTOR DE PRODUTO DE TAYLOE.[2] .................................................... 25

FIGURA 8 - CIRCUITO DO DETECTOR DE PRODUTO DE TAYLOE. ........................................................ 27

FIGURA 9 - DIAGRAMA TEMPORAL DE ACIONAMENTO DAS CHAVES ANALGICAS. ................... 28

FIGURA 10 - LARGURA DE BANDA DE DETECO DO DETECTOR DE PRODUTO DE TAYLOE. .... 40

FIGURA 11 - DIAGRAMA DE BLOCOS GERAL DO SISTEMA. ................................................................... 43

FIGURA 12 - CIRCUITO DO FILTRO PASSA-BAIXAS. ................................................................................. 46

FIGURA 13 - SMBOLO LGICO E TABELA DE ACIONAMENTO DO CI 74HC4066. .............................. 52

FIGURA 14 - DIAGRAMA LGICO E TABELA FUNCIONAL DO CI 74HC4017N. .................................... 53

FIGURA 15 - CIRCUITO DO DETECTOR DE PRODUTO DE TAYLOE. ...................................................... 55

FIGURA 16 - CIRCUITO DE UM AMPLIFICADOR DIFERENCIAL. ............................................................. 58

FIGURA 17 - CIRCUITO DOS AMPLIFICADORES DIFERENCIAIS............................................................. 60

FIGURA 18 - CIRCUITO DE DESLOCAMENTO DE FASE. ........................................................................... 62

FIGURA 19 - CIRCUITO DESLOCADOR DE FASE E SOMADOR. ............................................................... 64

FIGURA 20 - DIAGRAMA TEMPORAL DO PROTOCOLO DE COMUNICAO SPI. ............................... 69

FIGURA 21 - FLUXOGRAMA DE INICIALIZAO DO AD9833. ................................................................ 74

FIGURA 22 - FLUXOGRAMA DE ESCRITA NO AD9833............................................................................... 74

FIGURA 23 - CIRCUITO DO OSCILADOR LOCAL. ....................................................................................... 75

FIGURA 24 - CIRCUITO DO MICROCONTROLADOR. ................................................................................. 77

FIGURA 25 - DIAGRAMA TEMPORAL DE LEITURA NO FT245BL. ........................................................... 78

FIGURA 26 - DIAGRAMA TEMPORAL DE ESCRITA NO FT245BL. ........................................................... 79

FIGURA 27 - CIRCUITO CONVERSOR PARALELO/USB. ............................................................................ 80

FIGURA 28 - TELA DO SOFTWARE DO RECEPTOR AM. ............................................................................ 81

FIGURA 29 - VALOR DA FREQNCIA DE SINTONIA PARA EXPERIMENTAO. ............................. 87

FIGURA 30 - SINAIS DE SADA I E Q APS OS AMPLIFICADORES DIFERENCIAIS. ............................ 88

FIGURA 31 - SINAIS DE SADA APS O CIRCUITO DE DESLOCAMENTO DE FASE. ........................... 88

FIGURA 32 - SINAL DE SADA DE UDIO DO RECEPTOR. ........................................................................ 89

FIGURA 33 - RESPOSTA EM FREQNCIA DO HARDWARE DO RECEPTOR. ....................................... 90

FIGURA 34 - RESPOSTA EM FREQUENCIA DO FILTRO PASSA-BAIXAS. ............................................... 94

FIGURA 35 - ACIONAMENTO DAS CHAVES ANALGICAS. ..................................................................... 94

FIGURA 36 - SADAS DO DETECTOR DE PRODUTO DE TAYLOE. ........................................................... 95

FIGURA 37 - SADAS I E Q DO DETECTOR DE PRODUTO DE TAYLOE. ................................................. 95

FIGURA 38 - SADA I E Q APS CIRCUITO DE DESLOCAMENTO DE FASE. ......................................... 96

FIGURA 39 - SINAL DE SADA RESULTANTE DO CIRCUITO RECEPTOR. ............................................. 96

FIGURA 40 - LARGURA DE BANDA DE DETECO DO DETECTOR DE TAYLOE. .............................. 97

FIGURA 41 - AMPLIFICADOR OPERACIONAL. ............................................................................................ 98

FIGURA 42 - CIRCUITO DE DESLOCAMENTO DE FASE DE 90 . ............................................................ 100

FIGURA 43 - LAYOUT DA PLACA DE CIRCUITO IMPRESSO. ................................................................. 128

LISTA DE TABELAS

TABELA 1 REGIME TEMPORAL DAS CHAVES ANALGICAS. ....................................................... 31

TABELA 2 - ELEMENTOS NORMALIZADOS DO FILTRO TIPO CHEBYSHEV COM 0,5DB. ............ 48

TABELA 3 - DESCRIO DOS BITS DOS REGISTRADORES DE CONTROLE. .................................. 71

TABELA 4 - REGISTRADORES DE FREQUENCIA E FASE. ................................................................... 72

TABELA 5 - BITS DOS REGISTRADORES DE FREQUNCIA. .............................................................. 72

TABELA 6 - BITS DOS REGISTRADORES DE FASE. .............................................................................. 73

TABELA 7 - SADAS CORRESPONDENTES AOS BITS DE CONTROLE. ............................................. 73

TABELA 8 - DESCRIO DOS PINOS UTILIZADOS DO MICROCONTROLADOR. ........................... 77

LISTA DE ABREVIATURAS

Ohm;

A Ampre;

V Volts

W Watt;

Ampop Amplificador Operacional;

RF Rdio freqncia;

SDR Software Defined Radio (rdio definido por software);

AM Amplitude Modulation;

FM Frequency Modulation;

PM Phase Modulation;

Hz Hertz;

FI Frequncia Intermediria;

PC Personal Computer (computador pessoal);

A/D Analgico para Digital;

D/A Digital para Analgico;

RC Resistor-capacitor;

AGC Automatic Gain Control (controle automtico de ganho);

MSB Most Significative Bits (bits mais significativos);

LSB Low Significative Bits (bits menos significativos);

USB Universal Seria Bus;

DC Direct conversion (converso direta);

SSB Single Side Band (banda lateral nica);

SUMRIO

1. Estudo Terico...................................................................................................................... 15

1.1. Arquitetura dos receptores ......................................................................................... 15

1.1.1 Receptores superheterodinos .......................................................................... 15

1.1.2 Receptores de converso direta ou homodinos .............................................. 17

1.2. Software Defined Radio (SDR) ................................................................................. 18

1.2.1. A freqncia intermediria no SDR[7] .......................................................... 20

1.2.2. A rejeio de imagem no SDR ....................................................................... 21

1.2.3. Circuitos conversores de freqncia em quadratura ...................................... 22

1.2.3.1. Misturador em quadratura ........................................................................... 22

1.2.3.2. Detector por amostragem em quadratura ........................................................ 23

1.3. Introduo ao detector de produto de Tayloe ............................................................ 24

1.3.1. Funcionamento do detector de Tayloe[2] ...................................................... 24

1.3.2. Equacionamento do detector de Tayloe ......................................................... 26

1.3.3. Largura de banda de deteco (banda base) ................................................... 38

1.3.4. Largura de banda de deteco (RF) ............................................................... 40

2. Receptor de rdio AM para microcomputador ................................................................. 43

2.1. Diagrama de blocos do sistema ................................................................................. 43

2.1.1. Hardware do receptor ..................................................................................... 44

2.1.2. Software e interface com o usurio ................................................................ 45

2.2. Desenvolvimento do hardware .................................................................................. 45

2.2.1. Circuito do filtro passa-baixas ....................................................................... 46

2.2.2. Circuito do detector de produto de Tayloe ..................................................... 50

2.2.3. Circuito dos amplificadores somadores ......................................................... 57

2.2.4. Circuito deslocador de fase e somador........................................................... 62

2.2.5. Circuito do oscilador local ............................................................................. 67

2.2.6. Circuito do microcontrolador ......................................................................... 75

2.2.7. Circuito conversor Paralelo/USB ................................................................... 77

2.3. Desenvolvimento do software ................................................................................... 80

2.3.1. Descrio do software de controle do receptor .............................................. 81

2.3.2. Instrues de utilizao do software de controle do receptor ........................ 83

2.4. Simulaes do hardware do receptor ......................................................................... 84

2.5. Resultados experimentais do hardware do receptor .................................................. 86

2.6. Placa de circuito impresso ......................................................................................... 90

ANEXO A SIMULAO NO SOFTWARE PROTEUS .................................................... 94

ANEXO B EQUAO GERAL DE FUNCIONAMENTO DO AMPOP

[10]

...................... 98

ANEXO C PROJETO DO CIRCUITO DESLOCADOR DE FASE DE 90 ..................... 100

ANEXO D FIRMWARE DO MICROCONTROLADOR.................................................. 105

ANEXO E SOFTWARE DO APLICATIVO DE CONTROLE DO RECEPTOR ............ 110

ANEXO F CIRCUITO FINAL DO RECEPTOR ............................................................... 129

ANEXO G LAYOUT DA PLACA DE CIRCUITO IMPRESSO ...................................... 128

ANEXO H FOTOS DO PROTTIPO ................................................................................ 132

14

INTRODUO

Com o grande avano da tecnologia veio introduo de microprocessadores em

equipamentos de radiocomunicaes para controle de funes internas e incluso de novos

recursos, introduzindo-se tambm a possibilidade de se controlar os equipamentos de rdio a

partir de um computador por meio de interfaces e portas de comunicao utilizando um

software adequado para controle de numerosas funes do equipamento de rdio. Juntamente

veio a introduo de modernos equipamentos de radio com chips DSP aos quais permitem

mediante tcnicas digitais construir filtros de passagem de banda, de supresso de rudo entre

outras possibilidades, muito eficazes, e ainda melhor que os construdos tradicionalmente com

circuitos analgicos sendo estes receptores denominados de SDR.

Idealmente, um SDR consiste num rdio cujos mdulos de hardware so substitudos

por software. Desta maneira, as etapas de modulao e/ou demodulao, a sntese de

freqncias, a gerao de freqncias intermedirias (FI), as filtragens entre outros passam a

serem processados todos de forma digital. Essa substituio traz consigo diversas vantagens,

tais como a reduo de custo e consumo, d uma maior flexibilidade na implementao de

novas funcionalidades, a diminuio de tamanho e peso e facilita a manuteno e atualizao

destes equipamentos. Devido grande utilizao desses equipamentos atualmente este

trabalho tem o intuito de desenvolver um rdio definido por software que consiste em um

receptor de rdio AM por converso direta. Basicamente seu funcionamento est baseado em

um detector por amostragem em quadratura gerando sinais de banda base que sero

digitalizados, enviados ao PC pelo barramento USB onde sero processados e

disponibilizados no sistema sonoro do mesmo.

15

1. Estudo Terico

1.1.Arquitetura dos receptores

O papel de um receptor em rdio comunicao est relacionado transmisso

inteligente de informaes de um lugar para outro, sem qualquer meio fsico entre as antenas

de transmisso e recepo. Os blocos de construo bsicos de um sistema de rdio

comunicao so os transmissores e os receptores. Uma comunicao ocorre quando o

transmissor envia uma onda eletromagntica para um receptor e ento o receptor demodula e

recupera o sinal de banda base enviado pelo transmissor. Dentre as vrias configuraes dos

receptores, os mesmos so julgados quanto a sua capacidade de atenuar o rudo provindo da

transmisso pelo meio de comunicao ao qual submetido. Dentre as vrias configuraes

dos receptores podemos citar os receptores superheterodinos e os de converso direta (DC -

direct conversion) ou homodinos.

1.1.1 Receptores superheterodinos

A pea chave na arquitetura do receptor superheterodino uma ou mais converses de

freqncia entre o sinal desejado de RF e o detector. A etapa de converso de freqncia tem

dois objetivos principais, o primeiro a translao do sinal de RF a uma freqncia mais

baixa onde possvel realizar-se filtros passa-faixa mais estveis e de fcil implementao, e

o segundo usar o deslocamento de freqncia para rejeitar sinais potencialmente

interferentes. O propsito original do receptor superheterodino foi melhorar a seletividade

com respeito aos receptores de radio freqncia sintonizada (RFS).

A seo de translao de freqncia (pontos D e E na Figura 1) tambm considerada

parte do Front-end de um receptor em muitos livros. Ela consiste de um misturador de

freqncia e um oscilador local. A sada dessa seo chamada de freqncia intermediria.

O estgio de translao de freqncia seguido de um amplificador denominado de

16

amplificador de FI. Esse amplificador (pontos F, G e H na Figura 1) basicamente um

amplificador de rdio freqncia sintonizado em uma nica freqncia.

Uma amostra da sada do amplificador de FI aplicada a seo de controle automtico

de ganho (AGC) (pontos L e M na Figura 1). O propsito dessa seo manter o nvel do

sinal de sada mais ou menos constante. O circuito de controle automtico de ganho consiste

de um retificador e um filtro para as ondulaes que produzem uma tenso de controle DC,

sendo essa tenso de controle DC proporcional ao nvel de sinal de entrada de RF (ponto N na

Figura 1).

O estgio de deteco tem a funo de recuperar qualquer modulao do sinal de RF

de entrada sendo que o tipo de detector depende do tipo de modulao usado no sinal de

entrada. Sinais modulados em amplitude (AM) geralmente so manipulados por um detector

de envoltria. Sinais de SSB, DSBSC usaro um detector de produto enquanto que sinais de

FM e PM necessitaro de um detector sensvel a fase. Os estgios de sada (pontos J e K na

Figura 1) so usados para amplificao dos sinais demodulados.

Figura 1 - Diagrama de blocos de um receptor super-heterodino.[9]

17

1.1.2 Receptores de converso direta ou homodinos

Os receptores de converso direta so assim denominados porque a freqncia do sinal

de entrada convertida para banda base diretamente, sem passos intermedirios, como

acontece, por exemplo, nos receptores superheterodinos, onde feita a converso para uma

freqncia intermediria, para depois ser feita uma nova converso para obter-se o sinal de

banda base desejada.

A Figura 2 ilustra o sistema mais simples de um receptor de converso direta. O sinal

captado da antena convertido no misturador diretamente para banda base. Este sinal de

banda base passa por um filtro onde so eliminadas as componentes de alta freqncia do

sinal e aps o mesmo amplificado pelo amplificador de udio. O papel do misturador

realizar uma operao matemtica entre os sinais provindos da antena e o sinal do oscilador

local, sendo que esta operao resulta na soma e tambm na subtrao entre a freqncia

recebida e a freqncia do oscilador.

Figura 2 - Diagrama de blocos de um receptor de converso direta.[5]

18

1.2.Software Defined Radio (SDR)

Em se tratando de SDR, podemos encontrar diversas definies para descrev-lo. De

uma maneira bem resumida podemos dizer que um SDR basicamente um rdio em que

algumas ou todas as funes fsicas so definidas via software. Um rdio um sistema de

comunicao sem fio que transmite a informao atravs da propagao das ondas

eletromagnticas pelo espao. Uma grande diversidade de tipos de rdios existe atualmente,

caracterizados, por exemplo, pelas freqncias de operao, tcnicas de modulao,

codificao da informao e protocolos e os mesmos esto presentes em um grande ramo de

itens tais como celulares, computadores, veculos, televises dentre muitos outros mais.

Um SDR realiza a maior parte das funes de um equipamento de rdio, incluindo as

mais importantes, mediante o software implementado no computador. Em primeiro lugar, h

que se dizer que existe uma enorme diferena entre um radio definido por software e outro

controlado por software. Quase todos os equipamentos de rdio modernos dotados de

interfaces de informtica, so equipamentos que possuem opo de serem controlados por

computador, permitindo que se controle e visualize em parte ou todas as funes e parmetros

que normalmente esto presentes no painel frontal do equipamento, tais como, freqncia,

modo de operao (AM, FM, SSB...), controle automtico de ganho (AGC) dentre outros.

Existem at equipamentos de rdio comunicao que nem sequer painis frontais possuem,

sendo controlados totalmente por um computador, que realiza todas as funes de um painel

de comando. Nos SDR so utilizadas sofisticadas tcnicas de processamento digital de sinal,

mediante a introduo de chips DSP, implementados ao nvel das etapas de udio, para

melhorar a inteligibilidade e qualidade dos sinais. Um SDR composto de pelo menos duas

partes, que so:

Circuito conversor de freqncia em quadratura (hardware): faz parte do hardware

do dispositivo. responsvel pela converso de freqncia do sinal de RF a ser

recebido para uma freqncia intermediria (FI) suficientemente baixa para poder ser

processada por uma placa de som de um microcomputador ou ainda por um conversor

A/D adequado, em dois canais, em quadratura, determinados sinais em fase (I) e

quadratura (Q);

19

Programa de computador (software): permite processar matematicamente os sinais

em quadratura (I e Q) vindos do hardware, digitalizados por ele ou ainda digitalizados

pelo conversor A/D da placa de som. Este software realiza uma combinao

matemtica adequada dos sinais I e Q de modo a rejeitar a freqncia imagem

indesejvel existente na converso de freqncia, em seguida, efetuando a

demodulao do sinal.

Ainda relacionado ao circuito conversor de freqncia em quadratura existem hoje

circuitos de diversas configuraes que permitem a obteno destes sinais dentre os quais vale

citar o misturador em quadratura, o detector por amostragem em quadratura e o QSD

duplamente balanceado. A Figura 3 mostra o diagrama de blocos bsico de um SDR onde

podemos ver que na parte de hardware encontra-se o conversor de freqncia em quadratura

onde os sinais de FI so gerados que aps serem filtrados so enviados para um computador

ou ainda um DSP onde estes sinais sero processados.

Figura 3 - Princpio de funcionamento de um SDR.

20

1.2.1. A freqncia intermediria no SDR[7]

A freqncia intermediria (FI) dos sinais em quadratura gerados (I e Q) deve ser

suficientemente baixa para que estes sinais possam ser processados pela placa de som do PC,

que corresponde na verdade, a uma freqncia na faixa de udio e ultra-som que vai de zero

Hertz at a freqncia determinada pelo Teorema de Nyquist, que exatamente igual

metade da taxa de amostragem dos conversores A/D da placa de som do PC. A maior taxa de

amostragem das placas de som dos PCs de 48 kHz e, em vista disso os sinais em quadratura

que sero processados pelo software SDR devem ter largura de banda que vai desde 0 (Hz) a

24 kHz. Como o software do SDR processa corretamente as freqncias negativas pelo fato

de rejeitar a freqncia imagem, permitir ento, receber uma faixa de freqncias que vai

desde -24 kHz a 24 kHz em torno da freqncia do oscilador local como mostrado na Figura

4.

Portanto, em vista disso, a banda total recebida por um SDR exatamente igual taxa

de amostragem utilizada e a freqncia central da banda corresponde freqncia do

oscilador local. Citando um exemplo prtico para um valor de freqncia do oscilador local de

4 MHz, teremos que a banda total recebida ser:

(4 24 ) (4 24 ) BW MHz kHz MHz kHz = +

4 24 4 24 BW MHz kHz MHz kHz = + +

48 BW kHz =

Figura 4 - Espectro da banda recebida em um SDR.[9]

21

1.2.2. A rejeio de imagem no SDR

Num SDR, os sinais em quadratura que foram gerados pelo circuito conversor de

freqncia em quadratura (e que ambos os sinais I e Q contm a indesejvel freqncia

imagem) so digitalizados pela placa de som do PC, e em seguida processados digitalmente

pelo software SDR, que defasa o sinal Q em 90 negativos, e aps soma com o sinal I,

obtendo assim, um nico sinal de FI, com a freqncia imagem rejeitada. Aps, esse nico

sinal de FI poder ser submetido a outros processamentos digitais, como por exemplo, a

demodulao AM, SSB, FM, e DRM dentre outras . Aps a demodulao do sinal, o mesmo

convertido de analgico para digital pela placa de som (conversores DAC) para sinais de

udio, e conforme o tipo de modulao poder ser monofnico ou estreo (canais D e E).

Podemos notar que neste processo, fica evidente que o grau de rejeio da freqncia

imagem depender muito da preciso dos dois defasamentos de 90, um do circuito conversor

de freqncia em quadratura e outro do defasamento em 90 do sinal Q, e ainda, do grau de

amplitude dos sinais I e Q. No prprio software SDR, geralmente feito um ajuste fino e

automtico do grau de rejeio da freqncia imagem.

Mais detalhadamente, o processo de rejeio da freqncia imagem dado,

matematicamente por:

0

( ) cos(2. . . ) cos(2. . . )

I

I t f t f t = +

(1.0)

0

( ) sin(2. . . ) sin(2. . . )

I

Q t f t f t =

(1.1)

Mantendo o sinal ( ) I t inalterado e multiplicando o sinal ( ) Q t pela varivel

imaginria j teremos:

0

( ) cos(2. . . ) cos(2. . . )

I

I t f t f t = +

(1.2)

0

( ) .sin(2. . . ) .sin(2. . . )

I

Q t j f t j f t =

(1.3)

Como:

22

.sin( ) cos( ) j =

Teremos que o sinal ( ) Q t ser dado por:

( )

0

cos(2. . . ) cos(2. . . )

I

Q t f t f t =

(1.4)

Somando os dois sinais ( ) I t e ( ) Q t , teremos um novo sinal, sem a interferncia da

freqncia imagem que dado por:

( ) ( )

0 0

cos(2. . . ) cos(2. . . ) cos(2. . . ) cos(2. . . )

I I

f t f t f t f t I t Q t + + + =

( ) ( )

0

cos(2. . . . ) 2 I t Q t f t + =

1.2.3. Circuitos conversores de freqncia em quadratura

Como j mencionado, estes circuitos so responsveis pela converso de freqncia do

sinal de RF para uma freqncia intermediria suficientemente baixa para poder ser

processada por uma placa de som de um microcomputador ou ainda por um conversor A/D

adequado, em dois canais, em quadratura, determinados de I (In-phase signal) e Q

(Quadrature signal).

Atualmente, existem diversos tipos distintos de circuitos destinados a este fim e hoje,

os mais utilizados so os misturadores em quadratura e os detectores por amostragem em

quadratura.

1.2.3.1.Misturador em quadratura

Basicamente, este misturador em quadratura consiste em dividir o sinal de rdio

freqncia recebido ( ( ))

RF

x t multiplicando uma amostra deste sinal por um oscilador local

23

( )

LO

f , e outra amostra deste sinal pelo oscilador local ( )

LO

f defasado de 90. Deste processo

so gerados os dois sinais de sada em quadratura ( ) I t e ( ) Q t . O oscilador local responsvel

pela converso para a freqncia intermediria. A Figura 5 mostra o diagrama de blocos

simplificado deste circuito conversor de freqncia em quadratura.

Figura 5 - Diagrama de blocos de um misturador em quadratura.[6]

1.2.3.2. Detector por amostragem em quadratura

Neste tipo de circuito conversor de freqncia em quadratura o processo uma espcie

de converso direta, onde em cada ciclo da freqncia de chaveamento se obtm uma amostra

do sinal de udio em cada uma das sadas (0, 90, 180, 270). Assim, sero obtidas quatro

sadas com defasagens distintas e com essas quatro sadas distintas que se obtm os sinais em

quadratura I e Q atravs da soma dos sinais com defasagem 0 e 180, e dos sinais 90 e 270.

Essa soma realizada utilizando-se amplificadores operacionais na configurao diferencial.

Posteriormente, os sinais obtidos nessa deteco so filtrados por um filtro passa-baixa do

tipo RC, formado pela impedncia da antena e pelos capacitores de amostragem de cada ponto

do comutador rotativo como mostra a Figura 6.

24

Figura 6 - Circuito bsico de um detector por amostragem em quadratura.[6]

1.3.Introduo ao detector de produto de Tayloe

O detector de produto de Tayloe converte de um sinal de RF para um sinal de banda

base e consiste da comutao de chaves que servem para amostrar a forma de onda de RF

quatro vezes a cada perodo da freqncia de RF. Essas amostras so integradas ao longo do

tempo, produzindo uma tenso mdia nas sadas 0, 90, 180 e 270. A tenso na sada 0 o

sinal de banda base em fase ( ) I t , e a tenso na sada 90 o sinal de banda base em

quadratura ( ) Q t . Alternativamente, para incrementar ganho, o sinal na sada 0 pode ser

somado diferencialmente com o sinal na sada 180 para formar o sinal em fase ( ) I t , e o sinal

na sada 90 pode ser somado diferencialmente com o sinal na sada 270 para produzir o sinal

em quadratura ( ) Q t .

1.3.1. Funcionamento do detector de Tayloe[2]

Este circuito representa um simples e barato detector de produto que facilita a

converso de um sinal para banda base sem a interferncia da indesejvel freqncia imagem.

A comutao de chaves usada em combinao com capacitores para integrar amostras do

sinal de entrada. O sinal em fase ( ) I t e o sinal em quadratura ( ) Q t que resultam representam

o sinal de interesse de banda base.

25

Figura 7 - Circuito do detector de produto de tayloe.[2]

A Figura 7 ilustra um receptor de converso direta utilizando este detector. Neste

circuito esto presentes: resistores, circuito de polarizao, chaves de comutao, capacitores,

amplificadores somadores e estgios de atraso de fase.

Em operao, o sinal de RF ou IF

1

( ) f recebido pelo resistor 32 ( )

FILTER

R . Este

resistor forma um filtro passa-baixa do tipo RC em combinao com cada um dos capacitores

denominado por 72, 74, 76, 78 ( )

f

C . Depois que o sinal de RF passa pelo resistor 32 o

mesmo recebido na comutao das chaves de entrada. A freqncia de comutao das

chaves controlada por um sinal presente na entrada de controle 40. A freqncia do sinal de

entrada de controle igual a quatro vezes a freqncia do oscilador local que existe nos

receptores de converso direta simples. Como resultado, o sinal de entrada 36 est presente

em cada uma das quatro sadas (0, 90, 180, 270) durante um quarto do perodo da

freqncia do sinal que se deseja receber.

Durante o tempo em que a chave conecta a entrada na sada, o capacitor carregado.

O mesmo ocorre para cada um dos capacitores 72, 74, 76, 78, porm em tempos seqentes

distintos. No ciclo de comutao das chaves para as quatro sadas, os capacitores se carregam

com os valores iguais as tenses mdias do sinal de entrada durante seus respectivos

intervalos de tempo Cada capacitor um integrador, onde cada um integra um quarto do

perodo da forma onda do sinal de entrada.

A sada 42 representa o valor mdio do sinal de entrada durante o primeiro quarto do

perodo do sinal de entrada e determinado de sada 0. A sada 44 representa o valor mdio

do sinal de entrada durante o segundo quarto do perodo do sinal de entrada e determinado

26

de sada 90. A sada 46 representa o valor mdio do sinal de entrada durante o terceiro quarto

do perodo do sinal de entrada e determinado de sada 180. A sada 48 representa o valor

mdio do sinal de entrada durante o quarto quarto do perodo do sinal de entrada e

determinado de sada 270.

As sadas 42, 44, 46, 48 so as entradas dos amplificadores somadores 50 e 52. O

amplificador somador 50 soma diferencialmente a sada 0 e a sada 180, assim produzindo o

sinal de banda base em fase ( ) I t . O amplificador somador 52 soma diferencialmente a sada

90 e a sada 270, assim produzindo o sinal de banda base em quadratura ( ) Q t . O sinal de

banda base em fase ( ) I t 54 e o sinal de banda base em quadratura ( ) Q t 56 so as entradas de

um circuito de atraso de fase 58 que desloca a fase do sinal de banda base em quadratura ( ) Q t

. Os sinais resultantes ento so somados por um amplificador somador para produzir o sinal

de interesse.

O detector de produto de Tayloe apresenta diversas vantagens em relao a outros

circuitos destinados a este fim. Uma das vantagens a baixa perda de converso que pode ser

menor que 1dB, ou seja, em torno de 7dB abaixo dos conversores tpicos

6

. Outra vantagem do

detector de produto de Tayloe sua banda estreita de deteco. Como j mencionado, o

resistor de entrada e os capacitores ( )

f

C formam um filtro passa-banda para RF. O efeito do

chaveamento dos quatro capacitores forma um filtro passa-baixa que se torna um filtro passa-

banda em torno da freqncia

1

f , sendo que a largura de banda deste filtro passa-banda

determinada pela correta seleo do resistor e dos capacitores.

1.3.2. Equacionamento do detector de Tayloe

O detector de produto de Tayloe mostrado na Figura 8. Como j mencionado

anteriormente, cada chave (CH1, CH2, CH3, CH4) permanece fechada um determinado

tempo. Esse tempo determinado pela freqncia de chaveamento que ser aplicada a entrada

de controle de um circuito integrado que desempenhar o papel de acionamento das chaves. O

sinal de entrada ( )

i

V t e os sinais de sada so

1

( )

o

V t ,

2

( )

o

V t ,

3

( )

o

V t e

4

( )

o

V t que

correspondem respectivamente as j mencionadas sadas 0, 90, 180 e 270.

Figura

O sinal de entrada

genericamente representado por:

Onde, o sinal de banda base

A freqncia do sinal da portadora

freqncia do sinal de banda base

um sinal de largura de banda

de RF, ou seja, um sinal de alta

banda base, sendo assim, podemos

Portanto, vlido considerar que em um perodo do sinal da portadora

banda base ( ) z t praticamente constante. Para tal considerao, a freqncia de comutao

Figura 8 - Circuito do detector de produto de Tayloe.

O sinal de entrada ( )

i

V t um sinal de radiofreqncia, modulado em amplitude

epresentado por:

( ) . 1 . ( ) . ( )

P i

A m z V t t w t ( = +

de banda base ( ) z t e o sinal da portadora ( ) w t so

( ) cos(2. . . )

m

z t f t =

( ) cos(2. . . )

c

w t f t =

A freqncia do sinal da portadora determinada por

C

f (carrier

freqncia do sinal de banda base determinado por

m

f (message). O sinal da banda base

de largura de banda de aproximadamente a 20 k(Hz). O sinal da portador

de RF, ou seja, um sinal de alta freqncia, quando comparado com a

banda base, sendo assim, podemos dizer que:

m C

f f

, vlido considerar que em um perodo do sinal da portadora

praticamente constante. Para tal considerao, a freqncia de comutao

27

um sinal de radiofreqncia, modulado em amplitude

(1.5)

so representados por:

carrier) enquanto que a

O sinal da banda base

a 20 k(Hz). O sinal da portadora um sinal

quando comparado com a freqncia do sinal de

, vlido considerar que em um perodo do sinal da portadora ( ) w t o sinal de

praticamente constante. Para tal considerao, a freqncia de comutao

28

de cada chave deve ser exatamente igual freqncia do sinal da portadora e, ainda, devem

ter acionamento seqencias, ou seja, quando a primeira chave estiver fechada, todas as outras

devem permanecer abertas. Somente quando a primeira chave abrir a segunda chave fechar e

assim por diante. A Figura 9 ilustra a seqncia de comutao das chaves sendo o perodo da

freqncia de comutao de cada chave o perodo da freqncia da portadora do sinal de

entrada.

Figura 9 - Diagrama temporal de acionamento das chaves analgicas.

Quando uma das chaves estiver fechada, teremos um circuito RC srie sendo que a

mesma permanece fechada durante um perodo de tempo muito curto determinado por:

1

4.

on

C

t

f

=

Da mesma forma, como o perodo de chaveamento para cada uma das chaves

determinado pelo perodo do sinal da portadora, o tempo em que ela permanece aberta

determinado por:

1

ch

C

T

f

=

29

off ch on

t T t =

1 1

4.

C

off

C

t

f f

=

3

4.

ff

C

o

t

f

=

Como j mencionado, o sinal de banda base pode ser considerado constante no

perodo da freqncia da portadora, porm como cada chave ir fechar em um tempo

determinado por um quarto do perodo da portadora, na chave CH1 teremos o sinal de entrada

( ) x t sendo que na chave CH2 o sinal ser ( ) x t defasado de 90. Na chave CH3 o sinal ser

( ) x t defasado de 180 enquanto que na chave CH4 o sinal ( ) x t defasado de 270. Ento,

teremos que:

( ) ( ) ( ) 1 . 1 . .cos .

P i C

CH A m z V t t t ( = +

(1.6)

( ) 2 . 1 . .cos( . ( ) )

2

P i C

CH A m z t t V t

( = +

(1.7)

( ) ( ) 3 . 1 . .c ( . ) os

P i C

CH A m z t t V t ( = +

(1.8)

( )

3

( ) 4 . 1 . .cos( . )

2

P i C

CH A m z t V t t

( = +

(1.9)

Como:

( )

cos . sin( . )

2

C C

t t

= +

( ) cos . cos( . )

C C

t t =

( )

3

cos . sin( . )

2

C C

t t

=

Teremos:

( ) ( ) ( ) 1 . 1 . .cos .

P i C

CH A m z V t t t ( = +

(2.0)

( ) 2 . 1 . .sin( . ) ) (

i C P

CH A m z t V t t ( = +

(2.1)

( ) ( ) ( ) 3 . 1 . . cos .

C P i

CH A m t t V z t ( = +

(2.2)

30

( ) 4 . 1 . ( ) .sin( . )

P i C

CH A m z t V t t ( = +

(2.3)

Da Figura 11 quando a chave CH1 fechar o capacitor ir comear a se carregar atravs

do resistor R. Considerando o capacitor inicialmente descarregado, a corrente no instante em

que a chave fechar dada pelo valor da tenso de entrada dividido pelo resistor R, pois

inicialmente o capacitor em regime de corrente alternada se comporta como um elemento de

baixssima impedncia e pode ser considerado como um curto circuito. Como o perodo em

que a chave permanece fechada muito pequeno, o capacitor no ir se carregar totalmente, e

ento podemos considerar que a corrente que flui no instante em que a chave fechada dada

por:

( )

( )

i

V

i

R

t

t =

(2.4)

Conhecendo a corrente que flui no capacitor, podemos encontrar a tenso em cada

uma das sadas do circuito. A tenso em um capacitor em funo do tempo dada por:

( ) ( )

0

1

. .

T

C

V t i t dt

C

=

(2.5)

Como j mencionado, cada chave (CH1, CH2, CH3, CH4) permanece fechado por um

perodo de tempo igual, porm nunca todas ficam fechadas juntas. O tempo em que cada

chave permanece fechada dado por:

1

4. 2.

n

C

o

C

T

f

= =

A Tabela 1 mostra o tempo correspondente que cada chave permanece fechada

durante um perodo do sinal da portadora:

31

CH1 CH2 CH3 CH4

1

0

4.

C

f

1 1

4. 2.

C C

f f

1 3

2. 4.

C C

f f

3 1

4.

C C

f f

Tabela 1 Regime temporal das chaves analgicas.

Portanto, atravs dessa anlise as sadas do detector de produto de Tayloe so

determinadas atravs das equaes:

( )

1

4.

1

1 0

1

. ( )

1

.

c

o

f

V i t dt

C

t =

(2.6)

( )

1

2.

2

1 2

4

2

.

( )

1

. .

c

c

f

f

o

V t i t dt

C

=

(2.7)

( )

3

4.

3

1 3

2

3

.

( )

1

. .

c

c

f

f

o

V t i t dt

C

=

(2.8)

( )

1

4

3 4

4.

4

1

. ) . (

c

c

f

f

o

i t dt V t

C

=

(2.9)

Como os valores dos capacitores C1, C2, C3, C4 devem ter valores iguais,

determinaremos que:

1 2 3 4

32

E, portanto:

( )

1

4.

1

0

1

1

( ) . .

c

o

f

i dt

C

V t t =

(3.0)

( )

2.

2

1

2

1

4.

1

. . ( )

c

c

f

f

o

V t i t dt

C

=

(3.1)

( )

4.

3

3

3

1

2.

1

. . ( )

c

c

f

f

o

V t i t dt

C

=

(3.2)

( )

1

4

3

4.

4

( )

1

. .

c

c

f

f

o

i V t dt

C

t =

(3.3)

Portanto, atravs das equaes (3.0), (3.1), (3.2) e (3.3) as tenses nas sadas

correspondentes para cada chave so determinadas, respectivamente:

Para a chave CH1, substituindo a equao (1.6) em (2.4), teremos:

( )

( ) ( )

1

. 1 . .cos .

C P

A m z t t

i t

R

( +

=

(3.4)

Substituindo a equao (3.4) na equao (3.0), teremos:

( ) ( )

2

0

1

.

. 1 . . cos .

1

. . ( )

c

P C

o

V t

A m z t t

dt

C R

( +

=

(3.5)

( )

( )

2.

1

0

. 1 .

. cos . . ( )

.

c

P

o C

A m z t

t dt

R

V

C

t

( +

=

(3.5)

A integral indefinida de uma funo cossenoidal dada por:

33

( )

1

cos . . .sin( . ) x dx x

( )

1

. 1 .

1 1

. .sin( . ) .sin( .0)

. 2.

( )

o C C

C C C

P

A m z

V

C

t

t

w w

R

( + ( | | | |

=

( | |

(

\ \

(3.5)

( )

1

. 1 .

1 1

. .sin( ) .sin(0)

. 2

( )

o

C C

P

A m z t

RC

V t

( + ( | | | |

=

( | |

(

\ \

(3.5)

Como:

( ) sin 1; sin 0 0

2

| |

= =

|

\

( )

1

. 1 .

.

)

1

. 0 (

o

P

C

A m z t

RC

V t

( +

(

=

(

(3.5)

( )

1

. 1 .

( )

. .

C

P

o

A m z t

t

RC

V

( +

=

(3.5)

Para a chave CH2, substituindo a equao (1.7) em (2.4), teremos:

( )

( ) ( )

2

. 1 . .sin .

C P

A m z t t

i t

R

( +

=

(3.6)

Substituindo a equao (3.6) na equao (3.1), teremos:

( ) ( )

2.

2

. 1 . .sin .

1

( ) . .

c

c

C

o

P

A m z t

t V t

t

d

C R

( +

=

(3.7)

( )

( )

2.

2

. 1 .

. sin . .

.

( )

c

c

o C

P

A m z t

t

C

V d

R

t t

( +

=

(3.7)

34

A integral indefinida de uma funo senoidal dada por:

( )

1

sin . . .cos( . ) x dx x

( )

2

. 1 .

1 1

. . ( . ) . ( . )

. .

(

2

)

o C C

C C C

P

C

V

A m z t

cos w cos w

R C

t

( + ( | | | |

=

( | |

(

\ \

(3.7)

( )

2

. 1 .

1 1

. . ( ) . ( )

. 2

( )

C

P

o

C

A m z t

co V s os

RC

t c

( + ( | | | |

=

( | |

(

\ \

(3.7)

Como:

( ) cos 0; cos 1

2

| |

= =

|

\

( )

2

. 1

(

.

)

.

1

. 0

o

C

P

A m z t

RC

V t

( + ( | |

=

( |

(

\

(3.7)

( )

2

. 1 .

( )

. .

C

P

o

A m z t

t

RC

V

( +

=

(3.7)

Para a chave CH3, substituindo a equao (1.8) em (2.4), teremos:

( )

( ) ( )

3

. 1 . .cos .

C P

A m z t t

i t

R

( +

=

(3.8)

Substituindo a equao (3.8) na equao (3.2), teremos:

( ) ( )

3

.

3

.

2

. 1 . .co

(

s .

1

) . .

c

c

C

o

P

A m z t t

d V t t

C R

( +

=

(3.9)

35

( )

( )

3

2

3

.

.

. 1 .

. cos . .

.

( )

c

c

o C

P

A m z t

t dt

RC

V t

( +

=

(3.9)

A integral indefinida de uma funo cossenoidal dada por:

( )

1

c . . .sin( . ) os x dx x

( )

3

. 1 .

1 3. 1

. .sin( . ) .sin( . )

. 2.

( )

o C C

C C C C

P

A m z t

w w

R C

V t

( + ( | | | |

=

( | |

(

\ \

(3.9)

( )

3

. 1 .

1 3. 1

. .sin( ) .sin( )

. 2

( )

P

o

C C

A m

R

t

z

V

t

C

( + ( | | | |

=

( | |

(

\ \

(3.9)

Como:

( )

3.

sin 1; sin 0

2

| |

= =

|

\

( )

3

( )

. 1 .

1

. 0

.

o

C

P

A m z t

RC

V t

( +

(

=

(

(3.9)

( )

3

. 1 .

.

)

.

(

o

C

P

A m z t

RC

V t

( +

=

(3.9)

Para a chave CH4, substituindo a equao (1.9) em (2.4), teremos:

( )

( ) ( )

4

. 1 . .sin .

C P

A m z t t

i t

R

( +

=

(4.0)

Substituindo a equao (4.0) na equao (3.3), teremos:

36

( ) ( )

2.

3.

.

4

2

. 1 . .sin .

( )

1

. .

c

c

C P

o

A m z t

t V t

t

d

C R

( +

=

(4.1)

( )

( )

2.

3.

2

4

.

. 1 .

. ( sin . .

.

)

c

c

o C

P

V t

A m z t

t dt

RC

( +

=

(4.1)

A integral indefinida de uma funo senoidal dada por:

( )

1

sin . . .cos( . ) x dx x

( )

4

. 1 .

1 2. 1 3.

. .cos( . ) ( .cos( . )

.

)

2.

o C C

P

C C C C

V t

A m z t

w w

RC

( + ( | | | |

=

( | |

(

\ \

(4.1)

( )

4

. 1 .

1 3. 1

. .cos( ) .cos(2. )

. 2

( )

C C

P

o

V t

A m z t

RC

( + ( | | | |

=

( | |

(

\ \

(4.1)

Como:

( )

3.

cos 0; cos 2. 1

2

| |

= =

|

\

( )

4

. 1 .

1

. 0

.

( )

P

o

C

A m z t

RC

V t

( + ( | |

=

( |

(

\

(4.1)

( )

4

. 1 .

.

)

.

(

o

C

P

A m z t

RC

V t

( +

=

(4.1)

As equaes (3.5), (3.7), (3.9) e (4.1) representam as quatro sadas do detector de

produto de Tayloe em funo do tempo, que nada mais so do que amostras do sinal de banda

base. Analisando a equao (3.5) e relao equao (3.9) podemos notar que os sinais de

entrada so defasados em 90, pois:

37

cos( ) sin( . )

2

C

t

=

O mesmo ocorre com respeito s equaes (3.7) e (4.1). Como cada sinal difere do

outro, respectivamente em 90, os sinais com defasagem de 180 podero ser somados,

acrescentando um ganho e resultando em dois novos sinais. Estes sinais resultantes so

denominados de sinal em fase (I) e sinal em quadratura (Q).

Ento, se somarmos diferencialmente as equaes (3.5) e (3.9), teremos o sinal em

fase (I). Da mesma forma, somando diferencialmente as equaes (3.7) e (4.1), teremos o

sinal em quadratura (Q).

( )

1 3

( ) ( )

o o

V t V t I t =

(4.2)

( )

( ) ( ) . 1 . . 1 .

. . . .

C C

P P

A m z t A m z t

I t

RC RC

| | | | ( ( + +

= | |

| |

\ \

(4.2)

( )

( ) ( ) . 1 . . 1 .

. . . .

C

P

C

P

A m z t A m z t

I t

RC RC

| | | | ( ( + +

= + | |

| |

\ \

(4.2)

( )

( ) . 1 .

2.

. .

P

C

A m z t

I t

RC

| | ( +

= |

|

\

(4.2)

( )

2 4

( ) ( )

o o

V t V t Q t =

(4.3)

( )

( ) ( ) . 1 . . 1 .

. . . .

C C

P P

A m z t A m z t

Q t

RC RC

| | | | ( ( + +

= | |

| |

\ \

(4.3)

( )

( ) ( ) . 1 . . 1 .

. . . .

C

P

C

P

A m z t A m z t

Q t

RC RC

| | | | ( ( + +

= + | |

| |

\ \

(4.3)

( )

( ) . 1 .

2.

. .

P

C

A m z t

Q t

RC

| | ( +

= |

|

\

(4.3)

Sabemos que:

2.

C

C

T

=

(4.4)

38

Portanto, substituindo a equao (4.4) nas equaes (4.2) e (4.3) respectivamente

teremos:

( ) ( ) . .(1 . )

. .

C

p

T

I t A m z t

RC

| |

= +

|

\

(4.5)

( ) ( ) . .(1 . )

. .

C

p

T

Q t A m z t

RC

| |

= +

|

\

(4.6)

Analisando os sinais ( ) I t e ( ) Q t podemos notar que estes representam nada mais do

que o sinal de banda base ( ) z t adicionado a uma componente contnua. Estes sinais em

quadratura podem ainda serem defasados separadamente, obtendo-se dois sinais iguais com

mesma fase. Se os mesmos forem somados, como resultado ter um nico sinal, no caso o

sinal de banda base desejado.

1.3.3. Largura de banda de deteco (banda base)

Um circuito RC, srie nada mais do que um filtro passa-baixa quando em regime

permanente de corrente alternada. Sua funo de transferncia[1] dada por:

( ) 1

( ) 1 . .

Y s

X s s R C

=

+

A freqncia de corte deste filtro determinada por:

( 3 )

1

( )

2. . .

dB

f Hz

RC

=

(4.7)

Como j mencionamos, a freqncia do sinal de banda base muito menor que a

freqncia do sinal da portadora. Como o perodo do chaveamento do circuito to pequeno,

39

para o sinal de banda base, em um perodo da portadora, podemos considerar que os quatro

capacitores C1, C2, C3 e C4 encontram-se em paralelo.

Portanto, como os quatro capacitores so iguais, como se estivssemos um novo

capacitor que assumir o valor:

1 2 3 4

resultante

C C C C C = + + +

Como:

1 2 3 4 C C C C C = = = =

Teremos que:

resultante

C C C C C = + + +

(4.8)

4.

resultante

C C =

(4.8)

Portanto, do ponto de vista do sinal da banda base podemos considerar que o circuito

resultante um circuito RC, em que a taxa de atenuao de 20 . A freqncia

de corte deste filtro, substituindo a equao (4.8) em (4,7) dada por:

( 3 )

1

( )

2. . .(4. )

dB

f Hz

R C

=

(4.9)

A largura de banda de um filtro dada por:

2 1 c c

BW f f =

(5.0)

Como o filtro do tipo passa-baixas:

2 ( 3 ) c dB

f f

=

(5.1)

2

1

2. . .(4. )

c

f Hz

R C

=

(5.1)

40

1

0

c

f Hz =

(5.2)

Portanto, substituindo as equaes (5.1) e (5.2) na equao (5.0) a largura de banda do

filtro para o sinal de banda base a ser demodulado determinado por:

2 1 c c

BW f f =

(5.0)

1

0

2. . .(4. )

BB

BW

R C

=

(5.3)

( )

1

2. . . 4.

BB

BW Hz

R C

=

(5.3)

1.3.4. Largura de banda de deteco (RF)

Do ponto de vista de radiofreqncia, como j mencionado anteriormente, o detector

de produto de Tayloe se comporta como um filtro passa-banda de alta seletividade. A Figura

10 ilustra idealmente a largura de banda de deteco do ponto de vista do sinal de banda base

e do ponto de vista de RF.

Figura 10 - Largura de banda de deteco do detector de produto de Tayloe.

41

O detector de produto de Tayloe pode ser analisado como um filtro de comutao

digital. Isso significa que ele opera como um filtro de alta seletividade e sua largura de banda

de deteco[8] dada por:

1

. . .

RF

BW Hz

n RC

=

(5.4)

Onde n o nmero de capacitores do detector. A seletividade do mesmo

determinada por:

C

RF

RF

f

Q

BW

=

(5.5)

Onde

C

f a freqncia do sinal a ser recebido, ou seja, a freqncia de comutao de

cada uma das chaves. Da Figura 12 podemos notar que a banda de deteco do detector de

Tayloe do ponto de vista de RF simplesmente o dobro da largura de banda do detector do

ponto de vista do sinal de banda base.

Vamos considerar que o detector de produto de Tayloe estar em um receptor

operando na freqncia de 10 MHz com largura de banda do sinal de banda base de 3kHz. O

resistor R ser representado pela impedncia da antena, por exemplo 50. Portanto, da

equao (5.3) que representa a largura de banda de deteco para o sinal de banda base,

acharemos o valor do capacitor C.

( )

1

( )

2. . . 4.

BB

BW Hz

R C

=

1

( )

2. . .4.

BB

C F

R BW

=

1

( )

2. .50.4.3000

C F

=

265 ( ) C n F

Da equao (5.4), a largura de banda de deteco de RF dada por:

42

1

. . .

RF

BW

n RC

=

6

RF

BW kHz

Como podemos observar, a largura de banda de deteco de RF nada mais do que a

translao no espectro de freqncia do filtro de banda base centrado na freqncia de

chaveamento de cada uma das chaves do detector, comprovando que:

2.

RF BB

BW BW =

Da equao (5.5), a seletividade deste detector dada por:

c

RF

RF

f

Q

BW

=

10

6000

RF

M

Q =

1670

RF

Q

Do valor encontrado para a seletividade do filtro podemos notar que o mesmo se

comporta com um filtro passa-banda de alta de alta seletividade, conforme mencionado

anteriormente.

43

2. Receptor de rdio AM para microcomputador

O sistema desenvolvido consiste de um receptor de rdio de converso direta para sinais

AM, operando em uma faixa de freqncias determinada (530kHz 1600kHz). Este receptor

de rdio foi desenvolvido utilizando o Detector de produto de Tayloe na etapa de converso

de freqncias seguindo determinadas tcnicas que o caracterizaro como um SDR.

Basicamente, um sistema de hardware responsvel pela parte de converso de freqncias,

sendo o processamento dos sinais e ajuste de freqncia realizada pelo microcomputador.

2.1. Diagrama de blocos do sistema

O sistema do receptor de rdio construdo com base em alguns princpios j utilizados

nos receptores tradicionais. Este sistema dotado de um filtro de entrada da antena, um

oscilador local dentre outros mais circuitos para tratamento dos sinais. O diagrama de blocos

do receptor mostrado na Figura 11.

Figura 11 - Diagrama de blocos geral do sistema.

44

2.1.1. Hardware do receptor

O hardware do sistema encarregado por toda a parte de converso de freqncia dos

sinais de entrada de RF. Como o receptor desenvolvido de converso direta, o mesmo

dever apresenta em sua sada o sinal de banda base desejado, sem a interveno de etapas

intermedirias no processo de converso de freqncias. O hardware composto de:

Filtro de entrada: o filtro de entrada do sistema tem a funo de atenuar os sinais de

rdio freqncia indesejado ao receptor. Idealmente, os sinais de rdio freqncia

desejados para este receptor correspondem a uma faixa determinada, ento o mesmo

deveria ter um filtro passa-banda na entrada da antena, porm, como a resposta em

freqncia do detector de Tayloe uma resposta passa banda, o mesmo possuir um

filtro passa-baixa, que desenvolve a funo de atenuar interferncias de sinais de

freqncias elevadas gerados pelo circuito de deteco.

Detector de Tayloe: o detector de produto de Tayloe tem a funo de demodular o

sinal de RF. O sinal de sada do detector o sinal de banda base desejado, sendo que,

o mesmo disponibiliza quatro sadas, defasadas respectivamente 90 uma da outra.

Amplificadores diferenciais: os amplificadores operacionais na configurao

diferencial tm a funo de subtrair os sinais vindos da sada do detector de Tayloe.

Na sada dos amplificadores diferenciais teremos duas sadas correspondentes

respectivamente ao sinal de banda base em fase (I) e a o sinal de banda base em

quadratura (Q).

Circuito defasador somador: este circuito tm a funo de defasar os sinais provindos

do circuito dos amplificadores somadores afim de torn-los dois sinais de mesma fase

e aps som-los, disponibilizando na sua sada um nico sinal analgico, de udio.

Oscilador Local: o oscilador local tem a funo de gerar o sinal de freqncia a ser

determinada para controle do chaveamento do detector de produto de Tayloe.

45

Microcontrolador (Firmware): o microcontrolador responsvel por receber dados

digitais provindos do microcomputador, interpret-los e ajustar a freqncia do

oscilador local para a freqncia desejada pelo usurio.

Conversor Paralelo/USB: este circuito responsvel por converter os dados digitais

provindos do microcontrolador de maneira paralela para sinais digitas dentro do

protocolo de comunicao USB.

2.1.2. Software e interface com o usurio

Como j mencionado anteriormente, o receptor desenvolvido tem caractersticas que o

designam como um SDR e, portanto toda a parte de processamento dos sinais vindo da placa

de hardware realizada pelo microcomputador. Em um SDR, os sinais em quadratura vindos

do hardware so injetados na entrada de udio no microcomputador e aps so digitalizados,

filtrados, demodulados e posteriormente disponibilizados em um sistema de udio.

Neste projeto, o sinal de banda base (udio) analgico provindo da placa de hardware

injetado a entrada de udio do microcomputador. Neste projeto, um aplicativo desenvolvido

em ambiente Windows processa este sinal da maneira adequada e disponibiliz-o na sada de

udio do mesmo. Este aplicativo tambm disponibiliza ao usurio final o ajuste da freqncia

de sintonia, sendo tudo realizado atravs do microcomputador e dos seus perifricos de

entrada e sada, que no caso sero o teclado, o mouse e ainda o sistema de udio e vdeo.

A comunicao entre o sistema de hardware do receptor com o microcomputador

realizada atravs do protocolo USB, pois atualmente existe um circuito integrado comercial

bastante utilizado fabricado pela FTDI (Future Technology Devices International) que

possibilita a comunicao a elevadas taxas de transmisso, sendo estas suficientes para o

projeto a ser desenvolvido.

2.2. Desenvolvimento do hardware

Neste item so apresentado

hardware da Figura 13. Para uma melhor compreenso,

dos circuitos projetados.

2.2.1. Circuito do filtro passa

O filtro de entrada do receptor

utilizados somente componentes discretos como capac

deste filtro na entrada do receptor

disso, foi escolhido um filtro passa

na banda passante por apresentar uma resposta praticamente plana na banda p

juntamente a uma boa atenuao das freqncias indesejveis.

na Figura 12.

Do circuito da Figura

e

2

R a resistncia de carga do circuito

descritas a seguir. A relao entre as resistncias dada por:

Os valores dos indutores e capacitores do circuito so dados por:

apresentados os circuitos projetados para cada um dos blocos da

Para uma melhor compreenso, juntamente esto anexad

iltro passa-baixas

O filtro de entrada do receptor um filtro passa-baixa do tipo passivo, onde so

utilizados somente componentes discretos como capacitores, indutores e resistores. A funo

ltro na entrada do receptor atenuar as freqncias indesejveis na recepo, em vista

disso, foi escolhido um filtro passa-baixa do tipo Chebyshev de 5 ordem com 0,5dB de ripple

por apresentar uma resposta praticamente plana na banda p

juntamente a uma boa atenuao das freqncias indesejveis. O circuito do filtro mostrado

Figura 12 - Circuito do filtro passa-baixas.

Figura 12 temos que

1

R representa a impedncia da antena do receptor

a resistncia de carga do circuito. As equaes[4] para dimensionamento deste filtro so

descritas a seguir. A relao entre as resistncias dada por:

1 2

. R r R =

s valores dos indutores e capacitores do circuito so dados por:

1

.

k k

c

R

L g

=

(5.6)

46

os circuitos projetados para cada um dos blocos da parte de

o anexadas simulaes

baixa do tipo passivo, onde so

itores, indutores e resistores. A funo

atenuar as freqncias indesejveis na recepo, em vista

do tipo Chebyshev de 5 ordem com 0,5dB de ripple

por apresentar uma resposta praticamente plana na banda passante

O circuito do filtro mostrado

resenta a impedncia da antena do receptor

para dimensionamento deste filtro so

s valores dos indutores e capacitores do circuito so dados por:

47

1

1

.

.

k k

c

C g

R

=

(5.7)

Onde

C

representa o valor da freqncia de corte do filtro em

rad

s

e

k

g so os

valores dos indutores e dos capacitores do filtro normalizados para:

1

1( ) r =

1( )

c

rad

s

=

A ordem do filtro representada por n . Os parmetros r e

n

g so obtidos da

comparao entra a funo de transferncia do circuito do filtro com as funes de filtragem

e, os seus valores so no caso filtros de Chebishev dados por:

Para n mpar = :

1 r =

Para 1 k = :

2.

k

k

a

g

=

Para 2,3, , k n = :

1

1 1

4. .

.

k k

k

k k

a a

g

b g

=

Onde, para 1, 2,3, , k n = :

( ) 2. 1 .

sin

2.

k

k

a

n

(

=

(

48

2 2

.

sin ( )

k

k

b

n

= +

sinh( )

2.n

=

Em diversos livros especficos sobre anlise de filtros, encontram-se tabelas com os

valores de

k

g para filtros com diferentes ordens, e diferentes valores de ripple na banda de

passagem, para fins de anlise de sua sntese. A Tabela 2 apresenta os valores de

k

g para

filtros de ordem 1 6 com 0,5dB de amplitude de ripple na banda passante.

Tabela 2 - Elementos normalizados do filtro tipo Chebyshev com 0,5dB.[12]

O receptor, como j mencionado, ir receber sinais AM com largura de banda de:

1600 530 BW kHz kHz =

1, 07 BW MHz =

Como o filtro ser do tipo passa-baixa, a freqncia de corte ser dada ento por:

1600

c

f kHz =

49

Como:

2. . ( )

C c

rad

f

s

=

Ento:

2. .1, 6 ( )

C

rad

M

s

=

10, 05 ( )

C

rad

M

s

Para o projeto do filtro, sabemos que:

1

50 R =

0, 5

p

A dB =

5 n =

Da Tabela 2:

1

1, 7058 g =

2

1, 2296 g =

3

2, 5408 g =

4

1, 2296 g =

5

1, 7058 g =

Como

1 5

g g = , da equao (5.7):

( )

1 5 6

1

. 1, 7058

50.10, 05 10

C C F

x

| |

= =

|

\

1 5

3, 4 C C nF =

( )

3 6

1

. 2, 5408

50.10, 05 10

C F

x

| |

=

|

\

3

5, 0 C nF

50

Como

2 4

g g = , da equao (5.6):

( )

4 2

50

. 1, 2296

10, 05

L L H

M

| |

= =

|

\

2 4

6,1 L L H =

Portanto, como os valores dos capacitores, indutores e capacitores calculados nem

sempre so valores aos quais os fabricantes disponibilizam. Em valores comerciais teremos:

1 2

50 R R = =

1 5

3, 3 C C nF = =

3

4, 7 C nF =

4

6, 2

s

L L H = =

Na Figura 25 presente no Anexo A temos a resposta em freqncia deste filtro

simulado no software Proteus, onde podemos notar uma alta atenuao das freqncias

indesejveis.

2.2.2. Circuito do detector de produto de Tayloe

O circuito do detector de produto de Tayloe feito utilizando-se chaves analgicas

como podemos observar na Figura 7. Cada uma das chaves ir permanecer fechada por um

quarto do perodo do sinal de RF ao qual queremos demodular, portanto, ser utilizado um

circuito integrado que possui internamente quatro chaves analgicas, e ainda, outro circuito

integrado que far o acionamento das chaves, sendo que este dever ter um sinal na sua

entrada quatro vezes maior que a freqncia do sinal de interesse, para fim de que cada chave

permanea fechada o tempo determinado pela freqncia do sinal a sua entrada.

51

O circuito integrado das chaves analgicas ser o 74HC4066[12] fabricado pela

PHILIPS, escolhido devido a algumas de suas caractersticas, onde vale citar seu baixo valor

da resistncia da chave quando fechada, pois esta estar em srie com a antena, e quanto

menor seu valor menor a perda por converso do detector. A Figura 13 mostra o smbolo

lgico das chaves deste circuito integrado juntamente a sua tabela funcional. As principais

razes para escolha deste circuito integrado so:

Baixa resistncia ON;

- 50 tpico para V

CC

= +4,5V;

- 45 tpico para V

CC

= +6,0V;

- 35 tpico para V

CC

= +9,0V;

Alimentao: V

CC

= -0,5V V

CC

= +11,0V;

Mxima variao de resistncia ON;

- 5 tpico para V

CC

= +4,5V;

- 4 tpico para V

CC

= +6,0V;

- 3 tpico para V

CC

= +9,0V;

Freqncia mxima de operao;

- 180 MHz para V

CC

=+4,5V, R

L

=50 e C

L

=10pF;

- 200 MHz para V

CC

=+9,0V, R

L

=50 e C

L

=10pF;

Mxima capacitncia da chave de 8pF;

52

Figura 13 - Smbolo lgico e tabela de acionamento do CI 74HC4066.

O circuito integrado utilizado para acionamento das chaves analgicas utilizado o

MC74HC4017N[14]

]

fabricado pela MOTOROLA. Este circuito integrado um contador de

dcadas que utiliza na sua arquitetura interna cinco estgios de contadores Johnson e os

decodifica promovendo uma operao em alta velocidade. A Figura 14 mostra o diagrama

lgico deste circuito juntamente a sua tabela funcional. Este circuito integrado foi escolhido

devido a algumas de suas caractersticas dentre as quais:

Sadas diretamente interfaceadas para CMOS, NMOS e TTL;

Alimentao: V

CC

= -0,5V V

CC

= +7,0V;

Alta imunidade a rudo de dispositivos CMOS;

Baixa corrente de entrada: 1 A;

Mxima freqncia de clock (50% duty cycle);

- 4 MHz para V

CC

=+2,0V e -55C<TAMB<25C

- 20 MHz para V

CC

=+4,5V e -55C<TAMB<25C

- 24 MHz para V

CC

=+6,0V e -55C<TAMB<25C

53

Figura 14 - Diagrama lgico e tabela funcional do CI 74HC4017N.

Generalizando, a caracterstica principal pela qual estes dois circuitos integrados

foram escolhidos a sua freqncia mxima de operao, pois este um fato determinante

para o projeto. A freqncia mxima de comutao a qual ser submetida cada uma das

chaves analgicas ser a prpria freqncia de sintonia do receptor e a freqncia mxima do

sinal TTL na entrada do CI para acionamento das chaves quatro vezes maior, ento,

teremos:

1600

tunning

f kHz =

4.1600

tayloe

f kHz =

6, 4

tayloe

f MHz =

Portanto, a freqncia mxima do sinal aplicado na entrada de controle da chave e na

entrada do CI para acionamento das chaves para a tenso de alimentao de +5V dada,

respectivamente por:

74 4066

180

HC

mx

f MHz

1, 6

mx

comutao

f MHz =

74 4066 mx HC

comutao mx

f f <

54

1, 6 180 MHz MHz <

74 4017

20

HC

mx

f MHz

1, 6

mx

sinal

f MHz =

74 4017 mx HC

sinal mx

f f <

6, 4 20 MHz MHz <

Estas relaes demonstradas acima deixam bem claro que o circuito no apresentar

problemas quando estiver operando na sua freqncia mxima de sintonia. A Figura 15 ilustra

o circuito do detector de produto de Tayloe.

55

Figura 15 - Circuito do detector de produto de Tayloe.

Como podemos ver, aps passar por um resistor que no caso representado pela

impedncia da antena o sinal de entrada ligado diretamente as entradas das quatro chaves,

em paralelo. Quando uma chave fechada o circuito resultante um circuito RC, passa-baixa,

e da equao (5.3) calcularemos o valor dos capacitores C1, C2, C3 e C4 para uma largura de

banda determinada.

Um sinal modulado em amplitude tem por definio que o sinal de banda base um

sinal de voz, ento, sua largura de banda ser determinada por:

4

BB

BW kHz =

Da equao (5.3), o valor dos capacitores C1, C2, C3 e C4 sero dados por:

( )

1

2. . . 4.

BB

BW Hz

R C

=

56

Onde o resistor dado pela impedncia de entrada da antena e ainda a resistncia da

chave quando q mesma encontra-se fechada (ON). Da folha de dados do circuito integrado

74HC4066 a resistncia que as chaves apresentam quando se encontram em estado ON :

50

switchon

R

Ento:

_

switchon

R R R ANTENA = +

50 50 R = +

100 R =

Portanto, o valor de C ser:

1

2. . .4.

BB

C F

R BW

=

1

2. .100.4.4000

C F

=

100 C nF

Sendo que:

1 2 3 4

C C C C C = = = =

O circuito integrado 74HC4066 ser alimentado com uma tenso de +5V. Na sua folha

de dados, temos que com uma alimentao unipolar, quando a chave estiver fechada, somente

passar sinais por ela que estejam compreendidos entre sua tenso de alimentao, portanto,

ser adicionada uma tenso DC ao sinal de entrada vindo da antena, para no ocorrer perda da

parte negativa deste sinal. O acionamento das chaves realizado pelo circuito integrado

74HC4017, que disponibiliza 10 sadas digitais, sendo que somente so utilizadas 4 destas

sadas e para isto utilizado o pino de master reset, que acionado quando ocorre mudando

de nvel lgico baixo para nvel lgico alto na sada Q4 do mesmo.

57

Como todo o circuito ser alimentado com a tenso de +5V, faremos um divisor

resistivo a fim de acrescentar essa tenso contnua na entrada da chave analgica. O circuito

dado pelos componentes: R1, R2, R3, C5 e C6. Os resistores R1 e R2 formaro um divisor

resistivo com o valor da metade da tenso de alimentao, sendo que os capacitores C5 e C6

tero a funo de estabilizar a tenso caso ocorra oscilaes na fonte de alimentao do

circuito sendo que a tenso gerada injetada nas entradas das chaves analgicas atravs do

resistor R3. Portanto, faremos com que:

1 2

6, 8 R R k = =

3

270 R =

5

22 C F =

6

100 C nF =

2.2.3. Circuito dos amplificadores diferenciais

A funo deste circuito realizar a subtrao de quatro sinais de banda base provindos

das quatro sadas do detector de produto de Tayloe. Essa soma realizada atravs de

amplificadores operacionais. Aps uma anlise de diversos circuitos integrados de

amplificadores operacionais, por diversos fatores o amplificador operacional utilizado ser o

circuito integrado NE5534[13] fabricado pela Philips Semiconductors. Suas principais

caractersticas so:

Tenso de rudo de entrada mxima de 4 ;

Ganho de tenso AC: 6000 10kHz;

Slew rate: 13V/s;

Tenso de alimentao: 3V 20V.

Na Figura 16 temos o circuito de um dos amplificadores somadores.

58

Figura 16 - Circuito de um amplificador diferencial.

Neste circuito, idealmente deveramos ter um resistor conectado ao terminal positivo

do amplificador operacional para ser considerado como um amplificador na configurao

diferencial. Como o ganho dos amplificadores deve ser ajustado devido ao fato dos sinais

disponibilizados pelo detector de Tayloe possurem um leve desbalanceamento, este corrigido