Escolar Documentos

Profissional Documentos

Cultura Documentos

Lista 1

Enviado por

Paulo Fernando PaimDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Lista 1

Enviado por

Paulo Fernando PaimDireitos autorais:

Formatos disponíveis

ENGC40 - Eletr onica Digital 1a Lista - Exerc cios de Revis ao

Prof. Paulo Farias 13 de mar co de 2012

1. A Figura 1 mostra um circuito multiplicador que recebe dois n umeros bin arios x1 x0 e y1 y0 e gera a sa da z3 z2 z1 z0 , que e igual ao produto dos valores de entrada. Projete o circuito l ogico, considerando que o multiplicador s o trabalha com n umeros naturais.

Figura 1: Multiplicador. 2. Na Figura 2 temos o circuito de decodica ca o de endere cos usado por um determinado microprocessador (MPU). Apesar de possuir 16 bits de endere camento, este microprocessador s o est a usando os oito bits mais signicativos para decodicar os dispositivos mostrados. O c odigo do endere co e aplicado ao circuito l ogico, que gera os sinais de sele ca o RAM , ROM e I/O. Analise o circuito e identique as faixas de endere cos que ativam os dispositivos representados.

Figura 2: Decodica ca o de endere cos. 1

3. As formas de onda mostradas na Figura 3(a) s ao aplicadas ao circuito da Figura 3(b). Considere que inicialmente Q = 0 e determine a forma de onda da sa da Q.

(a) Formas de onda.

(b) Circuito.

Figura 3: Circuito sequencial. 4. Aplique as formas de onda J, K e CLK mostradas na Figura 4 a um FF JK de transi ca o negativa. Considere que inicialmente Q = 1 e determine a forma de onda da sa da Q.

Figura 4: Formas de onda. 5. Mostre como um FF D disparado por borda pode ser congurado para funcionar como um FF tipo T. 6. No circuito mostrado na Figura 5, as entradas A, B e C est ao incialmente em n vel BAIXO. Sup oe-se que a sa da Y v a para n vel ALTO apenas quando A, B e C forem para n vel ALTO em determinada sequ encia. (a) Determine a sequ encia que faz com que Y v a para n vel ALTO. (b) Explique a necessidade do pulso IN ICIO. (c) Modique o circuito, de modo a usar FFs tipo D.

Figura 5: Sequenciador. 7. Analise o circuito contador mostrado na Figura 6. (a) Se o contador come car em 000, qual ser a o valor da contagem ap os 13 pulsos de clock? E ap os 99 pulsos? E ap os 256 pulsos? (b) Repita o item anterior, considerando que o contador come cou com 100. (c) Conecte um quarto FF JK (X3 ) ao circuito e desenhe o diagrama de transi ca o de estados para esse novo contador de 4 bits. Se a frequ encia do clock for 80 MHz, como ser a a forma de onda na sa da de X3 ?

Figura 6: Contador. 8. Um somador completo pode ser implementado de diversas formas. A Figura 7 mostra como um somador completo pode ser constru do a partir de dois meio-somadores (HA-Half Adder ). Construa uma tabela-verdade para esta congura ca o e observe que este circuito funciona como um somador completo (FA-Full Adder ).

Figura 7: Full Adder. 9. Projete um somador bin ario de 4 bits que implementa a solu ca o lookahead carry para o problema de atraso provocado pela propaga ca o do carry (carry ripple ). 10. Um contador ass ncrono de quatro bits e acionado por um clock de 20 MHz. Desenhe as formas de onda na sa da de cada FF, considerando que cada um deles tem um tempo de atraso de propaga ca o (tpd ) de 20 nseg. Determine quais estados de contagem, caso existam, n ao ocorrer ao em virtude dos atrasos de propaga ca o. Qual a frequ encia m axima de clock que pode ser usada neste contador? Se o contador fosse expandido para seis bits, qual seria a m axima frequ encia de opera ca o? 11. Analise os circuitos mostrados na Figura 8. Responda as seguintes quest oes para os dois casos: (a) Desenhe o diagrama de transi ca o de estados para as sa das do contador. (b) Determine o m odulo do contador. (c) Qual a rela ca o da frequ encia de sa da do MSB com a frequ encia do clock? (d) Qual o ciclo de trabalho da forma de onda da sa da do MSB?

Figura 8: Contadores. 12. Analise o circuito mostrado na Figura 9a. (a) Desenhe o diagrama de transi ca o de estados para as sa das do contador. (b) Determine o m odulo do contador. crescente ou decrescente? (c) Qual a sequ encia de contagem? E (d) Podemos reproduzir a mesma sequ encia de contagem com um 74HC190?

Figura 9: Contadores. 13. Em rela ca o ao contador da Figura 9b: (a) Descreva a sa da do contador se ST ART estiver em n vel BAIXO. (b) Descreva a sa da do contador se ST ART estiver momentaneamente em n vel BAIXO e depois retornar ao n vel ALTO. 5

(c) Qual o m odulo do contador? Ele e auto-recicl avel? 14. Analise os contadores s ncronos da Figura 10. Desenhe os seus diagramas temporais e obtenha o m odulo de contagem de cada um.

Figura 10: Contadores. 15. Analise os contadores s ncronos da Figura 11. Desenhe os seus diagramas temporais e obtenha o m odulo de contagem de cada um.

Figura 11: Contadores. 16. Projete um contador s ncrono usando FFs JK, que tenha a seguinte sequ encia: 0, 2, 5, 6 e repete. Os estados esp urios devem ser direcionados para 0. 17. Refa ca o projeto da quest ao 16, sem nenhuma restri ca o em rela ca o aos estados esp urios. Compare os projetos. 18. O circuito mostrado na Figura 12 usa tr es multiplexadores de duas entradas. Determine a sua fun ca o l ogica.

Figura 12: Circuito baseado em multiplexadores. 7

19. Desenhe a forma de onda em Z (Figura 13).

Figura 13: Gerador de forma de onda. 20. O circuito da Figura 14 mostra como um MUX de oito entradas pode ser usado para gerar uma fun ca o de quatro vari aveis l ogicas, mesmo que existam apenas tr es entradas de sele ca o. (a) Construa a tabela-verdade do circuito. (b) Mostre que a equa ca o do circuito e: A + DC BA + DC B A Z = CB

Figura 14: Circuito baseado em multiplexador. 21. Considere o circuito da Figura 15. (a) Verique se algum dos seguintes endere cos ativa o m odulo de mem oria: 0x607F, 0x57FA, 0x5F00. (b) Determine a faixa de endere cos dessa mem oria. (c) Suponha que outro m odulo de mem oria seja acrescentado ao circuito, 4 do 74ALS138. Qual a sua de forma a ser habilitado pela linha O faixa de endere cos?

poss (d) E vel ao microprocessador acessar as duas mem orias ao mesmo tempo? Explique.

Figura 15: Interface entre microprocessador e mem oria. 22. Usando um multiplexador de 4 entradas e com o m nimo poss vel de portas l ogicas, implemente a fun ca o: f (w1 , w2 , w3 , w4 , w5 ) = w 1 w 2 w 4 w 5 + w1 w2 + w1 w3 + w1 w4 + w3 w4 w5 23. Projete um circuito para detectar n umeros primos de 4 bits, ou seja, a sa da e ativa em n vel alto se o n umero de entrada for primo. 24. Projetar um contador com a seguinte sequ encia de estados: ...0, 3, 5, 7, 1, 4, 0, 3.... Para evitar la cos esp urios, direcione os estados inexistentes para 0. 25. Projete um circuito combinacional comparador de magnitude para dois n umeros naturais X e Y . O circuito possui duas sa das G e L, que atendem as seguintes regras: (a) G = 1, se X > Y (b) G = 0, se X Y (c) L = 1, se X < Y (d) L = 0, se X Y A partir deste circuito, como poder amos detectar as condi co es X = Y e X = Y ? Considere que X e Y s ao n umeros de dois bits. 9

26. Usando a estrutura representada na Figura 16, implemente a fun ca o l ogica: f (w1 , w2 , w3 ) = w2 w 3 + w1 w3 + w 2 w3

Figura 16: Bloco l ogico. 27. Mostre como implementar a fun ca o l ogica representada pela Tabela 1 usando 1 decodicador de 3 entradas e 1 porta OU. INPUT 000 001 010 011 100 101 110 111 OUTPUT 0 1 1 1 0 1 1 0

Tabela 1: Fun ca o l ogica. 28. Projete um contador up /down de 3 bits, usando ip-ops T. O contador deve incluir a entrada de controle U /D de tal forma que, se U /D = 0, a contagem e crescente. Se U /D = 1, o circuito se comporta como um contador decrescente. Equa ca o do FF T: Qn+1 = T Qn + T Qn

10

Você também pode gostar

- LIVRO A Arte de Argumentar Antonio Suarez AbreuDocumento64 páginasLIVRO A Arte de Argumentar Antonio Suarez AbreuLuiz Carlos Tolentino100% (2)

- Controladores lógicos programáveis práticaDocumento61 páginasControladores lógicos programáveis práticaLeonardo Costa100% (1)

- Tabela Da Atalhos - Excel PDFDocumento1 páginaTabela Da Atalhos - Excel PDFpollyannasilvad33% (3)

- Arduino robô visão computacionalDocumento44 páginasArduino robô visão computacionalEtelvino OliveiraAinda não há avaliações

- Métodos de Gauss e Gauss-Seidel para resolução numérica de sistemas linearesDocumento301 páginasMétodos de Gauss e Gauss-Seidel para resolução numérica de sistemas linearesPaulo Fernando PaimAinda não há avaliações

- Manual Promark500Documento306 páginasManual Promark500Erison Barros0% (1)

- Apresentação Medidas Eletricas e Magneticas PDFDocumento120 páginasApresentação Medidas Eletricas e Magneticas PDFPaulo Fernando PaimAinda não há avaliações

- Guia Prático para Instalação e Utilização Do Software SEL-5032 AcSELerator ArchitectDocumento35 páginasGuia Prático para Instalação e Utilização Do Software SEL-5032 AcSELerator ArchitectHenrique Pereira MachadoAinda não há avaliações

- Proposta Link 12MbpsDocumento5 páginasProposta Link 12MbpsBruno Fonseca100% (1)

- ORATOPDocumento13 páginasORATOPramilanezAinda não há avaliações

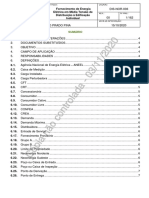

- Fornecimento de energia em média tensãoDocumento162 páginasFornecimento de energia em média tensãoKelvin SilvaAinda não há avaliações

- Diário Oficial do Estado da Bahia decreta utilidade pública de áreasDocumento100 páginasDiário Oficial do Estado da Bahia decreta utilidade pública de áreasPaulo Fernando PaimAinda não há avaliações

- Portarias de exoneração e conclusão de ensino médioDocumento1 páginaPortarias de exoneração e conclusão de ensino médioPaulo Fernando PaimAinda não há avaliações

- Apostila UFBA Pré-SEPDocumento66 páginasApostila UFBA Pré-SEPPaulo Fernando PaimAinda não há avaliações

- Projeto de cenotecniaDocumento5 páginasProjeto de cenotecniaPaulo Fernando PaimAinda não há avaliações

- Termo de ReferênciaDocumento10 páginasTermo de ReferênciaPaulo Fernando PaimAinda não há avaliações

- Reflexoessobrepossibilidades Tiago 2019Documento117 páginasReflexoessobrepossibilidades Tiago 2019Paulo Fernando PaimAinda não há avaliações

- Fornecimento de Energia Elétrica a EdifíciosDocumento225 páginasFornecimento de Energia Elétrica a EdifíciosFernando SantosAinda não há avaliações

- SEP 1 - Cap 3 Item 3.1.3 - Indutancia e Reatancia Indutiva PDFDocumento40 páginasSEP 1 - Cap 3 Item 3.1.3 - Indutancia e Reatancia Indutiva PDFDaniloT.HungaroMichelettiAinda não há avaliações

- CEIEDocumento1 páginaCEIEPaulo Fernando PaimAinda não há avaliações

- Instalações Elétricas - ExercíciosDocumento8 páginasInstalações Elétricas - ExercíciosPaulo Fernando PaimAinda não há avaliações

- Análise de Sistemas de Potência: Elementos ChaveDocumento236 páginasAnálise de Sistemas de Potência: Elementos ChavePaulo Fernando PaimAinda não há avaliações

- Stevenson - Elementos de Análise de Sistemas de Potência PDFDocumento236 páginasStevenson - Elementos de Análise de Sistemas de Potência PDFPaulo Fernando PaimAinda não há avaliações

- Automatização de Processos IndustriaisDocumento41 páginasAutomatização de Processos IndustriaisElkjaer BrazAinda não há avaliações

- HORTALIÇAS de A A ZDocumento48 páginasHORTALIÇAS de A A ZPaulo Fernando PaimAinda não há avaliações

- Lista TermoDocumento8 páginasLista TermoRonald BastosAinda não há avaliações

- Lista OscilaDocumento2 páginasLista OscilaMarcelo CarcaráAinda não há avaliações

- Curso de Caligrafia PDFDocumento102 páginasCurso de Caligrafia PDFcarolinamayo100% (1)

- Telefonia Basica 1Documento30 páginasTelefonia Basica 1Augusto Otto CannataroAinda não há avaliações

- Princípios de Motores de Indução AssíncronoDocumento8 páginasPrincípios de Motores de Indução AssíncronoRamon Platini SarchiAinda não há avaliações

- Rede Sem Fio ProjetoDocumento27 páginasRede Sem Fio ProjetoYwandeyAinda não há avaliações

- Acesso RemotoDocumento2 páginasAcesso RemotoFrederico PimentelAinda não há avaliações

- Guia Do Estudante P2000 3.8 & CK720 e CK721-Rev369Documento268 páginasGuia Do Estudante P2000 3.8 & CK720 e CK721-Rev369Carlos Eberhard Diaz TorresAinda não há avaliações

- Usando o Controle ReportViewer Do WinForms - Microsoft DocsDocumento25 páginasUsando o Controle ReportViewer Do WinForms - Microsoft DocsSales JuniorAinda não há avaliações

- Regulamento TIM Controle GIGA B Promo Express - Versão FinalDocumento8 páginasRegulamento TIM Controle GIGA B Promo Express - Versão FinalWaldemir JúniorAinda não há avaliações

- Eusouandroid Com Download Picsart Photo Studio Verso AtualizDocumento9 páginasEusouandroid Com Download Picsart Photo Studio Verso Atualizjhean.waggner2014Ainda não há avaliações

- Apresentação Ronni Aurora VisionDocumento14 páginasApresentação Ronni Aurora VisiondutrafaissalAinda não há avaliações

- Tudo Sobre ProcessadorDocumento5 páginasTudo Sobre ProcessadorJon AraujoAinda não há avaliações

- EATIC Artes e Expressões-Literacia Informática-QuestionárioDocumento1 páginaEATIC Artes e Expressões-Literacia Informática-QuestionárioAntónio MarquesAinda não há avaliações

- Caderno de Atividades - MISI e MCD - 2º Redes - AgostoDocumento8 páginasCaderno de Atividades - MISI e MCD - 2º Redes - AgostoJosé VidalAinda não há avaliações

- Manual Receiver Sony STR De885Documento68 páginasManual Receiver Sony STR De885Reilton Azeredo100% (4)

- PDF ClassDocumento3 páginasPDF ClassTony GuirrugoAinda não há avaliações

- Connectio Je03 Rev3.00Documento11 páginasConnectio Je03 Rev3.00Pedro Augusto PeresAinda não há avaliações

- Configurações de DNS Centos 7Documento4 páginasConfigurações de DNS Centos 7Anonymous cZGJ7Rsk1Ainda não há avaliações

- Ata de Registro de Preços - Hospital UniversitárioDocumento57 páginasAta de Registro de Preços - Hospital UniversitáriogillieryAinda não há avaliações

- Periféricos de EntradaDocumento4 páginasPeriféricos de EntradasantosleilaAinda não há avaliações

- Redes de Telefonia Celular e Transmissão de DadosDocumento48 páginasRedes de Telefonia Celular e Transmissão de DadosHugoAinda não há avaliações

- LG DVD Player 556/586Documento20 páginasLG DVD Player 556/586Geraldo Majella GuimaraesAinda não há avaliações

- Audacity - Editor de áudio gratuito com efeitos e recursos profissionaisDocumento4 páginasAudacity - Editor de áudio gratuito com efeitos e recursos profissionaisJose Roberto MartinezAinda não há avaliações

- Anexo I - Termo de Requisição de Aparelho CelularDocumento6 páginasAnexo I - Termo de Requisição de Aparelho CelularandrelmacedoAinda não há avaliações

- FundCompArq24hDocumento93 páginasFundCompArq24hvictor_timaoAinda não há avaliações

- Utilizando o WINMFD 2Documento2 páginasUtilizando o WINMFD 2reneemouraAinda não há avaliações

- Manual de Instalação Do Software AutoTOPO PDFDocumento25 páginasManual de Instalação Do Software AutoTOPO PDFjormaxfilhoAinda não há avaliações