Escolar Documentos

Profissional Documentos

Cultura Documentos

Fenix Especificacao 8051 CPU

Fenix Especificacao 8051 CPU

Enviado por

AbelGuilherminoDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Fenix Especificacao 8051 CPU

Fenix Especificacao 8051 CPU

Enviado por

AbelGuilherminoDireitos autorais:

Formatos disponíveis

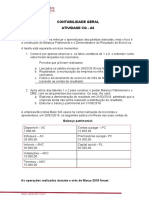

Especificao Funcional

Microcontrolador 8051 CPU

Projeto Fnix

BRAZIL IP

Verso 2.1 | 02/09/2003

Responsvel: Tiago Sampaio Lins

{tsl@cin.ufpe.br}

Fnix Project

Microcontrolador 8051 - CPU

Histrico de Alteraes

Data

Verso

Descrio

Autor

06/08/03

1.0

Primeira

verso

do

Especificao da CPU.

documento

de (jfbs, jcs, tsl)@cin.ufpe.br

01/09/03

2.0

Segunda

verso

do

Especificao da CPU.

documento

de (jfbs,jcs,aaca)@cin.ufpe.br

02/09/03

2.1

Correo ortogrfica.

(jfbs,jcs,aaca)@cin.ufpe.br

Lista de Aprovadores

Nome

Cargo

Edna Barros

Coordenadora Geral do Projeto Fnix

Srgio Cavalcante

Coordenao de Divulgao Externa do Brazil-IP

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 2/97

Microcontrolador 8051 - CPU

Fnix Project

Contedo

1. Caso de Uso Executar Instruo..................................................................................................... 16

1.1 Convenes, termos e abreviaes________________________________________________ 16

OV........................................................................................................................................................ 16

Overflow............................................................................................................................................... 16

SP......................................................................................................................................................... 16

Stack Pointer........................................................................................................................................ 16

ACC, A................................................................................................................................................. 16

Acumulador......................................................................................................................................... 16

IR.......................................................................................................................................................... 16

Registrador de Instruo..................................................................................................................... 16

DPTR LOW......................................................................................................................................... 16

Data Pointer Registrar Low................................................................................................................ 16

DPTR HIGH........................................................................................................................................ 16

Data Pointer Registrar High............................................................................................................... 16

PSW...................................................................................................................................................... 16

Program Status Work.......................................................................................................................... 16

C........................................................................................................................................................... 16

Carry flag............................................................................................................................................. 16

AC......................................................................................................................................................... 16

Carry flag auxiliar............................................................................................................................... 16

B........................................................................................................................................................... 16

Registrador B....................................................................................................................................... 16

SBUF.................................................................................................................................................... 16

Registrador usado no recebimento e na transferncia de dados da USART (Para maiores detalhes

vide a especificao da USART)........................................................................................................... 16

Write_to_sbuf....................................................................................................................................... 16

Sinal usado para escrever no SBUF (Para maiores detalhes vide a especificao da USART)......16

P0, P1, P2 e P3.................................................................................................................................... 16

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 3/97

Microcontrolador 8051 - CPU

Fnix Project

Portas de entradas e sada do 8051 (Para maiores detalhes vide especificao das portas de

entrada e sada) ................................................................................................................................... 16

1.2 Descrio___________________________________________________________________ 16

1.3 Diagrama Comportamental_____________________________________________________ 17

2. Diagrama de Blocos......................................................................................................................... 18

Nesta sesso ser mostrado um diagrama de blocos para a CPU do microcontrolador 8051 e como

foi feita a especificao do seu repertrio de instrues j se fazendo uma breve explanao de cada

uma......................................................................................................................................................... 18

A especificao do repertrio de instrues foi feita agrupando as instrues em cinco grupos:

operaes aritmticas, operaes lgicas, transferncia de dados, manipulao de variveis

booleanas e desvio de programa. O agrupamento foi feito com base na semelhana da operao

que cada instruo executa e pela forma de endereamento comum................................................. 18

Ainda dentro de cada grupo especificamos detalhadamente cada instruo e sugerimos um

diagrama de estados para uma possvel implementao..................................................................... 18

O diagrama de blocos abaixo mostra a arquitetura do microcontrolador 8051, temos um

barramento de dados de 8 bits, um barramento de endereo de 16 bits, os seguintes registradores:

SP, ACC, IR, DPTR LOW, DPTR HIGH e o PSW como registradores de 8 bits. A memria RAM

com 256 posies endereadas a byte e, contida nesta, a regio endereada a bit que vai do

endereo 20H a 2FH. Temos ainda as portas de entrada e sada P0, P1, P2 e P3. ........................... 18

Para um entendimento completo do restante da especificao o sumrio de termos apresentado

abaixo:................................................................................................................................................... 19

TERMO................................................................................................................................................ 19

DESCRIO....................................................................................................................................... 19

SFR...................................................................................................................................................... 19

Registrador de Funo Especial......................................................................................................... 19

Ciclo..................................................................................................................................................... 19

Um ciclo corresponde a 12 pulsos de clock na freqncia de 33 MHz............................................. 19

Rn......................................................................................................................................................... 19

Corresponde ao registrador R7-R0 do banco de registradores ativo................................................. 19

Direto................................................................................................................................................... 19

Endereo de um dado de 8 bits. Esse dado pode est localizado na RAM interna (0-127) ou um

SFR [portas de E/S, PSW, TCOM, etc. (128-255)].............................................................................. 19

@Ri....................................................................................................................................................... 19

Endereo de um dado de 8 bits localizado na RAM interna endereado indiretamente pelos

registradores R0 e R1. ......................................................................................................................... 19

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 4/97

Microcontrolador 8051 - CPU

Fnix Project

#dado.................................................................................................................................................... 19

Uma constante de 8 bits contida na instruo.................................................................................... 19

#dado 16............................................................................................................................................... 19

Uma constante de 16 bits contida na instruo.................................................................................. 19

Addr 16................................................................................................................................................. 19

Endereo de destino com 16 bits. Usado nas instrues LCALL e LJMP........................................ 19

Addr 11................................................................................................................................................. 20

Endereo de destino com 11 bits. Usado nas instrues ACALL e AJMP.......................................20

Rel........................................................................................................................................................ 20

Offset de 8 bits com sinal. Usado pela instruo SJMP e todas as instrues de desvio condicional.

Seu valor varia de 128 a +127............................................................................................................. 20

Bit......................................................................................................................................................... 20

Endereo direto de um bit na RAM interna ou de um SFR.............................................................. 20

3. Repertrio de Instrues.................................................................................................................. 20

A seguir temos uma tabela com todas as instrues do 8051 com uma breve descrio da sua

funcionalidade, o nmero de bytes e o nmero de ciclos que leva para executar. Adiante cada uma

das instrues ser minuciosamente detalhada................................................................................... 20

Conforme visto anteriormente neste documento as instrues do Microcontrolador 8051 foram

divididas em subgrupos por semelhanas na forma de endereamento e no tipo de operao que

executam. No decorrer desta sesso ser especificado detalhadamente o comportamento de cada

instruo do 8051 e a qual subgrupo ela pertence............................................................................... 25

Para uma melhor compreenso das instrues descritas a seguir, pode-se visualizar cada uma

delas como sendo um sub-fluxo do fluxo principal, tal sub-fluxo est contido dentro do estado de

execuo do fluxo principal.................................................................................................................. 25

Instrues Aritmticas____________________________________________________________ 27

Neste grupo esto as instrues ADD (adio de dois operandos), ADDC (adio de dois

operandos com carry flag), SUBB (subtrao de dois operandos com carry flag), INC (incrementa

operando), DEC (decrementa operando), MUL (multiplicao de dois operandos) DIV (diviso de

dois operandos) e DA (ajuste decimal)................................................................................................. 27

3.1.1 ADD A, operando.................................................................................................................. 27

ADD A, Rn........................................................................................................................................... 27

Opcode: 00101rrr (x28 ->x2F)............................................................................................................ 28

Operao: (A) (A) + (Rn)............................................................................................................... 28

ADD A, direto...................................................................................................................................... 27

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 5/97

Microcontrolador 8051 - CPU

Fnix Project

Opcode: 00100101 (x25)..................................................................................................................... 28

ADD A, @Ri......................................................................................................................................... 27

Opcode: 0010011i (x26 -> x27)........................................................................................................... 28

Operao: (A) (A) + ((Ri)).............................................................................................................. 28

ADD A, #dado...................................................................................................................................... 28

Opcode: 00100100 (x24)..................................................................................................................... 28

3.1.2 ADDC A, operando............................................................................................................... 28

ADDC A, Rn........................................................................................................................................ 29

Opcode: 00111rrr (x38 -> x3F)........................................................................................................... 29

Operao: (A) (A) + (Rn) + (C)...................................................................................................... 29

ADDC A, direto................................................................................................................................... 29

Opcode: 00110101 (x35)..................................................................................................................... 29

ADDC A, @Ri...................................................................................................................................... 29

Opcode: 0011011i (x36 -> x37)........................................................................................................... 29

Operao: (A) (A) + (C) + ((Ri)).................................................................................................... 29

ADDC A, #dado................................................................................................................................... 29

Opcode: 00110100 (x34)..................................................................................................................... 29

3.1.3 SUBB A, operando................................................................................................................ 29

SUBB A, Rn......................................................................................................................................... 30

Opcode: 01001rrr (x98 -> x9F)........................................................................................................... 30

Operao: (A) (A) - (C) - (Rn........................................................................................................ 30

SUBB A, direto.................................................................................................................................... 30

Opcode: 10010101 (x95)..................................................................................................................... 30

SUBB A, @Ri....................................................................................................................................... 30

Opcode: 1001011i (x96-> x97)............................................................................................................ 30

Operao: (A) (A) - (C) - ((Ri))...................................................................................................... 30

SUBB A, #dado.................................................................................................................................... 30

Opcode: 10010100 (x94)..................................................................................................................... 31

3.1.4 INC operando......................................................................................................................... 31

Opcode: 00000100 (x04)..................................................................................................................... 32

Operao: (A) (A) + 1..................................................................................................................... 32

INC Rn................................................................................................................................................. 31

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 6/97

Microcontrolador 8051 - CPU

Fnix Project

Opcode: 00001rrr (x08 -> x0F)........................................................................................................... 32

INC direto............................................................................................................................................ 31

Opcode: 00000101 (x05)..................................................................................................................... 32

Operao: (direto) (direto) + 1....................................................................................................... 32

INC @Ri............................................................................................................................................... 32

Opcode: 0000011i (x06 -> x07)........................................................................................................... 32

INC DPTR........................................................................................................................................... 32

Opcode: 10100011(xA3)...................................................................................................................... 32

3.1.5 DEC operando........................................................................................................................ 32

SUBB A, Rn......................................................................................................................................... 33

Opcode: 01001rrr (x98 -> x9F)........................................................................................................... 33

Operao: (A) (A) - (C) - (Rn........................................................................................................ 33

SUBB A, direto.................................................................................................................................... 33

Opcode: 10010101 (x95)..................................................................................................................... 33

SUBB A, @Ri....................................................................................................................................... 33

Opcode: 1001011i (x96-> x97)............................................................................................................ 33

Operao: (A) (A) - (C) - ((Ri))...................................................................................................... 33

SUBB A, #dado.................................................................................................................................... 33

Opcode: 10010100 (x94)..................................................................................................................... 33

3.1.6 MUL AB................................................................................................................................ 33

MUL AB............................................................................................................................................... 34

Opcode: 10100100 (xA4)..................................................................................................................... 34

Operao: (A)7-0 (A) x (B).............................................................................................................. 34

(B)15-8.............................................................................................................................. 34

3.1.7 DIV AB.................................................................................................................................. 34

DIV AB................................................................................................................................................ 35

Opcode: 10000100 (x84).................................................................................................................... 35

Operao: (A)15-8 (A)/(B).............................................................................................................. 35

(B)7-0................................................................................................................................. 35

3.1.8 DA A...................................................................................................................................... 35

DA A..................................................................................................................................................... 36

Opcode: 11010100 (xD4)..................................................................................................................... 37

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 7/97

Microcontrolador 8051 - CPU

Fnix Project

Operao: IF[[(A3-0) > 9] [(AC) = 1]]............................................................................................. 37

THEN(A3-0) (A3-0) + 6............................................................................................... 37

AND ................................................................................................................................. 37

IF[[(A7-4) > 9] [C = 1]]................................................................................................. 37

THEN(A7-4) (A7-4) + 6............................................................................................... 37

3.2 Instrues Lgicas____________________________________________________________ 37

Neste grupo esto as instrues de ANL (e lgico entre dois operandos), ORL (ou lgico de dois

operandos), XRL (ou exclusivo de dois operandos), CLR (limpa Acumulador), CPL (complemento

lgico do acumulador), RL (rotao para a esquerda), RLC (rotao para a esquerda com carry

flag), RR (rotao para a direita), RRC (rotao para a direita com carry flag) e SWAP (troca os

nibbles do acumulador)......................................................................................................................... 37

3.2.1 ANL A, operando.................................................................................................................. 37

ANL A, Rn........................................................................................................................................... 38

Opcode: 01011rrr (x58 -> 5F)............................................................................................................. 38

Operao: (A) (A)(Rn).................................................................................................................. 38

ANL A, Direto...................................................................................................................................... 38

Opcode: 01010101 (x55)..................................................................................................................... 38

ANL A, @Ri......................................................................................................................................... 38

Opcode: 0101011i (x56 -> 57)............................................................................................................. 38

Operao: (A) (A)(indireto).......................................................................................................... 38

ANL A, #dado...................................................................................................................................... 38

Opcode: 01010100 (x54)..................................................................................................................... 38

3.2.2 ANL direto, operando............................................................................................................ 38

ANL direto, A....................................................................................................................................... 39

Opcode: 01010010 (x52)..................................................................................................................... 39

Operao:(direto) (direto) (A)........................................................................................................ 39

ANL direto, #dado............................................................................................................................... 39

Opcode: 01010011 (x53)..................................................................................................................... 39

3.2.3 ORL A, operando................................................................................................................... 39

ORL A, Rn........................................................................................................................................... 40

Opcode: 01001rrr (x48 -> x4F)........................................................................................................... 40

Operao: (A) (A)(Rn).................................................................................................................. 40

ORL A, direto....................................................................................................................................... 40

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 8/97

Microcontrolador 8051 - CPU

Fnix Project

Opcode: 01000101 (x45)..................................................................................................................... 40

ORL A, @Ri......................................................................................................................................... 40

Opcode: 0100011i (x46 -> x47)........................................................................................................... 40

Operao: (A) (A)(indireto).......................................................................................................... 40

ORL A, #dado...................................................................................................................................... 40

Opcode: 01000100 (x44)..................................................................................................................... 40

3.2.4 ORL direto, operando............................................................................................................ 40

ORL direto, A....................................................................................................................................... 41

Opcode: 01000010 (x42)..................................................................................................................... 41

Operao:(direto)(direto) (A)......................................................................................................... 41

ORL direto, #dado............................................................................................................................... 41

Opcode: 01000011 (x43)..................................................................................................................... 41

3.2.5 XRL A, operando................................................................................................................... 41

XRL A, Rn............................................................................................................................................ 42

Opcode: 01101rrr (x68 -> 6F)............................................................................................................. 42

Operao: (A) (A) (Rn)................................................................................................................ 42

XRL A, Direto...................................................................................................................................... 42

Opcode: 01100101 (x65)..................................................................................................................... 42

XRL A, @Ri......................................................................................................................................... 42

Opcode: 0110011i (x66 -> x67)........................................................................................................... 42

Operao: (A) (A) (indireto)....................................................................................................... 42

XRL A, #dado...................................................................................................................................... 42

Opcode: 01100100 (x64)..................................................................................................................... 43

3.2.6 XRL direto, operando............................................................................................................ 43

Obs.: Quando esta instruo usada para modificar uma porta de sada, o valor usado como

origem deve ser lido do latch e no dos pinos de entrada.................................................................... 43

Modo de Endereamento: Acumulador e dado imediato................................................................... 43

XRL direto, A....................................................................................................................................... 43

Opcode: 01100010 (x62)..................................................................................................................... 44

Operao: (direto)(direto) (A)....................................................................................................... 44

XRL direto, #dado................................................................................................................................ 43

Opcode: 01100011 (x63)..................................................................................................................... 44

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 9/97

Microcontrolador 8051 - CPU

Fnix Project

3.2.7 CLR A.................................................................................................................................... 44

Fluxo:................................................................................................................................................... 44

1. Zera os bits do Acumulador;............................................................................................................ 44

2. No afeta nenhum flag..................................................................................................................... 44

Diagrama de Execuo da Instruo CRL A..................................................................................... 44

.............................................................................................................................................................. 44

Variaes:............................................................................................................................................ 44

CRL A.................................................................................................................................................. 44

Opcode: 11100100 (xE4)..................................................................................................................... 44

3.2.8 CPL A.................................................................................................................................... 44

Fluxo:................................................................................................................................................... 45

1. Complemento lgico de cada bit do Acumulador;.......................................................................... 45

2. No afeta nenhum flag..................................................................................................................... 45

Diagrama de Execuo da Instruo CPL A..................................................................................... 45

.............................................................................................................................................................. 45

CPL A................................................................................................................................................... 45

Opcode: 11110100 (xF4)..................................................................................................................... 45

3.2.9 RL A...................................................................................................................................... 45

Fluxo:................................................................................................................................................... 45

1. Rotaciona os bits do Acumulador e coloca o resultado no Acumulador;...................................... 45

2. No afeta nenhum flag..................................................................................................................... 46

Diagrama de Execuo da Instruo RL A....................................................................................... 46

.............................................................................................................................................................. 46

RL A..................................................................................................................................................... 46

Opcode: 00100011 (x23)..................................................................................................................... 46

Operao: (An+1) (An),.................................................................................................................. 46

n = 0 6,........................................................................................................................... 46

3.2.10 RLC A.................................................................................................................................. 46

Fluxo:................................................................................................................................................... 46

1. Rotaciona os bits do Acumulador e coloca o resultado no Acumulador;...................................... 46

2. Afeta carry flag................................................................................................................................. 46

Diagrama de Execuo da Instruo RLC A..................................................................................... 46

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 10/97

Microcontrolador 8051 - CPU

Fnix Project

.............................................................................................................................................................. 47

RLC A.................................................................................................................................................. 47

Opcode: 00110011 (x33)..................................................................................................................... 47

Operao: (An+1) (An),.................................................................................................................. 47

n = 0 6,........................................................................................................................... 47

(A0) C,.......................................................................................................................... 47

3.2.11 RR A.................................................................................................................................... 47

Fluxo:................................................................................................................................................... 47

1. Rotaciona os bits do Acumulador e coloca o resultado no Acumulador;...................................... 47

2. No afeta nenhum flag..................................................................................................................... 47

Diagrama de Execuo da Instruo RR A....................................................................................... 47

.............................................................................................................................................................. 48

RL A..................................................................................................................................................... 48

Opcode: 00000011 (x3)....................................................................................................................... 48

Operao: (An) (An+1),.................................................................................................................. 48

n = 0 6,.......................................................................................................................... 48

3.2.12 RRC A.................................................................................................................................. 48

Funo: Rotao a Direita com o Carry Flag................................................................................... 48

Fluxo:................................................................................................................................................... 48

1. Rotaciona os bits do Acumulador e coloca o resultado no Acumulador;...................................... 48

2. Afeta carry flag................................................................................................................................. 48

Diagrama de Execuo da Instruo RRC A.................................................................................... 49

.............................................................................................................................................................. 49

RLC A.................................................................................................................................................. 49

Opcode: 00010011 (x13)..................................................................................................................... 49

Operao: (An) (An+1),.................................................................................................................. 49

n = 0 6,........................................................................................................................... 49

(A7) C,.......................................................................................................................... 49

3.2.13 SWAP A.............................................................................................................................. 49

SWAP A............................................................................................................................................... 50

Opcode: 11000100 (xC4)..................................................................................................................... 50

3.3 Instrues de transferncia de dados_____________________________________________ 50

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 11/97

Microcontrolador 8051 - CPU

Fnix Project

As instrues de transferncia de dados so aquelas relacionadas a movimentao e copia de

dados entre a memria, registrador, acumulador. Essas instrues so descritas abaixo:...............50

3.3.1 MOV A, operando................................................................................................................. 50

MOV A, Rn......................................................................................................................................... 51

Opcode: 11101rrr (xE8 -> xEF)......................................................................................................... 51

MOV A, @Ri........................................................................................................................................ 51

Opcode: 1110011i (xE6 -> xE7)......................................................................................................... 51

MOV A, #dado..................................................................................................................................... 51

Opcode:01110100 (x74)...................................................................................................................... 51

MOV A, direto...................................................................................................................................... 51

Opcode: 11100101 (xE5)..................................................................................................................... 52

3.3.2 MOV Rn, operando................................................................................................................ 52

MOV Rn, A.......................................................................................................................................... 52

Opcode: 11111rrr (xF8 -> xFF)......................................................................................................... 52

MOV Rn, direto................................................................................................................................... 52

Opcode: 10101rrr (A8 -> AF)............................................................................................................. 52

MOV Rn, #dado................................................................................................................................... 52

Opcode: 1110011i (x78 -> x7F).......................................................................................................... 52

3.3.3 MOV direto, operando........................................................................................................... 53

MOV direto, A...................................................................................................................................... 53

Opcode: 11110101 (xF5)..................................................................................................................... 54

MOV direto, Rn................................................................................................................................... 53

Opcode:10001rrr (x88 -> x8F)............................................................................................................ 54

MOV direto, direto............................................................................................................................... 53

Opcode: 10000101 (x85)..................................................................................................................... 54

MOV direto, @Ri................................................................................................................................. 54

Opcode: 1000011i (x86 -> x87)........................................................................................................... 54

MOV direto, #dado.............................................................................................................................. 54

Opcode: 01110101 (x75)..................................................................................................................... 54

3.3.4 MOV @Ri, operando............................................................................................................. 54

MOV @Ri, A........................................................................................................................................ 55

Opcode:1111011i (xF6 -> xF7)........................................................................................................... 55

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 12/97

Microcontrolador 8051 - CPU

Fnix Project

MOV @Ri, direto................................................................................................................................. 55

Opcode: 1010011i (xA6 -> xA7)......................................................................................................... 55

MOV @Ri, #dado................................................................................................................................. 55

Opcode: 0111011i (x76 -> x77)........................................................................................................... 55

3.3.5 MOV DPTR, #dado16........................................................................................................... 55

MOV DPTR, #dado16......................................................................................................................... 56

Opcode: 10010000 (x90)..................................................................................................................... 56

Operao: (DPTR) (#dado(15-0)).................................................................................................. 56

3.3.6 MOVC A, @A+operando...................................................................................................... 56

MOVC A, @A + DPTR........................................................................................................................ 57

Opcode: 10010011 (x93)..................................................................................................................... 57

Opcode: 10000011 (x83)..................................................................................................................... 57

3.3.7 MOVX A, @operando........................................................................................................... 57

MOVX A, @Ri..................................................................................................................................... 58

Opcode: 1110001i (xE2 -> xE3)......................................................................................................... 58

MOVX A, @DPTR............................................................................................................................... 58

Opcode: 11100000 (xE0)..................................................................................................................... 58

3.3.8 MOVX @operando, A........................................................................................................... 58

Opcode: 1111001i (xF2 -> xF3).......................................................................................................... 59

MOVX @DPTR, A............................................................................................................................... 59

Opcode: 11110000 (xF0)..................................................................................................................... 59

3.3.9 PUSH operando..................................................................................................................... 59

PUSH direto......................................................................................................................................... 60

Opcode: 11000000 (xC0)..................................................................................................................... 60

3.3.10 POP operando...................................................................................................................... 60

POP direto........................................................................................................................................... 61

Opcode:10001rrr (xD0) ...................................................................................................................... 61

3.3.11 XCH A, operando................................................................................................................ 61

XCH A, Rn........................................................................................................................................... 62

Opcode: 11001rrr (xC8 -> xCF)......................................................................................................... 62

XCH A, direto...................................................................................................................................... 62

Opcode: 11000101 (xC5)..................................................................................................................... 62

XCH A, @Ri......................................................................................................................................... 62

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 13/97

Microcontrolador 8051 - CPU

Fnix Project

Opcode: 1100011i (xC6 -> xC7)......................................................................................................... 62

3.3.12 XCHD A, operando............................................................................................................. 62

XCHD A, @Ri...................................................................................................................................... 63

Opcode: 1101011i (xD6 -> xD7)......................................................................................................... 63

3.4 Instrues de manipulao de bit._______________________________________________ 63

Neste grupo esto as instrues CLR (Reseta bit) e CPL (Complementa bit), SETB (Seta bit),

ANL(AND lgico de bit), ORL(OR lgico de bit), MOV(Move bit Estas foram agrupadas, pois todas

manipulam bit. A seguir sero detalhados seus comportamentos e variaes...................................63

3.4.1 CLR operando........................................................................................................................ 63

3.4.2 SETB operando...................................................................................................................... 64

3.4.3 CPL operando........................................................................................................................ 65

3.4.4 ANL C, operando................................................................................................................... 67

3.4.5 ORL C, operando................................................................................................................... 68

3.4.6 MOV C, bit ........................................................................................................................... 69

3.4.7 MOV bit, C ........................................................................................................................... 70

3.5 Instrues de desvio___________________________________________________________ 71

Neste grupo esto as instrues JC, JNC, JB, JNB, JBC, ACALL, LCALL, RET, RETI, JMP,

LJMP, SJMP, JMP, JZ, JNZ, CJNE, DJNZ, NOP, que so instrues que executam desvio. A

seguir sero detalhados seus comportamentos e variaes.................................................................

3.5.1 JC rel......................................................................................................................................

3.5.2 JNC rel...................................................................................................................................

3.5.3 JB bit, rel................................................................................................................................

3.5.4 JNB bit, rel.............................................................................................................................

3.5.5 JBC bit,rel..............................................................................................................................

3.5.6 ACALL addr11......................................................................................................................

3.5.7 LCALL addr16......................................................................................................................

3.5.8 RET........................................................................................................................................

3.5.9 RETI.......................................................................................................................................

3.5.10 AJMP addr11.......................................................................................................................

3.5.11 LJMP addr16........................................................................................................................

3.5.12 SJMP rel...............................................................................................................................

3.5.13 JMP @A+DPTR..................................................................................................................

3.5.14 JZ rel....................................................................................................................................

3.5.15 JNZ rel.................................................................................................................................

71

71

72

73

75

76

77

78

79

80

81

83

83

84

85

86

Diagrama de Execuo da Instruo JNZ rel................................................................................... 87

.............................................................................................................................................................. 87

Variaes:............................................................................................................................................

3.5.16 CJNE A, operando, rel.........................................................................................................

3.5.17 CJNE Rn, dado, rel..............................................................................................................

3.5.18 CJNE @Ri, dado, rel...........................................................................................................

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 14/97

87

87

89

90

Microcontrolador 8051 - CPU

Fnix Project

3.5.19 DNJZ Rn, rel........................................................................................................................ 92

Funo: Decrementa e salta se o valor no for igual a zero............................................................. 92

3.5.20 DNJZ direto, rel................................................................................................................... 93

Funo: Decrementa e salta se o valor no for igual a zero............................................................. 93

3.5.21 NOP..................................................................................................................................... 95

4. Referncias....................................................................................................................................... 96

[1] Documento de Requisitos; BrazilIP_Requisitos_8051.doc........................................................... 96

[2] Modelo de Casos de Uso; <Excutar_Instruo.rtmdl>;................................................................ 96

[3] 80C51 family programmers guide and instruction set, Philips Semicondutores........................ 96

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 15/97

Fnix Project

Microcontrolador 8051 - CPU

1. Caso de Uso Executar Instruo

1.1

Convenes, termos e abreviaes

Esta subseo explica o conceito de alguns termos importantes que sero mencionados no decorrer

deste documento. Estes termos so descritos na tabela a seguir, estando apresentados por ordem

alfabtica.

Termo

1.2

Descrio

OV

Overflow

SP

Stack Pointer

ACC, A

Acumulador

IR

Registrador de Instruo

DPTR LOW

Data Pointer Registrar Low

DPTR HIGH

Data Pointer Registrar High

PSW

Program Status Work

Carry flag

AC

Carry flag auxiliar

Registrador B

SBUF

Registrador usado no recebimento e na transferncia de dados da

USART (Para maiores detalhes vide a especificao da USART)

Write_to_sbuf

Sinal usado para escrever no SBUF (Para maiores detalhes vide a

especificao da USART)

P0, P1, P2 e P3

Portas de entradas e sada do 8051 (Para maiores detalhes vide

especificao das portas de entrada e sada)

Descrio

Temporizao: O ciclo de instruo do 8051 se divide em 6 estados, cada estado em duas fases e cada

uma das fases tem a durao de um ciclo de clock, totalizando assim 12 ciclos de clock por ciclo de

instruo. Para se referir a uma fase em especfico se utiliza a notao SxPy, onde x representa o

nmero do estado e y o nmero da fase.

Pr-condies: no se aplica.

Ps-condies: no se aplica.

Fluxo de eventos principal

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 16/97

Fnix Project

Microcontrolador 8051 - CPU

1. Este caso de uso inicia quando se comea a execuo de um programa;

2. No estado de busca da instruo deve ser carregado o opcode da mesma;

3. No prximo passo a instruo lida decodificada;

4. A instruo decodificada no passo anterior executada e o reset checado ([SB001] Verifica

o reset);

5. Execuo do reset, caso a checagem seja positiva ([SB002] Executa o reset);

6. Checa o manipulador de interrupo para saber se h alguma interrupo pendente a ser

executada, caso haja, a CPU a tratar como uma instruo qualquer apenas com a diferena de

que ser habilitado um bit para que seja passada a informao ao manipulador de interrupo

que j foi tratada a interrupo especfica.

Subfluxo

[SB001] Verifica o Reset

1. A CPU verifica o reset na fase dois (P2) do estado S5, porm o reset s ser ativado se estiver

por dois ciclos de instruo ativado(24 ciclos de clock). Caso essa condio seja atendida a

CPU responde gerando um reset interno. Durante a verificao do Reset, ALE e PSEN (Vide

especificao Portas de Entrada/Sada) mantm suas atividades atuais por 19 perodos de

oscilao, para manter as atividades de leitura da memria externa, depois que o sinal de

Reset externo foi aplicado ao pino RST (pino do reset) e verificado na fase 2 do estado 5, ou

seja, quando RST ativado, de 19 a 31 perodos aps, ALE e PSEN sero ativados tambm.

[SB002] Executa o Reset

1. O sinal de Reset interno escreve 0 (zero) em todos os SFRs exceto nos latches das portas, no

Stack Pointer e no SBUF. Os latches das portas so inicializados com FFH, o Stack Pointer

com 07H, e o SBUF com valor indeterminado. A RAM interna no ter valores modificados

pelo Reset. E aps RST ser desativado, decorrer entre 1 a 2 ciclos de mquina at que ALE e

PSEN voltem a oscilar.

1.3

Diagrama Comportamental

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 17/97

Fnix Project

Microcontrolador 8051 - CPU

Diagrama geral de execuo de instruo

t2

Busca da

Instruo

D ecodificao

da Instruo

Execuo da

Instruo

S egunda

checagem

consecutiva do

R esetpositiva

E xecuo do

R eset

E4

Initial

E1

t1

E2

t1

E 3_1

T rue

t1

t2

Checagem do

R eset(S5P 2)

t1

E 3_2

False

C P1

P rim eira checagem

positiva do R eseto

u checagem

negativa

E5

C hecagem do

M anipuladorde

Interrupo

t1

2.

Di

agrama de Blocos

Nesta sesso ser mostrado um diagrama de blocos para a CPU do microcontrolador 8051 e como foi

feita a especificao do seu repertrio de instrues j se fazendo uma breve explanao de cada uma.

A especificao do repertrio de instrues foi feita agrupando as instrues em cinco grupos:

operaes aritmticas, operaes lgicas, transferncia de dados, manipulao de variveis booleanas

e desvio de programa. O agrupamento foi feito com base na semelhana da operao que cada

instruo executa e pela forma de endereamento comum.

Ainda dentro de cada grupo especificamos detalhadamente cada instruo e sugerimos um diagrama

de estados para uma possvel implementao.

O diagrama de blocos abaixo mostra a arquitetura do microcontrolador 8051, temos um barramento de

dados de 8 bits, um barramento de endereo de 16 bits, os seguintes registradores: SP, ACC, IR,

DPTR LOW, DPTR HIGH e o PSW como registradores de 8 bits. A memria RAM com 256 posies

endereadas a byte e, contida nesta, a regio endereada a bit que vai do endereo 20H a 2FH. Temos

ainda as portas de entrada e sada P0, P1, P2 e P3.

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 18/97

Fnix Project

Microcontrolador 8051 - CPU

As instrues que endeream a RAM para a escrita no registrador SBUF, tero o endereo

para escrita do SBUF identificado, e o sinal write_to_sbuf ficar ativado durante um perodo de

oscilao do Clock1, quando a escrita for efetivada.

Para um entendimento completo do restante da especificao o sumrio de termos apresentado

abaixo:

TERMO

DESCRIO

SFR

Registrador de Funo Especial

Ciclo

Um ciclo corresponde a 12 pulsos de clock na freqncia de 33 MHz

Rn

Corresponde ao registrador R7-R0 do banco de registradores ativo

Direto

Endereo de um dado de 8 bits. Esse dado pode est localizado na RAM

interna (0-127) ou um SFR [portas de E/S, PSW, TCOM, etc. (128-255)]

@Ri

Endereo de um dado de 8 bits localizado na RAM interna endereado

indiretamente pelos registradores R0 e R1.

#dado

Uma constante de 8 bits contida na instruo

#dado 16

Uma constante de 16 bits contida na instruo

Addr 16

Endereo de destino com 16 bits. Usado nas instrues LCALL e LJMP.

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 19/97

Fnix Project

Microcontrolador 8051 - CPU

Addr 11

Endereo de destino com 11 bits. Usado nas instrues ACALL e AJMP.

Rel

Offset de 8 bits com sinal. Usado pela instruo SJMP e todas as instrues

de desvio condicional. Seu valor varia de 128 a +127.

Bit

Endereo direto de um bit na RAM interna ou de um SFR.

3. Repertrio de Instrues

Modos de Endereamento

Descrio

Acumulador (A)

O endereo

acumulador.

Registrador (Rn)

O endereo especificado o do registrador

escolhido.

Endereamento direto (direto)

O endereo dado o endereo que ser acessado

na memria.

Endereamento indireto (@Ri)

O endereo a ser acessado, ser o endereo

contido no registrador selecionado, podendo ser

este registrador R0 ou R1 do banco de

registradores ativo.

especificado

do

prprio

Endereamento indireto por meio do DPTR O endereo a ser acessado ser o endereo contido

(@DPTR)

no DPTR.

Dado imediato (#dado)

Nesse caso o dado fornecido diretamente na

instruo.

A seguir temos uma tabela com todas as instrues do 8051 com uma breve descrio da sua

funcionalidade, o nmero de bytes e o nmero de ciclos que leva para executar. Adiante cada uma das

instrues ser minuciosamente detalhada.

MINEMNICO

DESCRIO

NMERO DE BYTES

CICLOS

OPERAES ARITMTICAS

ADD A,Rn

Soma registrador com Acumulador

ADD A,direto

Soma endereo direto com Acumulador

ADD A,@Ri

Soma

endereo

Acumulador

com 1

ADD A,#dado

Soma dado imediato com Acumulador

Executar Instruo

indireto

fenix_especificao_8051_CPU.d

oc

1

Pg 20/97

Fnix Project

Microcontrolador 8051 - CPU

ADDC A,Rn

Soma registrador com Acumulador e 1

Carry

ADDC A,direto

Soma endereo direto com Acumulador 2

e Carry

ADDC A,@Ri

Soma

endereo

Acumulador e Carry

com 1

ADDC A,#dado

Soma dado imediato com Acumulador e 2

Carry

SUBB A,Rn

Subtrai Acumulador de registrador com 1

Borrow

SUBB A,direto

Subtrai Acumulador de endereo direto 2

com Borrow

SUBB A,@Ri

Subtrai Acumulador

indireto com Borrow

endereo 1

SUBB A,#dado

Subtrai Acumulador de dado imediato 2

com Borrow

INC A

Incrementa Acumulador

INC Rn

Incrementa registrador

INC direto

Incrementa endereo direto

INC @Ri

Incrementa endereo indireto

DEC A

Decrementa Acumulador

DEC Rn

Decrementa registrador

DEC direto

Decrementa endereo direto

DEC @Ri

Decrementa endereo indireto

INC DPTR

Incrementa

Register(DPTR)

Pointer 1

MUL AB

Multiplica A por B

DIV AB

Divide A por B

DA A

Ajuste decimal do Acumulador

indireto

de

Dado

OPERAES LGICAS

ANL A,Rn

E Lgico

registrador

com 1

ANL A,direto

E Lgico do Acumulador com endereo 2

direto

ANL A,@Ri

E Lgico de endereo indireto com 1

Executar Instruo

do

Acumulador

fenix_especificao_8051_CPU.d

oc

Pg 21/97

Fnix Project

Microcontrolador 8051 - CPU

Acumulador

ANL A,#dado

E Lgico de dado imediato

Acumulador

com 2

ANL direto,A

E Lgico do Acumulador com endereo 2

direto

ANL direto,#dado

E Lgico de endereo direto com dado 3

imediato

ORL A,Rn

OU Lgico

registrador

do

Acumulador

com 1

ORL A,direto

OU Lgico do

endereo direto

Acumulador

com 2

ORL A,@Ri

OU Lgico de endereo indireto com 1

Acumulador

ORL A,#dado

OU Lgico de dado imediato com 2

Acumulador

ORL direto,A

OU Lgico do

endereo direto

com 2

ORL direto,#dado

OU Lgico de endereo direto com dado 3

imediato

XRL A,Rn

OU-Exclusivo

registrador

do

Acumulador

com 1

XRL A,direto

OU-Exclusivo do

endereo direto

Acumulador

com 2

XRL A,@Ri

OU-Exclusivo de endereo indireto com 1

Acumulador

XRL A,#dado

OU-Exclusivo de dado imediato com 2

Acumulador

XRL direto,A

OU-Exclusivo do

endereo direto

com 2

XRL direto,#dado

OU-Exclusivo de endereo direto com 3

dado imediato

CLR A

Limpa Acumulador

CPL A

Complemento lgico do Acumulador

RL A

Rotao para a esquerda

RLC A

Rotao para a esquerda com Carry

RR A

Rotao para a direita

Executar Instruo

Acumulador

Acumulador

fenix_especificao_8051_CPU.d

oc

Pg 22/97

Fnix Project

Microcontrolador 8051 - CPU

RRC A

Rotao para a direita com Carry

SWAP A

Trocar os nibbles do Acumulador

TRANSFENCIA DE DADOS

MOV A,Rn

Move registrador para Acumulador

MOV A,direto

Move endereo direto para Acumulador

MOV A,@Ri

Move

endereo

Acumulador

para 1

MOV A,#dado

Move dado imediato para Acumulador

MOV Rn,A

Move Acumulador para registrador

MOV Rn,direto

Move endereo direto para registrador

MOV Rn,#dado

Move dado imediato para registrador

MOV direto,A

Move Acumulador para endereo direto

MOV direto,Rn

Move registrador para endereo direto

MOV direto,direto

Move endereo direto para endereo 3

direto

MOV direto,@Ri

Move endereo indireto para endereo 2

direto

MOV direto,#dado

Move dado imediato para endereo 3

direto

MOV @Ri,A

Move Acumulador

indireto

endereo 1

MOV @Ri,direto

Move endereo direto para endereo 2

indireto

MOV @Ri,#dado

Move dado imediato para endereo 2

indireto

MOV DPTR,#dado16

Carrega o DPTR com uma constante de 3

16 bits

MOVC A,@A+DPTR

Move dado da memria de cdigo para 1

Acumulador usando o DPTR

MOVC A,@A+PC

Move dado da memria de cdigo para 1

Acumulador usando o PC

MOVX A,@Ri

Move dado da RAM externa para o 1

Acumulador

MOVX A,@DPTR

Move dado da RAM externa para 1

Acumulador usando DPTR

Executar Instruo

indireto

para

fenix_especificao_8051_CPU.d

oc

Pg 23/97

Fnix Project

Microcontrolador 8051 - CPU

MOVX @Ri, A

Move o Acumulador para RAM externa

MOVX @DPTR, A

Move o Acumulador para RAM externa 1

usando DPTR

PUSH direto

Armazena dado no topo da pilha

POP direto

Recupera dado do topo da pilha

XCH A,Rn

Troca Acumulador com registrador

XCH A,direto

Troca Acumulador com endereo direto

XCH A,@Ri

Troca Acumulador

indireto

endereo 1

XCHD A,@Ri

Troca nibbles inferiores do Acumulador 1

com endereo indireto

com

MANIPULAO DE VARIVEIS BOOLEANAS

CLR C

Limpa Carry

CLR bit

Limpa bit de endereo direto

SETB C

Seta o Carry

SETB bit

Seta bit endereo direto

CPL C

Complemento Lgico do Carry

CPL bit

Complemento Lgico de bit endereo 2

direto

ANL C,bit

E Lgico de bit endereo direto

ANL C,/bit

E Lgico do valor do endereo direto 2

complementado

ORL C,bit

OU Lgico de bit endereo direto

ORL C,/bit

OU Lgico do valor do endereo direto 2

complementado

MOV C,bit

Move bit endereo direto para Carry

MOV bit,C

Move Carry para endereo direto

INSTRUES DE DESVIO

JC rel

Desvia se o Carry est setado

JNC rel

Desvia se o Carry no est setado

JB bit, rel

Desvia se bit endereo direto est setado 3

JNB bit, rel

Desvia se bit endereo direto no est 3

setado

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 24/97

Fnix Project

Microcontrolador 8051 - CPU

JBC bit, rel

Desvia se bit endereo direto est setado 3

e limpa o bit

ACALL addr11

Chamada de sub-rotina com desvio 2

absoluto

LCALL addr16

Chamada de sub-rotina com 16 bits

RET

Retorno de sub-rotina

RETI

Retorno de interrupo

AJMP addr11

Desvio absoluto

LJMP addr16

Desvio com 16 bits

SJMP rel

Desvio curto considerando sinal

JMP @A+DPTR

Desvio com endereo indireto

JZ rel

Desvia se Acumulador zero

JNZ rel

Desvia se Acumulador no zero

CJNE A,direto,rel

Compara

endereo

direto

com 3

Acumulador e desvia se no forem

iguais

CJNE A,#dado,rel

Compara

dado

imediato

com 3

Acumulador e desvia se no forem

iguais

CJNE Rn,#dado,rel

Compara dado imediato com Registrador 3

e desvia se no forem iguais

CJNE @Ri,#dado,rel

Compara dado imediato com endereo 3

indireto e desvia se no forem iguais

DJNZ Rn,rel

Decrementa registrador e desvia se no 2

for zero

DJNZ direto,rel

Decrementa endereo direto e desvia se 3

no for zero

NOP

Nenhuma operao executada

Conforme visto anteriormente neste documento as instrues do Microcontrolador 8051 foram

divididas em subgrupos por semelhanas na forma de endereamento e no tipo de operao que

executam. No decorrer desta sesso ser especificado detalhadamente o comportamento de cada

instruo do 8051 e a qual subgrupo ela pertence.

Para uma melhor compreenso das instrues descritas a seguir, pode-se visualizar cada uma delas

como sendo um sub-fluxo do fluxo principal, tal sub-fluxo est contido dentro do estado de execuo

do fluxo principal.

Executar Instruo

fenix_especificao_8051_CPU.d

oc

Pg 25/97

Microcontrolador 8051 - CPU

Executar Instruo

Fnix Project

fenix_especificao_8051_CPU.d

oc

Pg 26/97

Fnix Project

Microcontrolador 8051 - CPU

Instrues Aritmticas

Neste grupo esto as instrues ADD (adio de dois operandos), ADDC (adio de dois operandos

com carry flag), SUBB (subtrao de dois operandos com carry flag), INC (incrementa operando),

DEC (decrementa operando), MUL (multiplicao de dois operandos) DIV (diviso de dois

operandos) e DA (ajuste decimal).

3.1.1

ADD A, operando

Funo: Operao de adio.

Descrio: Esta instruo executa a operao de adio entre o byte indicado pela instruo e o

contedo do Acumulador, armazenando o resultado no Acumulador. O carry flag e o carry flag

auxiliar, respectivamente, so alterados se existir o carry out do nibble mais significativo e do nibble

menos significativo. O OV indica a ocorrncia de overflow no byte.

Modos de Endereamento: Registrador, endereo direto, endereo indireto e dado imediato.

Fluxo:

1. Busca operando;

2. Executa a soma e coloca o resultado no Acumulador;

3. Afeta carry flag, carry flag auxiliar e OV.

Diagrama de Execuo da Instruo ADD A, operando.

Variaes:

ADD A, Rn

Bytes: 1

Executar Instruo

ADD A, direto

Bytes: 2

ADD A, @Ri

Bytes: 1

fenix_especificao_8051_CPU.d

oc

Pg 27/97

Fnix Project

Microcontrolador 8051 - CPU

Ciclos: 1

Opcode:

->x2F)

Ciclos: 1

00101rrr

(x28

Ciclos: 1

Opcode: 00100101 (x25)

Operao: (A) (A) + (direto)

Operao: (A) (A) + (Rn)

Opcode: 0010011i (x26 ->

x27)

Operao: (A) (A) + ((Ri))

ADD A, #dado