Escolar Documentos

Profissional Documentos

Cultura Documentos

Gabarito Exame Ee532 1s2013

Enviado por

Yuri OliveDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Gabarito Exame Ee532 1s2013

Enviado por

Yuri OliveDireitos autorais:

Formatos disponíveis

BR

Wiley/Razavi/Fundamentals of Microelectronics

[Razavi.cls v. 2006]

June 30, 2007 at 13:42

119 (1)

120

Chap. 3

D1

Sec. 3.6

D1

Vout

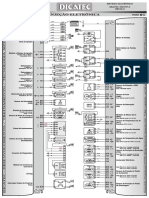

Exame de Eletronica Aplicada

EE532

Chapter Summary

I in

R1

R 1 = 1 k!

Prof. Candido

V in

VB

10 deD julho

(a) de 2013

2

RD2

1

Nome:

RA:

(a)

R1

I in

1.1

Figure 3.77 1.2

(c)

119

R 1 = 1 k!

D2

Vout

D1

(b)

R2

VB

R1

R1

Vout o circuito a seguir e o modelo da tens

Vout

1. Considere

ao

1 k ! constante para os diodos.

1 k!

(b)

I in

D

D

R

2k!

Marque V (verdadeiro) ou F (falso) no quadro de

V inacerto vale 0,4 ponto. Erros

Vout (c)

respostas abaixo. Cada

n

ao anulam acertos.

D 1 3.79

R2

Figure

D2

N

ao se apresse em responder as quest

oes; analise-as

VB

com atenc

ao e cuidado.

V

Vout

I in

R1

V in

Vout

D1

D1

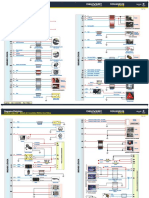

Diode Models and Circuits

V in

D1 R1

(d)

D2

Vout

R2

VB

V in

D1

(d)

Vout

0.5 Vcom D cortado.

(1.1) D2 nuncaC 1conduz

1

1.3

(1.2) Existe umaD 1faixa de Vin para a qual apeD1

Figure

V in 3.80

V in

Vout

Voutao Vout = (Vin

nas D1 conduz,

quando ent

1.4

V

)[R

/(R

+

R

)].

D,on

2

1

2

2.1

R 1 = 1 k!

R 1 = 1 k!

D1

2.2

(1.3) Quando

V

>

2V

+ VB , D1 e D2 conin

V in

DD,on

2 V

2.3

duzem, e Vout = VB + VD,on .out

2.4

0.5 V

C1

(1.4) Quando Vin

(a)

(b)< 2VD,on +VB , D1 e D2 cortam,

3.1

e Vout = 0.

3.2

D1 R1

Figure 3.81

R1

o circuito a seguir. Vout

V in

V in

Vout 2. Considere

3.3

1 k!

1 k!

3.4

D2

D2

R2 2 k !

4.1

D3

D2

4.2

Vout

(c)

(d)

Vin

4.3

RL

Figure 3.78 4.4

D1

D

4.5

4

5.1

Figure

37. A 3-V adaptor

using

a 3.82

half-wave rectifier must supply a current of 0.5 A with a maximum

5.2

ripple of

300

mV.

For

a frequency of 60 Hz, compute

minimum

required

smoothing

5.3

(2.1) the

Durante

o ciclo

negativo

da entrada, D1 e

capacitor.

43. Suppose in Fig. 3.43, the diodes

a currenteofVout

5 mA

and the load, a current of 20 mA. If

5.4

D3carry

conduzem,

= 0.

38. Assume6.1

the input andthe

output

groundsincreases

in a full-wave

rectifier

areisshorted

together.

the

load current

to 21(2.2)

mA, what

theo change

in theDraw

total

across

Durante

ciclo negativo

davoltage

entrada,

D1 the

e three

output waveform

with

and

without

the

load

capacitor

and

explain

why

the

circuit

does

not

diodes?

Assume

is

much

greater

than

.

6.2

D2 conduzem, e Vout = Vin .

operate6.3

as a rectifier.

44. In this problem, we estimate the ripple seen by the load in Fig. 3.43 so as to appreciate

(2.3) Durante o ciclo positivo da entrada, D2 e

39. Plot the6.4

voltage across

diode in

Fig. 3.38(b)

a function

of time if neglect the load.. Also,

theeach

regulation

provided

by theasdiodes.

For simplicity,

Hz,

D cortam, e Vout = 0.

Assume a constant-voltage diodeF,model and

, and3 the.peak voltage

produced by the transformer is equal to 5

(2.4) Trata-se

de um retificador

de onda

Tabela

Quadro de arespostas.

V.full-wave rectifier, a student mistakenly

40.

While1:constructing

has swapped

the terminals

of completa,

assim chamado

por converter

ambos os mV,

ciclos

da

(a)3.82.

Assuming

carries

a relatively

constant current

and

estimate

the

as depicted in Fig.

Explain what

happens.

ripple amplitude across . entrada (positivo e negativo) numa mesma polari41. A full-wave rectifier is driven by a sinusoidal input

, where

V

dadeofde

da. determine the ripple amplitude across the

(b) Using the small-signal model

thesa

diodes,

and

. Assuming

mV, determine the ripple amplitude with a

load.

1000- F smoothing capacitor and a load resistance

of 30 . o circuito a seguir, no qual os transisto3. Considere

res t

em mesmo

e mesmo

IS .Plot the

42. Suppose the negative terminals of

and

in Fig.

3.38(b)

are shorted

together.

input-output characteristic assuming an ideal diode

model

and

explaining

why

thecomo

circuitfonte de cor(3.1) O transistor Q1 opera

does not operate as a full-wave rectifier.

rente.

(3.2) Desprezado o efeito Early, a impedancia (de

pequenos sinais) vista olhando-se para dentro da

base de Q2 (veja indicacao na figura) e aproximadamente 2r .

mentals of Microelectronics

[Razavi.cls v. 2006]

31. The op amp in Fig. 8.54 suffers from a finite gain. Calculate

in terms of

and .

369 (1)

32. Due to a manufacturing error, a parasitic resistance

has appeared in the adder of Fi

8.55. Calculate

in terms of

and

for

and

. (Note that

ca

June 30, 2007 at 13:42

RF

7.6

re 7.82

re 7.83

V1

V2

Chapter Summary

R2

X

Vout

369 A 0

R1

RP

VDD = 1.8 V

RG

Figure 8.55

RD

C2

C1

o amp-op

ter of

ganho

finito,

Valso

impedance

the op

amp.)a entrada inversora nao

out represent the input

e um terra virtual, ja que as correntes de entrada

33. The voltage adder of Fig. 8.54 employs an op amp having a finite output impedance,

do amp-op nao mais sao nulas.

the opeamp model depicted in Fig. 8.44, compute

in terms of

and .

(3.3) Inicialmente, para o c

alculo dasUsing

correntes

(5.2)

Como

a

entrada

n

a

o-inversora

est

a

aterrada,

tens

oes de polarizac

ao, podemos 34.

assumir

que

Q

Consider the1voltage adder illustrated in Fig. 8.56,

where

is a parasitic resistance and th

R Fterra

a entrada inversora e um

virtual, indepenest

a no modo ativo direto. No entanto, apos os

R

dentemente

de2 o ganho do amp-op ser finito ou

V1

c

alculos, pode ocorrer de verificarmos

que

a

V Q1 est

VDD = 1.8

X

infinito.

de fato saturado. Nesse caso, devemos entao refaV2

Vout

A0

R1

R D de Q em saR 1 de o amp-op ter ganho finito

zer os c

alculos adotando

o modelo

(5.3) No caso

1

Vout

C1

turac

ao.

A0 , a sada do circuito

e Vout =

(v1 /R2 +

RP

M1

v

/R

)[R

||A

(R

||R

||R

||R

)].

2

1

F

0

1

2

F

P

(3.4) A corrente de polarizac

ao IC de amV in

M1

R2

V in

bos os

transistores e dada R pela

solucao da

(5.4) Considerando o ganho do amp-op infinito,

S Figure 8.56

equac

ao IC / = 2VT ln(IC /IS )/32k [VCC

a sada do circuito e Voutv.=

R [v1 /(R

||R ) +

BR

Wiley/Razavi/Fundamentals of Microelectronics [Razavi.cls

2006] F June

30,22007pat 13:42

696 (

2VT ln(IC /IS )]/18k.

v2 /(R

||R

)].

Basta

obter

o

equivalente

de shown in Fi

op amp exhibits a finite

input

impedance.

With

the

aid

of

the

op

amp

model

1

p

Th

eveninofparaand

cada .sinal de entrada e entao usar

8.43, determine

in terms

4. Considere o amplificador a seguir.

o

teorema

da

sobreposi

cao junto

comofaFig.

express

ao as a function

35. Plot the current flowing through

in the precision

rectifier

8.22(b)

conhecida

da

configura

c

a

o

inversora.

V for a sinusoidal input.

V = 1.8time

DD

R1

C1

RD

M1

V in

RS

36. Plot the696

current flowing

through o amplificador

in the precision

rectifier of Fig. Chap.

8.23(a)13as a function

6. Considere

a seguir.

Output S

time

for

a

sinusoidal

input.

Vout

37. Figure 8.57 shows a precision rectifier producingVCC

negative cycles. Plot

,

, and th

CS

V b1

V b1

Q3

V in

Q1

X

re 7.84

V in

D1

V out

Q3

Y

D1

Vout

(4.1) Se ignorarmos a modulac

ao de comprimento

D1

D2

D2

R1

de canal do transistor e se VoDDcapacitor

= 1.8 V CS cumprir

RL

devidamente o seu papel, ent

ao o ganho do amQ2

Vb

M 2da transcondut

plificador depende

apenas

ancia de

Figure 8.57

V b2

V in

Q4

Q4

M1 e de RD .

Vout

VEEa sinusoidal input.

current

as a function of time for

(4.2) DefinidoV in

um valorMpara a corrente

de flowing

pola- through

1

rizac

ao e para a fonte de alimenta

c

ao,Consider

o modothe

de precision rectifier depicted(a)

38.

in Fig. 8.58, where a parasitic resistor

has a(

operac

ao do transistor (saturac

ao oupeared

triodo)

dein parallel with

. Plot

and deaspolariza

a function

ofdetime

ine response

to a sinusoid

(6.1)

As

correntes

c

a

o

Q

Q

se3

Figure 13.15

stage with realization

of 1current sources, (b) s

re 7.85

pende apenas de RD .

input. Use a constant-voltage

model(a)

forPush-pull

the diode.

guem

ao entre

of

.aproximadamente a mesma proporc

39. We

to improve as

thecorrentes

speed of the

rectifiercashown

in Fig.

8.22(b)

(4.3) O valor da corrente de polariza

c

ao wish

depende

de satura

o reversa

de D

. connecting a dio

1 e Q1by

from

node

to

ground.

Explain

how

this

can

be

accomplished.

de

R

,

mas

n

a

o

depende

de

R

nem

de

R

,

desde

S

D for both transistors

gain of 20 and a power budget

of 2 mW. Assume 1

(6.2) and

Em regime senoidal, a eficiencia desse amplique olevel

transistor

permane

ca saturado.

he maximum allowable

at the output

is 1.5

V (i.e.,

must remain

saturation

if from

40. Suppose

in in

Fig.

8.24 varies

V to que V.

Sketch

ficador

cresce

`a medida

aumentamos

aand

tens

ao as a function

V).

if the opeamp is ideal.

(4.4) A imped

ancia de entrada do amplificador

de

pico

da

carga.

circuit can be reduced to that shown in Fig. 13.16(a), revealing a strik

vez que

a corrente

de gate

Consider the circuit infinita,

shown inuma

Fig. 7.86,

where

is very

largedo

andtransis. que o sistema opere adequadamente, a

(6.3)VPara

V

tor e nula. Essa e a grande vantagem do transistor

corrente de polarizacao de Q3CCdeve ser pelo meMOS

em

rela

c

a

o

ao

bipolar.

(a) Calculate the voltage gain.

V b1 ao valor

nos igual

aximo da corrente na Vcarga

Q 3 m

Q3

b1

(b) Design the circuit

for a Os

voltage

gain of 15C1and

budget

of

3

mW.

Assume

(4.5)

capacitores

e aCpower

s

a

o

chamados

de

dividido

por

+

1,

e

a corrente de polarizac

ao de

S

1

Q

and the

dc level of de

the acoplamento,

output must be cuja

equalfun

to cao e evitar

.

capacitores

Q4 deve ser pelo menos igual1 ao modulo do valor

as incorporates

imped

anciasados

est

agios de

entrada

e sa

da

The CS stage of Fig.que

7.87

degenerated

PMOS

current

source.

Them

degenernimo da corrente na carga dividido por 2 + 1.

D1

amplificador

interfiram

no ponto

de polariza

ation must raise thedo

output

impedance

of the current

source

to aboutcao

such

that the

(6.4)

A aplicacao da entrada entre os diodos

D1

circuito.

voltage gain remainsdo

nearly

equal to the intrinsic gain of

. Assume

e for

naoboth

logo acima de D ou logo abaixo de D

1

5. Considere o circuito a seguir.

(5.1) No caso de o amp-op ter ganho infinito, a

entrada inversora e um terra virtual, j

a que as correntes de entrada do amp-op s

ao nulas. No caso de

reduz a distorcao na(a)sada.

(b)

Figure 13.16 (a) Simplified diagram of a push-pull stage, (b) illustration o

mirror. In fact, since

Você também pode gostar

- EFC2 EA072 2s2016Documento3 páginasEFC2 EA072 2s2016Yuri OliveAinda não há avaliações

- Exp3 DesafioDocumento8 páginasExp3 DesafioYuri OliveAinda não há avaliações

- A Lógica Das Partituras em 10 Passos - Canal Posso Tocar PDFDocumento56 páginasA Lógica Das Partituras em 10 Passos - Canal Posso Tocar PDFoseas oliveira OliveiraAinda não há avaliações

- Instruções Declaração EUADocumento20 páginasInstruções Declaração EUAYuri OliveAinda não há avaliações

- Problemas Optica - 1s2017Documento3 páginasProblemas Optica - 1s2017Yuri OliveAinda não há avaliações

- DispersaoDocumento12 páginasDispersaoYuri OliveAinda não há avaliações

- Release Iguatemi 1TDocumento25 páginasRelease Iguatemi 1TYuri OliveAinda não há avaliações

- Recorrencias 4upDocumento12 páginasRecorrencias 4upYuri OliveAinda não há avaliações

- Ea614 TC2 2S2015Documento2 páginasEa614 TC2 2S2015Yuri OliveAinda não há avaliações

- PR3 Pedro PeresDocumento4 páginasPR3 Pedro PeresYuri OliveAinda não há avaliações

- Lista2 EE610ADocumento2 páginasLista2 EE610AYuri OliveAinda não há avaliações

- Introducao+classes de Funcoes 4upDocumento18 páginasIntroducao+classes de Funcoes 4upYuri OliveAinda não há avaliações

- Lista Grafos1 MC358Documento3 páginasLista Grafos1 MC358Yuri OliveAinda não há avaliações

- mc358 l5 2013s2 RezendeDocumento1 páginamc358 l5 2013s2 RezendeYuri OliveAinda não há avaliações

- tp2 Aeds2 201402Documento4 páginastp2 Aeds2 201402Yuri OliveAinda não há avaliações

- EA513 NotasAula 00Documento9 páginasEA513 NotasAula 00Yuri OliveAinda não há avaliações

- Rot 2Documento1 páginaRot 2Yuri OliveAinda não há avaliações

- EA614 Aula1 IntroDocumento14 páginasEA614 Aula1 IntroYuri OliveAinda não há avaliações

- Me323 p1 2011s1 Popov ResDocumento4 páginasMe323 p1 2011s1 Popov ResYuri OliveAinda não há avaliações

- Redações Comentadas-Unicap 2011Documento24 páginasRedações Comentadas-Unicap 2011Breno Urcino GomesAinda não há avaliações

- Poliemeros ImeDocumento5 páginasPoliemeros ImeYuri OliveAinda não há avaliações

- 3 e 4 - Ciclo Do Acucar - ImagensDocumento15 páginas3 e 4 - Ciclo Do Acucar - ImagensYuri OliveAinda não há avaliações

- Resumos - Til - Jose de AlencarDocumento7 páginasResumos - Til - Jose de AlencarYuri OliveAinda não há avaliações

- São BernardoDocumento1 páginaSão BernardoYuri OliveAinda não há avaliações

- Dom CasmurroDocumento6 páginasDom CasmurroYuri OliveAinda não há avaliações

- São BernardoDocumento1 páginaSão BernardoYuri OliveAinda não há avaliações

- Dom CasmurroDocumento6 páginasDom CasmurroYuri OliveAinda não há avaliações

- Exercícios de PronomeDocumento16 páginasExercícios de PronomeVanessa RabeloAinda não há avaliações

- Cat-0071 - Hercules 24000 C InoxDocumento247 páginasCat-0071 - Hercules 24000 C InoxRodrigo Rmv100% (2)

- Usível Tipo: ProjetoDocumento5 páginasUsível Tipo: ProjetorrdsilvaxpAinda não há avaliações

- Códigos de Falha Na Injeção Diesel Volvo D12C e D12DDocumento3 páginasCódigos de Falha Na Injeção Diesel Volvo D12C e D12DAdrian Hernandez100% (3)

- Ficha-Tecnica-1 - DIN 18799-1-2009Documento9 páginasFicha-Tecnica-1 - DIN 18799-1-2009Luís AmaroAinda não há avaliações

- Clubdediagramas - Ford Ka 2005Documento2 páginasClubdediagramas - Ford Ka 2005Ivan Hernandez PriorAinda não há avaliações

- Manual de Instruções Regulador de Tensão RT7-TH4EDocumento16 páginasManual de Instruções Regulador de Tensão RT7-TH4EclovismaoAinda não há avaliações

- Um 72-Rel - KSRDocumento1 páginaUm 72-Rel - KSRMariana Ribeiro GentaAinda não há avaliações

- COMPOSI Ç òESDocumento16 páginasCOMPOSI Ç òESFlavio RobertoAinda não há avaliações

- GED-11845 UnlockedDocumento42 páginasGED-11845 UnlockedDaniloAinda não há avaliações

- Tipos de VerboDocumento11 páginasTipos de VerboOziel MattosAinda não há avaliações

- Peugeot Bosch Monomotronic MA 3.1Documento23 páginasPeugeot Bosch Monomotronic MA 3.1ticocrazy100% (1)

- VectraC Esquema InjecaoDocumento2 páginasVectraC Esquema InjecaoMICHAEL88% (8)

- MANUAL - PEÇAS Yamaha XJ6 - Catalogo-2013Documento76 páginasMANUAL - PEÇAS Yamaha XJ6 - Catalogo-2013Renato FranciscoAinda não há avaliações

- 129 Pines Tornado PDFDocumento2 páginas129 Pines Tornado PDFJULIO OROZCOAinda não há avaliações

- Vista Explodida PT 838 TaurusDocumento2 páginasVista Explodida PT 838 TaurusEusébio CorrêaAinda não há avaliações

- Talha Demag Antiga Dkun 10 PDFDocumento21 páginasTalha Demag Antiga Dkun 10 PDFMarco Silva100% (1)

- Qdoc - Tips - Diagrama Aglale IsfDocumento35 páginasQdoc - Tips - Diagrama Aglale IsfAdderly Chinchero Torres100% (1)

- UntitledDocumento6 páginasUntitledYatã SantojaAinda não há avaliações

- Plano Electrivo Excavadora 320L 9kkDocumento2 páginasPlano Electrivo Excavadora 320L 9kkKeiber Bastos100% (2)

- Memória de Cálculo - San Lorenzo (2) (Recuperado Automaticamente)Documento65 páginasMemória de Cálculo - San Lorenzo (2) (Recuperado Automaticamente)Know HowAinda não há avaliações

- MANUAL DE INSTRUÇÕES - PISTOLAS TH TRILINGUE Logo Novo - CDRDocumento40 páginasMANUAL DE INSTRUÇÕES - PISTOLAS TH TRILINGUE Logo Novo - CDRAdriano Estevão ProchnoAinda não há avaliações

- Lista Cruzada Conversão VW (MAN) X Cummins PDFDocumento35 páginasLista Cruzada Conversão VW (MAN) X Cummins PDFFabio MacielAinda não há avaliações

- Catálogo - 2020 - Provisório-Paginas (1) Consumidor FinalDocumento44 páginasCatálogo - 2020 - Provisório-Paginas (1) Consumidor FinalÂngelo RodiniAinda não há avaliações

- CRF 230 FichaDocumento10 páginasCRF 230 FichaPedro Anderson Pires100% (1)

- DGRM - Lu Delivery IsfDocumento3 páginasDGRM - Lu Delivery IsfJuarezGeronimo100% (8)

- Fiat Freemont 2.4 16V 2011 Esquema Elétrico Injeção Eletrônica - Siemens VdoDocumento2 páginasFiat Freemont 2.4 16V 2011 Esquema Elétrico Injeção Eletrônica - Siemens VdoDouglas Laet100% (6)

- Anexo Iii - Composições Analíticas Data:28/12/2022Documento8 páginasAnexo Iii - Composições Analíticas Data:28/12/2022Maria ClaraAinda não há avaliações

- Circuito Hidráulico CH 570 - 20171105Documento132 páginasCircuito Hidráulico CH 570 - 20171105Luiz henrique Alves dos santosAinda não há avaliações

- Aula 07 Tiristores-AtualizadoDocumento44 páginasAula 07 Tiristores-AtualizadoDayana VieiraAinda não há avaliações