Escolar Documentos

Profissional Documentos

Cultura Documentos

Fonte Basico 2016

Enviado por

Romeu Corradi JúniorTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Fonte Basico 2016

Enviado por

Romeu Corradi JúniorDireitos autorais:

Formatos disponíveis

Verso 1.2.1 10.12.12 Adaptado Prof.

Corradi

www.laboratorio.online.pt

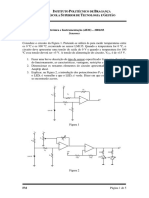

Fontes de alimentao (FALs): introduo

PRI

Uma fonte de tenso U0 genrica pode ser reduzida (ou

simplificada) aos blocos da figura ao lado representada:

- fonte de tenso UIN propriamente dita;

- respetiva resistncia interna.

I0

RI

PRL

UIn

Assim,

- a tenso UOUT aos seus terminais varia entre UOUT Max e UOUT

Min com UIn e tambm com a intensidade IO solicitada pela

carga devido RI; ou seja no uma tenso estabilizada;

- h dissipao ou perda - de potncia na resistncia

interna Ri, o que provoca aquecimento interno.

U0

I0

Ou seja:

RL

U

UO com estabilizao

UIN

UO = UIN - U em que U a queda de tenso na

UO sem estabilizao

resistncia interna RI (U = IO*RI );

PTOTAL = PRI + PRL

I

Define-se ainda regulao de carga/load regulation como (UO UIMax) / UIMax (em %) que nos

indica a variao da tenso com a corrente.

FALS LINEARES

As diversas solues tecnolgicas procuram dentro

dos limites e caratersticas pretendidas para cada fonte

reduzir ao mximo aqueles inconvenientes: reduzir as

perdas internas (e assim aumentar a eficincia) e

estabilizar a tenso de sada UO.

(a estabilizao obtida

mediante o controlo sobre UIN

ou/e RI)

PRINCIPAIS

TIPOS DE FALS

FALS COMUTADAS

(a estabilizao obtida

mediante o controlo sobre a

frequncia de comutao)

FALs lineares estabilizadas (com regulao em srie)

Regulador

T

UIN

UO

URef

Com este circuito, a U0

deixa de depender de UIN

ou RI pois o bloco URef

RL impe um valor constante

a UO

R1

UIN

UO = URef O,6V

URef R2

T o elemento regulador

srie de UO.

circuito, uma

U0 Neste

amostra de U0 ( obtida

RL

na diviso potenciomtrica de R1 e R2),

comparada com URef e

o resultado regula o

elemento srie T.

Esquema de uma FAL estabilizada com regulador srie (12VDC, 800mA)

Q1

BD237

1B4B42

12V

AC

R1

180

D

3

UREF

D1

C1

1mF

C2

100uF

UO = UZ 0,7V = 12,3V

PD Q1 = UCE IO

BZV85-C13

FAL_intro_a.doc

RL

A tenso de referncia UREF

obtida mediante o dodo

zener D1 que polarizado

por R1. Como o dodo tem

UZ = 13V, a tenso UO de

cerca de 12,3V.

Verso 1.2.1 10.12.12

www.laboratorio.online.pt

Fontes de alimentao (FALs): introduo (cont.)

(2)

FAL estabilizada com regulador srie com 2 transistores (12VDC, 800mA)

Q1

BD237

18V

AC

R1

2k

Se a tenso UOUT

aumentar, a tenso da

base de Q2 tambm

aumentar e a respetiva

corrente IC atravs de R1,

provocando uma reduo

da tenso do emissor de

Q2. Analogamente, se UO

diminuir, tambm diminuir

a tenso da base de Q2,

originando maior tenso na

base de Q1 e no emissor

do mesmo.

R3

3k

R5

1k

Q2

1B4B42

RL

R4

C1

1mF

BC237BP

3k

5%

D1

BZV60-C5V6

Como R3 e R4 constituem uma diviso potenciomtrica podemos calcular UO = (R3 + R4)/R3 (UZ + UBE) = 12,4V

Q1

BD237

2

18V

AC

R1

2k

R3

1k

R6

R5

1k

3

Q2

1B4B42

C1

1mF

RL

15k

95%

Key=B

BC237BP

R4

2k

D1

BZV60-C5V6 5%

Para se obter uma

tenso regulvel, a

srie R3+R4 do

circuito anterior

deve ser

substituida por

uma outra srie

com um

potencimetro e

duas resistncias

de segurana, ou

seja:

Estabilizao com regulador em paralelo

A estabilizao das FALs estudadas anteriormente obtida com o elemento regulador o

transstor NPN ligado em srie com a carga RL. Embora com desvantagens por causa da

dissipao de potncia em Rs tambm se pode usar o regulador em paralelo (Pe. LM4030, 4050..)

A regulao paralelo com

O dodo zener muito

U UIN Max

usado na estabilizao

um transstor seria:

I

em paralelo

UZ

UIN Min

UO

t

IS

IZMin

Como IZMin 0 IS IO e

IO

UZ = UO, temos que

RS Max = (UIN Min UZ)/ IO Max

IZ R

Para que o dodo no se

L

funda na UIN Max e IO Min

Dz

UO RS Min = (UIN Max - UZ) / IZMax

com IZMax = PZMax / UZ .

Rs

Quando

IZMx (PZMx)

polarizado

inversamente

(IZMin 0mA) a tenso UZ

mantem-se constante

independentemente da IZ

FAL_intro_a.doc

UIN

Uz

UOUT = UZ + UBE

IS

UIN

IO

Rs

Uz

DZ

UB

E

RL

Q1

UO

Verso 1.2.1 10.12.12

www.laboratorio.online.pt

Fontes de alimentao (FALs): introduo (cont.)

(3)

Regulao em srie com realimentao aumentada

(atravs de ampop)

Q1

R3

R2

U1

RL

UIN

UO

UZ

R1

Este circuito semelhante a um j

estudado (FAL estabilizada com

regulao srie com 2 transistores) .

Contudo o ampop refora a

realimentao negativa: se a tenso

de sada UO diminuir aumenta a

tenso na base de Q1 pelo que

aumenta UO e vice versa.

UOUT = (R1 + R2). UZ / R1

PD = (UIN UO) . IC

Por vezes substitui-se Q1 por um transstor Darlington, portanto com maior ganho (cerca de 1000) para a

corrente de sada do ampop: perante um ligeiro aumento de corrente na sua sada, UO estabiliza

Proteo contra excesso de corrente

IO

Q1

BD137

R1

470

A R2 funciona como sensor

da corrente de carga IO. A

tenso UR2 = IO x R2, que

proporcional corrente IO,

aplicada base de Q3.

Quando esta ultrapassa o

valor de 0,6V, Q3 comea a

conduzir reduzindo a tenso

de base de Q1, o transstor

de regulao, e diminui ou

anula mesmo a tenso de

sada UO.

R3

RL UO

Q2

UIN

BC238BP

10k

0%

Key=A

Dz

BZV60-C4V3

R4

4.7k

Q3

BC238BP

R2

1

UR2 = 1 x 0,6A

UR2=UBE=0,6V

No circuito do lado (em que

novamente o efeito da

realimentao reforado por um

ampop) a resistncia-sensor faz

Q2 conduzir quando for percorrida

por uma corrente IO = 0,2A (UBE Q2

= 3 x 0,2A = 0,6V). Assim, a

corrente de sada do ampop

desviada da base do transstor

FAL_intro_a.doc

IO

IO

Q1

BD137

R1

820

Q2

Dz

BZV60-C4V7

IO

IO

R4

750

BC238BP

R3

1k

UIN

R2

3

50%

1k

Key=A

R6

750

UO

RL

IO

Verso 1.2.1 10.12.12

www.laboratorio.online.pt

Fontes de alimentao (FALs): introduo (cont.)

(4)

Esquema de uma FAL estabilizada com regulador srie com tenso

de sada negativa em relao massa (-12V, 1A).

A anlise do circuito

desta FAL muito

1

UIN AC

semelhante ao circuito

4

1N4007

1N4007

Q1

TIP42A

12V

0

da FAL com sada

AC

D4

D2

positiva anteriormente

R1

2

220

analisada: como o

3

UO

1N4007

1N4007

potencial positivo est

R2

1k

agora ligado massa,

C1

D5

R

os componentes

L

C2

BZV60-C12

1mF

470uF

esto

consequentemente

reorientados (ponte

retificadora,

condensadores

eletrolticos, dodo zener, transstor (agora PNP),). Com um dodo zener de 12V, a tenso UO

de cerca de 11,4V

D3

FAL_intro_a.doc

D1

Verso 1.2.1 10.12.12

www.laboratorio.online.pt

Fontes de alimentao (FALs): introduo (cont.)

(5)

Projeto/Blocos de uma fonte estabilizada, regulvel e com proteo

0V...Umax

(230V)

TRANSFOR

MADOR

RECTIFICAO

/FILTRAGEM

AMPLIFICADOR /

REGULADOR

(DC)

(AC)

PROTECO

GERADOR

TENSO

REFERNCIA

COMPARADOR

A fonte que se segue estabilizada entre 0...0,4A e regulvel de 4...12V. Tem proteco para

uma corrente de 0,5A.

Amplificao

Q3

BD137

D3

U3

12V

V1

1N4001

R3

1.5k

Q2

BC548B

11

R6

100

10

1N4001

1N4001

D4

220V

D1

R1

4.7k

Umais

7

R7

2k

Key=A

Q4

D2

R2

220

BC548B

Comparao

15

1N4001

13

Tenso

C3

1uF Refer.

C4

100nF

D5

BZX55C3V0

50%

16

Q1

Transformao,

Rectificao,

Filtragem

C1

1mF

C2

R8

200

BC548B

R4

220

100nF

0

R5

Proteco

C5

470uF

C6

100nF

Umenos

1.8

Transformao, Rectificao e Filtragem: constituido pelo tranformador 220V/12V, dodos e

condensadores C1 e C2;

Gerador de Tenso Constante: Dodo Zener D5, polarizado por R3, de tal modo que mantm

sempre uma tenso de referncia constante mesmo que a corrente de polarizao

varie/diminua;

Comparao/Regulao: compara uma fraco da tenso de sada atravs do cursor de R 7

(Rvarivel) com a tenso do emissor de Q4: se a tenso UBE de Q4 diminui, tambm diminui a IC do

mesmo e a que-da de tenso em R1, pelo que aumenta a polarizao de Q 2/Q3... diminui a UCE

de Q3, e aumenta a U0;

Proteco: quando a corrente em R5 aumenta de modo a obter-se uma tenso UBE para Q1

aprecivel, este comea a conduzir e a puxar corrente do n 13. Q2 deixa de estar

conduo...

Amplificao de Potncia: constituido pela ligao em Par Darlington de Q2 e Q3...

Exerccio: simular e optimizar esta FAL a partir do seu circuito em MultiSim FAL_intro.ms10

FAL_intro_a.doc

Verso 1.2.1 10.12.12

www.laboratorio.online.pt

Fontes de alimentao (FALs): introduo (cont.)

(6)

Reguladores lineares monolticos

79XX

??78XX

??3940

??2940

Os circuitos discretos (constitudos por componentes

individuais) de FALs estudados anteriormente so na

OUT

TO-220

IN

prtica muitas vezes substitudos por circuitos

TO-220

IN

integrados monolticos, circuitos reguladores de

OUT

tenso srie pois so os mais eficientes e baratos. Os

78LXX

diversos fabricantes acrescentaram ainda outras funcionalidades e 79LXX

tambm por isso so muito populares e facilitam o projeto de FALs

TO-92

TO-92

para praticamente todas as situaes possveis. Estes CIS

chamados genericamente por reguladores de tenso pois, tal

OUT

como os estudados anteriormente, procuram estabilizar, e em

IN

IN

OUT

alguns casos regular, a tenso de sada UO apresentam-se com

(7)

723

diversos tipos de encapsulamento, a que correspondem

caractersticas e aplicaes diversas.

Como escolher um CI regulador de tenso

(Voltage Regulator)

OUT(10)

Caratersticas

IN (11,12)

PDIP14

UOUT pode ser fixa ou regulvel e ainda positiva ou negativa. A srie muito

popular 78XX de tenso positiva fixa; a srie 79XX negativa tambm fixa. A

srie LM117/LM317 pode por sua vez regular UOUT de 1,2V a 37V.

IOUT MAX, Intensidade mxima A IOUT determinada pela carga alimentada e limitada pela intensidade

mxima IOUT MAX caraterstica de cada tipo de regulador. Na srie 78XX ou 79XX

de carga

(cpsula TO-220) IOUT MAX de 1A a 1,5A quando o regulador montado num

dissipador de calor. Na srie 78LXX de 100mA (cpsula TO-92, designada por

baixa potncia, low-power IC regulators).

UINMAX, Tenso de entrada Tenso mxima que o regulador suporta entrada sem se queimar por

excesso de calor.

Tenso mnima entre UIN e UOUT que garante uma boa regulao. Nas sries

U, Dropout Voltage ou

78XX e 79XX de 23V. Quando no possvel haver aquela margem de

Tenso de Abatimento

segurana (nos circuitos alimentados por baterias) usam-se reguladores de

tenso de baixo abatimento/low dropout regulators como os da srie LM2940

que de 0,5V a 1V com 1A em IOUT , o que torna este regulador excelente para

algumas aplicaes.

UOUT, Regulao de carga Mede em percentagem a variao de UOUT em funo de uma gama de IOUT

(quanto menor, melhor o regulador). P.e., no LM7815, a tenso de sada

(15V) varia de 12mV quando a corrente de carga varia de IOUT = 5mA a IOUT = 1,5A.

UOUT, Regulao de rede Mede em percentagem a variao de UOUT em funo de uma gama de UIN

(quanto menor, melhor o regulador ). P.e., no LM7815, a tenso de sada

(15V) varia de 4mV quando a tenso UIN varia de UIN = 17,5V a UIN = 30V.

UIN/UOUT, Rejeio de Ripple Mede, em dB (80dB para o LM7805), a relao dos ripples de UIN e UOUT.

Proteo contra excesso de calor Um sensor trmico interno protege o CI do excesso de calor/Potncia dissipada

UOUT, Tenso de sada

Proteo contra IOUT elevadas

Proteo contra excesso de corrente e curto-circuitos

IQ, Corrente de repouso

Quiescente corrent, corrente consumida mesmo quando IOUT = 0

FAL_intro_a.doc

Verso 1.2.1 10.12.12

www.laboratorio.online.pt

Fontes de alimentao (FALs): introduo (cont.)

(7)

F. alimentao genrica com um regulador de 3 pinos

U

IIN

IN

REGULADOR

DE TENSO

OUT

(FIXO)

UIN

I0UT

IQ GND

C1

C2

UOUT

RL

C1, C2: condensadores de desacoplamento das correntes de alta frequncia ou transitrios

recomendados pelos fabricantes (cerca de 100nF, poliester).

U

UIN MAX

UIN MIN

UOUT

t

Caratersticas mais gerais a 25C de alguns dos reguladores de trs

pinos das sries 78XX e 78LXX da Texas Instruments/National

Semicondutor (A78XX A 78LXX)

35V

5V

35V

10V

35V

15V

40V

40V

30V

2,6V

30V

6,2V

-35V

-8V

40V 1,2537V

40V

MAX

>1,5A

>1,5A

>1,5A

>1,5A

100mA

100mA

<-1,5A

>1,5A

UOUT UOUT Rejeio

(Carga) (Rede) Ripple

2V 15mV

3mV

2V 12mV

7mV

2V 12mV 11mV

2V 12mV 18mV

1,7V 20mV 12mV

1,7V 35mV 16mV

1,1V 15mV 12mV

40V 0,1%/V 0,01%/V

237V 150mA 40V -0,3mV/V 0,1V/V

78dB

71dB

70dB

66dB

51dB

48dB

60dB

57dB

IQ

8mA

4,3mA

4,4mA

4,6mA

3,6mA

3,9mA

1,5mA

50A

TO220

FAL_intro_a.doc

(Valor Tpico)

IOUT

TO-92

A723

UOUT

TO-220

A7805C

A7810

A7815

A7824

A78L02

A78L06

A7908

LM317

UIN MAX

CPSULA

CI

DIP

74dB 2,3mA 14

Verso 1.2.1 10.12.12

www.laboratorio.online.pt

Fontes de alimentao (FALs): introduo (cont.)

(8)

Esquema de blocos de um regulador de tenso monoltico

(Fairchild Semicondutor)

Circuitos prticos com reguladores (srie) de tenso

Aplicao tpica

Para obter uma tenso estabilizada superior a VXX

Tenso de sada ajustvel

Aumento da Io MX

FAL_intro_a.doc

Verso 1.2.1 10.12.12

www.laboratorio.online.pt

Fontes de alimentao (FALs): introduo (cont.)

(9)

Circuitos prticos com reguladores (srie) de tenso (Cont.)

Aumento da Io MX e proteco contra CC

FAL de tenses simtricas

FAL comutada

Estabilizao de tenso negativa com

regulador positivo fixo

Aplicao tpica do LM117317

(Regulao varivel)

Regulao varivel com shutdown

Com IADJ.R2 0

FAL_intro_a.doc

Verso 1.2.1 10.12.12

www.laboratorio.online.pt

Fontes de alimentao (FALs): introduo (cont.)

(10)

Circuitos prticos com reguladores (srie) de tenso (Cont.)

Regulao com intensidade elevada

FAL comutada de baixo custo

FAL_intro_a.doc

Verso 1.2.1 10.12.12

www.laboratorio.online.pt

Fontes de alimentao (FALs): introduo (cont.)

(11)

Circuitos prticos com reguladores (srie) de tenso (Cont.)

Circuito FAL com LM723

FAL_intro_a.doc

Você também pode gostar

- Amplif Pot BásicoDocumento38 páginasAmplif Pot BásicoRomeu Corradi JúniorAinda não há avaliações

- Microparte 28051 PDFDocumento147 páginasMicroparte 28051 PDFRomeu Corradi JúniorAinda não há avaliações

- Aula 06 - Arquitetura-Computador - 2021Documento69 páginasAula 06 - Arquitetura-Computador - 2021Romeu Corradi JúniorAinda não há avaliações

- Eletrônica Industrial - Aplicação Tiristores - 2020Documento10 páginasEletrônica Industrial - Aplicação Tiristores - 2020Romeu Corradi JúniorAinda não há avaliações

- Introdução TDM I - 1Documento43 páginasIntrodução TDM I - 1Romeu Corradi JúniorAinda não há avaliações

- Introdução TDM I - 4Documento77 páginasIntrodução TDM I - 4Romeu Corradi JúniorAinda não há avaliações

- Me Did AseelDocumento18 páginasMe Did AseelRomeu Corradi JúniorAinda não há avaliações

- SensoresDocumento5 páginasSensoresRomeu Corradi JúniorAinda não há avaliações

- Controle e Automação - Ini - 2014Documento43 páginasControle e Automação - Ini - 2014Romeu Corradi JúniorAinda não há avaliações

- Exer Assembly 02 EmbarcadosDocumento12 páginasExer Assembly 02 EmbarcadosRomeu Corradi JúniorAinda não há avaliações

- Exer Assembly 01Documento24 páginasExer Assembly 01Romeu Corradi JúniorAinda não há avaliações

- Apostila 8051projetoDocumento62 páginasApostila 8051projetoRomeu Corradi JúniorAinda não há avaliações

- Desenho EletroeletrônicoDocumento44 páginasDesenho EletroeletrônicoRomeu Corradi JúniorAinda não há avaliações

- Teorema de TAllesDocumento1 páginaTeorema de TAllesRomeu Corradi JúniorAinda não há avaliações

- Conversor AD e DADocumento25 páginasConversor AD e DARomeu Corradi JúniorAinda não há avaliações

- Exer Assembly 02 EmbarcadosDocumento12 páginasExer Assembly 02 EmbarcadosRomeu Corradi JúniorAinda não há avaliações

- Exer Assembly 01Documento24 páginasExer Assembly 01Romeu Corradi JúniorAinda não há avaliações

- SensoresDocumento5 páginasSensoresRomeu Corradi JúniorAinda não há avaliações

- Exer Assembly 02 EmbarcadosDocumento12 páginasExer Assembly 02 EmbarcadosRomeu Corradi JúniorAinda não há avaliações

- Apostila de Sistemas Microprocessados PDFDocumento221 páginasApostila de Sistemas Microprocessados PDFRomeu Corradi JúniorAinda não há avaliações

- Manual Do KeyprogramDocumento182 páginasManual Do Keyprogramfgodoy85Ainda não há avaliações

- Micro 8051 NoturnoDocumento161 páginasMicro 8051 NoturnoRomeu Corradi JúniorAinda não há avaliações

- Overview 8051Documento16 páginasOverview 8051Romeu Corradi JúniorAinda não há avaliações

- Conversão TecnologiaDocumento2 páginasConversão TecnologiaRomeu Corradi JúniorAinda não há avaliações

- Apostila 8051Documento90 páginasApostila 8051Steffan FrantzAinda não há avaliações

- MicroMCS51 2010Documento79 páginasMicroMCS51 2010Romeu Corradi JúniorAinda não há avaliações

- Cai CLP BásicoDocumento46 páginasCai CLP BásicoRomeu Corradi JúniorAinda não há avaliações

- Teste de BateriaDocumento1 páginaTeste de BateriaRomeu Corradi JúniorAinda não há avaliações

- Amplificadores Potencia Classes 2018Documento69 páginasAmplificadores Potencia Classes 2018Romeu Corradi Júnior100% (1)

- Ficha Química 8º AnoDocumento4 páginasFicha Química 8º Anogorete71100% (2)

- Relatório 4 - Análise Dos Cátions Do Grupo III (Cr3+, Al3+, Fe3+, Zn2+, Mn2+, Fe2+, Co2+, Ni2+) - QAQ (Grupo 03)Documento22 páginasRelatório 4 - Análise Dos Cátions Do Grupo III (Cr3+, Al3+, Fe3+, Zn2+, Mn2+, Fe2+, Co2+, Ni2+) - QAQ (Grupo 03)David Carvalho100% (1)

- (Mansueto) ADABAS-C, ResumoDocumento10 páginas(Mansueto) ADABAS-C, ResumoAnderson CPSAinda não há avaliações

- OndasDocumento19 páginasOndasJoViAinda não há avaliações

- Evaporação Do Caldo ResumoDocumento2 páginasEvaporação Do Caldo ResumoRaniel Gomes AlexandreAinda não há avaliações

- 02-Movimento Retilíneo Uniforme (MRU)Documento4 páginas02-Movimento Retilíneo Uniforme (MRU)Italo VieiraAinda não há avaliações

- Apostila ESSA 2017-2018 Completa-1-2 PDFDocumento464 páginasApostila ESSA 2017-2018 Completa-1-2 PDFGabriel71% (7)

- Escola Técnica de Sete LagoasProcesso Seletivo - 2º Semestre de 2012Documento8 páginasEscola Técnica de Sete LagoasProcesso Seletivo - 2º Semestre de 2012fábio_amorim_1Ainda não há avaliações

- CV - Luiz Otavio-AtualDocumento3 páginasCV - Luiz Otavio-AtualLuiz Otávio PrevedelAinda não há avaliações

- Plano de Ensino Metrologia e InstrumentacaoDocumento4 páginasPlano de Ensino Metrologia e InstrumentacaoMauricio VeberAinda não há avaliações

- NR18 - Apostila - Terraplanagem - P21 - Nov 20Documento17 páginasNR18 - Apostila - Terraplanagem - P21 - Nov 20Luis Gustavo de Souza SantosAinda não há avaliações

- Trabalho de Biologia 3Documento3 páginasTrabalho de Biologia 3João VictorAinda não há avaliações

- Trabalho Semestral RennanDocumento3 páginasTrabalho Semestral RennanRennan BrancoAinda não há avaliações

- Zinc Clad 61 BRDocumento2 páginasZinc Clad 61 BRMarineide SantanaAinda não há avaliações

- ÓxidosDocumento7 páginasÓxidosFale Art'sAinda não há avaliações

- Mecânica Dos FluidosDocumento22 páginasMecânica Dos FluidosMary_Jane_FAinda não há avaliações

- Aula Prática 1 - Relatório Sobre Preparo Do MostoDocumento6 páginasAula Prática 1 - Relatório Sobre Preparo Do MostopoliveiramaiaraAinda não há avaliações

- Aço ASTM F1586 - VillaresDocumento2 páginasAço ASTM F1586 - Villareskayron limaAinda não há avaliações

- Relatório - Estimativa Da Potência de Um Forno de Microondas 1Documento11 páginasRelatório - Estimativa Da Potência de Um Forno de Microondas 1fernando katonaAinda não há avaliações

- UntitledDocumento314 páginasUntitledChristiane MenezesAinda não há avaliações

- 3 Avaliação Formativa: CadernoDocumento26 páginas3 Avaliação Formativa: CadernoGilson Fideles de OliveiraAinda não há avaliações

- Ac Jul Ces Que PDF - 16835Documento18 páginasAc Jul Ces Que PDF - 16835Fernanda MarquesAinda não há avaliações

- Comando PingDocumento3 páginasComando PingfinaseeAinda não há avaliações

- Projeto Conceitual E Análise Estrutural de Um Veículo ModularDocumento134 páginasProjeto Conceitual E Análise Estrutural de Um Veículo ModularIAGO MATEUS SA AQUINOAinda não há avaliações

- Cat C3 A1logo 20brakematic PDFDocumento66 páginasCat C3 A1logo 20brakematic PDFJefferson KennedyAinda não há avaliações

- Fluxograma PelotizaçãoDocumento1 páginaFluxograma PelotizaçãoJu CottaAinda não há avaliações

- Datasheet Lge Afff Ar 3 3 HC Ar Tp5Documento3 páginasDatasheet Lge Afff Ar 3 3 HC Ar Tp5Franco LealAinda não há avaliações

- Previsão e Monitoramento Da Vida Útil de Gasodutos Utilizando Modelos de CorrosãoDocumento11 páginasPrevisão e Monitoramento Da Vida Útil de Gasodutos Utilizando Modelos de CorrosãoPaulo Marcos Cabral JuniorAinda não há avaliações

- Plano-Estudos 636 PTDocumento24 páginasPlano-Estudos 636 PTpippiAinda não há avaliações

- Catálogo Repuestos Agrale MA 8.5 PlusDocumento105 páginasCatálogo Repuestos Agrale MA 8.5 PlusmarearrietaAinda não há avaliações