Escolar Documentos

Profissional Documentos

Cultura Documentos

1P Organizacao e Arquitetura de Computadores

Enviado por

Stélio ZacariasDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

1P Organizacao e Arquitetura de Computadores

Enviado por

Stélio ZacariasDireitos autorais:

Formatos disponíveis

Ministrio da Educao

UNIVERSIDADE TECNOLGICA FEDERAL DO PARAN

Cmpus Guarapuava

PLANO DE ENSINO

CURSO Curso Superior de Tecnologia em Sistemas para Internet MATRIZ 1

FUNDAMENTAO LEGAL Resoluo n 132/10-COEPP de 08 de outubro de 2010.

DISCIPLINA/UNIDADE CURRICULAR CDIGO PERODO CARGA HORRIA

Organizao e Arquitetura de AT AP APS AD APCC Total

SI31C 1.

Computadores 2 1 7 0 0 58

OBJETIVOS

Conhecer a Arquitetura fsica de Sistemas Computacionais. Entender como o computador trabalhar com instrues em

modo binrio.

EMENTA

Aritmtica para computadores com inteiros e ponto flutuante. Arquiteturas gerais de computadores. Unidade Central de

Processamento. Unidade Lgica e Aritmtica. Instrues e linguagem de mquina. Modos de endereamento. Sistemas

de memria. Pipeline. Mecanismos de interrupo. Interface com perifricos. Arquiteturas Paralelas e no

Convencionais.

CONTEDO PROGRAMTICO

ITEM EMENTA CONTEDO

Sistemas de numerao: decimal, binrio, hexadecimal.

Aritmtica para computadores com inteiros e Converso de um sistema para outro. Aritmtica de inteiros:

1

ponto flutuante soma, subtrao, diviso, multiplicao. Breve abordagem sobre

aritmtica de ponto flutuante.

Marco da Arquitetura de Computadores. Unidades de medida.

2 Arquiteturas gerais de computadores

Tipos de computadores.

Estrutura bsica de um computador: Unidade Central de

Unidade Central de Processamento. Unidade Processamento (Unidade de Controle, Unidade Lgica e

3

Lgica e Aritmtica. Pipeline Aritmtica, Registradores), memria, barramentos. Ciclo de

Busca-Decodificao- Execuo. Pipeline.

Conjunto de instrues: representao das instrues, tipos de

4 Instrues e linguagem de mquina

instrues, tipos de operandos, tipos de operaes.

Modos de endereamento: imediato, direto, indireto, por

5 Modos de endereamento

registrador.

Memria interna: caracterstica dos sistemas de memria,

hierarquia de memria, tipos de memria e organizao,

6 Sistemas de memria

memria cach. Memria externa: disco magntico, RAID, fita

magntica.

Conceito de interrupo. Interrupo e ciclo de instruo.

7 Mecanismos de interrupo

Mltiplas interrupes.

8 Interface com perifricos Barramentos, o padro PCI para interface com perifricos.

Multiprocessadores de memria compartilhada.

9 Arquiteturas Paralelas e no Convencionais

Multicomputadores de troca de mensagens.

Revisado por: Data:

Aprovado por: Coordenao de Curso Vigora a partir de:

PROCEDIMENTOS DE ENSINO

AULAS TERICAS

Aula expositiva. Exerccios.

A maioria das aulas sero aulas expositivas. Para estas aulas os seguintes recursos didticos sero utilizados:

multimdia, computador, ambiente virtual de aprendizagem (Moodle), pgina do professor na Internet, entre outros.

Alguns exerccios sero resolvidos durante a explicao de cada contedo para melhor entendimento do que foi

explicado.

AULAS PRTICAS

Aplicao de listas de exerccios.

Cada contedo abordado durante o andamento da disciplina ter sua respectiva lista de exerccio que ser resolvida

pelos alunos e corrigida parcialmente em sala de aula.

ATIVIDADES PRTICAS SUPERVISIONADAS

Listas de Exerccios, Trabalhos individuais e em grupo, alm de pesquisas complementares podero ser utilizados

como instrumentos auxiliares para a construo do conhecimento. Como trabalho final ser solicitado um trabalho

escrito (artigo), a ser explanado, sobre alguma arquitetura paralela ou alguma arquitetura no convencional, bem como

sobre processadores (p. e., Pentium).

ATIVIDADES A DISTNCIA

ATIVIDADES PRTICAS COMO COMPONENTE CURRICULAR

PROCEDIMENTOS DE AVALIAO

Duas (2) provas, listas de exerccios e trabalho final escrito.

As avaliaes sero realizadas considerando os contedos estudados durante o semestre. Duas provas tericas sero

aplicadas, as quais contemplaro os contedos discutidos em sala at a data de sua realizao. As provas contero

questes objetivas, subjetivas, mltipla escolha, entre outras. As provas valero 70% da nota final. O trabalho final

20% e os 10% restantes da nota final sero distribudos em outras atividades, como listas de exerccios, atividades de

pesquisa, entre outros. Caso o aluno no obtenha nota para a aprovao, ser realizada uma prova aplicando todo o

contedo da disciplina a qual substituir a menor nota das duas provas realizadas.

REFERNCIAS

Referencias Bsicas:

MONTEIRO, Mario. A. Introduo Organizao de Computadores. 5. ed. Rio de Janeiro: LTC, 2007.

STALLINGS, William. Arquitetura e Organizao de Computadores. 8. ed. So Paulo : Prentice Hall, 2010.

TANEMBAUM, Andrew. Organizao Estruturada de Computadores. 5. ed. So Paulo: Prentice-Hall, 2006.

Referncias Complementares:

HENNESSY, John L.; PATTERSON, David A.. Organizao e projeto de computadores: a interface

hardware/software. 2. ed. Rio de Janeiro: LTC, 2009.

MURDOCA, Miles J.; HEURING, Vincent P. Introduo arquitetura de computadores. Rio de Janeiro: Campus,

2000.

NESSY, John L.; PATTERSON, David A. Arquitetura de computadores: uma abordagem quantitativa. Rio De

Janeiro: Campus, 2008.

PARHAMI, Behrooz. Arquitetura de computadores: de microprocessadores a supercomputadores. So Paulo:

McGraw-Hill, 2008. 560 p.

WEBER, Raul Fernando. Fundamentos da arquitetura de computadores. 3. ed. Porto Alegre: Bookman, 2008.

ORIENTAES GERAIS

Assinatura do Professor Assinatura do Coordenador do Curso

Revisado por: Data:

Aprovado por: Coordenao de Curso Vigora a partir de:

Você também pode gostar

- S2.1 - Arquitetura e Organização de ComputadoresDocumento2 páginasS2.1 - Arquitetura e Organização de ComputadoresRicardo KratzAinda não há avaliações

- Arquitetura A1Documento16 páginasArquitetura A1lykerAinda não há avaliações

- Arquitetura e Organização de ComputadoresDocumento3 páginasArquitetura e Organização de ComputadoresXavier JoaquimAinda não há avaliações

- GSI013 Aula01Documento22 páginasGSI013 Aula01douglas13mgAinda não há avaliações

- 01-Introdução A Organização de ComputadoresDocumento40 páginas01-Introdução A Organização de ComputadoresNzuzii RodolfoAinda não há avaliações

- Aula 1 Micro 2 GBC036 - 01Documento26 páginasAula 1 Micro 2 GBC036 - 01Vivyane MarquesAinda não há avaliações

- Apresentação Da Disciplina Introdução A InformáticaDocumento36 páginasApresentação Da Disciplina Introdução A InformáticaRodrigo CostaAinda não há avaliações

- ArquiteturaDocumento4 páginasArquiteturaXavier JoaquimAinda não há avaliações

- Plano de Ensino Computação 1 UtfprDocumento2 páginasPlano de Ensino Computação 1 UtfprLuiz Felipe CostaAinda não há avaliações

- Planificação SI TPI 18-19Documento4 páginasPlanificação SI TPI 18-19jdoceAinda não há avaliações

- Arquitetura de ComputadoresDocumento1 páginaArquitetura de Computadorescoleveio100% (1)

- Laboratório de Arquitetura e Organização de ComputadoresDocumento4 páginasLaboratório de Arquitetura e Organização de ComputadoresLeandro De OliveiraAinda não há avaliações

- Plano de Ensino Arquitetura e Organizao de Computadores IDocumento5 páginasPlano de Ensino Arquitetura e Organizao de Computadores IDiógenes Vaz de MeloAinda não há avaliações

- Plano AOC V2 2023Documento3 páginasPlano AOC V2 2023SansaoTimbaneAinda não há avaliações

- Aula 1 - PortgDocumento32 páginasAula 1 - PortgAbisaque MiguelAinda não há avaliações

- Plano de Ensino-ArqComp TuB-1Sem2012Documento4 páginasPlano de Ensino-ArqComp TuB-1Sem2012Vinicios LoureiroAinda não há avaliações

- Estudo A Parte de Arquitetura e Organização de ComputadoresDocumento8 páginasEstudo A Parte de Arquitetura e Organização de ComputadoresCurso OpsAinda não há avaliações

- Arquitetura e ManutencaoDocumento89 páginasArquitetura e ManutencaoMonck Charles AlbuquerqueAinda não há avaliações

- Arquitetura e ManutencaoDocumento89 páginasArquitetura e ManutencaoSamyla BastosAinda não há avaliações

- Plano de Ensino - 2023-1 - Programação Estruturada V1-3Documento3 páginasPlano de Ensino - 2023-1 - Programação Estruturada V1-3João LinharesAinda não há avaliações

- Aula de Arquitetura de Memorias PDFDocumento30 páginasAula de Arquitetura de Memorias PDFJuliete BarrosAinda não há avaliações

- Pré-Prova Microcontroladores e MicroprocessadoresDocumento6 páginasPré-Prova Microcontroladores e MicroprocessadoresDouglas Cintra ValençaAinda não há avaliações

- Introducao A Ciencia Da ComputacaoDocumento3 páginasIntroducao A Ciencia Da ComputacaoAndrey Barros De SouzaAinda não há avaliações

- Resumo Sistemas ComputacionaisDocumento18 páginasResumo Sistemas ComputacionaisparreirasglAinda não há avaliações

- Plano de Aula Concurso UFRPE 2Documento3 páginasPlano de Aula Concurso UFRPE 2Lucas CambuimAinda não há avaliações

- Plano de Trabalho Docente - 2019: Ensino TécnicoDocumento7 páginasPlano de Trabalho Docente - 2019: Ensino TécnicoUi OiAinda não há avaliações

- Arq SiDocumento56 páginasArq SiEduardo FreireAinda não há avaliações

- Ementários Redes de ComputadoresDocumento52 páginasEmentários Redes de ComputadoresClaudio ForlanAinda não há avaliações

- 3 - Conceitos Básicos de SO Hardware e Software Concorrência (Modo de Compatibilidade)Documento25 páginas3 - Conceitos Básicos de SO Hardware e Software Concorrência (Modo de Compatibilidade)AndersonsuzukiAinda não há avaliações

- Introdução A Ciencia Da ComputaçãoDocumento3 páginasIntrodução A Ciencia Da Computaçãoscrib32Ainda não há avaliações

- Revisao Informática Básica - Modulo IDocumento59 páginasRevisao Informática Básica - Modulo IAlandey0% (1)

- Montagem-Manutenção-Computadores-GUIA - APRENDIZAGEM - 1 - 2Documento3 páginasMontagem-Manutenção-Computadores-GUIA - APRENDIZAGEM - 1 - 2Lanylldo araujoAinda não há avaliações

- Trabalho Algoritimos - Juliane Monteiro - MULTIVIXDocumento16 páginasTrabalho Algoritimos - Juliane Monteiro - MULTIVIXJuliane MonteiroAinda não há avaliações

- Arquitetura de Computadores - Unidade I PDFDocumento33 páginasArquitetura de Computadores - Unidade I PDFFábio AdrianoAinda não há avaliações

- Slides ExemploDocumento28 páginasSlides ExemploAugusto PedroAinda não há avaliações

- Informática BásicaDocumento56 páginasInformática BásicalaurahiungAinda não há avaliações

- Aula 1Documento2 páginasAula 1André BertoniAinda não há avaliações

- IccDocumento34 páginasIccDIonatanAinda não há avaliações

- Plano de Ensino Sistemas OperacionaisDocumento3 páginasPlano de Ensino Sistemas OperacionaisDiógenes Vaz de MeloAinda não há avaliações

- Organização de Computadores - ConteudoDocumento109 páginasOrganização de Computadores - Conteudoremotoc77Ainda não há avaliações

- Organizacao e Arquitetura de ComputadoresDocumento3 páginasOrganizacao e Arquitetura de ComputadoresPaulo AmparoAinda não há avaliações

- Plano de Ensino - 2023-1 - Programação Estruturada v1-3Documento3 páginasPlano de Ensino - 2023-1 - Programação Estruturada v1-3João LinharesAinda não há avaliações

- Modulo 4 - Componente Do Comp.Documento46 páginasModulo 4 - Componente Do Comp.Eduar AndrighettiAinda não há avaliações

- Aula 1Documento53 páginasAula 1Jeferson FerreiraAinda não há avaliações

- Apostila Sistemas Operacionais I Parte1Documento18 páginasApostila Sistemas Operacionais I Parte1Patrick MenezesAinda não há avaliações

- Aula01 IntroducaoDocumento18 páginasAula01 IntroducaokejaroAinda não há avaliações

- Trabalho de Aquitetura de ComputadoresDocumento17 páginasTrabalho de Aquitetura de ComputadoresManoel FilhoAinda não há avaliações

- Componentes de HardwareDocumento17 páginasComponentes de HardwareTulani C. da SilvaAinda não há avaliações

- Arquitetura de ComputadoresDocumento14 páginasArquitetura de ComputadoresNelsonAinda não há avaliações

- Sistemas Operacionais - A Arte de Passar em Concursos PúblicosDocumento111 páginasSistemas Operacionais - A Arte de Passar em Concursos PúblicosRoberto AraujoAinda não há avaliações

- Conceitos de Hardware e Software: Arquitetura de Computadores e Sistemas Operacionais Felipe RotermelDocumento44 páginasConceitos de Hardware e Software: Arquitetura de Computadores e Sistemas Operacionais Felipe RotermelAmanda SanttosAinda não há avaliações

- Organização de Computadores-1Documento130 páginasOrganização de Computadores-1Lucilio Carvalho0% (1)

- Sistemas OperacionaisDocumento3 páginasSistemas OperacionaisHallisom DouglasAinda não há avaliações

- Unidade 01 - Arquiteturas ParalelasDocumento14 páginasUnidade 01 - Arquiteturas Paralelasjulio carvalhoAinda não há avaliações

- Microprocess AdoresDocumento59 páginasMicroprocess AdoresRicardo GomesAinda não há avaliações

- IntroducaoDocumento249 páginasIntroducaoLucas CambuimAinda não há avaliações

- 1 Arquitetura de ComputadoresDocumento43 páginas1 Arquitetura de ComputadoresRogério FernandesAinda não há avaliações

- Ficha de ExerciciosDocumento4 páginasFicha de ExerciciosStélio ZacariasAinda não há avaliações

- Aula 2 - Novas Tendencias Da Arquitetura de ComputadoresDocumento29 páginasAula 2 - Novas Tendencias Da Arquitetura de ComputadoresStélio Zacarias100% (1)

- Rancho KubDocumento22 páginasRancho KubStélio ZacariasAinda não há avaliações

- Receitas MozDocumento6 páginasReceitas MozStélio ZacariasAinda não há avaliações

- Lista de Compras de Supermercado para Casal Com FilhosDocumento6 páginasLista de Compras de Supermercado para Casal Com FilhosStélio Zacarias100% (1)

- Frances 10 11 12 PDFDocumento122 páginasFrances 10 11 12 PDFStélio ZacariasAinda não há avaliações

- 1P Organizacao e Arquitetura de ComputadoresDocumento2 páginas1P Organizacao e Arquitetura de ComputadoresStélio ZacariasAinda não há avaliações

- SO de Redes - Active Directory 2Documento13 páginasSO de Redes - Active Directory 2Stélio ZacariasAinda não há avaliações

- Aula SoDocumento43 páginasAula SoStélio ZacariasAinda não há avaliações

- Plano Ensino INF119 UDocumento4 páginasPlano Ensino INF119 UStélio ZacariasAinda não há avaliações

- POSCOMP2011 Comentarios Joseana OACDocumento9 páginasPOSCOMP2011 Comentarios Joseana OACStélio ZacariasAinda não há avaliações

- Sistemas Operacionais - Erico Meneses LeãoDocumento128 páginasSistemas Operacionais - Erico Meneses LeãoCleusa GranattoAinda não há avaliações

- 2012ME MateusOrtigosaCunha PDFDocumento145 páginas2012ME MateusOrtigosaCunha PDFFelippe Matias RochaAinda não há avaliações

- SoDocumento14 páginasSoOliver RobustoAinda não há avaliações

- SoDocumento14 páginasSoOliver RobustoAinda não há avaliações

- Aula8 Zabbix InstalacaoDocumento20 páginasAula8 Zabbix InstalacaoStélio ZacariasAinda não há avaliações

- Org Arq Comp PDFDocumento116 páginasOrg Arq Comp PDFMarcelloAugustoAinda não há avaliações

- Abobadilha PDFDocumento2 páginasAbobadilha PDFStélio ZacariasAinda não há avaliações

- Arqt de Comp - Aula1 - IntroducaoDocumento86 páginasArqt de Comp - Aula1 - IntroducaoStélio ZacariasAinda não há avaliações

- Pavimentos GeralDocumento1 páginaPavimentos GeralStélio ZacariasAinda não há avaliações

- 02opcomput 131022233410 Phpapp01Documento32 páginas02opcomput 131022233410 Phpapp01Stélio ZacariasAinda não há avaliações

- Abo Bad IlhaDocumento2 páginasAbo Bad IlhaStélio ZacariasAinda não há avaliações

- Catalogo Sep Gorduras P.R.F.V.Documento1 páginaCatalogo Sep Gorduras P.R.F.V.Stélio ZacariasAinda não há avaliações

- Compacto Fossa FiltroDocumento1 páginaCompacto Fossa FiltroStélio ZacariasAinda não há avaliações

- Catalogo Sep Gorduras InoxDocumento1 páginaCatalogo Sep Gorduras InoxStélio ZacariasAinda não há avaliações

- Catalogo Sep Gorduras PEADDocumento1 páginaCatalogo Sep Gorduras PEADStélio ZacariasAinda não há avaliações

- Compacto Fossa FiltroDocumento1 páginaCompacto Fossa FiltroStélio ZacariasAinda não há avaliações

- Fossa Biologica Modular PEADDocumento1 páginaFossa Biologica Modular PEADStélio ZacariasAinda não há avaliações

- IntroducaociscoDocumento17 páginasIntroducaociscoJairson MonteiroAinda não há avaliações

- Apostila DelphiDocumento79 páginasApostila DelphiJoao AlvesAinda não há avaliações

- Formas de PropagaçãoDocumento12 páginasFormas de Propagaçãomx_zbAinda não há avaliações

- Normalizacao de Banco de DadosDocumento7 páginasNormalizacao de Banco de DadosAndré RibeiroAinda não há avaliações

- PC Host MultiusuarioDocumento14 páginasPC Host Multiusuarioxxxvirt100% (30)

- Instalando Banco de Dados SQL Server - SKF @ptitudeDocumento22 páginasInstalando Banco de Dados SQL Server - SKF @ptitudeAnderson V. VianaAinda não há avaliações

- Migrando Dados Do Paradox para SGBDsDocumento2 páginasMigrando Dados Do Paradox para SGBDsismaelvaleAinda não há avaliações

- Banco de Dados - 5° SlideDocumento17 páginasBanco de Dados - 5° Slideapi-3813652Ainda não há avaliações

- Esquema Do Gravador PicDocumento6 páginasEsquema Do Gravador Picdenilson.rodr1357Ainda não há avaliações

- Apostila LazarusDocumento21 páginasApostila LazarusrichardsenaAinda não há avaliações

- Aprenda A Programar - PythonBrasilDocumento46 páginasAprenda A Programar - PythonBrasilsoterobra100% (1)

- 1122 Prodmução de Kit Cesta BásicaDocumento13 páginas1122 Prodmução de Kit Cesta BásicaJaasiel Neres Maiane BritoAinda não há avaliações

- Apostila 1 PDFDocumento242 páginasApostila 1 PDFthiagovt2Ainda não há avaliações

- Apostila Ipd - Introdução Ao Processamento de DadosDocumento0 páginaApostila Ipd - Introdução Ao Processamento de DadosJessica OliveiraAinda não há avaliações

- Habilitando Aplicações Delphi para A Web em 10 MinutesDocumento1 páginaHabilitando Aplicações Delphi para A Web em 10 MinutesRonaldo Leandro SepedesAinda não há avaliações

- Tutorial BatchDocumento9 páginasTutorial Batch19912101Ainda não há avaliações

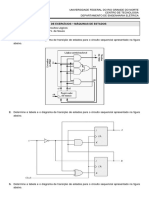

- Lista de Exercícios - Máquinas de EstadoDocumento4 páginasLista de Exercícios - Máquinas de EstadoThiago AbrantesAinda não há avaliações

- Pre Projeto AutomaçãoDocumento12 páginasPre Projeto AutomaçãoWans MacêdoAinda não há avaliações

- Sistemas Operacionais - ExercíciosDocumento2 páginasSistemas Operacionais - ExercíciosDiana Santos100% (3)

- 04 Construtores This Sobrecarga EncapsulamentoDocumento16 páginas04 Construtores This Sobrecarga EncapsulamentoIgnacio Andres Perez VergaraAinda não há avaliações

- A Metodologia de Projeto de Redes de ComputadoresDocumento3 páginasA Metodologia de Projeto de Redes de Computadoresricardo17754Ainda não há avaliações

- Noções de CriptografiaDocumento13 páginasNoções de CriptografiawcardosoAinda não há avaliações

- Apol 2 Microprocessadores e Microcontroladores - MicrocontrolaDocumento3 páginasApol 2 Microprocessadores e Microcontroladores - MicrocontrolaRobson Luiz0% (1)

- Elipse SCADA v2.29 Build095 Scad A Tutorial BRDocumento145 páginasElipse SCADA v2.29 Build095 Scad A Tutorial BRNicole Beatriz Portilla Constain100% (1)

- Revisão AvaliaçãoDocumento4 páginasRevisão AvaliaçãoCaio Henrique ClementeAinda não há avaliações

- Chamada Remota de Procedimento (RPC)Documento14 páginasChamada Remota de Procedimento (RPC)Amade Baptista MaiquitaAinda não há avaliações

- Metas de Um Sistema DistribuídoDocumento40 páginasMetas de Um Sistema DistribuídoCleuton Jorge100% (1)