Escolar Documentos

Profissional Documentos

Cultura Documentos

Somadores Binarios

Somadores Binarios

Enviado por

Carlos MartinsTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Somadores Binarios

Somadores Binarios

Enviado por

Carlos MartinsDireitos autorais:

Formatos disponíveis

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

Somadores Binários

E.T.M./2005 (revisão)

RESUMO

Esta experiência tem por objetivo a familiarização com somadores binários, notadamente os paralelos,

que realizam a soma simultânea de todos os bits de dois números binários. A parte experimental inclui o

projeto de uma calculadora simples que executa as operações de soma e subtração, utilizando o circuito

integrado 74283 (somador de 4 bits).

1. INTRODUÇÃO TEÓRICA

1.1 Meio Somador e Somador Completo

Sejam dois números binários X e Y, de n bits, que somados geram o número S como resultado:

X= Xn-1 Xn-2 ... X2 X1 X0

Y= Yn-1 Yn-2 ... Y2 Y1 Y0

S= Van-1 Sn-1 Van-2 Sn-2 Va2 S2 Va1 S1 Va0 S0

onde: Vai é o “vai um” do i-ésimo (ou bit de carry).

Por exemplo, para n = 4, a soma “2 + 6” resulta:

X= 0 0 1 0

Y= 0 1 1 0

S= 0 1 1 0 0

vai um

Podemos observar que o resultado final (0100) não é correto, pois os bits foram somados isoladamente

(em particular, o bit de “vai-um” gerado em X1 + Y1 não foi “incorporado” à soma de X2 + Y2). A tabela

verdade para a geração dos bits da soma é ilustrado na Tabela I.

Tabela I - Tabela Verdade do Meio Somador.

Xi Yi Si Vai

0 0 0 0 Si = Xi ⊕ Yi (1)

0 1 1 0

1 0 1 0 Vai = Xi Yi (2)

1 1 0 1

O circuito que implementa as equações acima é chamado meio somador, e pode ser construído com uma

porta EXCLUSIVE OR e uma porta AND (figura 1).

Ai

•

Si

Bi •

Va

i

Figura 1 – Meio Somador.

Somadores Binários (2005) 1

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

Esse circuito, porém, aplica-se apenas à soma de dois bits Xi e Yi isoladamente. Para efetuar-se somas

completas, levando-se em consideração os demais bits que constituem os números X e Y, cada um dos

bits “vai um” Vai deverá ser somado aos dígitos mais significativos Xi+1 e Yi+1.

No exemplo da soma “2 + 6”, teremos, portanto:

1 1

X= 0 0 1 0

Y= 0 1 1 0

S= 1 1 0 1 0 0

É comum denominar-se o “vai-um” gerado pela soma de Xi e Yi por “vem-um” (Vei+1), a ser

acrescentado à soma Xi+1+Yi+1. Portanto a tabela verdade para a geração dos bits de uma soma completa

é ilustrada na Tabela II abaixo.

Tabela II - Tabela Verdade do Somador Completo.

Xi Yi Vei Si Vai

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0 Si = Xi ⊕ Yi ⊕ Vei (3)

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1 Vai = Xi Yi + Vei (Xi ⊕ Yi) (4)

1 1 0 0 1

1 1 1 1 1

O circuito que implementa um somador completo está na figura 2.

Ve + ( Xi + Yi )

Ve i

Si

i Meio

Xi + Yi Ve ( X i + Yi )

Somador i

Xi Meio

X i Yi Va

Yi Somador i

Figura 2 - Somador Completo.

1.2. Somador com Propagação de “vai-um”

O somador com propagação de “vai-um”, também chamado de ripple carry adder, é construído ligando-

se em cascata vários circuitos de “soma completa” (SC). A figura 3 mostra o diagrama em blocos de um

somador binário de 4 bits implementado com essa técnica.

X3 Y 3 X2 Y2 X1 Y1 X0 Y0

Ve

SC SC SC SC

Va S3 S2 S1 S0

Figura 3 - Somador com Propagação de “vai-um” de 4 bits.

Somadores Binários (2005) 2

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

A vantagem deste tipo de somador é a simplicidade e a modularidade do circuito; sua desvantagem,

porém, é ser muito lento: seu atraso é aproximadamente igual à soma dos atrasos das saídas “vai-um”

dos circuitos de soma completa.

1.3. Somador com “vai-um” Antecipado

Também conhecido como carry lookahead adder, é um somador que tem um circuito que prevê o “vai-

um”, para cada bit da soma, eliminando-se o atraso de propagação de “vai-um” a partir do primeiro bit.

Tomando-se a equação (4) que expressa a geração do bit “vai-um”, e fazendo:

Gi = Xi Yi e Ti =Xi ⊕ Yi

temos:

Vai = Gi + Ti Vei

onde:

• Gi é o “gerador de “vai-um”, pois, se Gi = 1, certamente existe “vai-um” saindo do estágio i;

• Ti é o “transporte de vai-um”, pois, se Ti = 1, existe um “vai-um” saindo do estágio i se

houver “vem-um” do estágio anterior.

• Vei = Vai-1

Portanto, para um somador de 4 bits, tem-se:

S0 = X0 ⊕ Y0 ⊕ Ve

Va0 = G0 + T0 Ve, onde: G0 = X0 Y0 e T0 = ⊕ Y0

S1 = X1 ⊕ Y1 ⊕ Va0

Va1 = G1 + T1 Va0, onde: G1 = X1 Y1 e T1 = X1 ⊕ Y1

S2 = X2 ⊕ Y2 ⊕ Va1

Va2 = G2 + T2 Va1, onde: G2 = X2 Y2 e T2 = X2 ⊕ Y2

S3 = X3 ⊕ Y3 ⊕ Va2

Va = Va3 = G3 + T3 Va2, onde: G3 = X3 Y3 e T3 = X3 ⊕ Y3

Substituindo-se os valores de Vai, tem-se então:

S0 = X0 ⊕ Y0 ⊕ Ve

S1 = X1 ⊕ Y1 ⊕ (G0 + T0 Ve)

S2 = X2 ⊕ Y2 ⊕ (G1 + T1 G0 + T1 T0 Ve)

S3 = X3 ⊕ Y3 ⊕ (G2 + T2 G1 + T2 T1 G0 + T2 T1 T0 Ve)

Va = G3 + T3 G2 + T3 T2 G1 + T3 T2 T1 G0 + T3 T2 T1 T0 Ve)

A figura 4 mostra o somador de 4 bits com “vai-um” antecipado.

Somadores Binários (2005) 3

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

X3

• G3

•

• Va

• •

T3

Y3 • •

• •

X2

• G2

• •

•

•

S3

• X3

•

T2 • Y3

Y2 • •

• • •

X1

• G1

• •

•

S2

T1 • X2

Y1 • Y2

• •

X0 •

• G0

• •

S1

• X1

T0

Y0 • Y1

•

Ve • S0

X0

Y0

Figura 4 - Somador de 4 bits com “vai-um” antecipado.

Pode-se ver que o atraso deste tipo de somador é muito menor que os somadores com propagação de

“vai-um”, pois qualquer saída tem um atraso de no máximo 4 níveis de portas. O circuito, porém, é muito

mais complexo, e a expansão da largura das palavras a serem somadas torna-se mais difícil, pois quanto

maior a capacidade em bits, maior será o número de entradas das portas.

Para se simplificar a expansão da capacidade em bits do somador, é muito comum associarem-se em

cascata vários somadores com “vai-um” antecipado, de menor capacidade em bits. Por exemplo, para se

fazer um somador de 12 bits, ligam-se, em cascata, 3 somadores de 4 bits, como mostra a figura 5.

X 11 X 8 Y 11 Y 8 X7 X4 Y7 Y4 X3 X0 Y3 Y0

SOMADOR SOMADOR SOMADOR

Va Ve

S 11 S 8 S7 S4 S3 S0

Figura 5 - Somador de 12 bits com somadores de 4 bits com “vai-um” antecipado.

Somadores Binários (2005) 4

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

1.4. Subtração de Números Binários

Assim como circuitos combinatórios simples foram utilizados para montar meios somadores e somadores

completos, é possível construir meios subtratores e subtratores completos, a partir das tabelas verdade

(Tabelas III e IV), que realizam a operação D = X – Y (onde X → minuendo, Y → subtraendo),

observando-se que, no caso, Eei é o empréstimo de entrada e Esi é o empréstimo de saída.

Tabela III - Tabela Verdade do Meio Subtrator.

Xi Yi Di Esi

0 0 0 0

0 1 1 1

1 0 1 0

1 1 0 0

Tabela IV - Tabela Verdade do Subtrador Completo.

Xi Yi Eei D Esi

0 0 0 0 0

0 0 1 1 1

0 1 0 1 1

0 1 1 0 1

1 0 0 1 0

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

Analogamente aos somadores completos, pode-se ligar diversos subtradores em cascata para efetuar a

operação de subtração entre dois números, em paralelo.

Na prática, porém, considerando que a operação D = X – Y pode ser vista como uma soma do número X

com o complemento do número Y, isto é, D = X + (-Y), utilizam-se também circuitos somadores nas

operações de subtração.

1.5. Soma / Subtração Usando Complemento de Um

Em operações de soma ou subtração de operandos representados em complemento de um, sempre que

houver um “vai-um”, este deve ser adicionado ao resultado.

Exemplos:

4 - 6 = -2 7 - 3 = 4

0 1 0 0 0 1 1 1

1 0 0 1 1 1 0 0

resultado final 1 1 0 1 0 0 1 1

(não há “vai-um”) 1 1 “vai-um”

0 1 0 0 resultado final

A figura 6 mostra um circuito de soma/subtração com a realimentação do “vai-um”.

Somadores Binários (2005) 5

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

X Y ou Y'

4 4

"vai-um" "vem-um"

Figura 6 - Circuito de Soma/Subtração em Complemento de Um.

1.6. Soma/Subtração usando Complemento de Dois

Sabe-se, que numa operação aritmética em complemento de dois, não se corrige o resultado como no

caso do complemento de um. É necessário, porém, somar-se 1 ao complemento bit a bit do número:

(Complemento de 2) = (Complemento de 1) + 1.

Numa subtração, portanto, costuma-se “forçar” um “vem-um” na coluna de bits menos significativos dos

operandos.

Exemplos:

7 - 3 = 4 4 - 6 = -2

1 “vem-um” forçado 1 “vem-um” forçado

0 1 1 1 7 0 1 0 0 4

1 1 0 0 -3 (complemento de 1) 1 0 0 1 -6 (complemento de 1)

0 1 0 0 4 1 1 1 0 -2 (complemento de 2)

Numa soma de números positivos ou negativos a complementação não é necessária e, portanto não há

“vem-um” forçado.

Exemplo:

-2 - 3 = -5

1 1 1 0 -2 (complemento de 2)

1 1 0 1 -3 (complemento de 2)

1 0 1 1 -5 (complemento de 2)

A figura 7 mostra um circuito de soma/subtração em complemento de 2.

X Y ou Y'

4 4

SUBTR = 1

Figura 7 - Circuito de Soma / Subtração em Complemento de 2.

Somadores Binários (2005) 6

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

1.7. Circuitos Integrados de Somadores Completos

Diversos circuitos integrados implementa a função de somadores completos. O CI mais comum é o

somador paralelo de 4 bits, que contém quatro somadores completos e um circuito de antecipação de

“vai-um”. Os circuitos integrados mais comuns são o 7483A e o 74283. Ambos os circuitos são

funcionalmente idênticos, e a única diferença entre eles é a numeração dos pinos. A figura 8 ilustra um

esquema funcional do 74283.

B3 B2 B1 B0 A3 A2 A1 A0

somador paralelo de 4 bits

C4 C0

74283

Σ3 Σ2 Σ1 Σ0

Figura 8 – Somador paralelo 74283.

2. PARTE EXPERIMENTAL

Na parte prática desta experiência utiliza-se extensamente o circuito integrado 74283 para projetar um

somador/subtrador. Examine, portanto, com antecedência, o funcionamento dessa pastilha.

a) Faça o projeto detalhado do circuito somador/subtrador:

Na figura 2.1, ao ser acionado o botão EXECUTE o resultado deverá aparecer no display. O circuito

que realiza o complemento de um deverá complementar o dado de entrada quando em operação de

subtração (X–Y). A complementação dos bits de entrada das chaves pode ser efetuada usando portas

tipo OU EXCLUSIVO.

Chaves

"1" CHAVE = 0 Soma

CHAVE = 1 Subtr. Circuito

Complemento

de um

"0"

4

Y Y X X

3 0 3 0

"vem um"

Somador

(CHAVE)

"vai um"

(LED)

4

EXECUTE

Registrador

(Botão)

LIMPA

(Botão) •

4

Display

Figura 2.1 - Somador / Subtrador em Complemento 2.

Somadores Binários (2005) 7

EPUSP — PCS 2011/2305/2355 — Laboratório Digital

b) Efetue a montagem do circuito.

c) Verifique o funcionamento do circuito. Observe, também, a ocorrência de resultados inválidos. Caso

existam, em que condições eles ocorrem?

Perguntas

Responda as seguintes perguntas com relação à experiência.

1) Explique como funciona o circuito de complemento dos bits de entrada.

2) Qual é a melhor seqüência de montagem do circuito, de forma a garantir uma montagem e

teste modular?

3) O que acontece quando o resultado da operação ultrapassa os limites dos números válidos

para a representação em complemento de dois com 4 bits?

4) Como o circuito projetado poderia ser modificado para poder apresentar resultados com

5 bits?

3. BIBLIOGRAFIA

• FREGNI, Edson e SARAIVA, Antonio M. Engenharia do Projeto Lógico Digital: Conceitos e

Prática. Editora Edgard Blücher Ltda, 1995.

• MANO, M. M.; KIME, C. R. Logic and Computer Design Fundamentals. 3rd ed., Prentice-Hall,

2004.

• TOCCI, R. J.; WIDMER, N. S.; MOSS, G. L. Digital Systems: principles and applications. 9th ed.,

Prentice-Hall, 2004.

• WAKERLY, John F. Digital Design Principles & Practices. 3rd edition, Prentice Hall, 2000.

• Fairchild Semiconductor. TTL Data Book. Mountain View, California, 1978.

4. MATERIAL DISPONÍVEL

• Circuitos Integrados TTL:

7400, 7402, 7404, 7410, 7420, 7450, 7474, 7486, 74157, 74175, 74283.

5. EQUIPAMENTOS NECESSÁRIOS

• 1 painel de montagens experimentais.

• 1 fonte de alimentação fixa, 5V ± 5%, 4A.

• 1 osciloscópio digital.

• 1 multímetro digital.

• 1 gerador de pulsos.

Somadores Binários (2005) 8

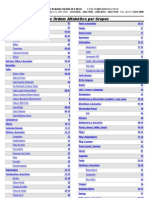

Você também pode gostar

- Ventilador VLP 4000 P - Vent-Logos PDFDocumento16 páginasVentilador VLP 4000 P - Vent-Logos PDFBruno100% (2)

- Pit 78362 00 PDFDocumento3 páginasPit 78362 00 PDFRafael Canto100% (3)

- Manual Aquecedor Bosch 25l GWH 520 23 25lDocumento24 páginasManual Aquecedor Bosch 25l GWH 520 23 25lFelipe LellisAinda não há avaliações

- PGS-002580 - Anexo 4 - Check List Seguran+â-ºa para Nada Consta - Rev - 00Documento2 páginasPGS-002580 - Anexo 4 - Check List Seguran+â-ºa para Nada Consta - Rev - 00Claudete vianaAinda não há avaliações

- Cat A Logo 102Documento60 páginasCat A Logo 102Gilson AlvesAinda não há avaliações

- Inspeção em Serviços de Desaeradores PDFDocumento6 páginasInspeção em Serviços de Desaeradores PDFrogeriogalianoAinda não há avaliações

- Elemaq1 Aula03 PDFDocumento46 páginasElemaq1 Aula03 PDFRezende JulioAinda não há avaliações

- APTA-APTitude Nº 63Documento16 páginasAPTA-APTitude Nº 63coasilva+scribd2303Ainda não há avaliações

- NOVO RENAULT CAPTUR TCe 120 NA "AUTO FOCO"Documento5 páginasNOVO RENAULT CAPTUR TCe 120 NA "AUTO FOCO"Grupo Renault PortugalAinda não há avaliações

- Choque Eletrico PDFDocumento10 páginasChoque Eletrico PDFTatty AlmeidaAinda não há avaliações

- Elevadores PDFDocumento15 páginasElevadores PDFRoberto Fernandes BarrosAinda não há avaliações

- Volume 3Documento100 páginasVolume 3João BritoAinda não há avaliações

- Aula de Ergonomia - Tipos de ErgonomiaDocumento63 páginasAula de Ergonomia - Tipos de ErgonomiaLuciano Nascimento100% (1)

- Prova de Sistemas PneumáticosDocumento3 páginasProva de Sistemas PneumáticosDanilo SilvaAinda não há avaliações

- 01 Integridade ApostilaDocumento30 páginas01 Integridade ApostilaMyguel ZorrerAinda não há avaliações

- Zoneamento Ecol Gico Econ Mico Do Tocantins Diagn Stico Meio NaturalDocumento522 páginasZoneamento Ecol Gico Econ Mico Do Tocantins Diagn Stico Meio NaturalRAIZ CLIENTESAinda não há avaliações

- Manual Sik-2500 Autolimpante Versão 12-13Documento21 páginasManual Sik-2500 Autolimpante Versão 12-13placoveAinda não há avaliações

- GaxetasDocumento5 páginasGaxetasrcejrAinda não há avaliações

- DS PH U60naDocumento1 páginaDS PH U60naMarco PederziniAinda não há avaliações

- Dimensionamento de Vigas ContínuasDocumento18 páginasDimensionamento de Vigas ContínuasVinicius Franco SilvaAinda não há avaliações

- Lista 1Documento3 páginasLista 1Raquel CamposAinda não há avaliações

- PT Mecan CompletoDocumento14 páginasPT Mecan CompletoJohnAinda não há avaliações

- Exercicio Aula 03Documento19 páginasExercicio Aula 03SYO LOBINHOAinda não há avaliações

- Apostila de Salvamento Terrestre OficialDocumento64 páginasApostila de Salvamento Terrestre OficialGustavo Daniel100% (1)

- Introdução À Construção de GUI - Tutorial Do NetBeans IDEDocumento6 páginasIntrodução À Construção de GUI - Tutorial Do NetBeans IDECarlos ManoelAinda não há avaliações

- Manometros-Usos - Conceito PDFDocumento10 páginasManometros-Usos - Conceito PDFExata MetrologiaAinda não há avaliações

- Tratamento de Efluentes de Curtume Através DoDocumento279 páginasTratamento de Efluentes de Curtume Através DoRenally CavalcantiAinda não há avaliações

- Efeito DopplerDocumento6 páginasEfeito DopplerKyvia LimaAinda não há avaliações

- Inf 245 Catlogo Geral 2021Documento324 páginasInf 245 Catlogo Geral 2021kra99Ainda não há avaliações

- LISTA5 ONDAS Sonoras CompletaDocumento19 páginasLISTA5 ONDAS Sonoras CompletaAna Carina Estevam TenórioAinda não há avaliações