Escolar Documentos

Profissional Documentos

Cultura Documentos

Risc Cisc

Risc Cisc

Enviado por

Ronnypetson Souza da SilvaTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Risc Cisc

Risc Cisc

Enviado por

Ronnypetson Souza da SilvaDireitos autorais:

Formatos disponíveis

Comparao entre as arquitecturas de

processadores RISC e CISC

Lus Filipe Silva

1

, Vtor Jos Marques Antunes

2

1

Email: ee91163@fe.up.pt

2

Email: ee95070@fe.up.pt

Faculdade de Engenharia da Universidade do Porto

Sumrio: Este documento visa ilustrar a relao

histrica e tcnica entre as arquitecturas de

processadores RISC (Redudec Instruction Set

Computer) e CISC (Complex Instruction Set Computer)

ao longo do tempo, cobrindo o debate entre as mesmas

pelo domnio do mercado desde o seu nascimento at

actualidade. Iremos especificar as arquitecturas,

procedendo sua comparao para chegarmos a

concluses que podem no ser as esperadas, pois cada

vez mais o importante o desempenho a qualquer

preo. Conclu-se que a diferena entre processadores

RISC e CISC j no reside no tamanho nem no tipo do

conjunto de instrues, mas sim na arquitectura em si, e

as nomenclaturas RISC e CISC j no descrevem a

realidade das arquitecturas actuais.

1. Introduo

Talvez a abordagem mais comum para a comparao

entre RISC e CISC seja a de listar as caractersticas de

ambas e coloc-las lado-a-lado para comparao,

discutindo o modo como cada caracterstica ajuda ou

no o desempenho. Esta abordagem correcta se

estivermos a comparar duas peas de tecnologia

contemporneas, como os sistemas operativos, placas de

vdeo, CPUs especficos, etc., mas ela falha quando

aplicada ao nosso debate. Falha porque RISC e CISC

no so exactamente tecnologias, so antes estratgias

de projecto de CPUs abordagens para atingir um

certo nmero de objectivos definidos em relao a um

certo conjunto de problemas. Ou, para ser um pouco

mais abstracto, poderamos chamar-lhes filosofias de

projecto de CPUs, ou maneiras de pensar acerca de um

determinado conjunto de problemas e das suas solues.

importante olhar para estas duas estratgias como

tendo evoludo a partir de um conjunto de condies

tecnolgicas que existiram num dado momento. Cada

uma delas foi uma abordagem ao projecto de mquinas

que os projectistas sentiram ser a mais eficiente no uso

dos recursos tecnolgicos existentes na poca. Na

formulao e aplicao destas estratgias, os projectistas

tomaram em considerao as limitaes da tecnologia

da altura limitaes essas que no so exactamente as

mesmas de hoje. Compreender estas limitaes e a

forma como os projectistas trabalharam com elas a

chave para perceber os dois tipos de arquitectura. Assim

sendo, uma comparao entre as arquitecturas RISC e

CISC requer mais do que apenas uma listagem das

caractersticas, benchmarks, etc. de cada uma requer

um contexto histrico.

Para entender o contexto histrico e tecnolgico de onde

evoluram as arquitecturas RISC e CISC necessrio,

em primeiro lugar, entender o estado das coisas em

relao a VLSI, memria/armazenamento e

compiladores nos anos 70 e inicio dos anos 80. Estas

trs tecnologias definiram o ambiente tecnolgico no

qual os projectistas e investigadores trabalharam para

construir as mquinas mais rpidas.

Memria e armazenamento

difcil subestimar os efeitos que a tecnologia de

armazenamento tinha no projecto de um CPU nos anos

70. Nessa altura, os computadores usavam memria de

cariz magntico para armazenar o cdigo dos

programas, memria que era, no s, cara como tambm

bastante lenta. Depois da introduo da RAM as coisas

melhoraram em termos de velocidade, no entanto o seu

preo era ainda proibitivo. Apenas a ttulo ilustrativo,

em finais dos anos 70, 1 MB de memria RAM podia

custar centenas de contos. Em meados dos anos 90, essa

mesma quantidade de memria custaria apenas poucos

(1-2) milhares de escudos [1]. Adicionado ao preo da

memria, o armazenamento secundrio era caro e lento,

por isso, colocar grandes volumes de cdigo na

memria desde o armazenamento secundrio era, por si

s, um grande impedimento ao desempenho.

O grande custo da memria e a lentido do

armazenamento secundrio conspiraram para fazer

com que a escrita de cdigo fosse um assunto muito

srio. O bom cdigo era o compacto j que era

necessrio coloc-lo todo num pequeno espao de

memria. Como a memria constitua uma parte

significativa do preo total do sistema, uma reduo no

tamanho do cdigo era traduzida directamente numa

reduo do custo total do sistema.

Compiladores

O trabalho de um compilador era relativamente simples

nesta altura: traduzir cdigo escrito numa linguagem de

alto nvel, como C ou Pascal, em assembly. O assembly

era depois convertido para cdigo mquina por um

assemblador. A compilao demorava bastante tempo e

o resultado dificilmente se poderia dizer ptimo. O

melhor que se poderia esperar era que a traduo da

linguagem de alto nvel para o assembly fosse correcta.

Se realmente se quisesse cdigo compacto e optimizado,

a nica soluo era programar em assembly.

VLSI

Em termos de VLSI (Very Large Scale Integration) a

tecnologia da altura apenas permitia densidades de

transstores que seriam muito baixas quando

comparadas com os standards de hoje. Era

simplesmente impossvel colocar muitas

funcionalidades num nico chip. No incio dos anos 80,

quando se comeou a desenvolver a arquitectura RISC,

um milho de transstores num nico chip era j

bastante [2]. Devido falta de recursos (transstores) as

mquinas CISC da altura tinham as suas unidades

funcionais espalhadas por vrios chips. Isto era um

problema por causa do alto tempo de espera nas

transferncias de dados entre os mesmos, o que desde

logo era um bice ao desempenho. Uma implementao

num nico chip seria o ideal.

2. CISC

No inicio dos anos 70, quer porque os compiladores

eram muito pobres e pouco robustos, quer porque a

memria era lenta e cara causando srias limitaes no

tamanho do cdigo, levou a que uma certa corrente

previsse uma crise no software. O hardware era cada

vez mais barato e o software cada vez mais caro. Um

grande nmero de investigadores e projectistas

defendiam que a nica maneira de contornar os grandes

problemas que se avizinhavam era mudar a

complexidade do (cada vez mais caro) software e

transport-la para o (cada vez mais barato) hardware.

Se houvesse uma funo mais comum, que o

programador tivesse de escrever vezes sem conta num

programa, porque no implementar essa funo em

hardware? Afinal de contas o hardware era barato e o

tempo do programador no. Esta ideia de mover o fardo

da complexidade do software para o hardware foi a

ideia impulsionadora por trs da filosofia CISC, e quase

tudo o que um verdadeiro CISC faz tem este objectivo.

Alguns investigadores sugeriram que uma maneira de

tornar o trabalho dos programadores mais fcil seria

fazer com que o cdigo assembly se parecesse mais com

o cdigo das linguagens de alto nvel (C ou Pascal).

Os mais extremistas falavam j de uma arquitectura de

computao baseada numa linguagem de alto nvel. Este

tipo de arquitectura era CISC levado ao extremo. A sua

motivao primria era reduzir o custo global do

sistema fazendo computadores para os quais fosse mais

fcil de programar. Ao simplificar o trabalho dos

programadores, pensava-se que os custos seriam

mantidos num nvel razovel.

Aqui est uma listagem das principais razes para se

promover este tipo de arquitectura [3]:

Reduzir as dificuldades de escrita de compiladores;

Reduzir o custo global do sistema;

Reduzir os custos de desenvolvimento de software;

Reduzir drasticamente o software do sistema;

Reduzir a diferena semntica entre linguagens de

programao e mquina;

Fazer com que os programas escritos em linguagens

de alto nvel corressem mais eficientemente;

Melhorar a compactao do cdigo;

Facilitar a deteco e correco de erros.

Sumariando, se uma instruo complexa escrita numa

linguagem de alto nvel fosse traduzida em,

exactamente, uma instruo assembly, ento:

Os compiladores seriam mais fceis de escrever.

Isto pouparia tempo e esforo para os

programadores, reduzindo, assim, os custos de

desenvolvimento de software;

O cdigo seria mais compacto, o que permitiria

poupar em memria, reduzindo o custo global do

hardware do sistema;

Seria mais fcil fazer a deteco e correco de

erros o que, de novo, permitiria baixar os custos de

desenvolvimento de software e de manuteno.

At este momento, centramos a ateno nas vantagens

econmicas da arquitectura CISC, ignorando a questo

do desempenho. A abordagem utilizada neste tipo de

arquitectura para melhorar o desempenho das mquinas

CISC foi, conforme j foi referido, transferir a

complexidade do software para o hardware. Para

melhor se compreender como que este tipo de

abordagem afecta o desempenho vamos analisar um

pouco a seguinte equao a equao do desempenho

de um processador uma mtrica vulgarmente utilizada

para avaliar o desempenho de um sistema de

computao:

1

]

1

,

_

,

_

,

_

Ciclo

Tempo

Instruo

Ciclos

Programa

Instrues

Programa

Tempo

Melhorar o desempenho significa reduzir o termo

esquerda do sinal de igual (=), porque quanto menor for

o tempo que um programa demora a ser executado,

melhor ser o desempenho do sistema. As mquina

CISC tentam atingir este objectivo reduzindo o primeiro

termo direita do sinal de igual, isto , o nmero de

instrues por programa. Os investigadores pensaram

que ao reduzir o nmero de instrues que a mquina

executa para completar uma determinada tarefa, poder-

se-ia reduzir o tempo que ela necessita para completar

essa mesma tarefa, aumentando, assim, o seu

desempenho.

Assim, ao reduzir o tamanho dos programas

conseguiam-se dois propsitos: por um lado era

necessria uma menor quantidade de memria para

armazenar o cdigo; e por outro o tempo de execuo

era, tambm, diminudo pois havia menos linhas de

cdigo para executar.

Alm de implementar todo o tipo de instrues que

faziam um variado nmero de tarefas como copiar

strings ou converter valores para BCD entre muitas

outras, havia outra tctica que os projectistas utilizavam

para reduzir o tamanho do cdigo e a sua complexidade:

os modos de endereamento complexos.

Vejamos o seguinte exemplo, meramente ilustrativo, da

multiplicao de dois nmeros armazenados em

memria:

A figura seguinte ilustra um esquema de

armazenamento para um computador genrico. Se

quisssemos multiplicar dois nmeros, teramos

primeiro que carregar cada um dos operandos de uma

localizao na memria para um dos registos.

Figura 1. Esquema de armazenamento para um

computador genrico.

Uma vez carregados nos registos, os operandos

poderiam ser multiplicados pela unidade de execuo

(ALU Aritmetric Logic Unit). Utilizaramos as

seguintes linhas de cdigo para multiplicar o contedo

das posies de memria [2:3] e [5:2] e armazenar o

resultado na posio [2:3]:

MOV [A, 2:3]

MOV [B, 5:2]

MUL [A, B]

MOV [2:3, A]

Este exemplo de cdigo explicita os passos que tm de

ser dados pelo processador para multiplicar os

contedos de duas posies de memria. H que

carregar os dois registos com o contedo da memria

principal, multiplicar os dois nmeros e guardar o

resultado de novo na memria principal. Se quisssemos

tornar o assembly menos complicado e mais compacto,

poderamos modificar a arquitectura por forma a

realizar a operao descrita com uma instruo apenas.

Para atingir esse objectivo, a instruo MUL teria que

ser alterada por forma a aceitar como parmetros duas

posies de memria:

MUL [2:3, 5:2]

Evoluir de quatro instrues para apenas uma uma

grande poupana. Apesar de a nova arquitectura ainda

ter que carregar o contedo das duas posies de

memria para os registos, multiplic-los e voltar a

armazenar na memria o resultado no h como

contornar isso todas essas operaes de baixo nvel

so feitas em hardware e so invisveis para o

programador. Este um exemplo de endereamento

complexo. Uma instruo assembly, na realidade leva a

cabo uma srie complexa de operaes. Uma vez mais,

isto um exemplo da filosofia CISC de transferir a

complexidade do software para o hardware.

Outra das caractersticas das mquinas CISC era a

utilizao de micro-cdigo. A micro-programao era

mesmo uma das caractersticas primordiais que permitia

aos projectistas a implementao de instrues

complexas em hardware [4]. Para melhor compreender

o que a micro-programao, vamos considerar,

sumariamente, a sua alternativa: a execuo directa.

Usando execuo directa, a mquina carrega a instruo

da memria, descodifica-a e envia-a para a unidade de

execuo. Esta unidade de execuo pega na instruo

sua entrada e activa alguns circuitos que levam a cabo

a tarefa. Se, por exemplo, a mquina carrega a instruo

de ADD com operadores em vrgula flutuante e a

fornece unidade de execuo, existe, algures, um

circuito que a carrega e direcciona as unidades de

execuo para garantir que todas as operaes de

deslocamento, adio e normalizao so executadas

correctamente. A execuo directa , na realidade, o que

se poderia esperar que acontecesse dentro de um

computador se no o houvesse conhecimento do micro-

cdigo.

A principal vantagem da execuo directa que ela

rpida. No existe qualquer tipo de abstraco ou

traduo extras; a mquina apenas descodifica e executa

as instrues em hardware. O seu maior problema que

pode ocupar algum espao. De facto, se todas as

instrues tm que ter um circuito que as execute, ento

quanto maior for o nmero de instrues, maior vai ser

o espao ocupado pela unidade de execuo. Por isso,

executar directamente as instrues no era uma boa

abordagem para o projecto de uma mquina CISC. At

porque os recursos (transstores) disponveis na altura

eram bastante escassos.

Chegamos assim micro-programao. Com a micro-

programao, quase como termos um mini-

processador dentro do processador. A unidade de

execuo um processador de microcdigo que executa

micro-instrues. Os projectistas usam estas micro-

instrues para escrever micro-programas que so

armazenados numa memria de controlo especial.

Quando uma instruo normal de um programa

carregada da memria, descodificada e entregue ao

processador de micro-cdigo, este ltimo executa a

subrotina de micro-cdigo adequada. Esta subrotina

diz s vrias unidades funcionais o que fazer e como

fazer.

No incio, o micro-cdigo era lento. Mas ainda assim, a

ROM utilizada para a memria de controlo era cerca de

10 vezes mais rpida que a memria magntica da

altura, por isso o processador de micro-cdigo ainda

conseguia estar suficientemente avanado para

oferecer um desempenho razovel [4].

Com a evoluo da tecnologia, o micro-cdigo estava

cada vez mais rpido os processadores de micro-

cdigo nos processadores modernos conseguem

velocidades da ordem dos 95% em relao execuo

directa. Como o micro-cdigo era cada vez melhor,

fazia cada vez mais sentido transferir funcionalidades

do software para o hardware. Assim, os conjuntos de

instrues cresceram rapidamente e o nmero mdio de

instrues por programa decresceu.

Contudo, medida que os microprogramas cresceram

para fazer face ao crescente nmero de instrues,

alguns problemas comearam a surgir. Para manter um

bom desempenho, o micro-cdigo tinha que ser

altamente optimizado, eficiente e bastante compacto

para que os custos de memria no comeassem a

crescer desmesuradamente. Como os micro-programas

eram, agora, to grandes, era bastante mais difcil test-

los e detectar e corrigir erros. Como resultado, o micro-

cdigo includo nas mquinas que vinham para o

mercado tinha, por vezes, erros e tinha que ser corrigido

inmeras vezes no terreno. Foram estas dificuldades de

implementao do micro-cdigo que levaram a que os

investigadores questionassem se a implementao de

todas estas instrues complexas e elaboradas em

micro-cdigo seria, realmente, o melhor caminho para

fazer uso dos limitados recursos (transstores) existentes

[4].

3. RISC

Como j foi referido, muitas das implementaes da

arquitectura CISC eram to complexas que eram

distribudas por vrios chips. Esta situao no era, por

razes bvias, ideal. Era necessrio uma soluo num

nico chip, uma soluo que fizesse melhor uso dos

escassos recurso disponibilizados (transstores). No

entanto, para que todo um processador coubesse num s

chip, algumas das suas funcionalidades teriam que ser

deixadas de fora. Nesse intuito, realizaram-se estudos

destinados a descobrir que tipos de situaes ocorrem

mais frequentemente na execuo de aplicaes. A ideia

era descobrir em que tipo de tarefas o processador

passava mais tempo e optimizar essas mesmas tarefas.

Se tivessem que ser feitos compromissos, estes deviam

ser feitos em favor da velocidade de execuo das

tarefas nas quais o processador passa mais tempo a

trabalhar, ainda que isso pudesse atrasar outras tarefas

no to frequentes.

Esta abordagem quantitativa, de fazer mais rpidas as

tarefas mais comuns, provocou a inverso da filosofia

iniciada pelos CISC e a complexidade teve que ser

retirada do hardware e ser passada para o software. A

memria estava a ficar mais barata e os compiladores

eram cada vez mais eficientes, por isso muitas das

razes que conduziram os projectistas a complicar o

conjunto de instrues deixaram de existir. Os

investigadores diziam que o suporte para as linguagens

de alto nvel poderia ser mais eficiente se fosse

implementada em software, gastar recursos

(transstores) preciosos para suportar as linguagens de

alto nvel em hardware era um desperdcio. Esses

recursos poderiam ser utilizados noutras tecnologias

para melhorar o desempenho.

Quando os investigadores tiveram que decidir quais as

funcionalidades que teriam que ser retiradas, o suporte

para o micro-cdigo foi o primeiro a sair, e com ele

saram tambm um grupo de instrues complexas que,

alegadamente, tornava o trabalho dos compiladores e

dos programadores mais fcil. A ideia era que quase

ningum utilizava aquelas instrues to complexas. Os

programadores ao escreverem compiladores, com

certeza que no as utilizavam pois estas eram difceis de

implementar. Ao compilar o cdigo, os compiladores

preteriam este tipo de instrues em favor da gerao de

um conjunto de instrues mais simples que realizassem

a mesma tarefa.

O que os investigadores concluram dos estudos

realizados foi que um pequeno conjunto de instrues

estava a fazer a maioria do trabalho. Aquelas instrues

que raramente eram usadas poderiam ser eliminadas

sem que houvesse perda de qualquer funcionalidade.

Esta ideia da reduo do conjunto de instrues,

deixando de for a todas as instrues que no fossem

absolutamente necessrias, substituindo as instrues

mais complexas por conjuntos de instrues mais

simples, foi o que esteve na origem do termo Reduced

Instruction Set Computer. Ao incluir apenas um

pequeno e criteriosamente escolhido grupo de instrues

numa mquina, poder-se-ia deixar de fora o suporte do

micro-cdigo e passar a usar a execuo directa.

No s o nmero de instrues foi reduzido, mas

tambm o tamanho das mesmas. Foi decidido que todas

as instrues RISC deveriam, sempre que possvel,

demorar apenas um ciclo de relgio a terminar a sua

execuo. A razo por trs desta deciso foi baseada em

algumas observaes feitas pelos investigadores. Em

primeiro lugar, aperceberam-se que tudo o que poderia

ser feito usando as instrues de micro-cdigo, tambm

poderia ser feito com pequenas e rpidas instrues de

assembly. A memria que estava a ser usada para

armazenar o micro-cdigo, poderia simplesmente ser

usada para armazenar o assembler, assim a necessidade

de micro-cdigo seria pura e simplesmente eliminada.

por esta razo que muitas das instrues de uma

mquina RISC correspondem a micro-instrues numa

mquina CISC [4].

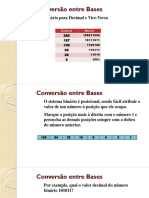

De seguida apresentada uma tabela ilustrativa das

diferenas que caracterizaram os primeiros

processadores das arquitecturas RISC e CISC ao longo

do tempo relativamente ao numero de instrues e a sua

relao com o tamanho do micro-cdigo e o tamanho

das instrues:

CISC RISC

IBM370 VAX

11/780

8086 SPARC I MIPS I

1973 1973 1978 1981 1983

208 303 100 39 55

54Kb 400Kb 11Kb 0 0

Ano

N Instr.

Microc.

Instr.

(bytes)

2-6 2-57 1-17 4 4

Tabela 1 . diferenas que caracterizaram os primeiros

processadores das arquitecturas RISC e CISC

A segunda razo que levou a que o formato fosse

uniformizado e demorasse apenas um ciclo de relgio

foi a observao de que a implementao do pipelining

s realmente vivel se no tiver que lidar com

instrues de diferentes graus de complexidade. Como o

pipelining permite a execuo de vrias instrues em

paralelo, uma mquina que o suporte consegue reduzir

drasticamente o nmero mdio de ciclos por instruo

(CPI Cycles Per Instruction). Baixar o nmero mdio

de ciclos que as instrues necessitam para terminar a

sua execuo uma maneira muito efectiva de baixar o

tempo total que necessrio execuo de um

programa.

Relembre-mos, de novo a equao do desempenho. Os

projectistas deste tipo de arquitectura tentaram reduzir o

tempo por programa reduzindo o segundo termo

direita do sinal de igual (ciclos/instruo), permitindo

que o primeiro termo (instrues/programa) aumentasse

ligeiramente. Pensava-se que uma reduo no nmero

de ciclos por instruo, alcanada custa da reduo do

conjunto de instrues, a introduo da tcnica de

pipelining e outras funcionalidades (das quais j

falaremos) compensariam largamente o aumento do

nmero de instrues por programa. Acabou por se

verificar que esta filosofia estava correcta.

Alm da tcnica de pipelining, houve duas inovaes

importantes que permitiram o decrscimo do nmero de

ciclos por instruo mantendo o aumento do tamanho do

cdigo num nvel mnimo: a eliminao dos modos de

endereamento complexos e o aumento do nmero de

registos internos do processador. Nas arquitecturas

RISC existem apenas operaes registo-registo e apenas

as instrues LOAD e STORE podem aceder

memria. Poder-se-ia pensar que o uso de LOADs e

STOREs em vez de uma nica instruo que operasse

na memria iria aumentar o nmero de instrues de tal

modo que o espao necessrio em memria e o

desempenho do sistema viriam afectados. Como

posteriormente se verificou, existem algumas razes que

fazem com que este pensamento no seja correcto.

Verificou-se que mais de 80% dos operandos que

apareciam num programa eram variveis escalares

locais [2]. Significa isto que, se fossem adicionados

mltiplos bancos de registos arquitectura, estas

variveis locais poderiam ficar armazenadas nos

registos, evitando ter que ir memria de todas as vezes

que fosse necessria alguma delas. Assim, sempre que

uma subrotina chamada, todas as variveis locais so

carregadas para um banco de registos, sendo a

mantidas conforme as necessidades.

Esta separao das instrues LOAD e STORE de todas

as outras, permite ao compilador programar uma

operao imediatamente a seguir ao LOAD (por

exemplo). Assim, enquanto o processador espera alguns

ciclos para os dados serem carregados para o(s)

registo(s), pode executar outra tarefa, em vez de ficar

parado espera. Algumas mquinas CISC tambm

tiram partido desta demora nos acessos memria mas

esta funcionalidade tem que ser implementada em

micro-cdigo.

Como se pode ver da discusso acima, o papel do

compilador no controlo dos acessos memria

bastante diferente nas mquinas RISC em relao s

mquinas CISC. Na arquitectura RISC, o papel do

compilador muito mais proeminente. O sucesso deste

tipo de arquitectura depende fortemente da

inteligncia e nvel de optimizao dos compiladores

que se aproveitam da maior responsabilidade que lhes

concedida para poderem debitar cdigo mais

optimizado. Este acto de transferir o fardo da

optimizao do cdigo do hardware para o compilador

foi um dos mais importantes avanos da arquitectura

RISC. Como o hardware era, agora, mais simples, isto

significava que o software tinha que absorver alguma da

complexidade examinando agressivamente o cdigo e

fazendo um uso prudente do pequeno conjunto de

instrues e grande nmero de registos tpicos desta

arquitectura. Assim, as mquinas RISC dedicavam os

seus limitados recursos (transstores) a providenciar um

ambiente em que o cdigo poderia ser executado to

depressa quanto o possvel, confiando no compilador

para fazer o cdigo compacto e optimizado.

Este tipo de arquitectura caracterizado, a este nvel,

por ter um nmero bastante grande, por comparao

com as mquinas CISC, de registos de uso geral.

4. RISC vs CISC

Vamos agora tecer uma breve considerao acerca do

estado actual dos trs parmetros que definiram o

ambiente tecnolgico do qual partiu estudo em questo:

Armazenamento e memria

A memria, hoje em dia, rpida e barata; qualquer

pessoa que tenha instalado recentemente um programa

da Microsoft sabe que muitas das companhias que

desenvolvem software j no tm em considerao as

limitaes de memria. Assim, as preocupaes com o

tamanho do cdigo que deram origem ao vasto conjunto

de instrues da arquitectura CISC j no existem. De

facto, os processadores da era ps-RISC tm conjuntos

de instrues cada vez maiores de um tamanho e

diversidade sem precedentes, e ningum pensa duas

vezes no efeito que isso provoca no uso da memria.

Compiladores

O desenvolvimento dos compiladores sofreu um

tremendo avano nos ltimos anos. De facto, chegou a

um ponto tal que a prxima gerao de arquitecturas

(como o IA-64 ou Merced da Intel) dependem apenas

do compilador para ordenar as instrues tendo em vista

a mxima taxa de instrues executadas.

Os compiladores RISC tentam manter os operandos em

registos por forma a poderem usar simples instrues

registo-registo. Os compiladores tradicionais, por outro

lado, tentam descobrir o modo de endereamento ideal e

o menor formato de instruo para fazerem os acessos

memria. Em geral, os programadores de compiladores

RISC preferem o modelo de execuo registo-registo de

forma que os compiladores possam manter os operandos

que vo ser reutilizados em registos, em vez de

repetirem os acessos memria de cada vez que

necessrio um operando. Usam, por isso, LOADs e

STOREs para aceder memria para que os operandos

no sejam, implicitamente, rejeitados aps terminada a

execuo de uma determinada instruo, como acontece

nas arquitecturas que utilizam um modelo de execuo

memria-memria.

VLSI

O nmero de transstores que cabem numa placa de

silcio extremamente elevado e com tendncia a

crescer ainda mais. O problema agora j no a falta de

espao para armazenar as funcionalidades necessrias,

mas o que fazer com todos os transstores

disponibilizados. Retirar s arquitecturas as

funcionalidades que s raramente so utilizadas j no

uma estratgia moderna de projecto de processadores.

De facto, os projectistas procuram afincadamente mais

funcionalidades para integrarem nos seus processadores

para fazerem uso dos vastos recursos (transstores)

disponveis. Eles procuram no o que podem tirar, mas

o que podem incluir. A maioria das funcionalidades

ps-RISC so uma consequncia directa do aumento do

nmero de transstores disponveis e da estratgia

incluir se aumentar o desempenho.

Conjunto de Instrues

Uma instruo um comando codificado em 0s e 1s

que leva o processador a fazer algo. Quando um

programador escreve um programa em C, por exemplo,

o compilador traduz cada linha de cdigo C em uma ou

mais instrues do processador. Para que os

programadores possam (se quiserem) ver estas

instrues no tendo que lidar com 0s e 1s as

instrues so representadas por mnemnicas por

exemplo MOV, que copia um valor de uma localizao

para outra ou ADD, que adiciona dois valores. A

seguinte linha de cdigo adiciona dois valores (b e c) e

coloca o resultado em a:

a=b+c

Um compilador de C poderia traduzir isto na seguinte

sequncia de instrues:

mov ax, b

add ax, c

mov a, ax

A primeira instruo copia o contedo da localizao de

memria que contm o valor b para o registo ax do

processador (um registo uma localizao de

armazenamento dentro do processador que pode conter

uma certa quantidade de dados, normalmente 16 ou 32

bits. Sendo uma parte integrante do processador, os

acessos aos registos so muitssimo mais rpidos que os

acessos memria). A segunda instruo adiciona o

valor c ao contedo de ax e a terceira copia o resultado,

que est em ax, para a localizao onde a varivel a est

armazenada. Qualquer programa, por mais complexo

que seja, traduzido, em ltima anlise, em sries de

instrues do gnero da anterior.

Os programas de aplicao modernos contm,

frequentemente, centenas de milhar de linhas de cdigo.

Os sistemas operativos so ainda mais complexos: o

Microsoft Windows 95 contm cerca de 10 milhes de

linhas de cdigo, a maior parte dele escrito em C, e o

Windows NT tem mais de 5 milhes de linhas de cdigo

escritas em C e C++. Imagine-se o que seria ter de

traduzir 1 milho de linhas de cdigo C num conjunto

de instrues com uma a vinte ou trinta instrues por

linha de cdigo e fcil de perceber o porqu de o

software de hoje em dia ser to complicado e to

difcil de corrigir.

Quando um programa corre, o processador carrega as

instrues uma a uma e executa-as. Leva tempo a

carregar uma instruo e mais tempo ainda a

descodificar essa instruo para determinar o que

representam os 0s e 1s. E quando comea a execuo,

so necessrios um determinado nmero de ciclos de

relgio (daqui em diante apenas designados por ciclos)

para a completar. Um ciclo um batimento do

oscilador que alimenta o processador. Num 386 a 25

MHz um ciclo de relgio igual a 40 ns, num

PENTIUM a 120 MHz um ciclo igual a menos de 9

ns. Uma maneira de fazer com que um processador

corra o software mais rapidamente aumentar a

velocidade do relgio. Outra diminuir o nmero de

ciclos que uma instruo requer para completar a

execuo. Se tudo o resto fosse igual, um processador

que funcionasse a 100 MHz teria apenas metade do

desempenho de um outro que funcionasse a 50 MHz, se

o primeiro requeresse 4 ciclos de relgio por instruo e

o segundo apenas um ciclo.

Desde o incio da era dos microprocessadores, o grande

objectivo dos projectistas de chips desenvolver um

CPU que requeira apenas 1 ciclo de relgio por

instruo no apenas certas instrues, mas TODAS

as instrues. O objectivo original dos projectistas de

chips RISC era limitar o nmero de instrues

suportadas pelo chip de modo a que fosse possvel

alocar um nmero suficiente de transstores a cada uma

delas, para que a sua execuo precisasse apenas de um

ciclo de relgio para se completar.

Em vez de disponibilizar uma instruo MUL, por

exemplo, o projectista faria com que a instruo ADD

executasse em 1 ciclo de relgio. Ento o compilador

poderia fazer a multiplicao de a e b somando a a ele

prprio b vezes ou vice versa.

Um CPU CISC poderia multiplicar 10 e 5 da seguinte

forma:

mov ax, 10

mov bx, 5

mul bx

enquanto um CPU RISC faria o mesmo de outro modo:

mov ax, 0

mov bx, 10

mov cx, 5

begin:

add ax, bx

loop begin; loop cx vezes

claro que este apenas um exemplo ilustrativo, pois

os chips RISC actuais tm, de facto, instrues de

multiplicao.

Comparao de dois tipos de arquitecturas

comerciais

O que que faz do PowerPC um processador RISC e

do PENTIUM um processador CISC? Ironicamente, a

resposta no tem nada a haver com o tamanho do

conjunto de instrues.

Se repararmos nos manuais tcnicos dos dois

processadores vamos descobrir que os processadores

RISC de hoje oferecem um conjunto de instrues mais

rico e complexo do que os processadores CISC. Por

exemplo, o PowerPC 601 oferece um conjunto de

instrues mais alargado do que o PENTIUM, mesmo

assim o PowerPC considerado um processador RISC e

o PENTIUM no deixa de ser um processador CISC.

Hoje em dia os processadores de arquitectura RISC j

no apresentam as caractersticas que eram consideradas

como sendo exclusivamente tecnologia RISC, nos

primrdios do seu desenvolvimento (incio dos anos

70), ou seja o conjunto de instrues na realidade j no

reduzido como era antigamente, o que nos leva a

concluir que j no faz sentido este tipo de arquitectura

ser denominada RISC (Reduced instruction Set

Computer).

O que realmente distingue os processadores RISC dos

CISC actualmente, est relacionado com a arquitectura

em si e no tanto com o conjunto de instrues. Podem

ser encontrados alguns pontos chave que caracterizam

as diferenas entre um PowerPC e um PENTIUM, das

quais so referidas as seguintes[5]:

Os processadores RISC tm um maior nmero de

registos de uso geral. A melhor maneira de

escrever cdigo rpido maximizar o nmero de

operaes executadas directamente no processador

e minimizar o nmero de acessos aos dados

guardados na memria RAM. Um maior nmero

de registos de uso geral pode assim facilitar a

concretizao do objectivo atrs referido, pois os

acessos aos registos internos so praticamente

instantneos, enquanto que os acessos memria

RAM demoram algum tempo. Enquanto que um

processador PENTIUM apenas possu 8 registos

internos, o PowerPC tem 32.

Alm disso, os processadores RISC tm, tambm,

um nmero significativo de registos dedicados

apenas a operaes de vrgula flutuante.

As instrues que operam directamente na

memria requerem inmeros ciclos de relgio para

completarem a sua execuo. Este tipo de

instrues tm ainda uma implementao a nvel

de hardware que requisita um nmero

excessivamente elevado de transstores. Os

processadores RISC tm arquitecturas que

minimizam o nmero de instrues que

manipulam dados directamente na memria.

Realizam as operaes lgicas directamente nos

registos internos, e quando chegam ao valor final

este finalmente guardado na memria.

Uma das caractersticas do PowerPC ter

instrues de comprimento fixo, enquanto que no

PENTIUM podem variar desde 1 byte at 7 bytes,

ou mais caso o cdigo de 32 bits esteja a ser

executado num segmento de 16 bits. Os

projectistas das arquitecturas RISC preferem

projectar todas as instrues do mesmo

comprimento, pois simplificam assim a busca de

instrues e a lgica de descodificao das

mesmas, permitindo que uma instruo inteira

possa ser buscada com apenas um acesso

memria de 32 bits.

Os microprocessadores RISC apresentam uma

melhor performance a nvel de vrgula flutuante, o

que justifica a sua preferncia pela comunidade

cientfica. Esta preferncia advm da necessidade

de desempenho a nvel de vrgula flutuante exigida

por aplicaes de ndole cientfica, que fazem mais

clculos em vrgula flutuante do que aplicaes de

processamento de texto. S recentemente, no incio

dos anos 90, a Intel comeou a introduzir a

unidade de co-processamento matemtico interna

em alguns dos seus processadores da famlia 486.

S posteriormente, com a introduo no mercado

dos processadores PENTIUM que a unidade de

co-processamento matemtico comeou a fazer

parte de todos os processadores.

Em geral, os projectistas de arquitecturas RISC tiveram

em vista a adopo de tecnologias de ponta como

caches directamente integradas no processador,

pipelining das instrues e lgica de predio de modo a

obter processadores que conseguissem um melhor

desempenho. Mas a Intel incorporou as mesmas

tecnologias nos seus processadores, logo difcil

distinguir processadores RISC e CISC tendo como base

estas tecnologias.

Na tabela abaixo podem ser observadas as diferenas

entre os tcnicas de pipelining adoptadas pelos

projectistas de ambas as arquitecturas:

Pipelines para RISC e CISC

RISC CISC

Como possu mais

instrues ortogonais,

apresenta uma menor

variao da estrutura

pipeline.

Como possu instrues

mais variadas, apresenta

tambm uma pipeline com

uma estrutura mais

complexa.

A maior parte das

instrues RISC so

baseadas em operaes

nos registos internos.

As instrues podem

aceder os registos internos

ou a memria.

A descodificao das

instrues trivial.

A descodificao das

instrues pode demorar

mais do que um ciclo de

relgio.

Tabela 2

De qualquer modo ainda existem alguns processadores

RISC que se mantm prximos da linha original dos

processadores RISC, por exemplo os processadores

Alpha da Digital que combinam conjuntos de instrues

reduzidas com enormes caches internas e elevadas

velocidades de relgio.

Por outro lado fabricantes de processadores como a

AMD, Cyrix, e a NexGen ajudaram ainda mais fuso

das arquitecturas RISC e CISC incorporando nos seus

processadores clones dos PENTIUM tecnologias

adoptadas pelas arquitecturas RISC. Por exemplo o K6

da AMD apresenta um conjunto instrues todas do

mesmo comprimento, assim como o PENTIUM II da

Intel.

RISC & CISC, lado a lado

J deve ser aparente que os acrnimos RISC e

CISC apoiam o facto de que ambas as filosofias

arquitectnicas tm que ter em conta muito mais do que

simplesmente a complexidade ou simplicidade do

conjunto de instrues. Qualquer deciso que afecte o

custo ir afectar tambm o desempenho e vice versa. Na

tabela abaixo so sumariados os factos apresentados at

ao momento ajudando a entender o porqu das decises

tomadas pelos projectistas de processadores.

CISC RISC

Preo/Desempenho

Preo: mudana da

complexidade do software

para o hardware.

Desempenho: diminuio

do tamanho do cdigo, em

troca de um maior CPI

*

.

Preo: mudana da

complexidade do hardware

para o software.

Desempenho: diminuio

do tamanho do CPI

*

, em

troca de um maior

tamanho do cdigo.

Decises Arquitectnicas

Um grande e variado

conjunto de instrues

que inclu instrues

rpidas e simples para

executar tarefas

bsicas assim como

complexas e multi-

ciclo que

correspondem a

declaraes em

HLL

**

.

Suporte para HLL

**

feito em hardware.

Modos de

endereamento

memria-memria.

Uma unidade de

controlo em micro-

cdigo.

Gastar menos

Instrues simples e

de um s ciclo que

executam somente

funes bsicas.

Instrues em

assembly

correspondem a

instrues em micro-

cdigo numa

arquitectura CISC.

Todo o suporte HLL

**

feito em software.

Modos de

endereamento

simples permitem

somente que as

funes LOAD e

STORE acedam

memria. Todas as

operaes so do tipo

registo-registo.

transstores no fabrico

dos registos internos.

Unidade de controlo

de execuo directa.

Gastar mais

transstores em vrios

bancos de registos.

Uso de execuo em

pipeline para baixar

CPI

*

.

*

CPI Cycles Per Instruction

**

HLL High Level Language

Tabela 3 . Comparao entre as arquitecturas RISC e

CISC.

5. O FUTURO

A maior ameaa para as arquitecturas RISC e CISC

pode no ser nenhuma delas (por oposio outra), mas

uma nova arquitectura denominada EPIC (Explicit

Parallel Instruction Computer). Como se pode

depreender da palavra paralelo a arquitectura EPIC

pode executar vrias instrues em paralelo umas com

as outras. Esta filosofia foi criada pela Intel e , de certa

forma, a combinao das arquitecturas RISC e CISC.

A Intel e a Hewlet Packard esto a desenvolver um

processador usando esta filosofia sob o nome MERCED

(IA-64) e a Microsoft j est a desenvolver uma

plataforma (WIN64) para o mesmo. O processador

MERCED ser um processador de 64 bits.

Se esta arquitectura for bem sucedida poder tornar-se

na maior ameaa arquitectura RISC. Todas as grandes

marcas de fabricantes de processadores, exceptuando a

Sun e a Motorola, esto neste momento a comercializar

produtos baseados no x86 e alguns esto apenas

espera que o MERCED venha para o mercado. Por

causa do mercado dos x86, no provvel que a

arquitectura CISC desaparea num futuro prximo, mas

a arquitectura RISC poder vir a ser uma arquitectura

em extino. O futuro poder trazer-nos processadores

baseados na arquitectura EPIC bem como mais famlias

de processadores CISC, enquanto que os processadores

baseados em arquitecturas RISC podero tender a

desaparecer do mercado.

6. CONCLUSO

A diferena entre processadores RISC e CISC j no

reside no tamanho nem no tipo do conjunto de

instrues, mas sim na arquitectura em si.

As nomenclaturas RISC e CISC j no descrevem a

realidade das arquitecturas actuais. O que conta

actualmente a velocidade com que o processador

consegue executar as instrues que lhe so passadas e a

fiabilidade com que consegue correr o software.

Hoje em dia os fabricantes de processadores, sejam eles

RISC ou CISC, esto a utilizar todos os truques de

modo a melhorarem o desempenho e permitir algum

avano em relao aos seus concorrentes.

Ambas as arquitecturas tm sobrevivido no mercado por

razes diferentes, a arquitectura RISC pela sua

performance e a arquitectura CISC pela compatibilidade

de software.

O futuro poder no trazer a vitria a nenhum deles,

mas sim a sua provvel extino, j que a Intel, que

sempre foi a empresa lder no fabrico da arquitectura

x86 (arquitectura CISC), a vai abandonar em favor da

arquitectura RISC depois de ter assinado com a HP para

o projecto do Merced. A arquitectura EPIC pode ento

fazer com que as arquitecturas RISC e CISC se tornem

obsoletas.

Referncias:

[1] John L. Hennessy, David A. Patterson, Computer

Architecture: A Quantitative Approach, Second

Edition Morgan Kaufmann Publishers, 1996.

[2] David A. Patterson, Carlo H. Sequin, RISC I: A

Reduced Instruction Set VLSI Computer. 25 years of

the international symposia on Computer architecture

(selected papers), 1998.

[3] David R. Ditzel, David A. Patterson, Retrospective

on HLLCA. 25 years of the international symposia on

Computer architecture (selected papers), 1998.

[4] David A. Patterson, Reduced Instruction Set

Computers, Commun. ACM 28, Jan. 1985.

[5]Jeff Duntemann, Ron Pronk, Inside the PowerPC

Revolution, Coriolis Group, 1994.

Você também pode gostar

- Apostila C PICDocumento301 páginasApostila C PICFernando Luiz Do AmaralAinda não há avaliações

- Resumão LPI 101Documento17 páginasResumão LPI 101sonicgnulinuxAinda não há avaliações

- Arquitetura CISCDocumento10 páginasArquitetura CISCskolachado_roAinda não há avaliações

- ARES 8023 200 v1.1 - ManualDocumento30 páginasARES 8023 200 v1.1 - ManualBarbosa Fernando100% (1)

- CLP - SenaiDocumento81 páginasCLP - Senaiwaldir.eng807250% (2)

- Apostila de Programação de PICs em C e ProteusDocumento40 páginasApostila de Programação de PICs em C e ProteusAndreia Rocha Amorim100% (1)

- A Melhor Apostila Endereços Do S7 200Documento125 páginasA Melhor Apostila Endereços Do S7 200JoaoPauloTeixeiraAinda não há avaliações

- Arquitetura Do Microprocessador 8086Documento30 páginasArquitetura Do Microprocessador 8086EiderCassioAinda não há avaliações

- Apostila de Microcontroladores PIC e Perifericos (WWW - Mecatronicadegaragem.blogspot - Com)Documento276 páginasApostila de Microcontroladores PIC e Perifericos (WWW - Mecatronicadegaragem.blogspot - Com)Khelen Diogo NetoAinda não há avaliações

- Arquitetura Risc e CiscDocumento21 páginasArquitetura Risc e CiscFelipe da SilveiraAinda não há avaliações

- Emmerson Silva, Maquina Risc X Cisc.Documento19 páginasEmmerson Silva, Maquina Risc X Cisc.Emerson SilvaAinda não há avaliações

- Artigo Arquitetura Risc Cisc PDFDocumento3 páginasArtigo Arquitetura Risc Cisc PDFMarcelo Rovea Serres100% (1)

- Yury Rodrigues Shelkvosky - Comparativo RISC e CISCDocumento4 páginasYury Rodrigues Shelkvosky - Comparativo RISC e CISCYury ShelkovskyAinda não há avaliações

- O Que É e Qual A Diferenças Entre Risc e CiscDocumento2 páginasO Que É e Qual A Diferenças Entre Risc e CiscAdriano Vieira da SilvaAinda não há avaliações

- Arquitetura Dos ProcessadoresDocumento14 páginasArquitetura Dos ProcessadoresDhellano0% (1)

- Avaliao - Do - Aprendizado - 2022.1 - 2 - José Rodrigues Do Nascimento Neto PDFDocumento3 páginasAvaliao - Do - Aprendizado - 2022.1 - 2 - José Rodrigues Do Nascimento Neto PDFJOSE NETOAinda não há avaliações

- Arquitetura CISC e RISCDocumento27 páginasArquitetura CISC e RISCKeven PaivaAinda não há avaliações

- Tema 2Documento68 páginasTema 2Alexander PaesAinda não há avaliações

- Apostila Arquitetura Risc e Cisc. Noções BásicasDocumento4 páginasApostila Arquitetura Risc e Cisc. Noções BásicasAdr Silva0% (1)

- Arquiteturas Risc Cisc PDFDocumento23 páginasArquiteturas Risc Cisc PDFmaia_owneedAinda não há avaliações

- Lista de Exercicios IIDocumento2 páginasLista de Exercicios IIdouglas_cptAinda não há avaliações

- O Que É Arquitetura RISC e CISC e Suas Diferenças - Cap SistemaDocumento11 páginasO Que É Arquitetura RISC e CISC e Suas Diferenças - Cap SistemaCaillou PotterAinda não há avaliações

- Arquitetura Cisc e Risc Qual DiferençaDocumento9 páginasArquitetura Cisc e Risc Qual DiferençaAnderson RaposoAinda não há avaliações

- Aula III - Arquitectura de Computador PDFDocumento24 páginasAula III - Arquitectura de Computador PDFInvestir VidaAinda não há avaliações

- Arquitetura RISC e CISCDocumento13 páginasArquitetura RISC e CISCAgnaldo Ferreira100% (1)

- Questionário 10Documento5 páginasQuestionário 10Marcus RamosAinda não há avaliações

- RISC e CISC v2Documento8 páginasRISC e CISC v2Otniel PinheiroAinda não há avaliações

- Arquitetura RAMDocumento30 páginasArquitetura RAMMarco Túlio MarcelinoAinda não há avaliações

- Arquitetura - CISCDocumento10 páginasArquitetura - CISCWesley Henrique0% (1)

- Risc e CiscDocumento4 páginasRisc e CiscJanser Franca100% (1)

- Risc X CiscDocumento7 páginasRisc X CischeronmarroniAinda não há avaliações

- Trabalho de MICDocumento7 páginasTrabalho de MICOtniel PinheiroAinda não há avaliações

- Arquitetura e Organização de Computadores: Contextualização ContextualizaçãoDocumento12 páginasArquitetura e Organização de Computadores: Contextualização ContextualizaçãoFelipe BrufattoAinda não há avaliações

- Risc e CiscDocumento5 páginasRisc e CiscInformaAinda não há avaliações

- Apostila Informatica Industrial I - Parte 4Documento13 páginasApostila Informatica Industrial I - Parte 4Jomar GontijoAinda não há avaliações

- Informatica 2Documento9 páginasInformatica 2Theresa MotaAinda não há avaliações

- O QueDocumento11 páginasO QueSCRATCH MULTISERVICESAinda não há avaliações

- Arquitetura CISC X RISCDocumento23 páginasArquitetura CISC X RISCsamuel souzaAinda não há avaliações

- O Que É Arquitetura RISC e CISC e Suas Diferenças - Cap SistemaDocumento12 páginasO Que É Arquitetura RISC e CISC e Suas Diferenças - Cap SistemaJosé ManuelAinda não há avaliações

- Trabalho Imprimir.mDocumento15 páginasTrabalho Imprimir.mLeandro VyctorAinda não há avaliações

- Arquitetura de Computadores - Questionário 10Documento5 páginasArquitetura de Computadores - Questionário 10Marcus RamosAinda não há avaliações

- Arquitetura de Processadores Cisc e Risc (1) OriginalDocumento11 páginasArquitetura de Processadores Cisc e Risc (1) OriginalClary ManuelAinda não há avaliações

- As CISC e RISCDocumento43 páginasAs CISC e RISCLuiz GomesAinda não há avaliações

- Fundamentos FlynnDocumento31 páginasFundamentos FlynnSávio RobertoAinda não há avaliações

- Arquitetura CISC X RISCDocumento23 páginasArquitetura CISC X RISCLuis Ricardo SouzaAinda não há avaliações

- Risc e CiscDocumento17 páginasRisc e CiscMonique CorrêaAinda não há avaliações

- TRE Sistemas de Computação - Livro WikiDocumento23 páginasTRE Sistemas de Computação - Livro WikiEmerson Veiga VazAinda não há avaliações

- Arquitetura de Computadores Unidade I e II DPDocumento19 páginasArquitetura de Computadores Unidade I e II DPvictor cccAinda não há avaliações

- Apostila CPICDocumento267 páginasApostila CPICdanielzidoiAinda não há avaliações

- Projeto ConceitualDocumento14 páginasProjeto ConceitualLarissa MeirelesAinda não há avaliações

- Aula01 IntroducaoDocumento18 páginasAula01 IntroducaokejaroAinda não há avaliações

- Arquitetura de Computadores - AULA - Conjunto de Instrues e MIPS - NovoDocumento91 páginasArquitetura de Computadores - AULA - Conjunto de Instrues e MIPS - NovoLucas ValeAinda não há avaliações

- RISC e CISCDocumento7 páginasRISC e CISCElton MironaAinda não há avaliações

- Trabalho de Microprocessadores - Kiala MárioDocumento28 páginasTrabalho de Microprocessadores - Kiala MárioKiala MárioAinda não há avaliações

- MicroDocumento10 páginasMicroSCRATCH MULTISERVICESAinda não há avaliações

- Programando O Pic Usando O Flowcode Parte I - Baseado Na Versão 6 E Pic16f887No EverandProgramando O Pic Usando O Flowcode Parte I - Baseado Na Versão 6 E Pic16f887Ainda não há avaliações

- Projeto De Hardware Para Conversor Adc Com Mcp3550-e/sn E Desenho De Esquema E Layout No KicadNo EverandProjeto De Hardware Para Conversor Adc Com Mcp3550-e/sn E Desenho De Esquema E Layout No KicadAinda não há avaliações

- Tabela de Acessórios, Fonte, DC Jack, Cabo Flat, Cooler - BringIT 27.04Documento269 páginasTabela de Acessórios, Fonte, DC Jack, Cabo Flat, Cooler - BringIT 27.04Jeferson Maia BarretoAinda não há avaliações

- Tabela Intelbras Novembro 2016Documento75 páginasTabela Intelbras Novembro 2016Jeferson Maia BarretoAinda não há avaliações

- Manual PromedicaDocumento190 páginasManual PromedicaJeferson Maia Barreto0% (1)

- Manual Sansung Star Lite TVDocumento47 páginasManual Sansung Star Lite TVroberto_hengling13Ainda não há avaliações

- Manual Sansung Star Lite TVDocumento47 páginasManual Sansung Star Lite TVroberto_hengling13Ainda não há avaliações

- FireMonkey e FireDAC - Construindo Uma Aplicação Completa - Parte IIDocumento26 páginasFireMonkey e FireDAC - Construindo Uma Aplicação Completa - Parte IIemircalife8474Ainda não há avaliações

- Aula MIPS MonocicloDocumento45 páginasAula MIPS MonocicloDanilo PintoAinda não há avaliações

- ELV6 V2 (1)Documento6 páginasELV6 V2 (1)lordsocramAinda não há avaliações

- Datasheet Defense IA 21 12Documento14 páginasDatasheet Defense IA 21 12lucianomartinsdreisAinda não há avaliações

- Prova Presencial Arquitetura de Computadores (1)Documento13 páginasProva Presencial Arquitetura de Computadores (1)fernando carisAinda não há avaliações

- Sistemas OperacionaisDocumento148 páginasSistemas OperacionaisKauã OliveiraAinda não há avaliações

- Manual CDA5Documento18 páginasManual CDA5Luis Oliveira Soares BarbosaAinda não há avaliações

- Manual Casio Fx-82msDocumento41 páginasManual Casio Fx-82msSilvio GomesAinda não há avaliações

- Iniciação À Informática HW e SWDocumento20 páginasIniciação À Informática HW e SWRenatoNascimentoAinda não há avaliações

- SRW01 Manual Do Usuario V1.3xDocumento82 páginasSRW01 Manual Do Usuario V1.3xObsol EtoAinda não há avaliações

- Ebook Monitoramento OnlineDocumento27 páginasEbook Monitoramento OnlineBruna BalsanelliAinda não há avaliações

- Manual SFX 35Documento32 páginasManual SFX 35Cintia CamposAinda não há avaliações

- Manual Avell - B154Documento49 páginasManual Avell - B154makumbatorAinda não há avaliações

- Manual VEX I Especia REV. HV01.00BDocumento2 páginasManual VEX I Especia REV. HV01.00BVagner Roberto MachadoAinda não há avaliações

- Informatica 86Documento85 páginasInformatica 86ApenasAinda não há avaliações

- Principais Comandos MS-DOSDocumento4 páginasPrincipais Comandos MS-DOSLuis Alfredo G. Caldas NetoAinda não há avaliações

- (TUTORIAL) Norton Ghost 14 Passo A Passo (+fotosDocumento20 páginas(TUTORIAL) Norton Ghost 14 Passo A Passo (+fotosaSFD6143100% (1)

- UNIP - EaD PIM IIDocumento12 páginasUNIP - EaD PIM IIBruno MoraesAinda não há avaliações

- PDF - 2 Simulado - GMF - Pos Edital 16HDocumento24 páginasPDF - 2 Simulado - GMF - Pos Edital 16HVerônica SoaresAinda não há avaliações

- trs961 Annex9 Supp8Documento28 páginastrs961 Annex9 Supp8janainaAinda não há avaliações

- ApostilaDocumento26 páginasApostilaFree FireAinda não há avaliações

- Exercício 3 - RecoverDocumento5 páginasExercício 3 - RecoverAndre LuizAinda não há avaliações

- Manual-Fechadura Biotec Biometrica S-798 PDFDocumento24 páginasManual-Fechadura Biotec Biometrica S-798 PDFNino BrownAinda não há avaliações

- Ecosport Audio MP3 Original - Manual UsuarioDocumento86 páginasEcosport Audio MP3 Original - Manual Usuariornesi20% (5)

- 12 HardwareDocumento31 páginas12 Hardwarenoisdigital00Ainda não há avaliações