Escolar Documentos

Profissional Documentos

Cultura Documentos

Cap 03 Flip-Flops Exp 01 05 PDF

Enviado por

Cairo GonçalvesTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Cap 03 Flip-Flops Exp 01 05 PDF

Enviado por

Cairo GonçalvesDireitos autorais:

Formatos disponíveis

Captulo 3 Flip-Flops

CAPTULO 3

FLIP-FLOPS

INTRODUO

Os flip-flops so os componentes bsicos de vrios dispositivos, dentre os quais destacam-se as

memrias semicondutoras e os contadores.

Os flip-flops podem ser classificados em dois tipos principais:

a)

b)

Flip-Flops Sncronos ou com "clock"

Flip-Flops Assncronos ou sem "clock"

Os flip-flops sncronos exigem, para seu perfeito funcionamento, um pulso de gatilhamento

tambm chamado "clock", alm das entradas normais. Deste modo, nos flip-flops sncronos as

mudanas s ocorrero durante o pulso de sincronizao, ou clock. J nos flip-flops assncronos,

as transies ocorrem aps ter sido completadas mudanas nas entradas normais, sem haver a

necessidade de pulsos de sincronizao.

De acordo com o funcionamento de suas entradas existem diversos tipos de flip-flops, sendo os

mais comuns: S-R, T, D e JK, cujas caractersticas de funcionamento passamos a descrever.

FLIP-FLOP S-R

Este o mais simples dispositivo de memria, tambm chamado de "Flip-Flop Set Reset".

A figura 1 mostra o diagrama em blocos e a tabela verdade do flip-flop S-R.

Figura 1 - Flip-Flop S-R - a) Smbolo - b) Tabela de Funcionamento - c) Tabela Resumida

A leitura da tabela se faz do seguinte modo:

"-"

QT

QT+1

significa no deve ocorrer ou no interessa.

a sada Q existente no instante (T) de aplicao das entradas S e R.

a sada Q aps a aplicao das entradas S e R.

Da tabela da figura 1 pode-se observar que quando S = 1 e R = a sada Q vai para 1; quando

S = e R = 1, a sada Q vai para ; quando R = S = , Q mantm o estado anterior e quando

S = R = 1 a sada ser indeterminada.

Datapool Eletrnica

Captulo 3 Flip-Flops

O flip-flop em sua verso mais simples muitas vezes chamado de LATCH, e pode ser

implementado com gates NO-OU ou com gates NO-E, como mostra a figura 2.

Figura 2 - Flip-Flop S-R - a) Smbolo - b) Implementao com gates NO-OU c) Implementao com gates NO-E - d) Formas de onda

Como pode ser observado, os flip-flops vistos so assncronos, isto , so diretamente operados

pelas entradas S e R; porm, estes dispositivos podem ser implementados com uma linha de

sincronizao em clock. Na figura 3 mostrado este circuito.

Figura 3 - Flip-Flop S-R Sncrono - a) Smbolo - b) Implementao com gates NO-E - c)

Tabela de Funcionamento

Na tabela da figura 3c notar que quando o clock est em 1 o flip-flop funciona normalmente, e

quando est em no ocorre mudanas na sada.

A figura 4 mostra as formas de onda de funcionamento do flip-flop S-R sncrono.

Datapool Eletrnica

Captulo 3 Flip-Flops

Figura 4 - Formas de onda de funcionamento de um Flip-Flop S-R Sncrono

FLIP-FLOP T

O Flip-Flop T (Toggle) ou Complementar tem sua tabela de funcionamento mostrada na figura 5.

Figura 5 - Flip-Flop T - a) Smbolo - b) Tabela de Funcionamento - c) Tabela Resumida

O Flip-Flop T no disponvel comercialmente, podendo no entanto ser construdo a partir de

outros.

FLIP-FLOP D

O Flip-Flop D quase sempre gatilhvel (sncrono), isto , vem sempre associado com uma

entrada de clock, s vezes denominada ENABLE. A figura 6 mostra a sua tabela de

funcionamento.

Figura 6 - Flip-Flop D - a) Sada - b) Tabela de Funcionamento - c) Tabela Resumida

Datapool Eletrnica

Captulo 3 Flip-Flops

Da figura 6b vemos que a sada Q acompanha a entrada D, desde que o clock esteja em 1. Com

o clock em no h mudana de sada.

FLIP-FLOP JK

Este o mais verstil dos flip-flops, no possuindo condies de entradas invlidas (como o S-R

para S = R = 1).

Figura 7 - Flip-Flop J-K - a) Smbolo - b) Tabela de Funcionamento - c) Tabela Resumida

Com o flip-flop J-K podemos construir outros tipos de flip-flops, como mostra a figura 8.

Figura 8 - Uso do Flip-Flop J-K na construo de outros - a) Construo do FF S-R Construo do FF T - c) Construo do FF D

b)

TIPOS DE GATILHAMENTO DOS FLIP-FLOPS

Quanto ao tipo de gatilhamento, os flip-flops se dividem em:

1.

2.

Gatilhvel por nvel (Level-Triggered)

Gatilhvel por rampa (Edge-Triggered)

Os flip-flops gatilhveis por nvel executam uma ao se a linha de clock estiver no nvel 1 (ou

algumas vezes).

Deste modo, "em um dispositivo gatilhvel por nvel as entradas de dados no devem ser

mudadas, exceto aps o trmino do estado ativo do clock."

Os flip-flops gatilhveis por edge podem ser de 2 tipos:

1.

2.

Datapool Eletrnica

Edge Positivo

Edge Negativo

Captulo 3 Flip-Flops

Os gatilhveis por Edge Positivo fazem a transferncia de informao, da entrada para a sada,

na subida do pulso de clock (edge positivo).

Os gatilhveis por Edge Negativo fazem esta transferncia na descida do pulso de clock (edge

negativo).

A figura 9 mostra os tipos de Edge:

Figura 9 - Tipos de Edge - a) Edge Positivo no incio do clock "Leading Edge" - b) Edge

Positivo no fim do clock "Trailing Edge" - c) Edge Negativo no fim do clock "Trailing Edge"

- d) Edge Negativo no incio do clock "Leading Edge"

Pode-se estabelecer que:

"Basicamente um dispositivo gatilhvel por Edge pode ter seus dados de entrada

mudados em qualquer instante, exceto durante o Edge."

A figura 10 mostra as simbologias mais usuais da conexo do clock.

Figura 10 - Simbologias das conexes do clock

Datapool Eletrnica

Captulo 3 Flip-Flops

FLIP-FLOPS GATILHVEIS DO TIPO MESTRE-ESCRAVO

Estes flip-flops so classificados como gatilhveis por nvel.

Basicamente, estes dispositivos so compostos de dois flip-flops, sendo um chamado Mestre e o

outro chamado Escravo.

A fim de executar uma transferncia correta de informao, da entrada para a sada, este flip-flop

exige que o clock execute uma transio completa, isto , saia do nvel , v para o nvel 1,

permanea um certo tempo e volte para o nvel .

Deste modo, as entradas no devem mudar durante o ciclo de clock.

A figura 11 mostra um circuito e as fases de funcionamento do flip-flop Mestre-Escravo.

ESCRAVO

Figura 11 - Flip-Flop Mestre-Escravo : Fases do Gatilhamento e Circuito de um FF MestreEscravo SR

A figura 12 mostra as formas de onda do circuito mostrado na figura 11.

Datapool Eletrnica

Captulo 3 Flip-Flops

Figura 12 - Formas de onda do FF Mestre-Escravo SR

FLIP-FLOP MESTRE-ESCRAVO COM DATA LOCK-OUT

Este flip-flop difere do Mestre-Escravo normal apenas pelo fato dos dados serem guardados no

mestre no Edge positivo e transferidos para a sada no Edge negativo do pulso do clock. Deste

modo, neste flip-flop pode haver mudana nas entradas durante o nvel positivo do clock, pois a

informao da entrada j foi armazenada no mestre no edge positivo do clock.

A figura 13 mostra as formas de onda FF Mestre-Escravo normal e do FF Mestre-Escravo com

Data Lock-Out (74111).

Figura 13 - Formas de onda de comparao entre os Flip-Flops Mestre-Escravo Normal e

com Data Lock-Out

Datapool Eletrnica

Captulo 3 Flip-Flops

PARMETROS IMPORTANTES DOS FLIP-FLOPS

a)

TEMPO DE SETAMENTO -tSET-UP

Este o tempo mnimo que o sinal deve estar presente nas entradas, antes da ocorrncia do

pulso de gatilhamento. A figura 14 mostra tal fato:

Figura 14 - TSET-UP (tempo de setamento)

b)

TEMPO DE MANUTENO - tHOLD

Este o tempo que o sinal deve permanecer nas entradas aps a ocorrncia do pulso de

gatilhamento. A figura 15 mostra tal fato:

Figura 15 - THOLD (tempo de Manuteno)

c)

FREQNCIA MXIMA fmx

a maior freqncia dos pulsos de clock que pode ser aplicado ao dispositivo, mantendo um

chaveamento confivel.

OBJETIVO

Atravs da utilizao da placa de experincias ED03, sero observadas, experimentalmente,

algumas das caractersticas dos principais tipos de flip-flops .

MATERIAL NECESSRIO

Placa de experincias ED-03;

Mdulo Universal 2000.

PROCEDIMENTO

Todas as experincias relatadas neste captulo esto prontas na placa ED03. Para selecionar a

experincia a ser executada, deve-se colocar as chaves H, I e J nas seguintes posies:

Datapool Eletrnica

Captulo 3 Flip-Flops

Experincia

Chave H

Chave I

Chave J

1

2

3

4

5

Descrio

Flip-Flop JK Mestre-Escravo

Flip-Flop Tipo D

Flip-Flop Tipo D utilizando entradas

Preset e Clear

Observao do tSET-UP

Introduo de atraso na linha de clock

Figura 16 - Tabela de descrio das experincias

EXPERINCIA 1 : FLIP-FLOP JK MESTRE-ESCRAVO

A chave TTL/CMOS deve estar na posio TTL, caso contrrio a placa de

experincias poder ser danificada.

1.

2.

3.

4.

5.

6.

Desligar o Mdulo Universal 2000;

Colocar a chave TTL/CMOS na posio TTL;

Encaixar a placa de experincias ED03 no SLOT H do Mdulo Universal 2000;

Ligar o Mdulo Universal;

Colocar as chaves H, I e J na posio ;

O circuito a ser verificado ser o da figura 17:

+5V

2

A

16

ck

Preset

15

L0

74LS76

Clear

14

L1

+5V

Figura 17 - Flip-Flop JK Mestre-Escravo 74LS76

Datapool Eletrnica

Captulo 3 Flip-Flops

10

7. Completar a tabela da figura 18.

ENTRADAS

J

A

1

1

1

1

1

1

K

B

1

1

1

1

1

1

SADAS

Clock

C

Q

L

Q

L1

Figura 18 - Tabela de Funcionamento do flip-flop 74LS76

8. Concluso:

Nesta experincia, pode-se observar o funcionamento do flip-flop mestre escravo e

a necessidade da aplicao de um pulso completo de clock para que o

dispositivo atue corretamente.

EXPERINCIA 2 : FLIP-FLOP TIPO D

A chave TTL/CMOS deve estar na posio TTL, caso contrrio a placa de

experincias poder ser danificada.

1.

2.

3.

4.

5.

6.

Desligar o Mdulo Universal 2000;

Colocar a chave TTL/CMOS na posio TTL;

Encaixar a placa de experincias ED03 no SLOT H do Mdulo Universal 2000;

Ligar o Mdulo Universal;

Colocar as chaves H e I na posio e a chave J na posio 1;

O circuito a ser verificado ser o da figura 19:

Datapool Eletrnica

Captulo 3 Flip-Flops

11

+5V

4

A

Preset

ck

L0

74LS74

Clear

L1

+5V

Figura 19 - Flip-Flop D Edge Triggered 74LS74

7. Completar a tabela da figura 20.

ENTRADAS

D=

Clock 1

D=1

Clock 1

Clock = 1

D 1

1

Clock

C

1

1

1

1

1

1

1

1

SADAS

Q

L

Q

L1

Figura 20 - Tabela de Funcionamento do FF D 74LS74

8. Concluso:

Observar que a transferncia de informao da entrada D para a sada se faz na

subida do clock, e que as entradas podem mudar de estado durante a permanncia

do clock em 1 ou , sem alterao da sada.

Datapool Eletrnica

Captulo 3 Flip-Flops

EXPERINCIA 3 : FLIP-FLOP D UTILIZANDO ENTRADAS PRESET E CLEAR

A chave TTL/CMOS deve estar na posio TTL, caso contrrio a placa de

experincias poder ser danificada.

1.

2.

3.

4.

5.

6.

Desligar o Mdulo Universal 2000;

Colocar a chave TTL/CMOS na posio TTL;

Encaixar a placa de experincias ED03 no SLOT H do Mdulo Universal 2000;

Ligar o Mdulo Universal;

Colocar as chaves H e J na posio e a chave I na posio 1;

O circuito a ser verificado ser o da figura 21:

A

4

D

ck

Preset

L0

74LS74

Clear

L1

1

B

Figura 21 - Circuito para teste do Preset e do Clear

7. Completar a tabela da figura 22.

ENTRADAS

Atuao do Preset

Atuao do Clear

Atuao do Preset e

do Clear simultneos

SADAS

Preset

A

Clear

B

Clock

C

D

D

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Q

L

Q

L1

Figura 22 - Tabela de Funcionamento do Preset e do Clear

Datapool Eletrnica

12

Captulo 3 Flip-Flops

13

8. Concluso:

Pode ser notado, pela tabela de funcionamento, que um na linha do Preset faz a

sada Q ir para o nvel 1 ("preseta" a sada), e um na linha clear faz a sada Q ir

para ("limpa" a sada). Ainda, deve ser observado que as linhas Preset e Clear

tm prioridade sobre as outras linhas de entrada (no caso, sobre as linhas D e

clock). Pela informao das ltimas duas linhas da tabela, v-se que a atuao de

Preset e do Clear, simultaneamente, faz com que a sada Q e Q fiquem em nvel 1,

perdendo assim a caracterstica de serem complementares.

EXPERINCIA 4 : OBSERVAO DO tSET-UP

A chave TTL/CMOS deve estar na posio TTL, caso contrrio a placa de

experincias poder ser danificada.

1.

2.

3.

4.

5.

6.

Desligar o Mdulo Universal 2000;

Colocar a chave TTL/CMOS na posio TTL;

Encaixar a placa de experincias ED03 no SLOT H do Mdulo Universal 2000;

Ligar o Mdulo Universal;

Colocar a chave H na posio e as chaves I e J na posio 1;

O circuito a ser verificado ser o da figura 23:

+5V

4

2

ck

Preset

L0

74LS74

Clear

L1

1

B

Figura 23 - Circuito para teste do tSET-UP

7. Completar a tabela da figura 24:

Datapool Eletrnica

Captulo 3 Flip-Flops

ENTRADAS

D = ck

C

14

SADAS

Clear

B

1

1

Q

L

Q

L1

Figura 24 - Tabela de funcionamento do Circuito da Figura 23

8. Concluso:

Quando a chave C vai de para 1 a sada deveria mudar de para 1, pois a

entrada D est com 1 e houve um edge positivo no clock. Isto no ocorre devido ao

set-up-time, pois a informao nas linhas de entrada devem estar disponveis um

tempo antes do aparecimento do edge positivo do clock, tempo este chamado de

tSET-UP (setamento).

EXPERINCIA 5 : INTRODUO DE ATRASO NA LINHA DE CLOCK

A chave TTL/CMOS deve estar na posio TTL, caso contrrio a placa de

experincias poder ser danificada.

1.

2.

3.

4.

5.

6.

Desligar o Mdulo Universal 2000;

Colocar a chave TTL/CMOS na posio TTL;

Encaixar a placa de experincias ED03 no SLOT H do Mdulo Universal 2000;

Ligar o Mdulo Universal;

Colocar a chave H na posio 1 e as chaves I e J na posio ;

O circuito a ser verificado ser o da figura 25:

+5V

4

2

A

1

2

74LS04

4

74LS04

6

74LS04

Preset

ck

74LS74

74LS04

Clear

L0

L1

1

B

Figura 25 - Circuito com Introduo de um atraso na linha do Clock

Este circuito fornece um atraso entre o dado e o clock. Caso o uso de 4 inversores no

for suficiente, deve-se aumentar o nmero de inversores para obter um atraso maior.

Este atraso pode variar, dependo do fabricante.

Datapool Eletrnica

Captulo 3 Flip-Flops

15

7. Completar a tabela da figura 26.

ENTRADAS

D = ck

A

Clear

B

1

1

SADAS

Q

L

Q

L1

Figura 26 - Tabela de Funcionamento do Circuito da Figura 25

8. Concluso:

Com a modificao introduzida, o atraso de tempo dos gates inversores promovem

o tSET-UP. Deste modo, o dispositivo funcionou corretamente. A figura 27 mostra as

formas de onda do ocorrido.

Figura 27 - Formas de Onda do Circuito da figura 25

EXERCCIOS

a)

b)

Datapool Eletrnica

Com um flip-flop J-K pode-se construir um flip-flop D.

1.

Certo.

2.

Errado.

As linhas de Preset e de Clear prevalecem sobre as outras linhas de

entrada.

1.

Certo.

2.

Errado.

Captulo 3 Flip-Flops

c)

d)

Datapool Eletrnica

Em um flip-flop Mestre-Escravo o

clock:

16

funcionamento correto exige que o

1.

Tenha um Edge negativo.

2.

Tenha um Edge positivo.

3.

Saia do nvel , v para 1, permanea um tempo

mnimo 1 e volte para .

O tempo set-up em um flip-flop D exige que:

1.

A entrada D esteja presente aps o clock.

2.

A entrada D esteja presente antes do clock.

3.

A entrada D e o clock devam ocorrer simultaneamente.

Captulo 3 Flip-Flops

CAPTULO 3 : FLIP-FLOPS.................................................................................1

INTRODUO............................................................................................................... 1

FLIP-FLOP S-R .......................................................................................................... 1

FLIP-FLOP T .............................................................................................................. 3

FLIP-FLOP D.............................................................................................................. 3

FLIP-FLOP JK ............................................................................................................ 4

TIPOS DE GATILHAMENTO DOS FLIP-FLOPS ....................................................... 4

FLIP-FLOPS GATILHVEIS DO TIPO MESTRE-ESCRAVO .................................... 6

FLIP-FLOP MESTRE-ESCRAVO COM DATA LOCK-OUT ....................................... 7

PARMETROS IMPORTANTES DOS FLIP-FLOPS ................................................. 8

a)

b)

c)

TEMPO DE SETAMENTO -tSET-UP .................................................................................8

TEMPO DE MANUTENO - tHOLD ...............................................................................8

FREQNCIA MXIMA fmx .......................................................................................8

OBJETIVO..................................................................................................................... 8

MATERIAL NECESSRIO............................................................................................ 8

PROCEDIMENTO.......................................................................................................... 8

EXPERINCIA 1 : FLIP-FLOP JK MESTRE-ESCRAVO ............................................. 9

EXPERINCIA 2 : FLIP-FLOP TIPO D....................................................................... 10

EXPERINCIA 3 : FLIP-FLOP D UTILIZANDO ENTRADAS PRESET E CLEAR .... 12

EXPERINCIA 4 : OBSERVAO DO tSET-UP............................................................ 13

EXPERINCIA 5 : INTRODUO DE ATRASO NA LINHA DE CLOCK.................. 14

EXERCCIOS:.............................................................................................................. 15

Datapool Eletrnica

Você também pode gostar

- Manual Gestor Frota #12Documento29 páginasManual Gestor Frota #12Cairo Gonçalves100% (1)

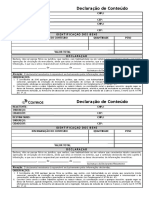

- Declaração de ConteúdoDocumento1 páginaDeclaração de ConteúdoCairo GonçalvesAinda não há avaliações

- O Problema Do Plágio AcadêmicoDocumento10 páginasO Problema Do Plágio AcadêmicoCairo GonçalvesAinda não há avaliações

- Check List para Veicúlos 1Documento3 páginasCheck List para Veicúlos 1diracmoutinho100% (1)

- Relatório de Prestação de Contas: Categoria QTD Não Reembolsáveis Reembolsáveis TotalDocumento6 páginasRelatório de Prestação de Contas: Categoria QTD Não Reembolsáveis Reembolsáveis TotalCairo GonçalvesAinda não há avaliações

- Check List para Carros Usados Attach s636751Documento2 páginasCheck List para Carros Usados Attach s636751Nuno Cunha100% (1)

- Projeto de Pesquisa (Modelo)Documento29 páginasProjeto de Pesquisa (Modelo)Cairo GonçalvesAinda não há avaliações

- Intro IPv6Documento50 páginasIntro IPv6Cairo GonçalvesAinda não há avaliações

- Manual Teoria Do ErpDocumento221 páginasManual Teoria Do ErpJoao MarceloAinda não há avaliações

- Manual para Elaboração de ArtigosDocumento45 páginasManual para Elaboração de Artigosmuleke21Ainda não há avaliações

- Exercicio Enderecamento (Nic - BR)Documento3 páginasExercicio Enderecamento (Nic - BR)Cairo GonçalvesAinda não há avaliações

- A RDS Canavitsas Adhoc 06MAIODocumento16 páginasA RDS Canavitsas Adhoc 06MAIOCairo GonçalvesAinda não há avaliações

- COMO CONVERTER O SEU CARRO PARA ELÉTRICO - Elifas GurgelDocumento170 páginasCOMO CONVERTER O SEU CARRO PARA ELÉTRICO - Elifas GurgelCairo Gonçalves50% (2)

- Referências em Formato Eletrônico PDFDocumento22 páginasReferências em Formato Eletrônico PDFCairo GonçalvesAinda não há avaliações

- Introdução Ao Espalhamento EspectralDocumento21 páginasIntrodução Ao Espalhamento EspectralHelio MouraAinda não há avaliações

- 173Documento105 páginas173Cairo GonçalvesAinda não há avaliações

- Formatação de Trabalhos AcadêmicosDocumento16 páginasFormatação de Trabalhos AcadêmicosCairo GonçalvesAinda não há avaliações

- SBRT 07 Espectro CaoticoDocumento5 páginasSBRT 07 Espectro CaoticoCairo GonçalvesAinda não há avaliações

- 2012 RenatoSalesBizerra PDFDocumento78 páginas2012 RenatoSalesBizerra PDFCairo GonçalvesAinda não há avaliações

- Referências em Formato EletrônicoDocumento22 páginasReferências em Formato EletrônicoCairo GonçalvesAinda não há avaliações

- ResumoDocumento1 páginaResumoCairo GonçalvesAinda não há avaliações

- 2012 RenatoSalesBizerra PDFDocumento78 páginas2012 RenatoSalesBizerra PDFCairo GonçalvesAinda não há avaliações

- Ia889 11 PDFDocumento6 páginasIa889 11 PDFCairo GonçalvesAinda não há avaliações

- Artigo Cientifico Normas Da ABNT.Documento7 páginasArtigo Cientifico Normas Da ABNT.Edinho LarruscainAinda não há avaliações

- Set 1Documento8 páginasSet 1Enos Marcos BastosAinda não há avaliações

- LTEDocumento1 páginaLTECairo GonçalvesAinda não há avaliações

- 2012 RenatoSalesBizerra PDFDocumento78 páginas2012 RenatoSalesBizerra PDFCairo GonçalvesAinda não há avaliações

- Tutorialredes 4 GDocumento17 páginasTutorialredes 4 GCairo GonçalvesAinda não há avaliações

- O Espectro de Frequencia Telecomunicacoes PDFDocumento10 páginasO Espectro de Frequencia Telecomunicacoes PDFCairo GonçalvesAinda não há avaliações

- Matlab UFMSDocumento89 páginasMatlab UFMSLeonardo FerreiraAinda não há avaliações

- Manual de Uso e Peças - PXDocumento33 páginasManual de Uso e Peças - PXThiago DuarteAinda não há avaliações

- Redes de Banda LargaDocumento3 páginasRedes de Banda LargaRico Root'sAinda não há avaliações

- CPU Expert DX - CatálogoDocumento132 páginasCPU Expert DX - CatálogoCaio SlompoAinda não há avaliações

- Manual de Normas Logo PO CHDocumento140 páginasManual de Normas Logo PO CHHugo Chorão PereiraAinda não há avaliações

- Srco FeiDocumento115 páginasSrco FeiShimon Whoami DemicovitchAinda não há avaliações

- Requisitos Técnicos para Instalação 24-08-22Documento9 páginasRequisitos Técnicos para Instalação 24-08-22Marcelo L. da SilvaAinda não há avaliações

- Mop 7Documento2 páginasMop 7Weslei CunhaAinda não há avaliações

- Neurodyn Portable TENS FESDocumento42 páginasNeurodyn Portable TENS FESFabiana Alves Da Silva Xavier100% (1)

- Guia Hardware ComptiaA+-10Documento120 páginasGuia Hardware ComptiaA+-10ROBERTO GOMESAinda não há avaliações

- Curso de Telefonia Celular (GSM e 5G)Documento11 páginasCurso de Telefonia Celular (GSM e 5G)Elisiö Dicälä Homem da LéiAinda não há avaliações

- Como Crimpar Cabo de Rede Rj45 e Rj11 (Tutorial Completo)Documento9 páginasComo Crimpar Cabo de Rede Rj45 e Rj11 (Tutorial Completo)Perionda0% (1)

- DM706 R1Documento11 páginasDM706 R1Thiago OliveiraAinda não há avaliações

- CTM CTM104754 Jul12 PT PDFDocumento2.362 páginasCTM CTM104754 Jul12 PT PDFIvo Silva100% (2)

- Configuraã Ã Es Bã - Sicas Id880hDocumento9 páginasConfiguraã Ã Es Bã - Sicas Id880hRicardoAinda não há avaliações

- Grade Engenharia Elétrica PDFDocumento3 páginasGrade Engenharia Elétrica PDFFernando DiasAinda não há avaliações

- Catalogo VHF 2022 17mb PDFDocumento35 páginasCatalogo VHF 2022 17mb PDFAxel FurtadoAinda não há avaliações

- Ocupação Dos Fusiveis New Actros PDFDocumento8 páginasOcupação Dos Fusiveis New Actros PDFluan hemriqueAinda não há avaliações

- Manual Portão Peccinin CP3020Documento23 páginasManual Portão Peccinin CP3020Fernando Barbosa67% (3)

- Guia Rápido de Manuntenção - F650 - r1Documento24 páginasGuia Rápido de Manuntenção - F650 - r1robertoseniorAinda não há avaliações

- Sistemas EmbarcadosDocumento8 páginasSistemas EmbarcadosLeonardo RochaAinda não há avaliações

- Manual Instalação ATI QuitériosDocumento16 páginasManual Instalação ATI QuitériosNuno MonteiroAinda não há avaliações

- Transístor Bipolar: Dr. José A. Chaljub DuarteDocumento33 páginasTransístor Bipolar: Dr. José A. Chaljub DuarteWalter António CumbucaneAinda não há avaliações

- Toledo: MODELO 2095Documento22 páginasToledo: MODELO 2095Henryque FariasAinda não há avaliações

- Toshiba Sd3010s 3020vk CompletoDocumento47 páginasToshiba Sd3010s 3020vk CompletoFernando Monteiro67% (3)

- Informações Técnicas - Sinais de VídeoDocumento68 páginasInformações Técnicas - Sinais de VídeoFernando LopesAinda não há avaliações

- Atualização+software+d32w931 Rev1 2Documento5 páginasAtualização+software+d32w931 Rev1 2Paulo Henrique100% (2)

- Arduino-Ce - Automação Residencial Com Celular Usando Arduino MegaDocumento16 páginasArduino-Ce - Automação Residencial Com Celular Usando Arduino MegaEvandro Junior RodriguesAinda não há avaliações

- Dentroda Placa Mae 1Documento5 páginasDentroda Placa Mae 1p3r3gr1n0Ainda não há avaliações

- Inversor de FrequênciaDocumento4 páginasInversor de FrequênciaPedro AraujoAinda não há avaliações

- Chip Ene KB 9012 QF A3 Gravar FirmewareDocumento8 páginasChip Ene KB 9012 QF A3 Gravar FirmewareKrista TranAinda não há avaliações