Escolar Documentos

Profissional Documentos

Cultura Documentos

Lista de Exercícios - Circuitos Combinacionais

Enviado por

CarlinhosDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Lista de Exercícios - Circuitos Combinacionais

Enviado por

CarlinhosDireitos autorais:

Formatos disponíveis

UNIVERSIDADE FEDERAL DO ESPÍRITO SANTO

CENTRO TECNOLÓGICO – Departamento de Engenharia Elétrica

Circuitos Lógicos – ELE15935 – Lista de Exercícios de Circuitos Combinacionais

Data: 25/09/2023

Aluno : _______________________________________________Turma Lab. :___

1) Represente a função F(A,B,C) na Tabela-verdade 1 nas formas canônicas de Tabela-verdade 1

(a) (1,0 ponto) Soma de Mintermos

(b) (1,0 ponto) Produto de Maxtermos

2) a-Escreva a forma de soma de mintermos para a função

F(w,x,y,z) = (w + x’yz’)’ + wxy’

usando os teoremas da álgebra de Boole. Escreva as propriedades que utilizar em cada passo de

transformação.

b-Determine a soma de produtos mínima (grupos de 1's) usando mapas de Karnaugh

c-Determine o produto de somas mínimo (grupos de 0's) usando mapas de Karnaugh.

d-Considerando que as variáveis estão disponíveis em forma normal e complementada, determine o custo

de cada implementação em termos de número de entradas de portas AND e OR.

e-Desenhe a forma mínima (ou seja, de menor custo) obtida para a função.

Obs1: faça um mapa de Karnaugh para agrupar 0's e outro para agrupar 1's.

Obs2: as portas AND e OR podem ter mais de 2 entradas.

3) Quine McCluskey

a) Escreva a expressão de soma de produtos mínima para a função

f(D,C,B,A)=(D+C+B+A)(D+C+B+A’)(D+C+B’+A)(D+C’+B’+A)(D’+C+B+A)(D’+C+B’+A)

(D’+C+B’+A’)(D’+C’+B+A)

usando o método de Quine McCluskey. Considere que as entradas DCBA = 0101, 0111, 1101 e 1111 nunca

acontecem e, portanto, nestes casos a saída é don’t care.

b) Verifique seu resultado fazendo o mapa de Karnaugh.

c) Desenhe o circuito usando dois níveis de NAND.

Obs1: as portas NAND podem ter mais de 2 entradas.

Obs2: considere que as entradas normais e complementadas estão disponíveis.

4) Projete um deslocador com uma entrada de dados X, três entradas de controle (MULT, DIV e ROT_R)

de 1 bit cada e uma saída Z de 4 bits que realize as seguintes funções (em ordem de prioridade decrescente):

I. Multiplicação inteira por 2 (entrada de controle MULT = 1)

II. Divisão inteira por 2 mantendo o sinal em complemento de dois (entrada de controle DIV = 1)

III. Deslocamento circular para a direita de 1 bit (entrada de controle ROT_R= 1)

IV. Não deslocar

Utilize multiplexadores do menor tamanho possível para o deslocamento e minimize a rede combinacional

que gera os sinais de seleção dos MUXes. Desenhe a rede completamente.

5) a)Projete um circuito conversor de código Gray em 3 bits (G2,G1,G0) para código binário em 3 bits

(B2,B1,B0) usando portas XOR e XNOR de duas entradas onde for conveniente de acordo com a expressão

obtida no mapa de Karnaugh. Desenhe o circuito sabendo que o número de níveis pode ser maior que dois.

b) Implemente novamente o circuito utilizando um decodificador de 3:8 e portas OR.

Código Gray(entrada):

G2G1G0 = 000-001-011-010-110-111-101-100

Código Binário(saída):

B2B1B0 = 000-001-010-011-100-101-110-111

6) Utilize um MUX de 8:1 para implementar a função

f(D,C,B,A) = ∏M(1,2,4,5,7,11,12)

conectando as entradas de dados aos sinais D, D', 1 (Vdd) ou 0

(Gnd). Justifique a escolha das conexões usando mapas de Karnaugh

e/ou tabelas verdade.

7) Considere a arquitetura de uma Unidade Aritmética da Figura 1 que, para 2 palavras de entrada de n bits

cada (x e y, em complemento de dois), implemente as operações conforme a Tabela 1, onde s é saída

(também de n bits). Implemente completamente o circuito que controla a unidade, ou seja, a rede que

determina Kx, KMX, Ky, KMY, c0 a partir de x, y, f (f2f1f0) e cin, minimizando cada circuito. Gere também as

saídas zero (que é igual a 1 se s=0), sign (que é o sinal de s), overflow (que indica se o resultado ultrapassou

o limite da representação) e cout (que é o carry ou vai-1 da soma dos n bits).

Código da

Função

f2f1f0 Função

000 z = x+1

001 z = x+y

010 z = y+1

011 z = x-y

100 z = y-x

101 z = abs(x)

110 z=-y

111 z=-x

Tabela 1

Figura 1

Bom trabalho!

Profa. Eliete Caldeira

Você também pode gostar

- Lista de Exercícios de Aritmética de Ponto FlutuanteDocumento5 páginasLista de Exercícios de Aritmética de Ponto FlutuanteDiego santiago de lima0% (1)

- Limite e ContinuidadeDocumento19 páginasLimite e ContinuidadeHeitor Claro da SilvaAinda não há avaliações

- Lista 1Documento4 páginasLista 1wfsouza2010Ainda não há avaliações

- Exercicio Arquitetura de ComputadoresDocumento3 páginasExercicio Arquitetura de Computadorestbsss100% (1)

- Circuitos digitais: lista de exercícios de eletrônica digitalDocumento2 páginasCircuitos digitais: lista de exercícios de eletrônica digitalfdsafsdAinda não há avaliações

- ELC 1112 - Aritmética DigitalDocumento50 páginasELC 1112 - Aritmética DigitalRicardo Souza SenandesAinda não há avaliações

- Vários Exercícios Sobre FUNCOES DO 1º 2º GRAUDocumento18 páginasVários Exercícios Sobre FUNCOES DO 1º 2º GRAUramires79Ainda não há avaliações

- Função quadrática - lista de exercíciosDocumento9 páginasFunção quadrática - lista de exercíciosJetro DimitreAinda não há avaliações

- Funções Do 2º GrauDocumento24 páginasFunções Do 2º Grauanon-611911100% (4)

- Sist Dig V21Documento57 páginasSist Dig V21Nuno CarvalhoAinda não há avaliações

- Curso de Engenharia Eléctrica LaboratórioDocumento7 páginasCurso de Engenharia Eléctrica LaboratórioPatrick AugustoAinda não há avaliações

- Funções Polinomiais - ExercíciosDocumento6 páginasFunções Polinomiais - ExercíciosisraelemanuaAinda não há avaliações

- Lista de exercícios de funções quadráticasDocumento3 páginasLista de exercícios de funções quadráticasJoão AugustoAinda não há avaliações

- Funções quadráticasDocumento5 páginasFunções quadráticasDaniele RodriguesAinda não há avaliações

- Representações Transformadas; Filtragem no tempo e na frequência - Lista de Exercícios parte 2Documento11 páginasRepresentações Transformadas; Filtragem no tempo e na frequência - Lista de Exercícios parte 2Joselito da SilvaAinda não há avaliações

- Função Do 2º Grau (Quadrática)Documento20 páginasFunção Do 2º Grau (Quadrática)Papiro é a soluçãoAinda não há avaliações

- GABProfMarcosRevisaoPrimSerMATITerCert2015Documento5 páginasGABProfMarcosRevisaoPrimSerMATITerCert2015natyellenramosribeiroAinda não há avaliações

- CNC CadernodeExercícioseRespostasDocumento107 páginasCNC CadernodeExercícioseRespostasdalibolzanAinda não há avaliações

- Função - Parte 4Documento8 páginasFunção - Parte 4YOUTUBER PLAYERAinda não há avaliações

- Função - Parte 4Documento8 páginasFunção - Parte 4Micael LourençoAinda não há avaliações

- Funções do 1o Grau (AfimDocumento6 páginasFunções do 1o Grau (AfimF9C19 - ISABELLA FONTAINE REISAinda não há avaliações

- Microsoft Word Função Quadrática GabDocumento2 páginasMicrosoft Word Função Quadrática GabCamila SilvaAinda não há avaliações

- Lista de Atividades de Funções de 1º e 2º GrausDocumento4 páginasLista de Atividades de Funções de 1º e 2º GrausEdu gameplayAinda não há avaliações

- Cálculo I - Função do 1o grau e gráficos de retasDocumento13 páginasCálculo I - Função do 1o grau e gráficos de retasBeatriz CastroAinda não há avaliações

- Funções quadráticasDocumento15 páginasFunções quadráticascapitão gondinAinda não há avaliações

- Funçao AfimDocumento4 páginasFunçao AfimIsrael Miguel CostaAinda não há avaliações

- fgvsp2012 AdministracaoDocumento79 páginasfgvsp2012 Administracaosilvaerikvieira300Ainda não há avaliações

- Lista de exercícios de funções quadráticasDocumento3 páginasLista de exercícios de funções quadráticasIsabela LimaAinda não há avaliações

- RESOLUcAODocumento15 páginasRESOLUcAOMayala ChuAinda não há avaliações

- Exercicios para A ProvaDocumento3 páginasExercicios para A ProvaMarco Antonio GomesAinda não há avaliações

- Apostila 2 de 2015 Função Quadratica, ExponencialDocumento13 páginasApostila 2 de 2015 Função Quadratica, Exponencialkurth096657Ainda não há avaliações

- Função Do 1° GrauDocumento4 páginasFunção Do 1° GrauAline *Materiais de estudo para concursos*100% (2)

- Lista I - III Unidade - 9° Ano - Dom Pedro II.Documento6 páginasLista I - III Unidade - 9° Ano - Dom Pedro II.yasmin gomesAinda não há avaliações

- Lista 3 GabaritoDocumento5 páginasLista 3 GabaritoJulia Helena RossieriAinda não há avaliações

- 1 - Lista de Funções Do 1º GrauDocumento4 páginas1 - Lista de Funções Do 1º GrauAndre MartinsAinda não há avaliações

- Experimento 04 AM Parte 1Documento7 páginasExperimento 04 AM Parte 1Lucas OliveiraAinda não há avaliações

- Lista 1Documento9 páginasLista 1Grazielle Tomaz NevesAinda não há avaliações

- Lab 3 SCMDocumento15 páginasLab 3 SCMCaetano PellegrinAinda não há avaliações

- 5 ListaDocumento7 páginas5 ListaPriscilla Braga Pinheiro CorrêaAinda não há avaliações

- Cálculo Diferencial - Funções, Exercícios e GráficosDocumento15 páginasCálculo Diferencial - Funções, Exercícios e GráficosErica Helena Martins de OliveiraAinda não há avaliações

- Teoria - FunçõesDocumento4 páginasTeoria - FunçõesCircuito JavaAinda não há avaliações

- Funções matemáticasDocumento14 páginasFunções matemáticasRodrigo SgarbiAinda não há avaliações

- Função QuadráticaDocumento5 páginasFunção QuadráticaEdinei Chagas100% (1)

- Serie4 ResolucaoCircuitosLogicosI PDFDocumento11 páginasSerie4 ResolucaoCircuitosLogicosI PDFLais Fernanda'100% (1)

- Exercícios de Cálculo Numérico: Erros de Aproximação e Métodos para Equações Não-linearesDocumento20 páginasExercícios de Cálculo Numérico: Erros de Aproximação e Métodos para Equações Não-linearesLucas TuãoAinda não há avaliações

- Exercícios de Cálculo Numérico: Erros de Aproximação e Métodos para Equações Não-linearesDocumento20 páginasExercícios de Cálculo Numérico: Erros de Aproximação e Métodos para Equações Não-linearesLucas TuãoAinda não há avaliações

- Lista de Exercícios LP07Documento3 páginasLista de Exercícios LP07FABIO EDUARDO MANSILLA CONDEAinda não há avaliações

- Função Do 2º GrauDocumento2 páginasFunção Do 2º GrauJúlio César0% (1)

- Null 4Documento1 páginaNull 4Anivaldo SamboAinda não há avaliações

- Ficha DerivadasDocumento8 páginasFicha DerivadasRenata PereiraAinda não há avaliações

- Lista de Cálculo NuméricoDocumento4 páginasLista de Cálculo NuméricoAnonymous 1QsclBAinda não há avaliações

- Função quadrática: análise e aplicaçõesDocumento3 páginasFunção quadrática: análise e aplicaçõesJulioCesarMohnsamAinda não há avaliações

- CDI I - Lista 1 de funções e gráficosDocumento4 páginasCDI I - Lista 1 de funções e gráficosjoselitoAinda não há avaliações

- Curso SI: Funções do 1o e 2o grauDocumento3 páginasCurso SI: Funções do 1o e 2o grauSamuel De Paula Faria50% (2)

- Aula 1 ScilabDocumento6 páginasAula 1 ScilabHenry FerreiraAinda não há avaliações

- LIsta de Exercícios - Função Afim e Quadrática (4)Documento5 páginasLIsta de Exercícios - Função Afim e Quadrática (4)romanafsoaresAinda não há avaliações

- Função ExponencialDocumento12 páginasFunção ExponencialNoberto Pessoa100% (1)

- Controle Vetorial, Máquina De Indução E Métodos NuméricosNo EverandControle Vetorial, Máquina De Indução E Métodos NuméricosAinda não há avaliações

- Manual Placa Kazuk G41Documento8 páginasManual Placa Kazuk G41Jorge PetersenAinda não há avaliações

- Relatório 06 - Mux e DemuxDocumento11 páginasRelatório 06 - Mux e DemuxJoão Pedro da Silva RodriguesAinda não há avaliações

- Apostila PICMINASDocumento120 páginasApostila PICMINASMatheus AndradeAinda não há avaliações

- Apostila - Introdução Aos Microcontroladores ARM Cortex-M4 Tiva C Series Da Texas InstrumentsDocumento61 páginasApostila - Introdução Aos Microcontroladores ARM Cortex-M4 Tiva C Series Da Texas InstrumentsDiego SchneiderAinda não há avaliações

- Sistemas de numeração digital e código BCDDocumento33 páginasSistemas de numeração digital e código BCDJosé Ferreira JúniorAinda não há avaliações

- Entrega Semana 3y5 Subgrupo #17 OKDocumento23 páginasEntrega Semana 3y5 Subgrupo #17 OKMaria HolguinAinda não há avaliações

- Tipos de Memória RAMDocumento6 páginasTipos de Memória RAMCPUCGAinda não há avaliações

- Notas de Aula 07Documento59 páginasNotas de Aula 07Pedro VaraAinda não há avaliações

- Sistemas Eletrônicos Embarcados: Ewaldo Luiz de Mattos MehlDocumento18 páginasSistemas Eletrônicos Embarcados: Ewaldo Luiz de Mattos Mehls5w0s56wwAinda não há avaliações

- Apostila Informatica CompletaDocumento303 páginasApostila Informatica CompletaFlavioswAinda não há avaliações

- Registradores de Deslocamento e Máquinas de Estados FinitosDocumento12 páginasRegistradores de Deslocamento e Máquinas de Estados FinitosJefferson CavalcanteAinda não há avaliações

- Coerência de cache: protocolos de hardware e softwareDocumento4 páginasCoerência de cache: protocolos de hardware e softwareThiago MeirelesAinda não há avaliações

- Assembly Program DebuggingDocumento12 páginasAssembly Program DebuggingRenê PaivaAinda não há avaliações

- Flip-Flops Diagramas Tempo ExercíciosDocumento5 páginasFlip-Flops Diagramas Tempo ExercíciosFladimy RochaAinda não há avaliações

- Sistemas Digitais - Produtos Canônicos e MUXDocumento64 páginasSistemas Digitais - Produtos Canônicos e MUXJACKSON TORRES DE LIMAAinda não há avaliações

- Contadores e Registradores: Projeto e AplicaçõesDocumento30 páginasContadores e Registradores: Projeto e AplicaçõesPedro ThiagoAinda não há avaliações

- Cap19 - Configurações de JumpersDocumento66 páginasCap19 - Configurações de Jumpersapi-3711983100% (1)

- Códigos AMI e Phoenix BIOSDocumento5 páginasCódigos AMI e Phoenix BIOSAntonio PradoAinda não há avaliações

- Circuitos Digitais AnáliseDocumento78 páginasCircuitos Digitais AnálisePedro T V Souza100% (1)

- Arquitetura SEsDocumento42 páginasArquitetura SEsMarcosAinda não há avaliações

- Workstation Razor Pro Prodigy (Minimo)Documento3 páginasWorkstation Razor Pro Prodigy (Minimo)Anonymous dDfyKNkQAAinda não há avaliações

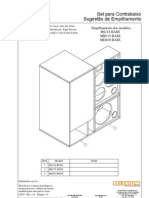

- Set contrabaixo 3 caixasDocumento14 páginasSet contrabaixo 3 caixassaymoncoppiAinda não há avaliações

- Gravador de 8051Documento26 páginasGravador de 8051Lucio MarlonAinda não há avaliações

- Risc e CiscDocumento17 páginasRisc e CiscMonique CorrêaAinda não há avaliações

- Sistemas digitais microcontroladosDocumento86 páginasSistemas digitais microcontroladosdener10Ainda não há avaliações

- Como Funciona A Placa PC AnalyzerDocumento3 páginasComo Funciona A Placa PC AnalyzerThalisson OliveiraAinda não há avaliações

- Introdução à lógica programável - 10o AnoDocumento1 páginaIntrodução à lógica programável - 10o AnoWilliam CoteAinda não há avaliações

- Unidade III - O Hardware de Um MicrocontroladorDocumento18 páginasUnidade III - O Hardware de Um MicrocontroladorDouglas José de Souza VieiraAinda não há avaliações